# High Current Driver Amplifier and Digital VGA/Preamplifier with 3 dB Steps

# AD8260

#### FEATURES

**High current driver** Differential input—direct drive from DAC Preset gain: 1.5× -3 dB bandwidth: 195 MHz Large output drive: >±300 mA VGA/preamplifier Low noise Voltage noise: 2.4 nV/√Hz Current noise: 5 pA/√Hz -3 dB bandwidth: 230 MHz Gain range: 30 dB in 3 dB steps -6 dB to +24 dB (for preamplifier gain of 6 dB) Single-ended preamplifier input and differential VGA output Supplies: 3.3 V to 10 V (with VMID enabled) ±3.3 V to ±5 V (with VMID disabled) Power: 93 mW with 3.3 V supplies Power-down for VGA, driver amplifier, and system

#### APPLICATIONS

Digital AGC systems Tx/Rx signal processing Power line transceivers

#### **GENERAL DESCRIPTION**

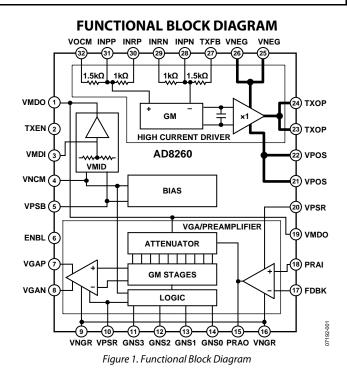

The AD8260 includes a high current driver, usable as a transmitter, and a low noise digitally programmable variable gain amplifier (DGA), useable as a receiver.

The receiver section consists of a single-ended input preamplifier, and linear-in-dB, differential-output DGA. The receiver has a small signal -3 dB bandwidth of 230 MHz; the driver small signal bandwidth is 195 MHz. The driver delivers ±300 mA, well suited for driving low impedance loads, even when connected to a 3.3 V supply.

The AD8260 DGA is ideal for trim applications and has a gain span of 30 dB, in 3 dB steps. Excellent bandwidth uniformity is maintained across the entire frequency range. The low outputreferred noise of the DGA is advantageous in driving high speed ADCs. The differential output facilitates the interface to modern low voltage high speed ADCs.

Single-supply and dual-supply operation makes the part versatile and enables gain control of negative-going pulses, such as those generated by photodiodes or photo-multiplier tubes, as well as processing band-pass signals on a single supply. For maximum

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

dynamic range, it is essential that the part be ac-coupled when operating on a single supply.

The AD8260 preamplifier (PrA) is configured with external resistors for gains greater than 6 dB and can be inverting or noninverting. The DGA is characterized with a noninverting preamplifier gain of  $2\times$ . The attenuator has a range of 30 dB and the output amplifier has a gain of  $8\times$  (18.06 dB). The lowest noninverting gain range is -6 dB to +24 dB and shifts up with increased preamplifier gain. The gain is controlled via a parallel port (Pin GNS0 to Pin GNS3) with 10 gain steps of 3 dB per code. The preamplifier and DGA are disabled for any code that is not assigned a gain step.

The AD8260 can operate with single or dual supplies from 3.3 V to  $\pm 5$  V. An internal buffer normally provides a split supply reference for single-supply operation; an external reference can also be used when the VMID buffer is shut down.

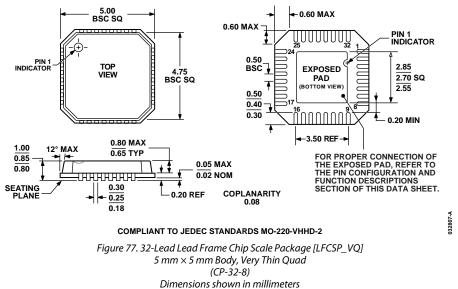

The operating temperature range is  $-40^{\circ}$ C to  $+105^{\circ}$ C. The AD8260 is available in a 5 mm × 5 mm, 32-lead LFCSP.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2008-2011 Analog Devices, Inc. All rights reserved.

# TABLE OF CONTENTS

| VMID Buffer                             | 22 |

|-----------------------------------------|----|

| Preamplifier                            | 22 |

| Preamplifier Noise                      | 22 |

| DGA                                     | 23 |

| Gain Control                            |    |

| Output Stage                            |    |

| Attenuator                              |    |

| Single-Supply Operation and AC Coupling | 24 |

| Power-Up/Power-Down Sequence            |    |

| Logic Interfaces                        |    |

| Applications Information                | 25 |

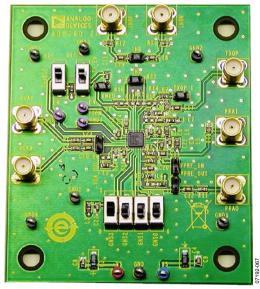

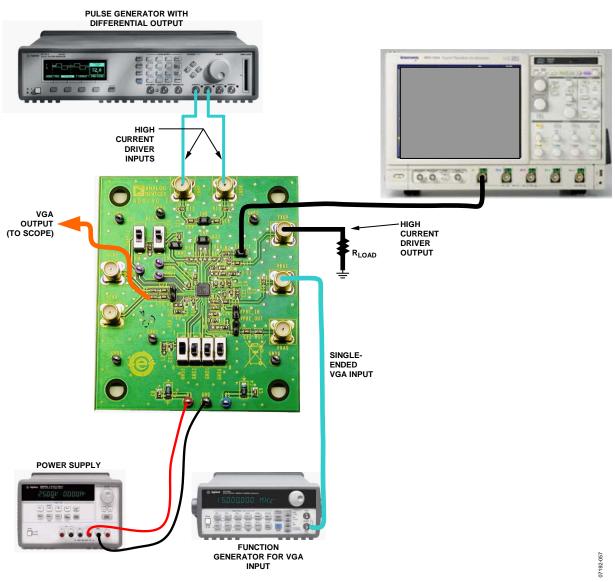

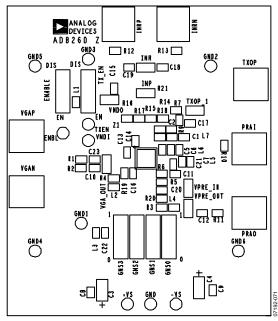

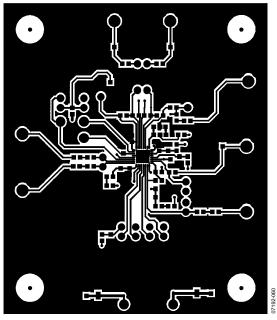

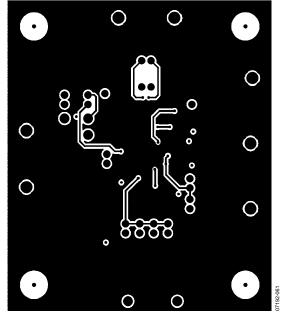

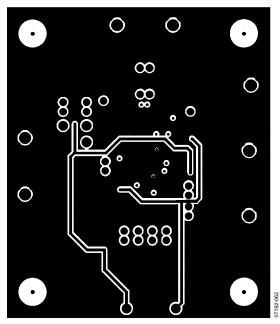

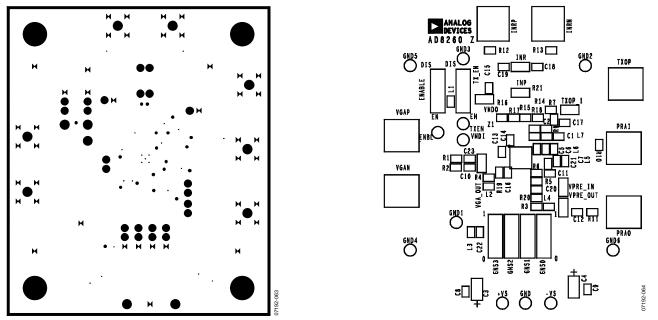

| Evaluation Board                        |    |

| Connecting the Evaluation Board         |    |

| Outline Dimensions                      |    |

| Ordering Guide                          |    |

### **REVISION HISTORY**

| 2/11—Rev. 0 to Rev. A            |   |

|----------------------------------|---|

| Added EPAD Notation              | 7 |

| Changes to Figure 70             |   |

| 5/08—Revision 0: Initial Version |   |

### **SPECIFICATIONS**

$V_s$  (supply voltage) = 3.3 V,  $T_A$  = 25°C, preamplifier gain = 2× ( $R_{FB1} = R_{FB2} = 100 \Omega$ ),  $V_{VMDO} = V_s/2$ , f = 10 MHz,  $C_L$  = 5 pF,  $R_{LOAD}$  = 500  $\Omega$ , DGA differential output. All dBm values are referenced to 50  $\Omega$ , gain code 1011, unless otherwise specified.

| Parameter                                                          | Conditions                                                                                                                                                                                                                                                  | Min | Тур               | Max | Unit |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------|-----|------|

| DRIVER AMPLIFIER—GENERAL PARAMETERS                                |                                                                                                                                                                                                                                                             |     |                   |     |      |

| –3 dB Small Signal Bandwidth                                       | $V_{OUT} = 10 \text{ mV p-p}, R_{LOAD} = 500 \Omega$                                                                                                                                                                                                        |     | 195               |     | MHz  |

|                                                                    | $V_{OUT} = 10 \text{ mV p-p}, R_{LOAD} = 50 \Omega$                                                                                                                                                                                                         |     | 120               |     | MHz  |

|                                                                    | $V_{OUT} = 10 \text{ mV p-p}, R_{LOAD} = 10 \Omega$                                                                                                                                                                                                         |     | 85                |     | MHz  |

| –3 dB Large Signal Bandwidth                                       | $V_{OUT} = 1 V p - p$                                                                                                                                                                                                                                       |     | 195               |     | MHz  |

|                                                                    | $V_{OUT} = 2 V p - p$                                                                                                                                                                                                                                       |     | 190               |     | MHz  |

|                                                                    | $V_{OUT} = 2 V p - p, R_{IOAD} = 50 \Omega$                                                                                                                                                                                                                 |     | 180               |     | MHz  |

| Slew Rate                                                          | $V_{OUT} = 1 V p p$                                                                                                                                                                                                                                         |     | 730               |     | V/µs |

|                                                                    | $V_{OUT} = 2 V p - p$                                                                                                                                                                                                                                       |     | 725               |     | V/µs |

|                                                                    | $V_{OUT} = 2 V p - p, R_{IOAD} = 50 \Omega$                                                                                                                                                                                                                 |     | 620               |     | V/µs |

| Gain                                                               | Nominal gain with internal gain setting resistors                                                                                                                                                                                                           | 3.0 | 3.52              |     | dB   |

| Input Voltage Noise                                                | f = 10 MHz                                                                                                                                                                                                                                                  |     | 9.5               |     | nV/√ |

| Noise Figure                                                       | $R_s = 100 \Omega$ (differential, 2 × 50 $\Omega$ that convert differential DAC output currents to differential voltage)                                                                                                                                    |     | 17.6              |     | dB   |

| Output-Referred Noise                                              | Gain = $3.52 \text{ dB} (1.5 \times)$ , includes internal gain setting resistors                                                                                                                                                                            |     | 14.3              |     | nV/√ |

| Output Impedance                                                   | DC to 10 MHz, $V_s = \pm 3.3 V$                                                                                                                                                                                                                             |     | ≤1.7              |     | Ω    |

| Output Current                                                     | $R_{LOAD} = 1 \Omega, V_{IN} = \pm 0.5 V$                                                                                                                                                                                                                   |     | ±310              |     | mA   |

| Output Signal Range                                                | $R_{LOAD} \ge 500 \Omega$                                                                                                                                                                                                                                   |     | $V_{MDO} \pm 1.5$ |     | v    |

|                                                                    | $V_s = +5 V$                                                                                                                                                                                                                                                |     | $V_{MDO} \pm 2.3$ |     | v    |

|                                                                    | $V_{c} = \pm 5 V$                                                                                                                                                                                                                                           |     | ±4.7              |     | v    |

| Input Signal Range                                                 | Differential input signal                                                                                                                                                                                                                                   |     | 2                 |     | Vp-p |

| Output Offset Voltage                                              | Gain = 3.52 dB (1.5×), max and min limits are $3\sigma$                                                                                                                                                                                                     | -20 | ±5                | +20 | mV   |

| PRIVER AMPLIFIER—DYNAMIC PERFORMANCE                               |                                                                                                                                                                                                                                                             | 20  | ±3                | 120 | IIIV |

|                                                                    | $\mathcal{V}_{-1}$                                                                                                                                                                                                                                          |     |                   |     |      |

|                                                                    | $V_{OUT} = 1 V p p$<br>f = 1 MHz                                                                                                                                                                                                                            |     | 04                |     | dDa  |

| HD2                                                                | I = I MHZ                                                                                                                                                                                                                                                   |     | -84               |     | dBc  |

| HD3                                                                | £ 10 MUL                                                                                                                                                                                                                                                    |     | -85               |     | dBc  |

| HD2                                                                | f = 10 MHz                                                                                                                                                                                                                                                  |     | -83               |     | dBc  |

| HD3                                                                |                                                                                                                                                                                                                                                             |     | -70               |     | dBc  |

| Harmonic Distortion                                                | $V_{OUT} = 2 V p - p$                                                                                                                                                                                                                                       |     | 70                |     | 10   |

| HD2                                                                | f = 1 MHz                                                                                                                                                                                                                                                   |     | -78               |     | dBc  |

| HD3                                                                | 6                                                                                                                                                                                                                                                           |     | -76               |     | dBc  |

| HD2                                                                | f = 10 MHz                                                                                                                                                                                                                                                  |     | -70               |     | dBc  |

| HD3                                                                |                                                                                                                                                                                                                                                             |     | -58               |     | dBc  |

| Input 1 dB Compression Point                                       |                                                                                                                                                                                                                                                             |     | 13                |     | dBm  |

| Multitone Power Ratio (MTPR, In-Band)                              | $R_{LOAD} = 50 \Omega$ , $V_{OUT} = 1.4 V p$ -p max, 10 tones, 2 MHz to 22 MHz with missing tone at 12 MHz (spacing 2 MHz)                                                                                                                                  |     | -49               |     | dBc  |

|                                                                    | $\label{eq:RLOAD} \begin{array}{l} R_{LOAD} = 50 \ \Omega, \ V_{OUT} = 1.4 \ V \ p-p \ max, \ 16 \ tones, \ 2 \ MHz \ to \\ 38 \ MHz \ with \ missing \ tones \ at \ 10 \ MHz, \ 20 \ MHz, \ 30 \ MHz, \\ and \ 40 \ MHz \ (spacing \ 2 \ MHz) \end{array}$ |     | -43               |     | dBc  |

| Two-Tone Intermodulation Distortion (IMD3)                         | $V_{OUT} = 1 V p-p, f_1 = 10 MHz, f_2 = 11 MHz$                                                                                                                                                                                                             |     | -90               |     | dBc  |

|                                                                    | $V_{OUT} = 2 V p-p, f_1 = 10 MHz, f_2 = 11 MHz$                                                                                                                                                                                                             |     | -71               |     | dBc  |

|                                                                    | $V_{OUT} = 1 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                                                                                                                                             |     | -60               |     | dBc  |

|                                                                    | $V_{OUT} = 2 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                                                                                                                                             |     | -48               |     | dBc  |

| Output Third-Order Intercept                                       | V <sub>OUT</sub> = 1 V p-p, f = 10 MHz                                                                                                                                                                                                                      |     | 43                |     | dBm  |

|                                                                    | V <sub>OUT</sub> = 2 V p-p, f = 10 MHz                                                                                                                                                                                                                      |     | 40                |     | dBm  |

|                                                                    | $V_{OUT} = 1 V p-p, f = 45 MHz$                                                                                                                                                                                                                             |     | 28                |     | dBm  |

|                                                                    | $V_{OUT} = 2 V p-p, f = 45 MHz$                                                                                                                                                                                                                             |     | 28                |     | dBm  |

| Two-Tone Intermodulation Distortion (IMD3), $R_{LOAD} = 50 \Omega$ | $V_{OUT} = 1 \text{ V p-p}, f_1 = 10 \text{ MHz}, f_2 = 11 \text{ MHz}$                                                                                                                                                                                     |     | -69               |     | dBc  |

|                                                                    | $V_{OUT} = 2 V p-p, f_1 = 10 MHz, f_2 = 11 MHz$                                                                                                                                                                                                             |     | -72               |     | dBc  |

|                                                                    | $V_{OUT} = 1 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                                                                                                                                             |     | -51               |     | dBc  |

|                                                                    | $V_{OUT} = 2 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                                                                                                                                             | 1   | -48               |     | dBc  |

Rev. A | Page 3 of 32

| arameter                                             | Conditions                                                                                                                        | Min | Тур                      | Max | Unit       |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|--------------------------|-----|------------|

| Output Third-Order Intercept, $R_{LOAD} = 50 \Omega$ | V <sub>OUT</sub> = 1 V p-p, f = 10 MHz                                                                                            |     | 33                       |     | dBm        |

|                                                      | V <sub>OUT</sub> = 2 V p-p, f = 10 MHz                                                                                            |     | 40                       |     | dBm        |

|                                                      | V <sub>OUT</sub> = 1 V p-p, f = 45 MHz                                                                                            |     | 23                       |     | dBm        |

|                                                      | $V_{OUT} = 2 V p-p, f = 45 MHz$                                                                                                   |     | 28                       |     | dBm        |

| REAMPLFIER AND VGA—GENERAL PARAMETERS                |                                                                                                                                   |     |                          |     |            |

| –3 dB Small Signal Bandwidth                         | $V_{OUT} = 10 \text{ mV p-p}$ , gain code = 0110                                                                                  |     | 230                      |     | MHz        |

| –3 dB Large Signal Bandwidth                         | V <sub>OUT</sub> = 1 V p-p, gain code = 0110                                                                                      |     | 165                      |     | MHz        |

|                                                      | $V_{OUT} = 2 V p-p$ , gain code = 0110                                                                                            |     | 135                      |     | MHz        |

| Slew Rate                                            | $V_{OUT} = 1 V p-p$ , gain code = 0110                                                                                            |     | 330                      |     | V/µs       |

|                                                      | V <sub>OUT</sub> = 1.6 V p-p, gain code = 0110                                                                                    |     | 335                      |     | V/µs       |

| Input Voltage Noise                                  | f = 10 MHz (shorted input)                                                                                                        |     | 2.4                      |     | nV/√l      |

|                                                      | f = 10 MHz (input open)                                                                                                           |     | 6.2                      |     | nV/√       |

| Noise Figure                                         | Max gain (gain code = 1011), $R_s = 50 \Omega$ , unterminated                                                                     |     | 10.2                     |     | dB         |

|                                                      | Max gain (gain code = 1011), $R_{s}$ = 50 $\Omega,$ shunt terminated with 50 $\Omega$                                             |     | 15.5                     |     | dB         |

| Output-Referred Noise                                | Max gain (gain code = 1011), gain = 24 dB (input short)                                                                           |     | 38                       |     | nV/√l      |

|                                                      | Max gain (gain code = 1011), gain = 24 dB (input open)                                                                            |     | 98.1                     |     | nV/√       |

|                                                      | Min gain (gain code = 0001), gain = $-6 \text{ dB}$                                                                               |     | 25                       |     | nV/√       |

| Output Impedance                                     | DC to 10 MHz                                                                                                                      |     | ≤3                       |     | Ω          |

| Output Signal Range (per Pin)                        | $R_{LOAD} \ge 500 \Omega$                                                                                                         |     | $V_{\text{MDO}} \pm 0.7$ |     | V          |

|                                                      | $V_s = +5 V$                                                                                                                      |     | $V_{MDO} \pm 1.4$        |     | V          |

|                                                      | $V_{S} = \pm 5 V$                                                                                                                 |     | ±3.6                     |     | V          |

| Input Signal Range                                   | Preamplifier input                                                                                                                |     | $V_{\text{MDO}} \pm 0.3$ |     | V          |

| Output Offset Voltage                                | Max gain (gain code = 1011), gain = 24 dB, 3 $\sigma$ limits                                                                      | -50 | ±20                      | +50 | mV         |

| REAMPLIFIER AND VGA—DYNAMIC PERFORMANCE              |                                                                                                                                   |     |                          |     |            |

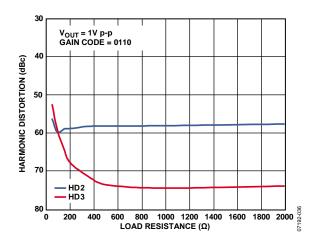

| Harmonic Distortion                                  | Gain code = 0110, gain = 9 dB, $V_{OUT}$ = 1 V p-p                                                                                |     | 00                       |     | al D a     |

| HD2<br>HD3                                           | f = 1 MHz                                                                                                                         |     | -90<br>-87               |     | dBc<br>dBc |

| HD2                                                  | f = 10 MHz                                                                                                                        |     |                          |     | dBc        |

| HD2<br>HD3                                           | I = I0 MHZ                                                                                                                        |     | -75<br>-58               |     | dBc        |

| Harmonic Distortion                                  | Gain code = 1011, gain = 24 dB, $V_{OUT}$ = 2 V p-p                                                                               |     | -38                      |     | ubc        |

| HD2                                                  | f = 1  MHz                                                                                                                        |     | -94                      |     | dBc        |

| HD3                                                  |                                                                                                                                   |     | -90                      |     | dBc        |

| HD2                                                  | f = 10 MHz                                                                                                                        |     | -61                      |     | dBc        |

| HD3                                                  |                                                                                                                                   |     | -84                      |     | dBc        |

| Input 1 dB Compression Point                         | Min gain (gain code = 0001), gain = -6 dB<br>(preamplifier limited)                                                               |     | 1.9                      |     | dBm        |

|                                                      | Max gain (gain code = 1011), gain = 24 dB<br>(VGA limited)                                                                        |     | -9.2                     |     | dBm        |

| MTPR (In-Band)                                       | $V_{OUT} = 1.4 V p-p-max$ , 10 tones, 2 MHz to 22 MHz with missing tone at 12 MHz (spacing 2 MHz), gain code = 1011, gain = 24 dB |     | -68                      |     | dBc        |

|                                                      | $V_{OUT}$ = 1.4 V p-p-max, 16 tones, 2 MHz to 38 MHz with missing tones at 10 MHz, 20 MHz, 30 MHz, and 40 MHz (spacing 2 MHz)     |     | -61                      |     | dBc        |

| Two-Tone Intermodulation Distortion (IMD3)           | Gain code = 1011, gain = 24 dB                                                                                                    |     |                          |     |            |

|                                                      | $V_{OUT} = 1 V p-p, f_1 = 10 MHz, f_2 = 11 MHz$                                                                                   |     | -92                      |     | dBc        |

|                                                      | $V_{OUT} = 2 V p-p, f_1 = 10 MHz, f_2 = 11 MHz$                                                                                   |     | -77                      |     | dBc        |

|                                                      | $V_{OUT} = 1 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                   |     | -50                      |     | dBc        |

|                                                      | $V_{OUT} = 2 V p-p, f_1 = 45 MHz, f_2 = 46 MHz$                                                                                   |     | -36                      |     | dBc        |

| Output Third-Order Intercept                         | Gain code = 1011, gain = 24 dB                                                                                                    |     |                          |     |            |

|                                                      | V <sub>OUT</sub> = 1 V p-p, f = 10 MHz                                                                                            |     | 44                       |     | dBm        |

|                                                      | $V_{OUT} = 2 V p-p, f = 10 MHz$                                                                                                   |     | 43                       |     | dBm        |

|                                                      | $V_{OUT} = 1 V p-p, f = 45 MHz$                                                                                                   |     | 27                       |     | dBm        |

|                                                      | $V_{OUT} = 2 V p-p, f = 45 MHz$                                                                                                   |     | 22                       |     | dBm        |

| Overload Recovery                                    | Max gain (gain code = 1011), gain = 24 dB, $V_{IN} = 50$ mV p-p to 500 mV p-p                                                     |     | 50                       |     | ns         |

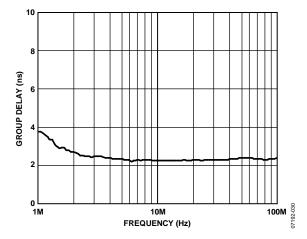

| Group Delay Variation                                | 1 MHz < f < 50 MHz, full gain range                                                                                               |     | 2                        |     | ns         |

| Parameter                         | Conditions                                                                                     | Min   | Тур   | Max  | Unit |

|-----------------------------------|------------------------------------------------------------------------------------------------|-------|-------|------|------|

| ACCURACY                          |                                                                                                |       |       |      |      |

| Absolute Gain Error               | -0.5                                                                                           | ±0.15 | +0.5  | dB   |      |

| Gain Law Conformance (DNL)        | Differential gain error code-to-code                                                           | -0.3  | ±0.15 | +0.3 | dB   |

| GAIN CONTROL                      |                                                                                                |       |       |      |      |

| Gain Step per Code                |                                                                                                |       | 3.0   |      | dB   |

| Gain Range                        | Default = -6dB to +24 dB                                                                       |       | 30    |      | dB   |

| Response Time                     | 30 dB gain change (gain code stepped from 0001 to 1011)                                        |       | 50    |      | ns   |

| LOGIC INTERFACES                  |                                                                                                |       |       |      |      |

| High Level Input Voltage          |                                                                                                | 1.4   |       | Vs   | V    |

| Low Level Input Voltage           |                                                                                                | 0     |       | 0.8  | V    |

| Logic Input Bias Current          | Logic high, $V_{LOGIC} = 3.3 V$                                                                |       | 0.2   |      | μA   |

|                                   | Logic low                                                                                      |       | 18    |      | nA   |

| POWER SUPPLY                      |                                                                                                |       |       |      |      |

| Supply Voltage                    | Single supply                                                                                  | 3.3   |       | 10   | v    |

|                                   | Dual supply                                                                                    | ±3.3  |       | ±5   | V    |

| Quiescent Current                 | Full chip enabled (TXEN = 1, ENBL = 1, gain code = 0001)                                       |       | 28.3  |      | mA   |

|                                   | TXEN = 0, ENBL = 1, gain code = $0001$ , driver off, DGA on                                    |       | 19.1  |      | mA   |

|                                   | TXEN = 1, ENBL = 1, gain code = 0000, driver on, DGA off                                       |       | 10.8  |      | mA   |

|                                   | Chip disabled (TXEN = 0, ENBL = 0, gain code = $0000$ )                                        |       | 35    |      | μA   |

|                                   | $V_s = \pm 5$ V, no signal                                                                     |       | 34.2  |      | mA   |

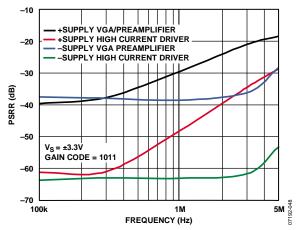

| PSRR                              | Max gain (gain code = 1011), gain = 24 dB, 1 MHz                                               |       | -30   |      | dB   |

|                                   | Driver amplifier, 1 MHz                                                                        |       | -48   |      | dB   |

| Power Dissipation                 | No signal                                                                                      |       | 93    |      | mW   |

|                                   | No signal, $V_{POS} - V_{NEG} = 10 V$                                                          |       | 342   |      | mW   |

| ENABLE TIMES                      |                                                                                                |       |       |      |      |

| Chip Enable Time                  | Bias only, TXEN = 0, gain code = 0000, ENBL = 0 to 1                                           |       | 0.4   |      | μs   |

|                                   | All at once, TXEN = 0 to 1, gain code = 0000 to 0001,<br>ENBL = 0 to 1                         |       | 0.3   |      | μs   |

| Preamplifier and DGA Enable Time  | ENBL = 1, TXEN = 0, gain code = 0000 to 0001                                                   |       | 0.3   |      | μs   |

| Driver Enable Time                | ENBL = 1, gain code = 0001, TXEN stepped from 0 to 1                                           | 0.2   |       |      | μs   |

| DISABLE TIMES                     |                                                                                                |       |       |      |      |

| Chip Disable Time                 | TXEN = 1 to 0, gain code = 0001 to 0000,<br>ENBL = 1 to 0, $I_{SUPPLY} = 100 \ \mu A$          |       | 20    |      | μs   |

|                                   | All at once, TXEN = 1 to 0, gain code = 0001 to 0000, ENBL = 1 to 0, $I_{SUPPLY}$ = 35 $\mu$ A |       | 50    |      | μs   |

| Preamplifier and DGA Disable Time | ENBL = 1, TXEN = 0, gain code = 0001 to 0000                                                   |       | 0.4   |      | μs   |

| Driver Disable Time               | ENBL = 1, gain code = 0000, TXEN = 1 to 0                                                      |       | 2.2   |      | μs   |

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                       | Rating          |

|-------------------------------------------------|-----------------|

| Voltage                                         |                 |

| Supply Voltage (VPOS, VNEG)                     | ±6 V            |

| Input Voltage (INxx, PRAI,<br>FDBK, VMDI, VOCM) | VPOS, VNEG      |

| Logic Voltages                                  | VPOS, ground    |

| Temperature                                     |                 |

| Operating Temperature Range                     | -40°C to +105°C |

| Storage Temperature Range                       | –65°C to +150°C |

| Lead Temperature (Soldering, 60 sec)            | 300°C           |

| Thermal Data <sup>1</sup>                       |                 |

| Maximum Junction Temperature                    | 125°C           |

| $\Theta_{JA}$                                   | 47.3°C/W        |

| θ <sub>JC</sub>                                 | 6.9°C/W         |

| $\Theta_{JB}$                                   | 28.6°C/W        |

| Ψ <sub>JT</sub>                                 | 0.6°C/W         |

| $\Psi_{JB}$                                     | 27.4°C/W        |

<sup>1</sup> Thermal data at zero airflow with exposed pad soldered to four-layer JEDEC board with vias per JESD51-5.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

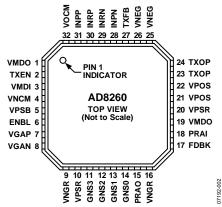

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

NOTES

1. THE EXPOSED PAD IS NOT CONNECTED INTERNALLY. FOR INCREASED RELIABILITY OF THE SOLDER JOINTS AND MAXIMUM THERMAL CAPABILITY, IT IS RECOMMENDED THAT THE PAD BE SOLDERED TO THE GROUND PLANE. THE GROUND PLANE PATTERN SHOULD INCLUDE A PATTERN OF VIAS TO INNER LAYERS.

Figure 2. Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin No.             | Mnemonic | Description                                                                                                                                                                                                                                                                        |

|---------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 19 <sup>1</sup>  | VMDO     | VMID Buffer Output. Requires robust ac decoupling with a capacitance of 0.1 µF capacitor or greater.                                                                                                                                                                               |

| 2                   | TXEN     | Driver Enable. Logic threshold = $1.1 \text{ V}$ with $\pm 0.2 \text{ V}$ hysteresis.                                                                                                                                                                                              |

| 3                   | VMDI     | VMID Input Voltage. Normally decoupled with a 0.1 μF capacitor. When pulled to VNCM, the VMID buffer shuts down. This can be useful when using the part with dual supplies or when an external midpoint generator is used.                                                         |

| 4                   | VNCM     | Negative Supply for Bias Cell, VMID Cell, and Logic Inputs. (Ground this pin in applications.)                                                                                                                                                                                     |

| 5                   | VPSB     | Positive Supply for Bias Cell and VMID Cell.                                                                                                                                                                                                                                       |

| 6                   | ENBL     | Enable. Logic threshold = 1.1 V. When low, the AD8260 is disabled and the supply current is 35 μA when TXEN and all GNSx pins are also low.                                                                                                                                        |

| 7                   | VGAP     | Positive VGA Output (Needs to Be Ac-Coupled for Single Supply).                                                                                                                                                                                                                    |

| 8                   | VGAN     | Negative VGA Output (Needs to Be Ac-Coupled for Single Supply).                                                                                                                                                                                                                    |

| 9, 16 <sup>1</sup>  | VNGR     | Negative Supply for Preamplifier and DGA (Set to –VPOS for Dual Supply; GND for Single Supply).                                                                                                                                                                                    |

| 10, 20 <sup>1</sup> | VPSR     | Positive Supply for Preamplifier, DGA, and GNSx Logic Decoder.                                                                                                                                                                                                                     |

| 11                  | GNS3     | MSB for Gain Control. Logic threshold = 1.1 V.                                                                                                                                                                                                                                     |

| 12                  | GNS2     | Gain Control Bit. Logic threshold = 1.1 V.                                                                                                                                                                                                                                         |

| 13                  | GNS1     | Gain Control Bit. Logic threshold = 1.1 V.                                                                                                                                                                                                                                         |

| 14                  | GNS0     | LSB for Gain Control. Logic threshold = 1.1 V.                                                                                                                                                                                                                                     |

| 15                  | PRAO     | Preamplifier Output.                                                                                                                                                                                                                                                               |

| 17                  | FDBK     | Negative Input of Preamplifier.                                                                                                                                                                                                                                                    |

| 18                  | PRAI     | Positive Input of Preamplifier.                                                                                                                                                                                                                                                    |

| 21, 22 <sup>1</sup> | VPOS     | Positive Supply for Driver Amplifier.                                                                                                                                                                                                                                              |

| 23, 24 <sup>1</sup> | ТХОР     | Driver Output.                                                                                                                                                                                                                                                                     |

| 25, 26 <sup>1</sup> | VNEG     | Negative Supply for Driver Amplifier (Set to –VPOS for Dual Supply; GND for Single Supply).                                                                                                                                                                                        |

| 27                  | TXFB     | Feedback for Driver Amplifier.                                                                                                                                                                                                                                                     |

| 28                  | INPN     | Negative Driver Amplifier Input.                                                                                                                                                                                                                                                   |

| 29                  | INRN     | Negative Gain Resistor Input for Driver Amplifier.                                                                                                                                                                                                                                 |

| 30                  | INRP     | Positive Gain Resistor Input for Driver Amplifier.                                                                                                                                                                                                                                 |

| 31                  | INPP     | Positive Driver Amplifier Input.                                                                                                                                                                                                                                                   |

| 32                  | VOCM     | Output Common Mode Pin. Normally connected to Pin VMDO.                                                                                                                                                                                                                            |

|                     | EPAD     | Exposed Pad. The exposed pad is not connected internally. For increased reliability of the solder joints and maximum thermal capability it is recommended that the pad be soldered to the ground plane. The ground plane pattern should include a pattern of vias to inner layers. |

<sup>1</sup> Pins with the same name are connected internally.

### **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_s$  (supply voltage) = 3.3 V,  $T_A = 25^{\circ}$ C,  $C_L = 5$  pF, f = 10 MHz, preamplifier gain = 2×,  $R_{FB1}$  and  $R_{FB2}$  of the preamplifier = 100  $\Omega$ ,  $R_{LOAD}$  of the driver amplifier = 500  $\Omega$ ,  $T_x$  and  $R_x$  enabled, unless otherwise specified.

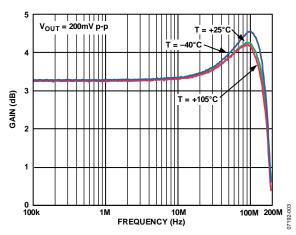

Figure 3. Small-Signal Frequency Response at Three Temperatures of the High Current Driver—See Figure 51

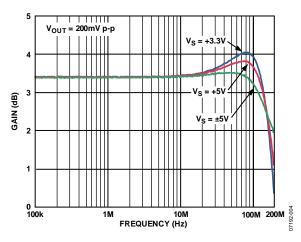

Figure 4. Small-Signal Frequency Response of the High Current Driver for Three Supply Voltages—See Figure 51

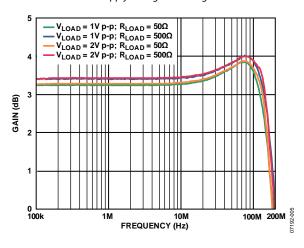

Figure 5. Large-Signal Frequency Response of the High Current Driver for Two Values of Output Voltage and Two Values of Load Resistance—See Figure 51

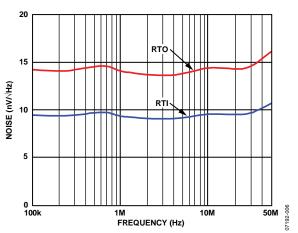

Figure 6. Input-Referred and Output-Referred Noise of the High Current Driver—See Figure 52

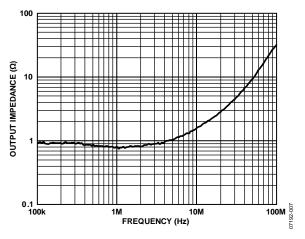

Figure 7. Output Impedance of the High Current Driver See Figure 53

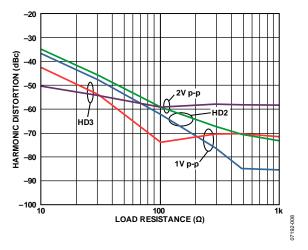

Figure 8. Harmonic Distortion (HD2, HD3) vs. Load Resistance for the High Current Driver—See Figure 54

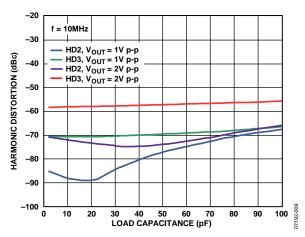

Figure 9. Harmonic Distortion (HD2, HD3) vs. Load Capacitance at Two Values of Output Voltage for the High Current Driver—See Figure 54

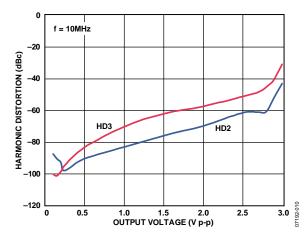

Figure 10. Harmonic Distortion (HD2, HD3) vs. Output Voltage for the High Current Driver—See Figure 54

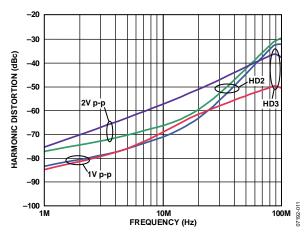

Figure 11. Harmonic Distortion (HD2, HD3) vs. Frequency of the High Current Driver at Two Values of Output Voltage—See Figure 54

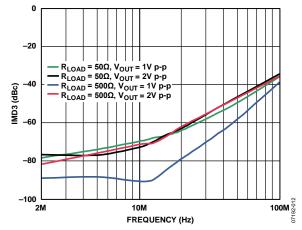

Figure 12. IMD3 vs. Frequency for Two Values of Output Voltage and Two Values of Load Resistance for the High Current Driver—See Figure 55

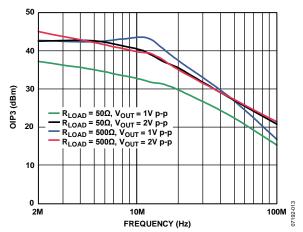

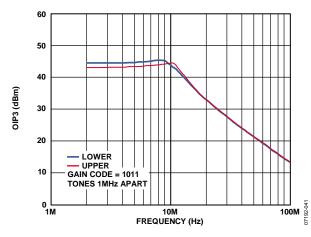

Figure 13. Third-Order Intercept (OIP3) vs. Frequency for the High Current Driver See Figure 55

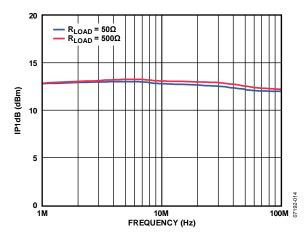

Figure 14. Input-Referred 1 dB Compression (IP1dB) vs. Frequency for Two Values of Load Resistance for the High Current Driver

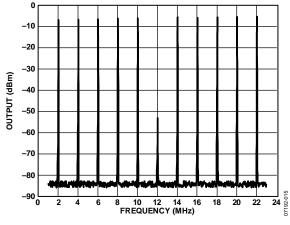

*Figure 15. Missing Tone Power Ratio for the High Current Driver*

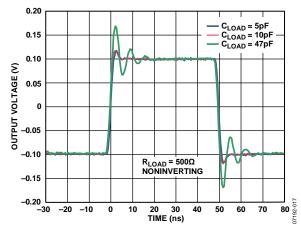

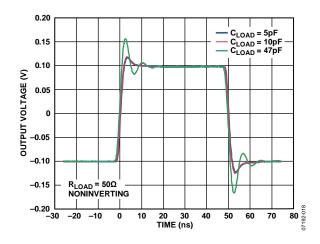

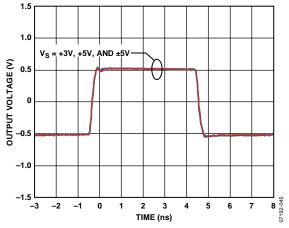

Figure 16. Small-Signal Pulse Response of the High Current Driver for Various Values of Load Resistance,  $R_{LOAD}$ —See Figure 56

Figure 17. Small-Signal Pulse Response of the High Current Driver for Various Values of Load Capacitance,  $C_{LOAD}$ , and  $R_{LOAD} = 500 \,\Omega$ —See Figure 56

Figure 18. Small-Signal Pulse Response of the High Current Driver for Various Values of Load Capacitance,  $C_{LOAD}$ , and 50  $\Omega$  Load—See Figure 56

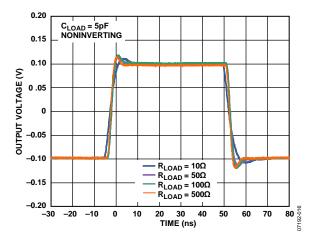

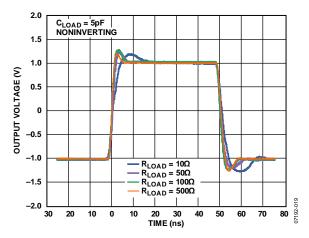

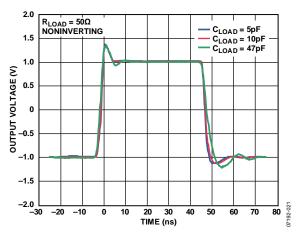

Figure 19. Large-Signal Pulse Response of the High Current Driver for Various Values of Load Resistance, R<sub>LOAD</sub>—See Figure 56

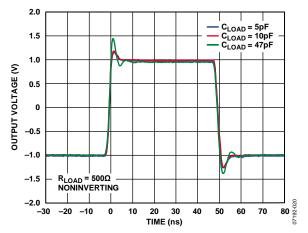

Figure 20. Large-Signal Pulse Response of the High Current Driver for Various Values of Load Capacitance,  $C_{LOAD}$ , and  $R_{LOAD} = 500 \Omega$ —See Figure 56

Figure 21. Large-Signal Pulse Response of the High Current Driver for Various Values of Load Capacitance,  $C_{LOAD'}$  and 50  $\Omega$  Load—See Figure 56

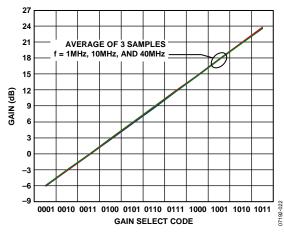

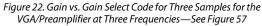

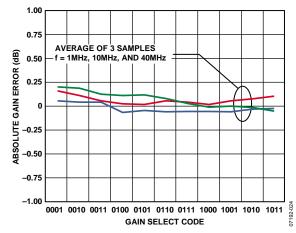

Figure 23. Gain Step vs. Gain Select Code for Three Samples for the VGA/Preamplifier at Three Frequencies—See Figure 57

Figure 24. Absolute Gain Error vs. Gain Select Code for Three Samples for the VGA/Preamplifier at Three Frequencies Normalized to 1 MHz and Code 0110 See Figure 57

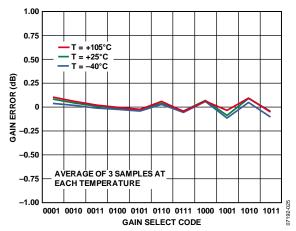

Figure 25. Gain Error vs. Gain Select Code at Three Temperatures for the VGA/Preamplifier—See Figure 57

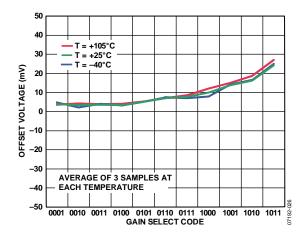

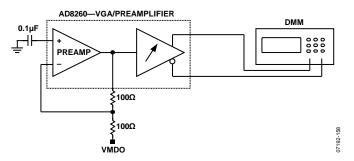

Figure 26. Output Offset Voltage vs. Gain Select Code at Three Temperatures for the VGA/Preamplifier—See Figure 58

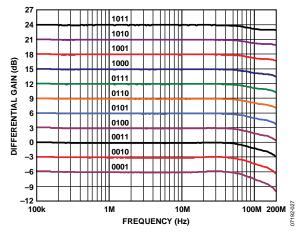

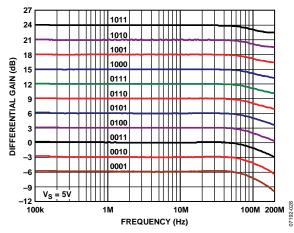

Figure 27. Frequency Response for a Supply Voltage (V<sub>5</sub>) of 3.3 V for all Codes of the VGA/Preamplifier—See Figure 59

Figure 28. Frequency Response for a Supply Voltage (V<sub>s</sub>) of 5 V for All Codes for the VGA/Preamplifier—See Figure 59

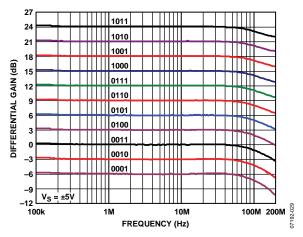

Figure 29. Frequency Response for a Dual Supply ( $V_S$ ) = ±5 V for All Codes for the VGA/Preamplifier—See Figure 59

Figure 30. Group Delay vs. Frequency for the VGA/Preamplifier See Figure 59

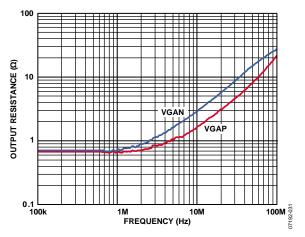

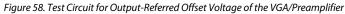

Figure 31. Output Resistance vs. Frequency for the VGA/Preamplifier See Figure 60

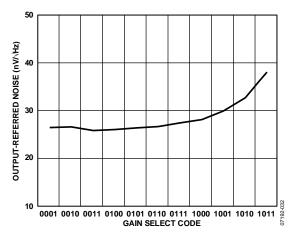

Figure 32. Output-Referred Noise vs. Gain Select Code for the VGA/Preamplifier—See Figure 61

Figure 33. Output-Referred Noise vs. Frequency for the VGA/Preamplifier at Maximum Gain—See Figure 61

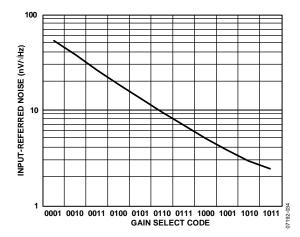

Figure 34. Input-Referred Noise vs. Gain Select Code for the VGA/Preamplifier See Figure 61

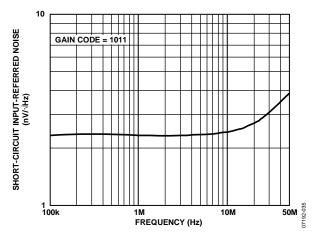

Figure 35. Short-Circuit Input Noise vs. Frequency for the VGA/Preamplifier See Figure 61

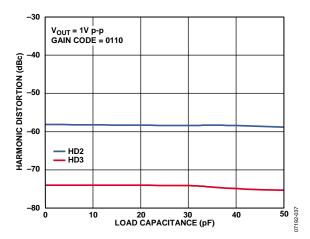

Figure 36. Harmonic Distortion (HD2, HD3) vs. Load Resistance for the VGA/Preamplifier—See Figure 62

Figure 37. Harmonic Distortion (HD2, HD3) vs. Load Capacitance for the VGA/Preamplifier—See Figure 62

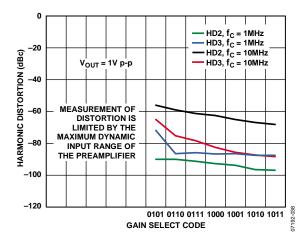

Figure 38. Harmonic Distortion (HD2, HD3) vs. Gain Select Code at 1 MHz and 10 MHz for the VGA/Preamplifier—See Figure 62

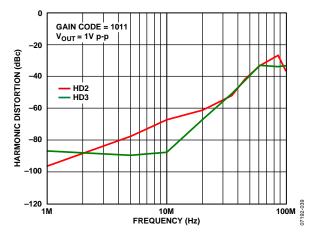

Figure 39. Harmonic Distortion (HD2, HD3) vs. Frequency for the VGA/Preamplifier—See Figure 62

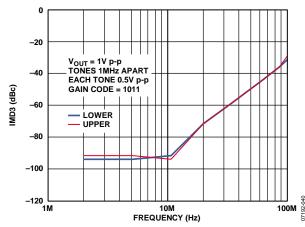

Figure 40. Third-Order Intermodulation Distortion (IMD3) vs. Frequency for the VGA/Preamplifier

Figure 41. OIP3 vs. Frequency for the VGA/Preamplifier

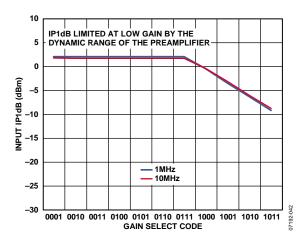

Figure 42. Input 1 dB Compression (IP1dB) vs. Gain Select Code at 1 MHz and 10 MHz for the VGA/Preamplifier

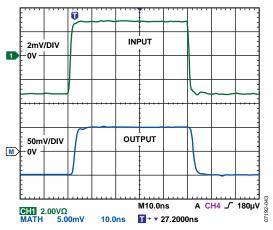

Figure 43. Small-Signal Pulse Response for the VGA/Preamplifier

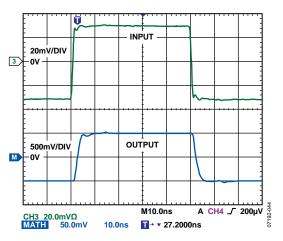

Figure 44. Large-Signal Pulse Response for the VGA/Preamplifier

Figure 45. Large-Signal Pulse Response for Various Values of Supply Voltage for the VGA/Preamplifier

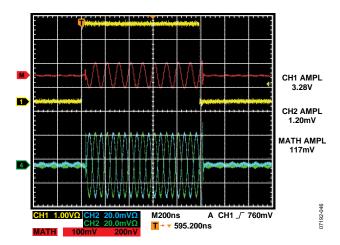

Figure 46. Gain Response for the VGA/Preamplifier, Yellow: Gain Code Select, Red: VGA Differential Output, Blue/Green: VGAP and VGAN

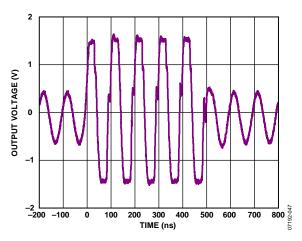

*Figure 47. Overdrive Recovery of the VGA/Preamplifier—Gain Code = 1011*

Figure 48. PSRR vs. Frequency for Dual Supplies for the High Current Driver and the VGA/Preamplifier

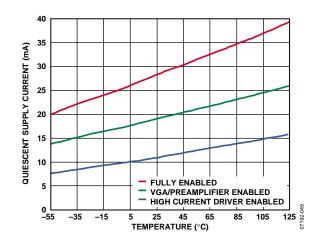

Figure 49. Quiescent Supply Current vs. Temperature for Three Operating States

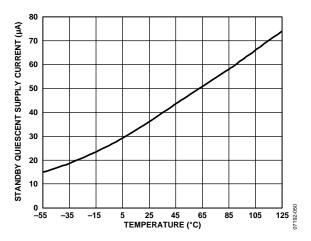

Figure 50. Standby Quiescent Supply Current vs. Temperature

### **TEST CIRCUITS**

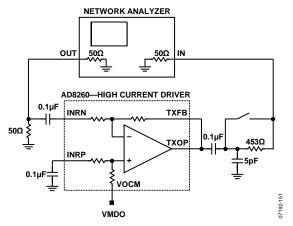

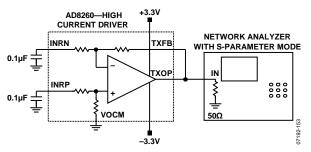

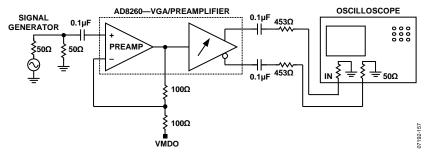

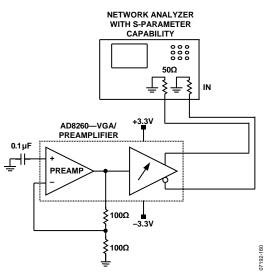

Figure 51. Test Circuit for Frequency Response of the High Current Driver

Figure 52. Test Circuit for Input-Referred and Output-Referred Noise of the High Current Driver

Figure 53. Test Circuit for Output Impedance of the High Current Driver

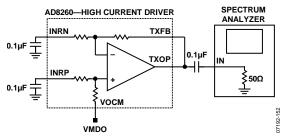

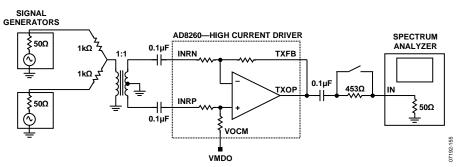

Figure 54. Test Circuit for Harmonic Distortion of the High Current Driver

Rev. A | Page 16 of 32

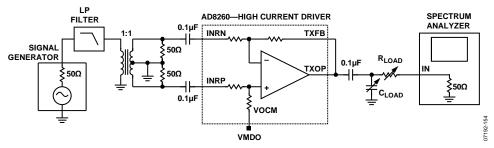

Figure 55. Test Circuit for IMD3 and OIP3 of the High Current Driver

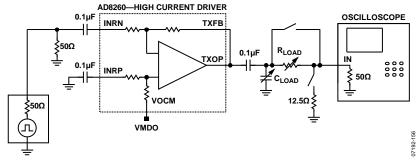

Figure 56. Test Circuit for Pulse Response of the High Current Driver

Figure 57. Test Circuit for Gain Step Size and Error of the VGA/Preamplifier

Figure 59. Test Circuit for Frequency Response and Group Delay of the VGA/Preamplifier

Figure 60. Test Circuit for Output Resistance of the VGA/Preamplifier

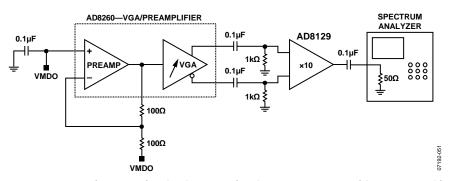

Figure 61. Test Circuit for Input-Referred and Output-Referred Noise Measurements of the VGA/Preamplifier

Rev. A | Page 18 of 32

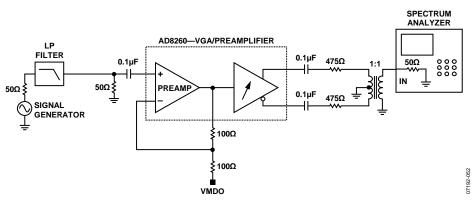

Figure 62. Test Circuit for Harmonic Distortion Measurements of the VGA/Preamplifier

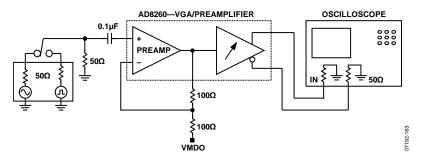

Figure 63. Test Circuit for IP1dB, Pulse Response, Overdrive Recovery, and Gain Response of the VGA/Preamplifier

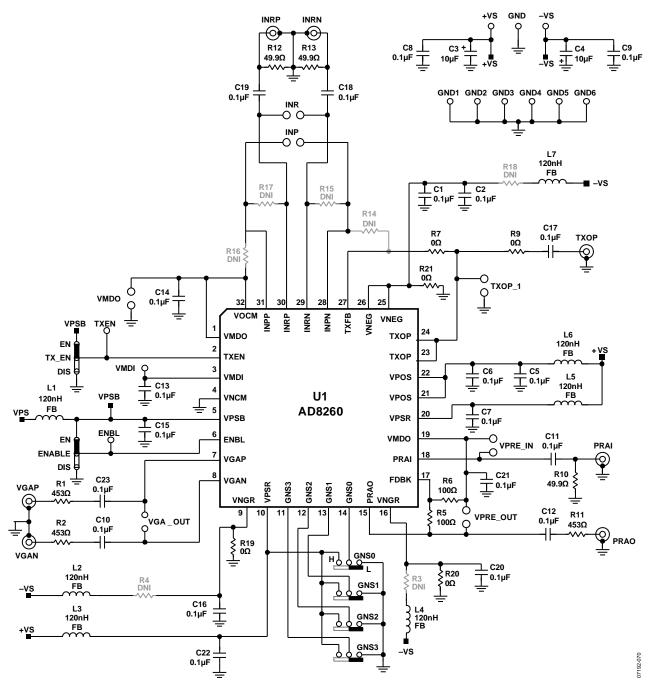

### THEORY OF OPERATION overview

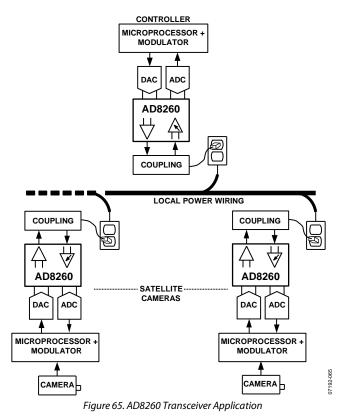

The AD8260 is a self-contained transceiver intended for analog communications using a power line as the media. Operating on supplies as low as 3.3 V, it includes a high current driver usable as a transmitter and a low noise digitally programmable variable gain amplifier (DGA), usable as a receiver (see Figure 64). An uncommitted current-feedback high frequency op amp acts as a preamplifier and interface to the DGA and is user configured for gains greater than 6 dB. Combined, the VGA and preamplifier are usable at high signal levels from dc to 100 MHz, with a small-signal –3 dB bandwidth of 230 MHz. To implement a high current-output VGA, the VGA output can be connected to the driver-amplifier differential input.

The small-signal -3 dB bandwidth of the driver amplifier is 195 MHz and the large-signal bandwidth is >115 MHz, even when driving a 50  $\Omega$  load.

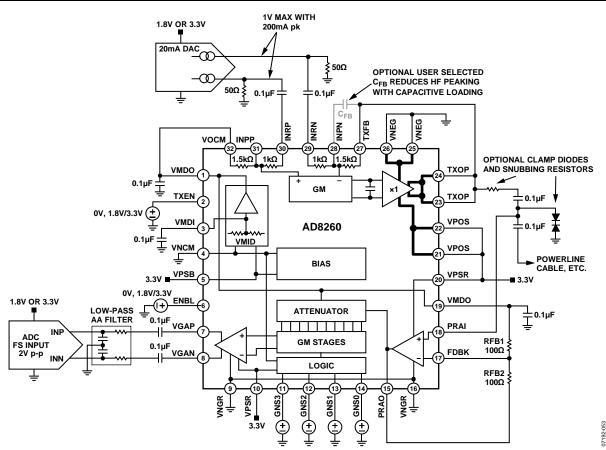

The device is fabricated on the Analog Devices, Inc., high speed (eXtra Fast Complementary Bipolar) XFCB process. The preamplifier and DGA feature low dc offset voltage, and a nominal gain range of -6 dB to +24 dB, a 30 dB gain span, and a differential output for ADC driving. The power consumption is 93 mW with a single 3.3 V supply. The supply current is typically about 28 mA when all circuits in the device are active. During normal usage, either the driver amplifier is on or the preamplifier and DGA are on and, therefore, the supply current in general is less than 28 mA. The gain of the AD8260 VGA is programmed via a 4-bit parallel interface. Figure 64 shows the circuit block diagram and basic application connections, and illustrates the envisioned external DAC, ADC, and power-line bus interface connections. The diagram shows the connections for single 3.3 V supply operation; if a dual supply is available, the VMID generator can be shut down and Pin VMDI, Pin VMDO, and Pin VOCM need to be grounded. Note that Pin VNCM functions as the negative supply for the bias and VMID cells, plus the logic interfaces, and should always be tied to ground.

For optimal dynamic range, it is important that the inputs and outputs to both the driver amplifier and the preamplifier and the DGA output amplifier be ac-coupled in a single-supply application. In Figure 64, the DAC and ADC are presumed to operate on a 1.8 V or 3.3 V supply with a corresponding limited output and input swing. The DAC outputs are currents that point down and generate a voltage in the 50  $\Omega$  resistors that are connected to ground. The maximum voltage with a peak DAC output current of 15 mA is 0.75 V; if a DAC with a 20 mA peak current is used, then the maximum voltage is 1 V per side for a differential input signal of 2 V p-p.

The driver amplifier supports a 3 V p-p output swing on a 3.3 V supply. Because of its gain of 1.5, the maximum input swing is 2 V p-p. The corresponding maximum output swing for the DGA is 2.4 V p-p differential; the input to the preamplifier can be a maximum of 0.6 V p-p.

Figure 64. Block Diagram and Basic Application Connections

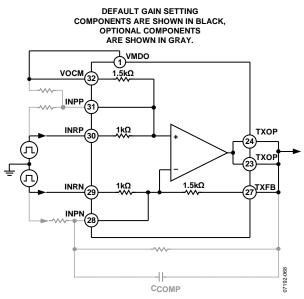

### **HIGH CURRENT DRIVER AMPLIFIER**

The high current driver amplifier can deliver very large output currents suitable for driving complex impedances, such as a power line, a 50  $\Omega$  line, or a coaxial cable. The input of the amplifier is fully differential and intended to be driven by a differential current-output DAC, as shown in Figure 64. The differential input signal is amplified by 1.5× and produces a 2.25 V p-p single-ended output signal from a 1.5 V p-p input signal. A DAC with 15 mA maximum output current into a 50  $\Omega$  load provides 1.5 V p-p of input voltage and results in 2.25 V p-p at the output. A DAC whose output is 20 mA produces an output swing of 3 V p-p (neglecting a small gain error when driving the parallel combination of the 50  $\Omega$  load-resistor and the internal 1 k $\Omega$  gain resistor of the AD8260).

For a 3.3 V supply rail, the maximum limit of the output voltage is 3 V p-p and distorts severely if exceeded. The recommended output for optimum distortion is 2 V p-p for a 3.3 V supply. Correspondingly, larger output swings are accommodated for higher supply voltages such as +5 V or  $\pm 5$  V. For optimum distortion, the input drive must be controlled such that the output swing is well within saturation levels established by the supply rail. The output swing can be reduced by using load resistors with values less than 50  $\Omega$  or by reducing the amplifier gain by connecting external resistors in parallel with the internal 1 k $\Omega$  and 1.5 k $\Omega$  resistors between Pin 27, Pin 28, and Pin 29, and between Pin 30, Pin 31, and Pin 32. Coincidently, noise is reduced because the gain setting resistors are the primary noise sources of the high current driver amplifier.

The output-referred noise is  $14 \text{ nV}/\sqrt{\text{Hz}}$ , of which  $11 \text{ nV}/\sqrt{\text{Hz}}$  is due to the gain setting resistors. Matching of the gain setting resistors is important for good common-mode rejection and the accuracy of the differential gain. If external resistors are used, their accuracy should be at least  $\pm 1\%$ . How low the resistor values can be is primarily determined by the quality of the ac ground at Pin VOCM; as the gain setting resistors decrease in value, the dynamic current increases, and the quality of the decoupling capacitors needs to increase correspondingly.

### PRECAUTIONS TO BE OBSERVED DURING HALF-DUPLEX OPERATION

During receive, when the high current driver-amplifier is disabled, its gain setting resistors provide a signal path from input to output. To prevent inadvertent DAC signals from being transmitted while receiving via the preamplifier and DGA, the DAC in Figure 64 must have no output signal.

During transmit, the preamplifier and VGA should be disabled through any of the nongain-setting codes (see Table 4).

### **VMID BUFFER**

The VMID buffer is a dc bias source that generates the voltage on Pin 1 and Pin 19, VMDO. Node VMDO cannot accommodate large dynamic currents and requires excellent ac decoupling to ground. A high quality  $0.1\mu F$  capacitor located as close as possible to Pin 1 and Pin 19 (see Figure 64) is normally sufficient to decouple the high values of current from Node VMDO.

When operating with dual power supplies, the buffer is disabled by connecting Pin VMDI, Pin VOCM, and Pin VMDO to ground. Because the logic decoder in the DGA (GNSx inputs) requires 3.3 V of headroom, the positive supply rails must be 3.3 V or greater whether single-ended or dual. If a dual supply is used, the negative rails are the same magnitude (opposite polarity) as the positive, that is, -3.3 V when VPOS, VPSB, and VPSR are +3.3 V.

#### PREAMPLIFIER

The AD8260 includes an uncommitted current feedback op amp to buffer the resistive attenuator of the DGA. External resistors are used to adjust the gain. The preamplifier is characterized with a noninverting gain of 6 dB (2×) and both gain resistor values of 100  $\Omega$ . The preamplifier gain can be increased using different gain ratios of R<sub>FB1</sub> and R<sub>FB2</sub>, trading off bandwidth and offset voltage. The sum of the values of R<sub>FB1</sub> and R<sub>FB2</sub> should be ≥200  $\Omega$  to maintain low distortion. R<sub>FB2</sub> should be ≥100  $\Omega$  because it and an internal compensation capacitor determine the -3 dB bandwidth of the amplifier. Smaller resistor values may compromise preamplifier stability.

Because the AD8260 is internally dc-coupled, larger preamplifier gains increase its offset voltage. The circuit contains an internal bias resistor and some offset compensation; however, if a lower value of offset voltage is required, it can be compensated by connecting a resistor between the FDBK pin and the supply voltage. If the offset is negative, the resistor value connects to the negative supply; otherwise, it connects to the positive supply.

For larger gains, the overall noise is reduced if a low value of  $R_{FB1}$  is selected. For values of  $R_{FB1} = 20~\Omega$  and  $R_{FB2} = 301~\Omega$ , the preamplifier gain is  $16\times$  (24.1 dB) and the input-referred noise is about 1.5 nV/ $\sqrt{Hz}$ . For this value of gain, the overall gain range increases by 18 dB so that the absolute gain range is 12 dB to 42 dB.

#### PREAMPLIFIER NOISE

The total input-referred voltage and current noise of the positive input of the preamplifier is about 2.4 nV/ $\sqrt{\text{Hz}}$  and 5 pA/ $\sqrt{\text{Hz}}$ , respectively. The DGA output referred noise is about 25 nV/ $\sqrt{\text{Hz}}$  at low gains and 39 nV/ $\sqrt{\text{Hz}}$  at the highest gain. The 25 nV/ $\sqrt{\text{Hz}}$  divided by the DGA fixed gain of 8× results in 3.12 nV/ $\sqrt{\text{Hz}}$  referred to the DGA input. Note that this value includes the noise of the DGA gain setting resistors as well. If this voltage is divided by the preamplifier gain of 2×, the DGA noise referred all the way to the preamplifier input is about 1.56 nV/ $\sqrt{\text{Hz}}$ . From this, it can be determined that the preamplifier, including the 100  $\Omega$  gain setting resistors, contributes about 1.8 nV/ $\sqrt{\text{Hz}}$ . The two 100  $\Omega$  resistors each contribute 1.29 nV/ $\sqrt{\text{Hz}}$  at the output of the preamplifier and 0.9 nV/ $\sqrt{\text{Hz}}$  referred to the input. With the gain resistor noise subtracted, the preamplifier noise alone is about 1.6 nV/ $\sqrt{\text{Hz}}$ .

Equation 1 shows the calculation that determines the outputreferred noise at maximum gain (24 dB or  $16\times$ ).

$$e_{n-out} = \sqrt{\left(e_{n,RS} \times A_t\right)^2 + \left(e_{n,PrA} \times A_t\right)^2 + \left(i_{n,PrA} \times R_S\right)^2 + \left(e_{n,RFB1} \times \frac{R_{FB2}}{R_{FB1}} \times A_{VGA}\right)^2 + \left(e_{n,RFB2} \times A_{VGA}\right)^2 + \left(e_{n,VGA} \times A_{VGA}\right)^2}$$

(1)

where:

$A_t$  is the total gain from preamplifier input to the VGA output.

$e_{n,RS}$  is the noise of the source resistance.

$e_{n,PrA}$  is the input-referred voltage noise of the preamplifier.

$i_{n,PrA}$  is the current noise of the preamplifier at the PRAI pin.

$R_{\rm s}$  is the source resistance.

$A_{VGA}$  is the VGA gain.

$e_{n,RFB1}$  is the voltage noise of R<sub>FB1</sub>.

$e_{n,RFB2}$  is the voltage noise of R<sub>FB2</sub>.

$e_{n,VGA}$  is the input-referred voltage noise of DGA (low gain output-referred noise divided by a fixed gain of 8×).

Assuming  $R_{S}$  = 0,  $R_{FB1}$  =  $R_{FB2}$  = 100  $\Omega,\,A_{t}$  = 16, and  $A_{VGA}$  = 8, the noise simplifies to

$$e_{n-out} = \sqrt{(1.6 \times 16)^2 + 2(1.29 \times 8)^2 + (3.12 \times 8)^2} =$$

39 nV /  $\sqrt{\text{Hz}}$  (2)

Taking this result and dividing by 16 gives the total input-referred noise with a short-circuited input as 2.4 nV/ $\sqrt{Hz}$ . When the preamplifier is used in the inverting configuration with the same  $R_{FB1} = R_{FB2} = 100 \ \Omega$  as in the previous example, then  $e_{n-out}$  does not change; however, because the gain decreases by 6 dB, the input-referred noise increases by a factor of 2 to about 4.8 nV/ $\sqrt{Hz}$ . The reason for this is that the noise gain to the DGA output of all the noise generators stays the same, but the preamp inverting gain is ( $-1\times$ ) compared to the ( $+2\times$ ) in the noninverting configuration. This doubles the input-referred noise.

### DGA

Referring to Figure 64, the signal path consists of a 30 dB programmable attenuator followed by a fixed gain amplifier of 18 dB for a total DGA gain range of -12 dB to +18 dB. With the preamplifier configured for a gain of 6 dB, the composite gain range is -6 dB to +24 dB from single-ended preamplifier input to differential DGA output.

The DGA plus preamplifier with 6 dB of gain implements the following gain law:

$$Gain(dB) = \left[3.01 \frac{dB}{Code} \times Code\right] + ICPT(dB)$$

where:

*ICPT* is the nominal intercept, –9 dB. *Code* values are decimal from 1 to 11.

The ICPT increases as the gain of the preamplifier is increased. For example, if the gain of the preamplifier is increased by 6 dB, then ICPT increases to -3 dB.

#### **GAIN CONTROL**

To change the gain, the desired four bits are programmed on Pin GNS0 to Pin GNS3, where GNS0 is the LSB (D0) and GNS3 is the MSB (D3). The states of Decimal 0 and Decimal 12 through Decimal 15 disable the preamplifier (PrA) and DGA (see Table 4).

| Tab | Table 4. Gain Control Logic Table |    |    |          |                                                                   |  |  |

|-----|-----------------------------------|----|----|----------|-------------------------------------------------------------------|--|--|

| D3  | D2                                | D1 | D0 | Function | Comments                                                          |  |  |

| 0   | 0                                 | 0  | 0  | Disable  | PrA and DGA powered down                                          |  |  |

| 0   | 0                                 | 0  | 1  | -6       | The numbers in the function                                       |  |  |

| 0   | 0                                 | 1  | 0  | -3       | column are composite gain                                         |  |  |

| 0   | 0                                 | 1  | 1  | 0        | values in dB for the correspond-                                  |  |  |

| 0   | 1                                 | 0  | 0  | 3        | ing code, when the preamplifier gain is 6 dB. For other values of |  |  |

| 0   | 1                                 | 0  | 1  | 6        | preamplifier gain, the gain is                                    |  |  |

| 0   | 1                                 | 1  | 0  | 9        | amended accordingly; for                                          |  |  |

| 0   | 1                                 | 1  | 1  | 12       | example, if the preamplifier                                      |  |  |

| 1   | 0                                 | 0  | 0  | 15       | gain is 12 dB, the gain values                                    |  |  |

| 1   | 0                                 | 0  | 1  | 18       | increase by 6 dB. When using the DGA single ended, the            |  |  |

| 1   | 0                                 | 1  | 0  | 21       | composite gain decreases                                          |  |  |

| 1   | 0                                 | 1  | 1  | 24       | by 6 dB.                                                          |  |  |

| 1   | 1                                 | 0  | 0  | Disable  | PrA and DGA powered down                                          |  |  |

| 1   | 1                                 | 0  | 1  | Disable  | PrA and DGA powered down                                          |  |  |

| 1   | 1                                 | 1  | 0  | Disable  | PrA and DGA powered down                                          |  |  |

| 1   | 1                                 | 1  | 1  | Disable  | PrA and DGA powered down                                          |  |  |

|     |                                   |    |    |          |                                                                   |  |  |

#### Table 4. Gain Control Logic Table

### **OUTPUT STAGE**

The gain of the voltage feedback output stage is fixed at 18 dB and inaccessible to the user. Otherwise, it is similar to the preamplifier in speed and bandwidth. The overall -3 dB bandwidth of the preamplifier and DGA combination is 230 MHz.

#### ATTENUATOR

The input resistance of the VGA attenuator is nominally 265  $\Omega$ . Assuming that the default preamplifier feedback network of R<sub>FB1</sub> and R<sub>FB2</sub> is 200  $\Omega$ , the effective preamplifier load is about 114  $\Omega$ . The attenuator is composed of ten 3.01 dB sections for a total attenuation span of -30.10 dB. Following the attenuator is a fixed gain amplifier with 18 dB (8×) gain. Because of this relatively low gain, the output offset is less than 20 mV over the operating temperature range; the offset is largest at maximum gain because the preamplifier offset is amplified. The VMDO pin defines the common-mode reference for the input and output. The voltage at VMID is half the supply voltage for single-supply operation and 0 V when dual supplies are used.

### SINGLE-SUPPLY OPERATION AND AC COUPLING

When operating the AD8260 from a single supply, there are two bias options for VMDO.

- Use an external low impedance midpoint reference at Pin VMDO and pull VMDI to VNCM to shut down the VMID buffer.

- Use the internal VMID buffer as shown in Figure 64.

In both cases, decoupling capacitors are needed on Pin VMDO to absorb the dynamic currents.

During single-supply operation, the preamplifier input is normally ac-coupled. An internal bias resistor (nominally 1 k  $\Omega$ ) connected between PRAI and VMDO provides bias to the preamplifier input pin. A 50  $\Omega$  resistor connected between Pin PRAI and Pin VMDO, in parallel with the internal 1 k $\Omega$ , serves as a termination resistor and at the same time reduces the offset; the result is a composite value of about 48  $\Omega$ . The VGA input is biased through the attenuator network and the voltage at Pin VMDO. When active, the VMID buffer provides the needed bias currents. When the buffer is disabled, an external voltage is required at Pin VMDO to provide the bias currents. For example, for a single 5 V application, a reference such as the ADR43 and a stable op amp provide an adequate 2.5 V VMDO source.

#### **POWER-UP/POWER-DOWN SEQUENCE**

For glitch-free power-up operation, the following power-up and power-down sequence is recommended:

- 1. Enable the bias by pulling the ENBL pin high. Maintain GNS0 to GNS3 and TXEN at ground.

- 2. It is assumed that after the part wakes up from sleep mode, the receive section (preamplifier and DGA) needs to be