# AN-1518

# LP38513S-1.8 Evaluation Board

National Semiconductor Application Note 1518 Don Jones August 2007

#### Introduction

This board is designed to enable the evaluation of the LP38513S-1.8 Voltage Regulator. Each board is assembled and tested in the factory. This evaluation board has the TO-263 5-lead package mounted.

#### **General Description**

The LP38513 is a linear regulator capable of supplying up to 3A of output current, and incorporates Enable and Error flag features.

The device has been designed to work with 10  $\mu$ F ceramic input and output capacitors. Footprints areas for  $C_{\rm IN}$  and  $C_{\rm OUT}$  will allow for a variety of sizes.

#### Operation

The input voltage, applied between  $V_{\rm IN}$  and GND, should be at least 2.25V, and no higher than 5.5V.

Loads can be connected to V<sub>OUT</sub> with reference to GND.

Test points are provided on the board to allow monitoring of  $V_{OUT}$ ,  $V_{IN}$ , Enable, and ERROR signals during operation If the application does not require the Enable function, the EN pin should be connected to directly to the adjacent  $V_{IN}$  pin.

#### **Enable Operation**

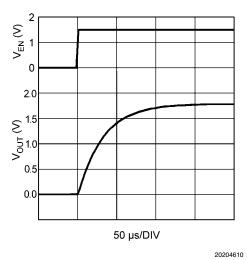

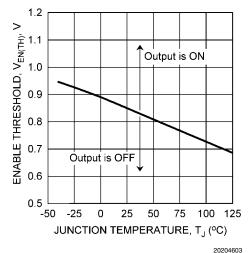

The Enable On/Off threshold is typically 850 mV, and has no hysteresis. The voltage signal must rise and fall cleanly, and promptly, through this threshold.

The Enable pin (EN) has no internal pull-up or pull-down to establish a default condition and, as a result, this pin must be terminated either actively or passively.

FIGURE 1. V<sub>OUT</sub> vs. V<sub>EN</sub>

If the Enable pin is driven from a single ended device (such as the collector of a discrete transistor) a pull-up resistor to  $V_{\rm IN}$ , or a pull-down resistor to ground, will be required for

proper operation. A 1 k $\Omega$  to 100 k $\Omega$  resistor can be used as the pull-up or pull-down resistor to establish default condition for the EN pin. The resistor value selected should be appropriate to swamp out any leakage in the external single ended device, as well as any stray capacitance.

If the Enable pin is driven from a source that actively pulls high and low (such as a CMOS rail to rail comparator output), the pull-up, or pull-down, resistor is not required.

If the application does not require the Enable function, the EN pin should be connected to directly to the adjacent  $V_{\text{IN}}$  pin.

The status of the Enable pin also affects the behavior of the ERROR Flag. While the Enable pin is high the regulator control loop will be active and the ERROR Flag will report the status of the output voltage. When the Enable pin is taken low the regulator control loop is shutdown, the output is turned off, and the internal logic will immediately force the ERROR Flag pin low.

#### FIGURE 2. Enable Threshold

#### **ERROR** Flag

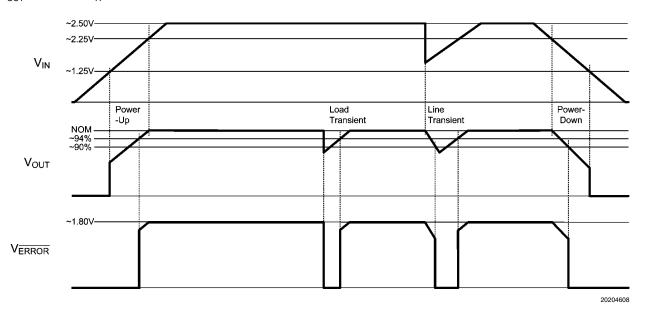

When the LP38513 Enable pin is high, the  $\overline{\text{ERROR}}$  Flag pin will produce a logic low signal when the output drops by more than 10% (typical) from the nominal output voltage. The drop in output voltage may be due to low input voltage, current limiting, or thermal limiting. This flag has a built in hysteresis. The output voltage will need to rise to within 5% of the nominal output voltage for the  $\overline{\text{ERROR}}$  Flag to return to a logic high state. It should also be noted that when the Enable pin is pulled low, the  $\overline{\text{ERROR}}$  Flag pin is forced to be low as well.

The internal  $\overline{\text{ERROR}}$  flag comparator has an open drain output stage. Hence, the  $\overline{\text{ERROR}}$  pin requires an external pull-up resistor. The value of the pull-up resistor should be in the range of 2 k $\Omega$  to 100 k $\Omega$ , and should be connected to the LP38513 output voltage pin. The  $\overline{\text{ERROR}}$  Flag pin should not be pulled-up to any voltage source higher than V<sub>IN</sub> as current flow through an internal parasitic diode may cause unexpected behavior. When the input voltage is less than typically

1.25V the status of the  $\overline{\text{ERROR}}$  flag output will not be reliable. The  $\overline{\text{ERROR}}$  Flag pin must be connected to ground if this function is not used.

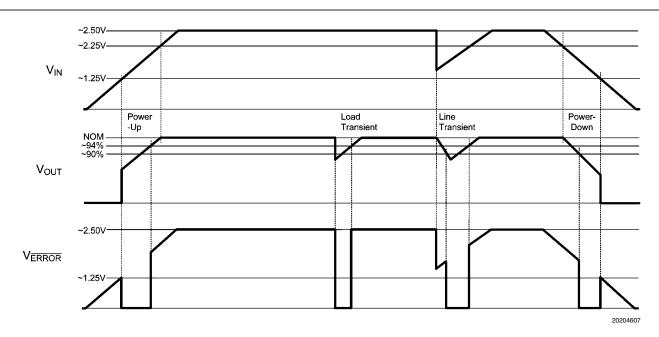

The timing diagram in *Figure 4* shows the relationship between the ERROR flag and the output voltage when the pull-up resistor is connected to the output voltage pin.

The timing diagram in *Figure 5* shows the relationship between the ERROR flag and the output voltage when the pull-up resistor is connected to the input voltage pin.

#### **Power Dissipation**

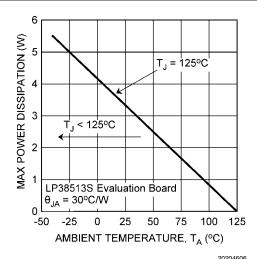

The TO-263 package alone has a junction to ambient thermal resistance ( $\theta_{JA}$ ) rating of 60°C/W. When mounted on the LP38513S evaluation board the  $\theta_{JA}$  rating is approximately 30°C/W

Although there is only approximately 0.28 square inches of 1 ounce copper area immediately under the tab, the top copper surface area is extended to an additional copper area, 1 square inch of 1 ounce copper, on the bottom of the board by the use of nine thermal vias.

With the 30°C/W thermal rating the LP38513S-1.8 evaluation board will deliver the rated 3A output current if  $V_{IN}$  = 2.5V,  $V_{OUT}$  = 1.8V, and  $T_A \le 25^{\circ}C$ .

FIGURE 3. Maximum Power Dissipation vs. Ambient Temperature

FIGURE 4. ERROR Flag when Pull-Up is from Vout

FIGURE 5.  $\overline{\text{ERROR}}$  Flag when Pull-Up is from  $V_{\text{IN}}$

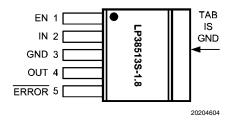

# **Connection Diagram**

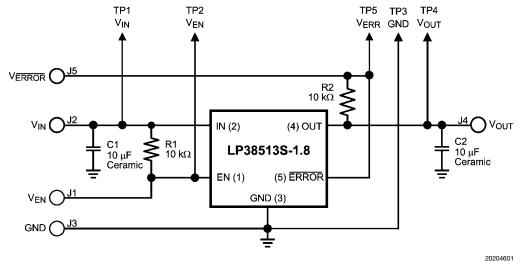

#### **Schematic Diagram**

**Evaluation Board Schematic**

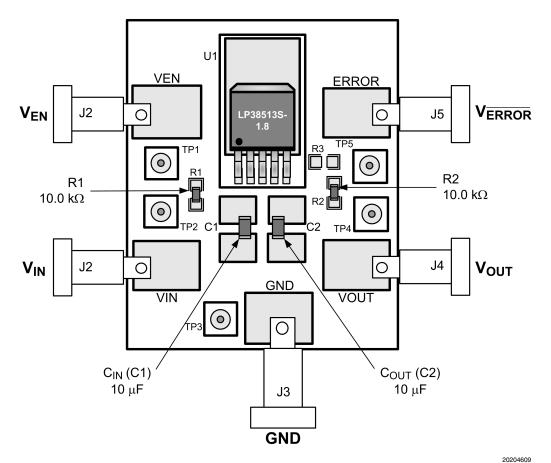

# **PCB Layout**

**Evaluation Board Component and Pin Layout**

5

### **Bill of Materials**

| ID  | Name               | Description                                         | Manufacturer                          | Part Number       |

|-----|--------------------|-----------------------------------------------------|---------------------------------------|-------------------|

| U1  | U1                 | LP38513S-1.8 NOPB                                   | National Semiconductor<br>Corporation | LP38513S-1.8 NOPB |

| C1  | C <sub>IN</sub>    | 10 μF, 10%, MLCC, 10V, X7R, 1210                    | AVX                                   | 1210ZC106KAT2A    |

| C2  | C <sub>OUT</sub>   | 10 μF, 10%, MLCC, 10V, X7R, 1210                    | AXV                                   | 1210ZC106KAT2A    |

| J1  | V <sub>EN</sub>    | Banana Jack : Insulated Solder<br>Terminal ; White  | Johnson Components                    | 108-0901-001      |

| J2  | V <sub>IN</sub>    | Banana Jack : Insulated Solder<br>Terminal ; Red    |                                       | 108-0902-001      |

| J3  | GND                | Banana Jack : Insulated Solder<br>Terminal ; Black  |                                       | 108-0903-001      |

| J4  | V <sub>OUT</sub>   | Banana Jack : Insulated Solder<br>Terminal ; Orange |                                       | 108-0906-001      |

| J5  | V <sub>ERR</sub>   | Banana Jack : Insulated Solder<br>Terminal ; Blue   |                                       | 108-0910-001      |

| R1  | _                  | Resistor: 10 kΩ ±1%; 0805                           | Vishay Dale                           | CRCW 0805 1002 F  |

| R2  | _                  | Resistor: 10 kΩ ±1%; 0805                           | Vishay Dale                           | CRCW 0805 1002 F  |

| R3  | _                  | Not Installed                                       | N/A                                   | N/A               |

| TP1 | TP <sub>EN</sub>   | Turret Terminal :  Mounting Hole Diameter = 0.062"  | Keystone                              | 1593-2            |

| TP2 | TP <sub>IN</sub>   |                                                     |                                       |                   |

| TP3 | $TP_{GND}$         |                                                     |                                       |                   |

| TP4 | TP <sub>OUT</sub>  |                                                     |                                       |                   |

| TP5 | TP <sub>BIAS</sub> |                                                     |                                       |                   |

#### **Notes**

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2007 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Customer Support Center Email:

new.feedback@nsc.com Tel: 1-800-272-9959

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530-85-86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +49 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor Asia** Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan **Customer Support Center** Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560