# NXP dual-channel, up to 14 bit, 750 Msps D/A converter DAC1408D series

# JESD204A-compliant D/A conversion for wideband communication & instrumentation

Optimized for high-speed applications, such as 2.5/3/4G wireless, video broadcast, and instrumentation, this advanced DAC has selectable interpolating filters and a four-lane CGV<sup>TM</sup> serial interface, and complies with the new JEDEC JESD204A.

# **Key features**

- Dual-channel, 14 bit resolution

- ▶ 750 Msps maximum output rate

- ▶ Four-lane JEDEC204A serial digital input

- ▶ 32 bit programmable NCO frequency synthesizer with low-power option

- ▶ SPI control/status interface

- ▶ HVQFN64 package

- ▶ MDS (Multi-DAC Synchronisation)

- ▶ Interpolation filters: 2x, 4x, 8x

# **Applications**

- Wireless infrastructure: Multicarrier GSM, EDGE, CDMA, WCDMA, TD-SCDMA, WiMAX, LTE

- ▶ Multipoint communication infrastructure: LMDS/MMDS

- ▶ Broadband wireless systems

- Digital radio links

- ▶ High-speed instrumentation

- ▶ Automated Test Equipment (ATE)

- ▶ Video broadcast equipment

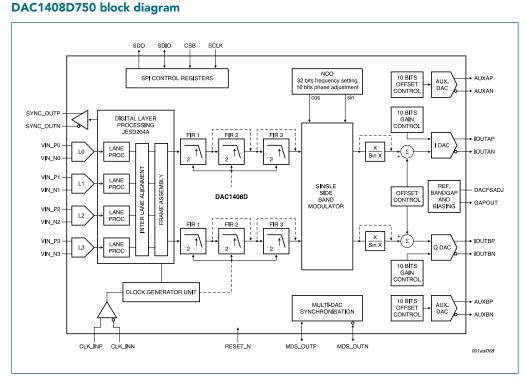

The NXP DAC1408D series, 14 bit digital-to-analog converters with two channels, are equipped with interpolation filters selectable as 2x, 4x, or 8x. It is a high-speed solution optimized for a variety of advanced applications, including single- and multi-carrier wireless infrastructure transmitter signals.

It uses fully configurable digital on-chip modulation to manage I and Q inputs, up-converting them from baseband to IF. The mixing frequency is adjusted, via an SPI (Serial Peripheral Interface) interface with a 32 bit NCO (Numerically Controlled Oscillator). The phase is controlled by a 16 bit register.

Supporting input data rates up to 375 Msps as well as polarity and lane swapping, the DAC1408D series has fourlane CGV<sup>™</sup> receivers.

CGV<sup>™</sup> (Convertisseur Grande Vitesse) designates NXP's compliant, superset implementation of the JEDEC JESD204A interface standard, with enhanced rate (4.0 Gbps typical), enhanced reach (100 cm typical), enhanced features (multiple DAC synchronization) and assured FPGA interoperability. Specifically, NXP offers enhancements in terms of transceiver

rate (up to 4.0 Gbps versus the standard rate of 3.125 Gbps, a 28% increase) and transmitter reach (up to 100 cm versus the standard reach of 20 cm, a 400% increase). The enhanced CGV features include Multi Device Synchronization (MDS), which is not specified, but informatively discussed in the JEDEC specification. NXP has implemented this optional feature to enable LTE MIMO base station and other advanced multichannel applications. NXP's implementation of MDS enables up to sixteen DACs data streams to be sample synchronized and phase coherent.

This new interface has numerous advantages over the traditional parallel one: easy PCB layout, lower pin count, reduced PCB layers and cost, lower radiated noise, selfsynchronous link, skew compensation.

Other features include a two's complement or binary-offset data format, and 74 dBc IMD3 at  $F_{DAC}$  = 640 Msps and  $F_{OUT}$  = 154 MHz. DAC1408D series also include an LVDS compatible clock with multiplier capable of x2, x4 and x8 operation and internal regulation to adjust the output full scale current up to 20 mA.

A digital offset correction can be used to adjust the common mode level at the DAC output. And 2 embedded auxiliary DACs -current mode sources allow offset compensation between the DAC and the next stage in your transmission path.

**Example of reference design**

with DAC1408D750 and FPGA

DAC1408D750 demonstration board, for easy connection to Altera, Xilinx or Lattice evaluation kit

# DAC1408D series

| Туре            | Related demoboard | Description                               |

|-----------------|-------------------|-------------------------------------------|

| DAC1408D series | DAC1408D650W0/DB  | DAC1408D650 demo board                    |

|                 | DAC1408D650W1/DB  | DAC1408D650 demo board with Virtex 5 FPGA |

|                 | DAC1408D750W0/DB  | DAC1408D750 demo board                    |

|                 | DAC1408D750W1/DB  | DAC1408D750 demo board with Virtex 5 FPGA |

www.nxp.com/dataconverters

# www.nxp.com

## © 2010 NXP B.V.

All rights reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Date of release: June 2010

Document order number: 9397 750 16888

Printed in the Netherlands