### **General Description**

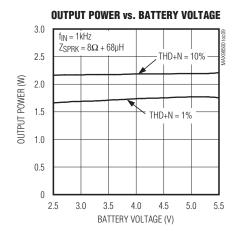

The MAX98500 is a high-efficiency, Class D audio amplifier that features an integrated boost converter to deliver a constant output power over a wide range of battery supply voltages.

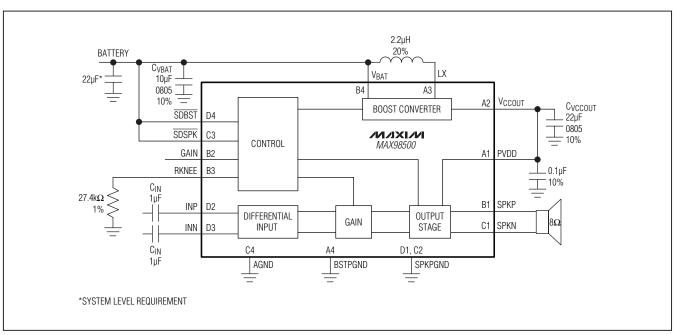

The boost converter operates at 2MHz, requiring only a small (2.2µH) external inductor and capacitor.

The automatic level control has a battery tracking function that reduces the output swing as the supply voltage drops, preventing collapse of battery voltage.

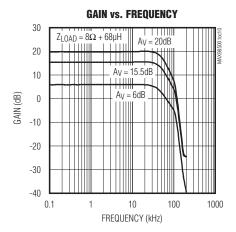

The amplifier has differential inputs and an internal fully differential design. The MAX98500 also features three gain settings (6dB, 15.5dB, and 20dB) that are selectable with a logic input.

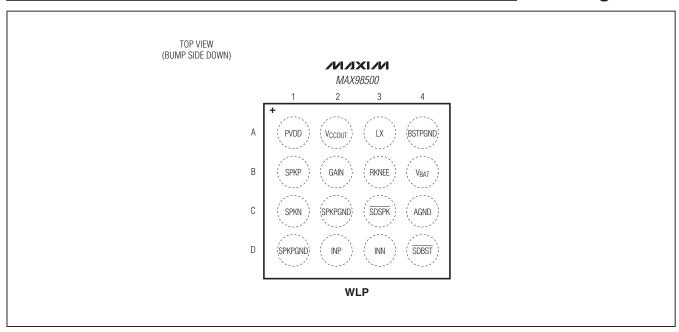

The MAX98500 is available in a small, 0.5mm pitch 16-bump WLP package (2.1mm x 2.1mm). It is specified over the extended -40°C to +85°C temperature range.

### \_Applications

Cell Phones

Smartphones

**GPS** Devices

Mobile Internet Devices

Active Speaker Accessories

## \_\_\_\_Features

- ♦ Boosted Class D Output

- ♦ Integrated Automatic Level Control

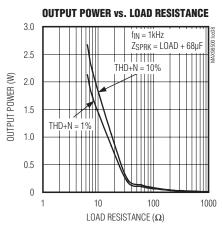

- ♦ Output Power 2.2W into 8Ω, 10% THD+N 1.7W into 8Ω, 1% THD+N

- ♦ Wide 2.5V to 5.5V Supply Voltage Range

- **♦ Undervoltage Lockout Protection**

- ♦ High Total Efficiency of 87%

- ♦ High Step-Up Switching Frequency (2MHz)

- ♦ Active Emission Limiting for Low EMI

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |  |

|--------------|----------------|-------------|--|

| MAX98500EWE+ | -40°C to +85°C | 16 WLP      |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Typical Application Circuit appears at end of data sheet.

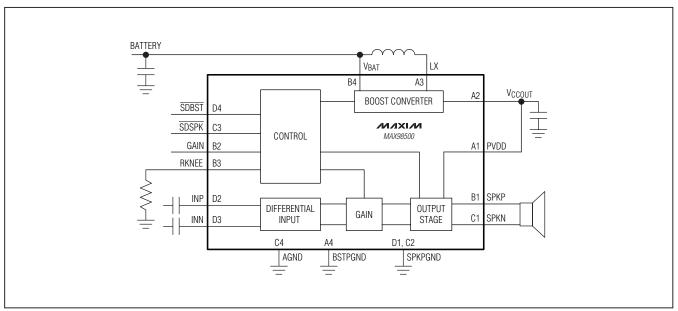

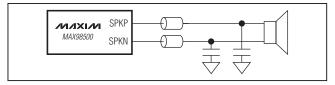

### Simplified Block Diagram

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| VBAT to AGND                               |                    |

|--------------------------------------------|--------------------|

| VCCOUT to BSTPGND, AGNDPVDD to SPKPGND     | 0.3V to +6V        |

| BSTPGND, SPKPGND to AGND                   | 0.3V to +0.3V      |

| GAIN to AGND0.3V to                        | $(V_{BAT} + 0.3V)$ |

| SDBST, SDSPK to AGND                       | -0.3V to VBAT      |

| All Other Pins (excluding LX) to AGND      | 0.3V to +6V        |

| Current Into/Out of LX, VCCOUT, BSTPGND    | ±3.9A              |

| Continuous Current Into/Out of SPK_, PVDD, |                    |

| SPKPGND                                    | ±800mA             |

| Continuous Input Current (all other pins)  | ±20mA              |

| Duration of Short Circuit Between VCCOUT   |                    |

| and BSTPGND                                | Continuous         |

| Duration of SPK_ Short Circuit to PVDD or SPKPGND | Continuous                 |

|---------------------------------------------------|----------------------------|

| Duration of Short Circuit Between SPKP            |                            |

| and SPKN                                          | Continuous                 |

| Continuous Power Dissipation, Multilayer Bo       | ard $(T_A = +70^{\circ}C)$ |

| WLP (derate 20.4mW/°C above +70°C)                | 1.33W                      |

| θ <sub>JA</sub> (Note 1)                          | 49°C/W                     |

| Junction Temperature                              |                            |

| Operating Temperature Range                       | 40°C to +85°C              |

| Storage Temperature Range                         | 65°C to +150°C             |

| Soldering Temperature (reflow)                    | +260°C                     |

|                                                   |                            |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(VBAT = 3.6V, RL =  $\infty$  between SPKP and SPKN, Av = +6dB, CIN = 1 $\mu$ F, 20Hz to 22kHz AC measurement bandwidth, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25 $^{\circ}$ C.) (Note 2)

| PARAMETER                             | SYMBOL               | CON                                                 | DITIONS                                                        | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------|----------------------|-----------------------------------------------------|----------------------------------------------------------------|------|------|------|-------|

| Power-Supply Rejection Ratio (Note 3) | PSRR                 | T <sub>A</sub> = +25°C, V <sub>BAT</sub> =          |                                                                | 95   |      | dB   |       |

|                                       | h                    | TA = +25°C, SDSPK                                   | = SDBST = VBAT                                                 |      | 3.05 |      |       |

| Quiescent Current                     | IVBAT                | TA = +25°C, VSDSPk                                  | ( = 0V, SDBST = V <sub>BAT</sub>                               |      | 0.09 | 0.15 | mA    |

| Quiescent Current                     | IPVDD                | $T_A = +25$ °C, PVDD = $\overline{SDBST} = V_{BAT}$ | = 5.55V, <del>SDSPK</del> =                                    |      | 1.7  | 2.7  |       |

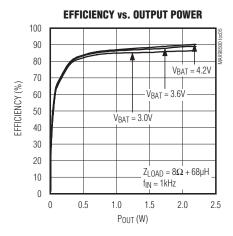

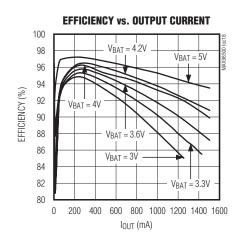

| Combined Efficiency                   | η                    | Pout = 1.7W, f = 1k                                 | Hz, Zspk = $8\Omega + 68\mu$ H                                 |      | 87   |      | %     |

| Shutdown Current                      | ISHDN                | VSDSPK = VSDBST =                                   | 0V, T <sub>A</sub> = +25°C                                     |      | 0.04 | 1.5  | μΑ    |

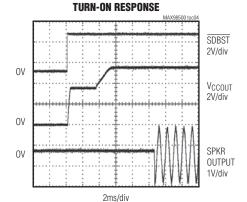

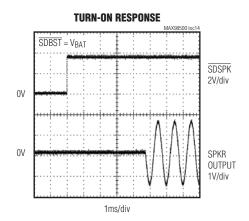

| Turn-On Time                          | ton                  | Time from power-on                                  | to full operation                                              |      | 10   | 12   | ms    |

| BOOST CONVERTER                       |                      |                                                     |                                                                |      |      |      |       |

| Battery Supply Voltage Range          | VBAT                 |                                                     |                                                                | 2.5  |      | 5.5  | V     |

| Soft-Start Interval                   | ton                  |                                                     |                                                                |      | 5.6  |      | ms    |

| Undervoltage Lockout                  | UVLO                 | V <sub>BAT</sub> falling                            |                                                                | 2.1  | 2.2  | 2.3  | V     |

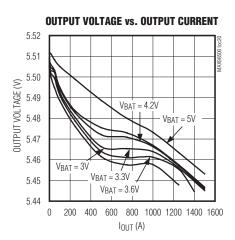

| Boost Converter Output Voltage        | Vvccout              | $I_{LOAD} = 0mA$                                    |                                                                | 5.45 | 5.5  | 5.65 | V     |

| Output Current Limit                  | I <sub>MAX</sub>     | VBAT ≥ = 3.6V                                       |                                                                | 1.5  |      |      | А     |

| Input Current Limit                   | ILIMIT               | Startup, VCCOUT = 0                                 | V                                                              |      | 0.3  | 0.5  | А     |

| nMOS Current Limit                    | I <sub>L</sub> X,MAX |                                                     |                                                                |      | 3.3  |      | А     |

| pMOS Turn-Off Current Limit           |                      |                                                     |                                                                |      | 10   |      | mA    |

| Switching Frequency                   | fs                   |                                                     |                                                                | 1.8  | 2.0  | 2.2  | MHz   |

| Efficiency                            | η                    | 0.1A ≤ I <sub>OUT</sub> ≤ 0.75A                     |                                                                |      | 93   |      | %     |

| Startup Short-Circuit Time            |                      | Converter latch off                                 |                                                                |      | 50   |      | ms    |

| Thermal Shutdown                      |                      |                                                     |                                                                |      | 165  |      | °C    |

| LX Leakage Current                    |                      | $V_{LX} = 0V \text{ or } 5.5V,$                     | T <sub>A</sub> = +25°C                                         | -1.0 | +0.1 | +1.0 |       |

| LA Leanage Ourielli                   |                      | VCCOUT = 5.5V                                       | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$ |      | 0.1  |      | μΑ    |

MIXIM

### **ELECTRICAL CHARACTERISTICS (continued)**

(VBAT = 3.6V, RL =  $\infty$  between SPKP and SPKN, Av = +6dB, CIN = 1 $\mu$ F, 20Hz to 22kHz AC measurement bandwidth, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25 $^{\circ}$ C.) (Note 2)

| PARAMETER                               | SYMBOL | CONDITIONS                                                               |                                            | MIN  | TYP  | MAX  | UNITS   |  |

|-----------------------------------------|--------|--------------------------------------------------------------------------|--------------------------------------------|------|------|------|---------|--|

| SPEAKER AMPLIFIER                       |        |                                                                          |                                            |      |      |      |         |  |

| Output Offset Voltage                   | Vos    | T <sub>A</sub> = +25°C                                                   |                                            |      | 1    | 3    | mV      |  |

| Olish and Ban Laval                     | KCP    | Peak voltage, T <sub>A</sub> = +25°C, A-weighted, 32 samples per second, | Into shutdown                              |      | -56  |      | — dBV   |  |

| Click-and-Pop Level                     | NCP    | ZSPK = $8\Omega$ + $68\mu$ H, (Notes 3, 4)                               | Out of shutdown                            |      | -56  |      | UDV     |  |

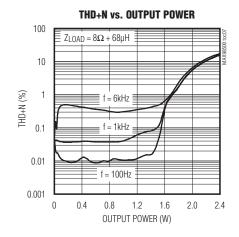

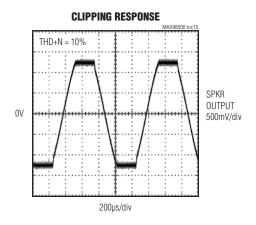

| Output Power (Note 5)                   | Pout   | $Z_{SPK} = 8\Omega + 68\mu H$                                            | THD+N ≤ 1%                                 |      | 1.7  | -    | l w     |  |

| Cutput i ower (Note 3)                  | 1001   | 25PK = 022 + 00µ11                                                       | THD+N ≤ 10%                                |      | 2.2  |      | V V     |  |

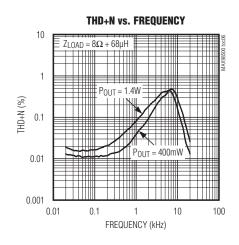

| Total Harmonic Distortion Plus<br>Noise | THD+N  | $f = 1kHz$ , $P_{OUT} = 850m^3$<br>$Z_{SPK} = 8\Omega + 68\mu H$         | $W, T_A = +25^{\circ}C,$                   |      | 0.05 |      | %       |  |

| Output Switching Frequency              |        |                                                                          |                                            |      | 300  |      | kHz     |  |

|                                         |        | GAIN = AGND                                                              |                                            | 5.5  | 6    | 6.5  |         |  |

| Gain                                    | Av     | GAIN = unconnected                                                       |                                            | 15   | 15.5 | 16   | dB      |  |

|                                         |        | GAIN = VBAT                                                              |                                            | 19.5 | 20   | 20.5 |         |  |

| Output Current Limit                    |        |                                                                          |                                            |      | 2    |      | А       |  |

| Efficiency                              | η      | POUT = 1.7W, f = 1kHz, Z <sub>SPK</sub> = $8\Omega$ + $68\mu$ H          |                                            |      | 92   |      | %       |  |

| Output Noise                            |        | A-weighted                                                               |                                            |      | 43   |      | μVRMS   |  |

|                                         |        |                                                                          | $A_V = 6dB$<br>(GAIN = AGND)               | 36   | 54   | 72   |         |  |

| Input Resistance                        | RIN    | SDBST = SDSPK = VBAT                                                     | Ay = 15.5dB<br>(GAIN =<br>unconnected)     | 12   | 18   | 26   | kΩ      |  |

|                                         |        |                                                                          | Av = 20dB<br>(GAIN = VBAT)                 | 6.5  | 11   | 16   |         |  |

|                                         |        | VSDBST = VSDSPK = 0V                                                     | All gain settings                          |      | 110  |      |         |  |

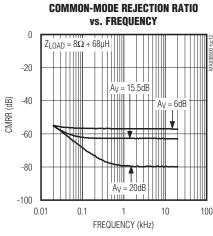

| Common-Mode Rejection Ratio             | CMRR   | f = 1kHz                                                                 |                                            |      | 60   |      | dB      |  |

| Bias Voltage                            | VBIAS  |                                                                          |                                            | 1.3  | 1.4  | 1.5  | V       |  |

| ALC                                     |        |                                                                          |                                            |      |      |      |         |  |

| Attack Time                             |        |                                                                          |                                            |      | 20   |      | μs/dB   |  |

| Release Time                            |        |                                                                          |                                            |      | 1.6  |      | s/dB    |  |

| Maximum Attenuation                     |        |                                                                          |                                            |      | 8    |      | dB      |  |

| Attenuation Resolution                  |        |                                                                          |                                            |      | 0.5  |      | dB      |  |

|                                         |        | Ri                                                                       | $NEE = 154k\Omega$                         | 2.19 | 2.3  | 2.42 |         |  |

| Knee Voltage                            | VKNEE  | $T_A = +25^{\circ}C$                                                     | $\langle \text{NEE} = 40.5 \text{k}\Omega$ | 3.14 | 3.3  | 3.47 | \ \ \ \ |  |

|                                         |        | $R_{KNEE} = 13k\Omega$                                                   |                                            | 3.71 | 3.9  | 4.10 |         |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{BAT}=3.6V, R_L=\infty)$  between SPKP and SPKN,  $A_V=+6dB, C_{IN}=1\mu F, 20Hz$  to 22kHz AC measurement bandwidth,  $T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .) (Note 2)

| PARAMETER                    | SYMBOL     | C                                                  | CONDITIONS                | MIN  | TYP  | MAX  | UNITS |

|------------------------------|------------|----------------------------------------------------|---------------------------|------|------|------|-------|

| Knee Resistor                |            | T <sub>A</sub> = +25°C,<br>A <sub>V</sub> = 15.5dB | V <sub>KNEE</sub> = 3.25V |      | 43.2 |      |       |

|                              |            |                                                    | VKNEE = 3.35V             |      | 37.4 |      |       |

|                              |            |                                                    | VKNEE = 3.45V             |      | 32.4 |      |       |

|                              | RKNEE      |                                                    | VKNEE = 3.55V             |      | 27.4 |      | kΩ    |

|                              |            |                                                    | VKNEE = 3.65V             |      | 23.2 |      |       |

|                              |            |                                                    | VKNEE = 3.75V             |      | 18.7 |      |       |

|                              |            |                                                    | V <sub>KNEE</sub> = 3.85V |      | 15.0 |      |       |

| DIGITAL INPUTS (SDBST, SDSPI | <u>(</u> ) |                                                    |                           |      |      |      |       |

| Input Voltage High           | ViH        |                                                    |                           | 1.4  |      |      | V     |

| Input Voltage Low            | VIL        |                                                    |                           |      |      | 0.4  | V     |

| Input Capacitance            | CIN        |                                                    |                           |      | 10   |      | рF    |

| Input Leakage Current        | liN        | T <sub>A</sub> = +25°C                             |                           | -1.0 |      | +1.0 | μΑ    |

Note 2: 100% production tested at TA = +25°C. Specifications over temperature limits are guaranteed by design.

**Note 3:** Amplifier inputs are AC-coupled to AGND. **Note 4:** Mode transitions are controlled by SDSPK.

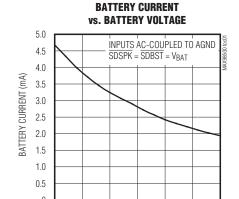

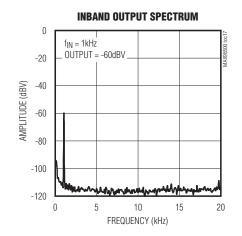

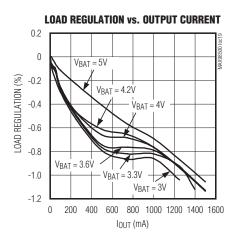

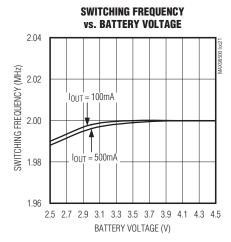

### **Typical Operating Characteristics**

$(V_{BAT} = 3.6V, R_L = \infty \text{ between SPKP and SPKN, } A_V = +15.5dB, RKNEE = V_{BAT}, 20Hz \text{ to } 22kHz \text{ AC measurement bandwidth, unless otherwise noted.})$

#### General

4.0

BATTERY VOLTAGE (V)

4.5

2.5

3.0

3.5

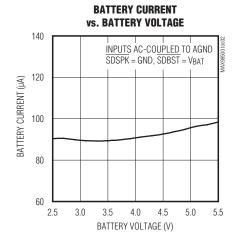

### Typical Operating Characteristics (continued)

$(V_{BAT} = 3.6V, R_L = \infty$  between SPKP and SPKN,  $A_V = +15.5dB$ , RKNEE =  $V_{BAT}$ , 20Hz to 22kHz AC measurement bandwidth, unless otherwise noted.)

#### Speaker

### Typical Operating Characteristics (continued)

$(V_{BAT} = 3.6V, R_L = \infty$  between SPKP and SPKN,  $A_V = +15.5dB$ , RKNEE =  $V_{BAT}$ , 20Hz to 22kHz AC measurement bandwidth, unless otherwise noted.)

FREQUENCY (kHz)

-100

0.01

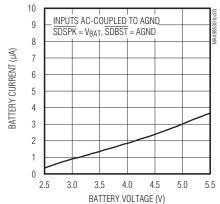

### **Typical Operating Characteristics (continued)**

(V<sub>BAT</sub> = 3.6V, R<sub>L</sub> =  $\infty$  between SPKP and SPKN, A<sub>V</sub> = +15.5dB, RKNEE = V<sub>BAT</sub>, 20Hz to 22kHz AC measurement bandwidth, unless otherwise noted.)

#### **Boost Converter**

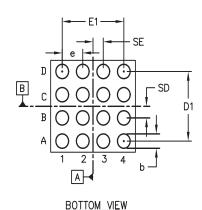

## Pin Configuration

### **Pin Description**

| BUMP   | NAME    | FUNCTION                                                                                                                                                                                  |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | PVDD    | Speaker Amplifier Power Supply. Bypass to SPKPGND with a 0.1µF capacitor.                                                                                                                 |

| A2     | VCCOUT  | Boost Converter Output. Connect a 22μF (0805) capacitor between V <sub>CCOUT</sub> and BSTPGND.                                                                                           |

| A3     | LX      | Boost Switch Input                                                                                                                                                                        |

| A4     | BSTPGND | Boost Power Ground                                                                                                                                                                        |

| B1     | SPKP    | Positive Speaker Output                                                                                                                                                                   |

| B2     | GAIN    | Gain Select Input. Connect GAIN to ground to set the speaker gain to 6dB. Leave GAIN unconnected to set the speaker gain to 15.5dB. Connect GAIN to VBAT to set the speaker gain to 20dB. |

| В3     | RKNEE   | ALC Knee Voltage Set Input. Set the ALC knee voltage with a resistor to AGND.                                                                                                             |

| B4     | VBAT    | Battery Voltage Input. Connect a 10μF (0805) capacitor between V <sub>BAT</sub> and BSTPGND. Include at least 22μF of system bulk capacitance.                                            |

| C1     | SPKN    | Negative Speaker Output                                                                                                                                                                   |

| C2, D1 | SPKPGND | Speaker Ground                                                                                                                                                                            |

| C3     | SDSPK   | Speaker Output Shutdown. Drive SDSPK low to shutdown the speaker output.                                                                                                                  |

| C4     | AGND    | Analog Ground                                                                                                                                                                             |

| D2     | INP     | Positive Audio Input                                                                                                                                                                      |

| D3     | INN     | Negative Audio Input                                                                                                                                                                      |

| D4     | SDBST   | Boost Converter Shutdown. Drive SDBST low to shutdown the boost converter and the speaker output.                                                                                         |

### **Detailed Description**

The MAX98500 is a high-efficiency Class D audio amplifier that features an integrated boost converter to deliver a constant output power over a large range of battery supply voltages. The boost converter operates at 2MHz, requiring only a small (2.2µH) external inductor and output capacitor. The amplifier has differential inputs and an internal fully differential design with three gain settings (6dB, 15.5dB, and 20dB) that are selectable with a logic input.

The MAX98500 also features automatic level control. The automatic level control reduces the output swing when the battery voltage decreases to prevent the collapse of battery voltage.

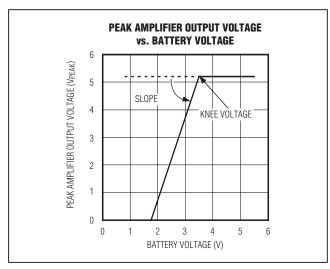

Figure 1. Typical Tracking Function

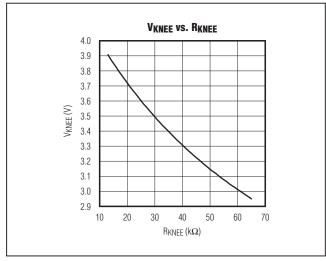

Figure 2. The Relationship of RKNEE and VKNEE

#### **Class D Speaker Amplifier**

The MAX98500 filterless Class D amplifier offers much higher efficiency than Class AB amplifiers. The high efficiency of a Class D amplifier is due to the switching operation of the output stage transistors. Any power loss associated with the Class D output stage is mostly due to the I<sup>2</sup>R loss of the MOSFET on-resistance and quiescent current overhead.

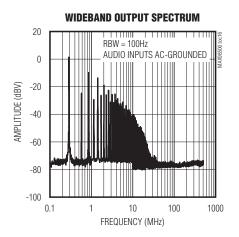

#### Low-EMI Filterless Output Stage

Traditional Class D amplifiers require the use of external LC filters, or shielding, to meet EN55022B electromagnetic-interference (EMI) regulation standards. Maxim's active emissions limiting edge-rate control circuitry reduces EMI emissions, while maintaining up to 92% efficiency (speaker only). Above 10MHz, the wideband spectrum looks like noise for EMI purposes.

#### **Automatic Level Control**

The MAX98500 features an automatic level control circuit that limits the maximum speaker output swing. This helps:

- Avoid clipping

- Save the battery from collapsing, which could cause a reset of the system

The limiter keeps the peak voltage below a value that is a function of battery voltage, as shown in Figure 1.

The full output swing of 5.2V is maintained for battery voltages down to the knee voltage, while for lower battery voltages the maximum VPEAK-swing is reduced by 3V/V.

The knee voltage can be changed by applying different resistors between RKNEE and AGND. The typical tracking function is shifted horizontally with different RKNEE resistor values (Figure 2).

The preamplifier gain reduces as the automatic level control activates. The maximum gain reduction is 8dB with a resolution of 0.5dB steps.

The attack (gain reduction) happens immediately (20 $\mu$ s/ dB), while the release is set to 1.6s/dB.

#### **GAIN Select**

The MAX98500 features three internal gain settings that are selectable with the GAIN input. Table 1 shows the gain settings.

Table 1. Gain Settings

| GAIN             | AMPLIFIER GAIN (dB) |

|------------------|---------------------|

| AGND             | 6                   |

| Unconnected      | 15.5                |

| V <sub>BAT</sub> | 20                  |

**Table 2. Shutdown Configurations**

| SDBST | SDSPK | BOOST<br>STATUS | SPEAKER<br>STATUS |  |

|-------|-------|-----------------|-------------------|--|

| Low   | Low   | Off             | Off               |  |

| Low   | High  | Off             | Off               |  |

| High  | Low   | On              | Off               |  |

| High  | High  | On              | On                |  |

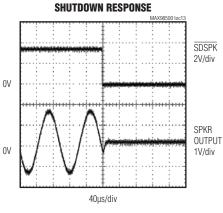

#### Shutdown

The MAX98500 features two active-low shutdown inputs ( $\overline{\text{SDSPK}}$  and  $\overline{\text{SDBST}}$ ). Table 2 shows the different shutdown configurations.

#### Click-and-Pop Suppression

The MAX98500 speaker amplifier features Maxim's comprehensive click-and-pop suppression. During startup, the click-and-pop suppression circuitry reduces any audible transient sources internal to the device. When entering shutdown, the differential speaker outputs ramp down to SPKPGND quickly and simultaneously.

#### **Current-Limit and Thermal Protection**

The IC features overcurrent and thermal protection. The IC shuts down when the VCCOUT output decreases to about 80% of the expected output. The IC also enters into shutdown when the die temperature exceeds +165°C. The device remains in shutdown until power is reset or \$\overline{SDBST}\$ is toggled low and back high after the fault condition has been removed. The IC speaker amplifier also features a 2A (typ) short-circuit protection scheme.

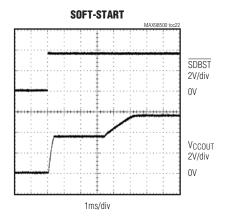

#### **Boost Converter** Soft-Start

The MAX98500 features a two-stage, soft-start, power-up sequence. When SDBST is taken high and VBAT is above UVLO the soft-start first ramps VCCOUT quickly to VBAT voltage with a battery current of 300mA (typ). Once the VCCOUT reaches the VBAT voltage, the internal switching turns on and ramps the VCCOUT to 5.5V in 5ms (typ), see the Soft-Start graph in the *Typical Operating Characteristics*. The maximum load current is available after the soft-start is completed.

#### Undervoltage Lockout (UVLO)

The undervoltage lockout (UVLO) circuit compares the voltage at VBAT with the UVLO threshold (2.2V typ) to ensure that the input voltage is high enough for reliable operation. Once the VBAT voltage exceeds the UVLO

threshold, the soft-start begins. When the input voltage falls below the UVLO threshold, the boost converter and speaker amplifier turn off.

# Applications Information Filterless Class D Operation

Traditional Class D amplifiers require an output filter to recover the audio signal from the amplifier's output. The filter adds cost, increases the solution size of the amplifier, and can decrease efficiency and THD+N performance. The traditional PWM scheme uses large differential output swings (2 x supply voltage peak-to-peak) and causes large ripple currents. Any parasitic resistance in the filter components results in a loss of power and lowers the efficiency.

The MAX98500 does not require an output filter. The device relies on the inherent inductance of the speaker coil and the natural filtering of both the speaker and the human ear to recover the audio component of the square-wave output. Eliminating the output filter results in a smaller, less costly, and more efficient solution.

Because the frequency of the MAX98500 output is well beyond the bandwidth of most speakers, voice coil movement due to the square-wave frequency is very small. Although this movement is small, a speaker not designed to handle the additional power can be damaged. For optimum results, use a speaker with a series inductance >  $10\mu H$ . Typical  $8\Omega$  speakers exhibit series inductances in the  $20\mu H$  to  $100\mu H$  range.

#### RF Susceptibility

GSM radios transmit using time-division multiple access (TDMA) with 217Hz intervals. The result is an RF signal with strong amplitude modulation at 217Hz and its harmonics that is easily demodulated by audio amplifiers. The MAX98500 is designed specifically to reject RF signals; however, PCB layout has a large impact on the susceptibility of the end product.

In RF applications, improvements to both layout and component selection decrease the MAX98500's susceptibility to RF noise and prevent RF signals from being demodulated into audible noise. Trace lengths should be kept below 1/4 of the wavelength of the RF frequency of interest. Minimizing the trace lengths prevents them from functioning as antennas and coupling RF signals into the MAX98500. The wavelength ( $\lambda$ ) in meters is given by:  $\lambda = c/f$  where  $c = 3 \times 10^8$  m/s, and f = the RF frequency of interest.

Route audio signals on the middle layers of the PCB to allow the ground planes above and below to shield them from RF interference. Ideally the top and bottom layers of the PCB should primarily be ground planes to create effective shielding.

Additional RF immunity can also be obtained from relying on the self-resonant frequency of capacitors as it exhibits the frequency response similar to a notch filter. Depending on the manufacturer, 10pF to 20pF capacitors typically exhibit self resonance at RF frequencies. These capacitors, when placed at the input pins, can effectively shunt the RF noise at the inputs of the MAX98500. For these capacitors to be effective, they must have a low-impedance, low-inductance path to the ground plane. Do not use microvias to connect to the ground plane as these vias do not conduct well at RF frequencies.

## **Speaker Component Selection**Optional Ferrite Bead Filter

Additional EMI suppression can be achieved using a filter constructed from a ferrite bead and a capacitor to ground (Figure 3). Use a ferrite bead with low DC resistance, high-frequency (> 100MHz) impedance between  $100\Omega$  and  $600\Omega$ , and rated for at least 1A. The capacitor value varies based on the ferrite bead chosen and the actual speaker lead length. Select a capacitor less than 1nF based on EMI performance.

#### Input Capacitor (CIN)

An input capacitor, C<sub>IN</sub>, in conjunction with the input impedance of the MAX98500 speaker inputs forms a highpass filter that removes the DC bias from an incoming analog signal. The AC-coupling capacitor allows the amplifier to automatically bias the signal to an optimum DC level. Assuming zero-source impedance, the -3dB point of the highpass filter is given by:

$$f_{-3dB} = \frac{1}{2\pi R_{IN} C_{IN}}$$

Choose C<sub>IN</sub> such that f-3dB is well below the lowest frequency of interest. For best audio quality, use capacitors whose dielectrics have low-voltage coefficients, such as tantalum or aluminum electrolytic. Capacitors with high-voltage coefficients, such as ceramics, could result in increased distortion at low frequencies.

## **Boost Converter Component Selection**Inductor Selection

In most step-up converter designs, a reasonable inductor value can be derived from the following equation. This equation sets peak-to-peak inductor current at 1/2 the DC inductor current:

$$L = (2 \times V_{BATT} \times D \times (1-D))/(I_{OUT}(MAX) \times f_{SW})$$

where fsW is the switching frequency, and D is the duty factor given by D = 1 - (VBAT/VOUT). Using L from the equation above results in a peak-to-peak inductor current ripple of 0.5 x IOUT/(1 - D), and a peak inductor current of 1.25 x IOUT/(1 - D). Ensure the peak (saturation) current rating of the inductor meets or exceeds this requirement.

The recommended nominal inductance for the MAX98500 is  $2.2\mu\text{H}$ . Nominal inductance decreases as the inductor current increases. If the decrease from the nominal inductance is severe, the boost converter may become unstable or shut down at lower output power levels than expected. Ensure the minimum inductance at the peak inductor current is  $1.0\mu\text{H}$ .

#### Output Capacitor (CVCCOUT)

An output capacitor, CVCCOUT, is required to keep the output voltage ripple small and to ensure regulation loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors are highly recommended due to their small size and low ESR. Ceramic capacitors with X5R or X7R temperature characteristics generally perform well. The recommended nominal capacitance for the MAX98500 is  $22\mu\text{F}$  (0805 case size or larger). Ensure the minimum capacitance at 5.5V is  $6.8\mu\text{F}$ .

#### Input Capacitor (CVBAT)

An input capacitor, CVBAT, reduces the current peaks drawn from the battery or input power source and reduces switching noise in the IC. The impedance of the input capacitor at the switching frequency should be kept very low. Ceramic capacitors are highly recommended due to their small size and low ESR. Ceramic capacitors with X5R or X7R temperature characteristics generally perform well. One 10µF ceramic capacitor is recommended with a system bulk capacitance of 22µF or larger.

Figure 3. Optional Class D Ferrite Bead Filter

MIXIM

#### Supply Bypassing, Layout, and Grounding

Proper layout and grounding are essential for optimum performance. Use a large continuous ground plane on a dedicated layer of the PCB to minimize loop areas. Connect AGND and BSTPGND/SPKPGND directly to the ground plane using the shortest traces length possible. Proper grounding improves audio performance, and prevents any digital noise from coupling into the analog audio signals.

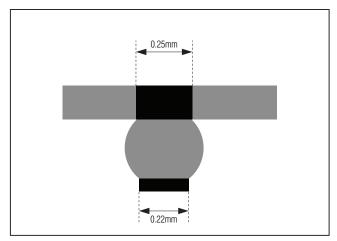

Figure 4. Recommended PCB Footprint

Bypass VBAT with a  $10\mu F$  capacitor and a system bulk capacitance of  $22\mu F$  or larger. Bypass PVDD to SPKPGND with a  $0.1\mu F$  capacitor and with as minimal a loop area as possible. Connect SPKP and SPKN to the speaker using the shortest and widest traces possible. Reducing trace length minimizes radiated EMI. Route SPKP/SPKN as a differential pair on the PCB to minimize loop area, thereby, the inductance of the circuit. If filter components are used on the speaker outputs, be sure to locate them as close as possible to the MAX98500 to ensure maximum effectiveness. Minimize the trace length from any ground-tied passive components to SPKPGND to further minimize radiated EMI.

An evaluation kit (MAX98500 Evaluation Kit) is available to provide an example layout for the MAX98500.

#### **WLP Applications Information**

For the latest application details on WLP construction, dimensions, tape carrier information, PCB techniques, bump-pad layout, and recommended reflow temperature profile, as well as the latest information on reliability testing results, refer to the Application Note 1891: Wafer-Level Packaging (WLP) and Its Applications on Maxim's website at www.maxim-ic.com/ucsp. See Figure 4 for the recommended PCB footprint for the MAX98500.

### **Typical Application Circuit**

MIXIM

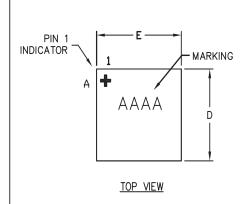

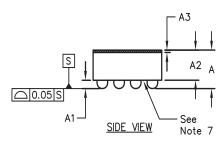

### Package Information

For the latest package outline information and land patterns, go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 16 WLP       | W162B2+1     | <u>21-0200</u> |

| CC | DMMON DIMENSIONS |  |  |  |

|----|------------------|--|--|--|

| Α  | 0.64±0.05        |  |  |  |

| A1 | 0.24±0.03        |  |  |  |

| A2 | 0.40 REF         |  |  |  |

| А3 | 0.025 BASIC      |  |  |  |

| b  | Ø0.31±0.03       |  |  |  |

| D1 | 1.50 BASIC       |  |  |  |

| E1 | 1.50 BASIC       |  |  |  |

| е  | 0.50 BASIC       |  |  |  |

| SD | 0.25 BASIC       |  |  |  |

| SE | 0.25 BASIC       |  |  |  |

|           | Е    |      | D    |      | DEPOPULATED |

|-----------|------|------|------|------|-------------|

| PKG. CODE | MIN  | MAX  | MIN  | MAX  | BUMPS       |

| W162B2+1  | 1.98 | 2.11 | 1.98 | 2.11 | NONE        |

| W162C2+1  | 2.12 | 2.26 | 1.99 | 2.13 | NONE        |

| W162D2+1  | 1.99 | 2.01 | 1.99 | 2.01 | B3, C2      |

#### NOTES:

- 1. Terminal pitch is defined by terminal center to center value.

- 2. Outer dimension is defined by center lines between scribe lines.

- 3. All dimensions in millimeters.

- 4. Marking shown is for package orientation reference only.

- 5. Tolerance is  $\pm$  0.02mm unless specified otherwise.

- 6. All dimensions apply to PbFree (+) package codes only.

- 7. Front-side finish can be either Black or Clear.

/VI/IXI/VI

NTI F•

PACKAGE OUTLINE

16 BUMPS, WLP PKG. 0.5mm PITCH

APPROVAL

DOCUMENT CONTROL NO. 21-0200

E 1/1

-DRAWING NOT TO SCALE-

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 5/10          | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600