# **Evaluation Board For** AD768x/AD769x/AD794x/AD798x

### **Preliminary Technical Data**

## EVAL-AD76XXCB 8/10-Pin

#### **FEATURES**

Versatile analog signal conditioning circuitry On-board reference, crystal oscillator and buffers **16-bit Parallel Buffered Outputs** Ideal for DSP and data acquisition card interfaces Analog and digital prototyping area for breadbording the target system

Stand-alone operation or Eval control board compatibility PC software for control and data analysis LabVIEW<sup>1</sup> driver to develop custom application

#### **GENERAL DESCRIPTION**

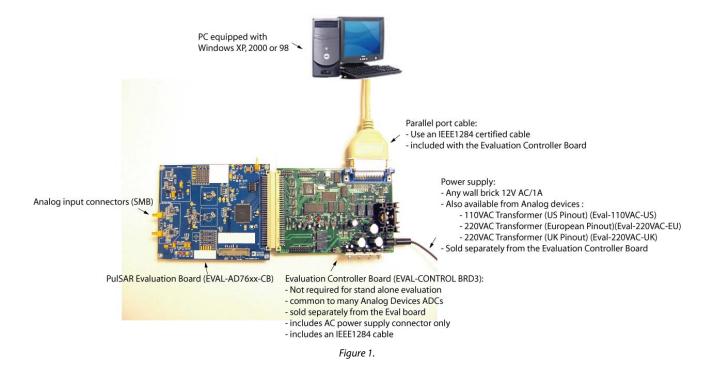

The EVAL-AD76XXCB 8/10-Pin is an evaluation board for the AD768x/AD769x/AD794x/AD798x 8 and 10-pin PulSAR high resolution ADCs (see the Ordering Guide at the end of this document for a product list).

The evaluation board is designed to demonstrate the ADC's performance and to provide an easy to understand interface for a variety of system applications. A full description of the

AD768x/AD769x/AD794x/AD798x is available at www.analog.com and should be consulted when utilizing this evaluation board.

The evaluation board is ideal for use with either Analog Devices EVAL-CONTROL BRD2/BRD3 (EVAL-CONTROL BRDx), DSP based controller board, to run the Analog devices evaluation software and to develop a specific application using LabVIEW, or as a stand-alone evaluation board.

The EVAL-CONTROL BRDx is sold separately from the evaluation board, is required to run the evaluation software, is not required in stand alone mode and can be reused with many Analog Devices ADCs.

Rev. Pr G

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2007 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>1</sup> Labview is a trademark of National Instruments.

## **EVAL-AD76XXCB 8/10-Pin**

## **Preliminary Technical Data**

### **TABLE OF CONTENTS**

| Detailed Description                             | Use as a Standalone Evaluation Board |

|--------------------------------------------------|--------------------------------------|

| Using the EVAL-AD768x/AD769x/AD794xCB Software 3 | Ordering Guide                       |

| Testing Methods                                  | ESD Caution                          |

#### **REVISION HISTORY**

03/07—PrG Version

02/06-PrF Version

05/05—PrE Version

### EVAL-AD76XXCB 8/10-Pin

#### **Detailed Description**

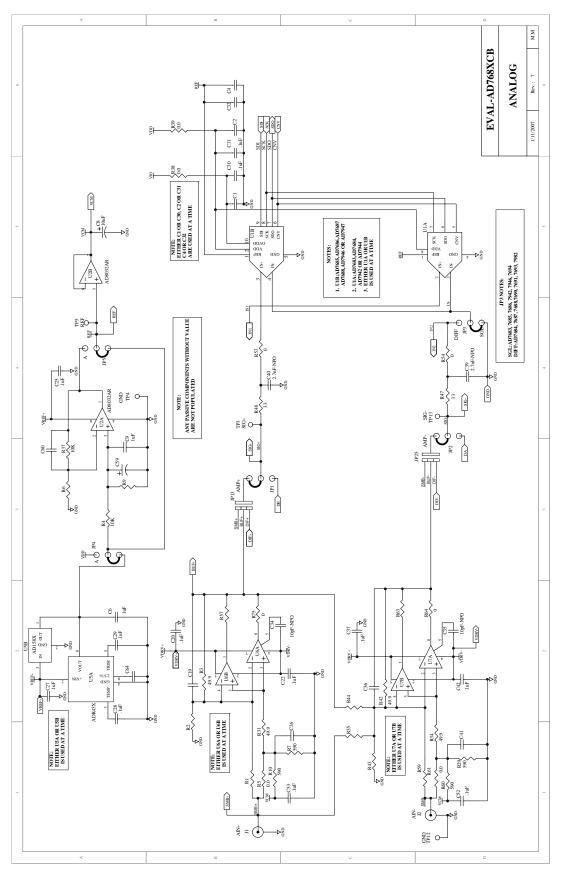

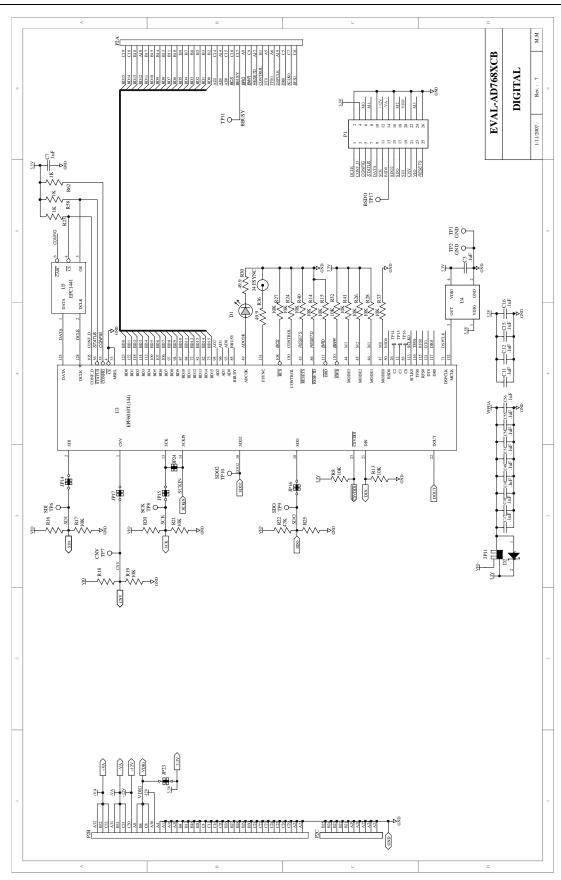

The EVAL-AD76XXCB 8/10-Pin includes a 5V ultrahigh precision reference (ADR435), and a signal conditioning circuit with two opamps (ADA4841-x) and digital logic. The board interfaces with a 96-way connector for the EVAL-CONTROL BRDx and a 26-pin IDC connector for the serial output interface.

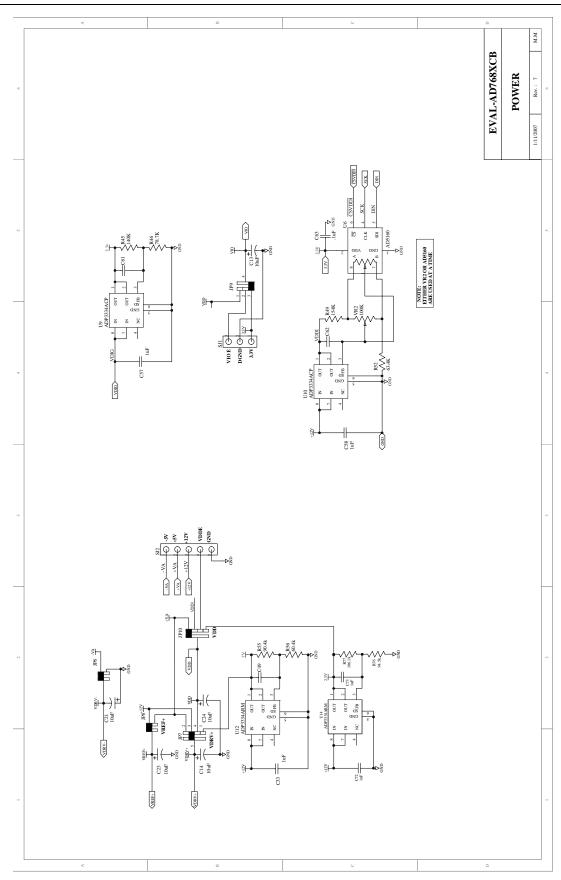

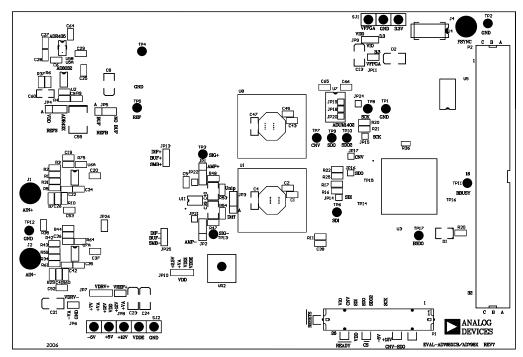

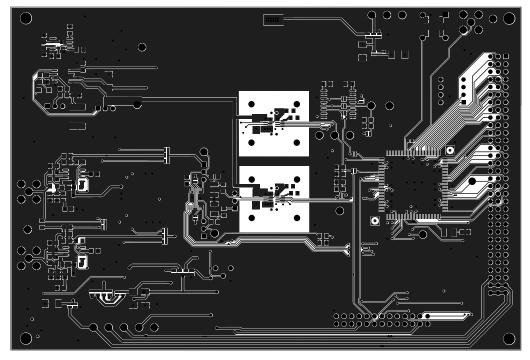

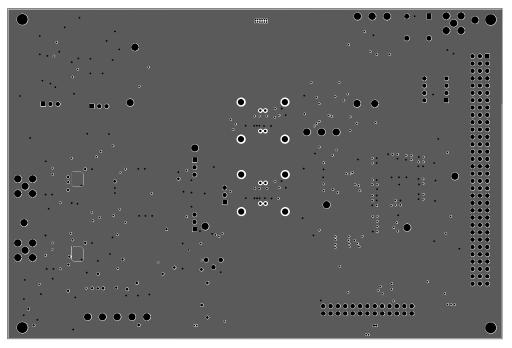

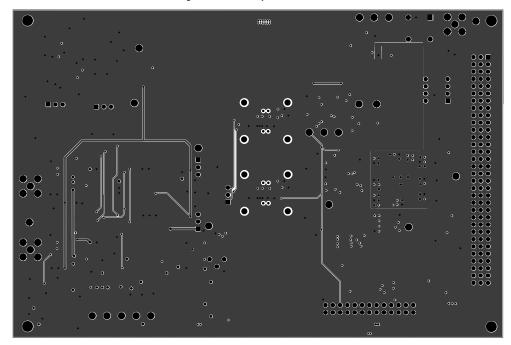

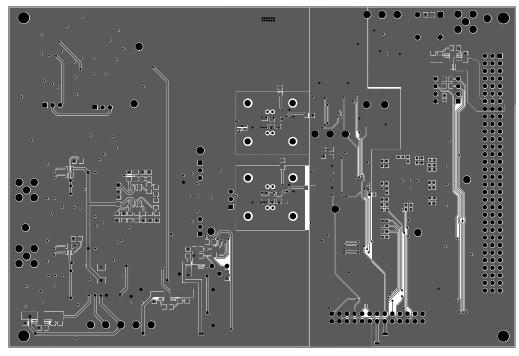

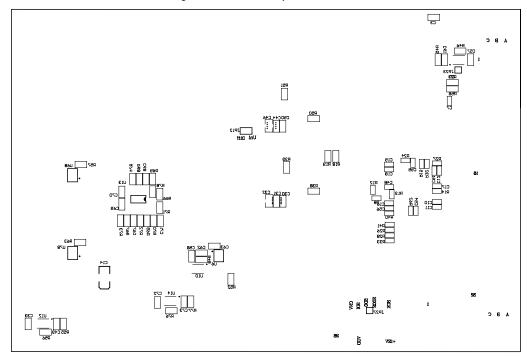

The evaluation board is a four-layer board carefully laid out and tested to demonstrate the specific high accuracy performance of the AD768x/ AD769x/AD794x/AD798x. Figure 2 through Figure 5 show the schematics of the evaluation board. The layouts of the board are shown in the following figures:

Figure 6: Top-Side Silk-Screen

Figure 7: Top-Side Layer

Figure 8: Ground Layer

Figure 9: Shield Layer

Figure 10: Bottom-Side Layer

Figure 11: Bottom-Side Silk-Screen

The evaluation board has a flexible design that enables the user to choose among many different board configurations. A description of each selectable jumper is listed in Table 1, and the available test points are listed in Table 2.

The evaluation board is configured in the factory with the front-end amplifiers U6 and U7 set to a gain of 1. The board is set to be powered through the EVAL-CONTROL BRDx.

Buffered conversion data is available at the output parallel bus BD on U3 and on the 96-pin connector P3 and is valid during the falling edge of BBUSY on P3. Activity of the ADC turns on the on-board LED

#### **Power Supplies and Grounding**

The evaluation board has two power supply blocks:

- -SJ1 for the digital interface circuitry and the digital section of the ADC.

- -SJ2 for the analog section including the signal conditioning and the reference voltage circuitry.

These offer flexibility to evaluate the ADC and the surrounding circuitry with any power supply combination.

#### **Analog Input Ranges and Multiplexing**

The analog front-end amplifier circuitry U6 and U7 allows flexible configuration changes such as positive or negative gain, input range scaling, filtering, addition of a DC component, and the use of different op-amp and supplies.

The factory configuration of the analog input of U6 and U7 is set at midscale. This allows a transition noise test without any other equipment. An FFT test can be done by applying a very

low distortion AC source.

As an option, an ADG739 multiplexer can be used in front of the ADC to demonstrate performances for multichannel applications.

A second ADC can be mounted on the board to demonstrate the daisy-chain feature.

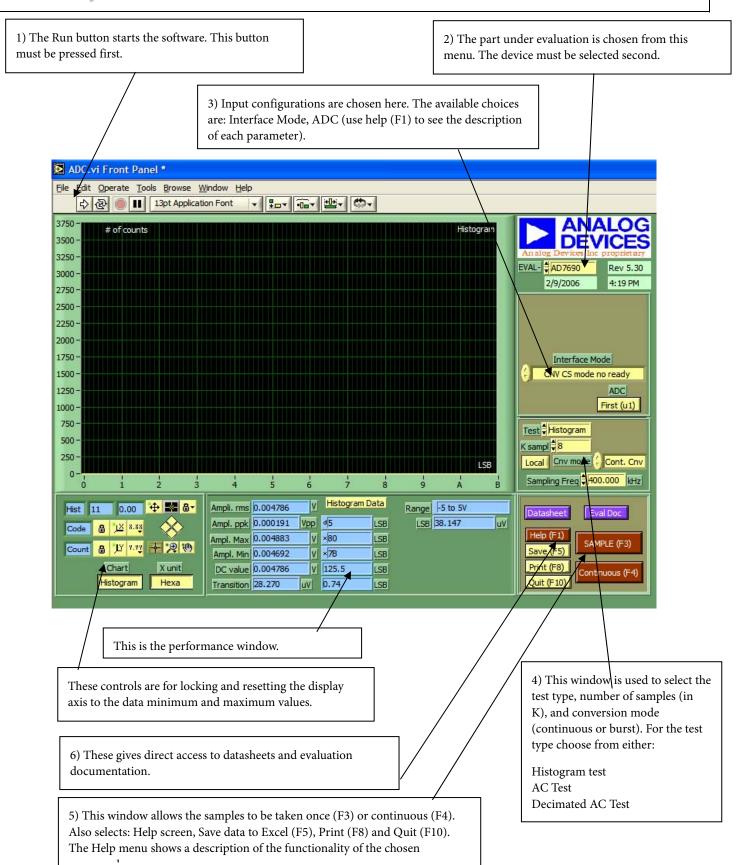

#### **Using the Software**

This configuration requires to use the EVAL-CONTROL BRDx to interface the evaluation board with the PC.

#### **Software Description**

The evaluation board comes with software for analyzing the AD768x/AD769x/AD794x/AD798x. One can perform a histogram to determine code transition noise, and Fast Fourier Transforms (FFT's) to determine the Signal-to-Noise Ratio (SNR), Signal-to-Noise-plus-Distortion (SINAD) and Total-Harmonic-Distortion (THD). The AC performances can also been evaluated after digital filtering (averaging) with enhanced resolution (up to 32 bits). The front-end PC software has four screens:

Figure 12 is the Setup Screen where sample rate, number of samples are selected.

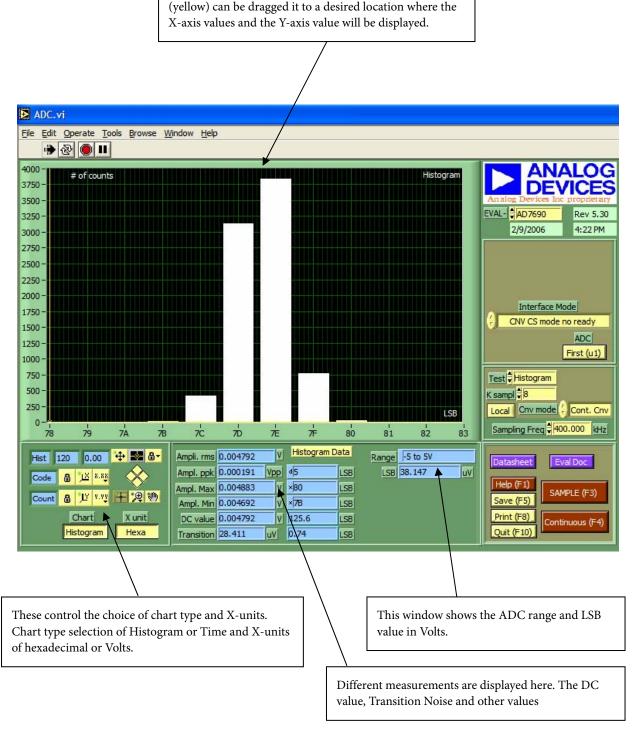

Figure 13 is the Histogram Screen, which allows the code distribution for DC input and computes the mean and standard deviation.

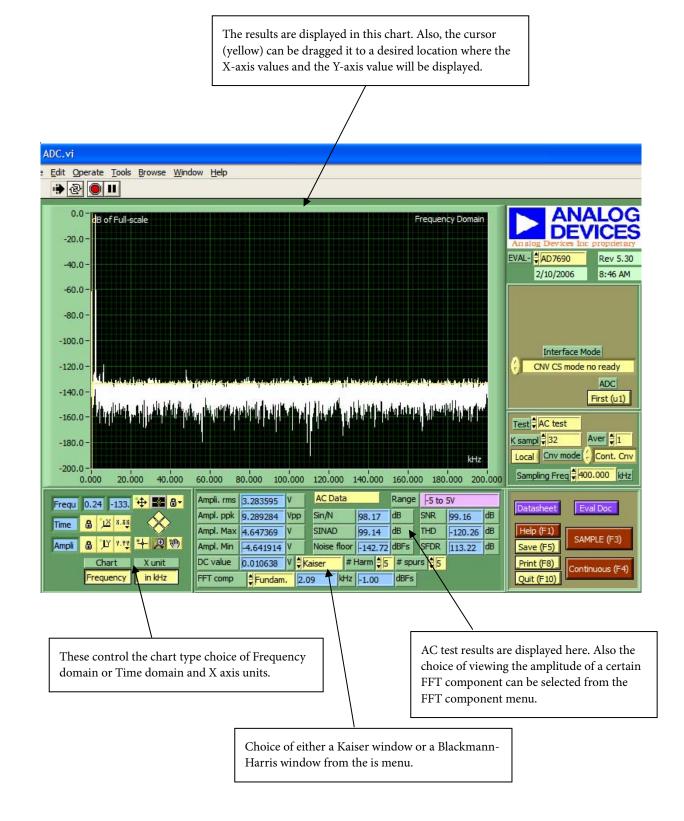

Figure 14 is the FFT Screen, which performs an FFT on the captured data, computes SNR, SINAD and THD.

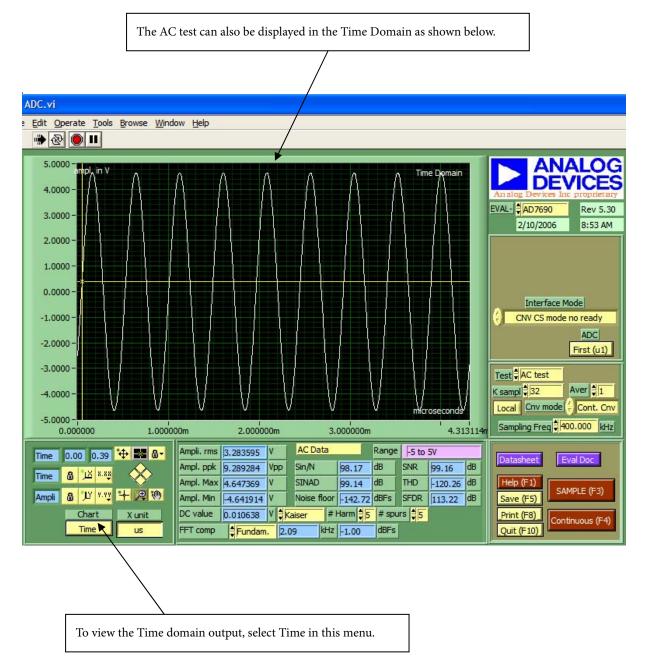

Figure 15 is the time domain representation of the output. When the on-board conversion (CNV) generation is used, a synchronous FFT can be achieved by synchronizing an external AC generator with the 10MHz Fsync signal (J4) a 10 MHz signal, exact division of master clock (MCLK).

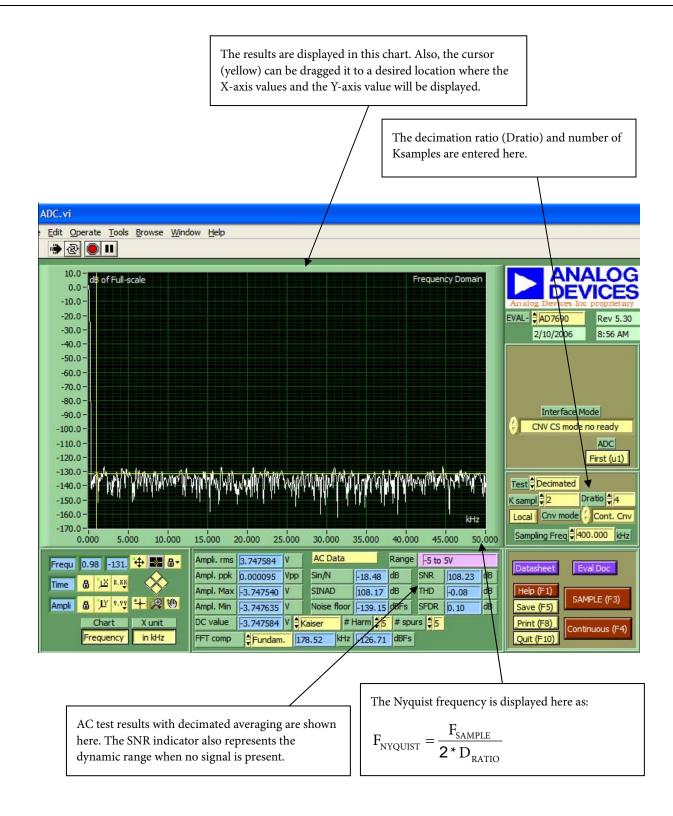

Figure 16 is the FFT Screen when averaging is used.

#### Software Installation (executable)

There is no need to have LabVIEW installed to run the executable.

Double-click on Setup.exe in the LabVIEW exe folder from the CD-ROM shipped with the evaluation board (do not use the CD shipped with the EVAL-CONTROL BRDx) and follow the installation instructions.

#### Developing your own application using LabVIEW

You need LabVIEW 7.1 or above to do this. Install the executable first, copy the folder LabVIEW VI and run the ADC vi example.vi

#### Testing Methods Histogram

To perform a histogram test, apply a DC signal to the input. It is

advised to filter the signal to make the DC Source noise compatible with that of the ADC. C26 and C41 provide this filtering.

#### **AC Testing**

To perform an AC test, apply a sinusoidal signal to the evaluation board. Low distortion, better than 100dB, is required to allow true evaluation of the part. One possibility is to filter the input signal from the AC source. There is no suggested band-pass filter but consideration should be taken in the choice.

#### **Decimated Testing (Averaging)**

This test can be run with a shorted input to evaluate dynamic range or as the AC test.

#### **Setup Requirements**

- EVAL-CONTROL BRDx (ADSP2189)

- EVAL-AD76XXCB 8/10-Pin evaluation board

- Power supply (AC 12V/1A source could be bought from Analog Devices – sold separately from the EVAL-CONTROL BRDx)

- Parallel port cable (provided with the evaluation control board)

- AC source (low distortion)

- DC source (low noise)

- Band-pass filter (value based on the signal frequency, low distortion)

#### Use as a Standalone Evaluation Board

You have the option of using the evaluation board as a standalone. This method does not require the EVAL-CONTROL BRDx, nor does it require use of the accompanied software. The ADC serial interface signals are available on P1 (26-pin connector).

**Table 1. Jumper Description**

| Jumper<br>Designation | Default position with the control board (Factory settings) | Function                                                                                                                                                          |

|-----------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP1                   | AMP+                                                       | Selection of the IN+ analog signal of U1 and U8, ADC0 and ADC1.                                                                                                   |

|                       |                                                            | Position AMP+ = the signal present on JP13, buffered through U6.                                                                                                  |

|                       |                                                            | Position not in AMP+ = optional multiplexer output, DB, is used.                                                                                                  |

| JP2                   | AMP-                                                       | Selection of JP3 source.                                                                                                                                          |

|                       |                                                            | Position AMP- = the signal present on JP25, buffered through U7.                                                                                                  |

|                       |                                                            | Position not in AMP- = optional multiplexer output, DA, is used.                                                                                                  |

| JP3                   | Unip or Diff (see text)                                    | Selection of the IN– analog signal of U1.                                                                                                                         |

|                       |                                                            | Position Unip = single-ended ADC: AD7683, AD7685, AD7694, AD7942, AD7946, AD7980.                                                                                 |

|                       |                                                            | Position Diff = true differential ADC: AD7684, AD7687, AD7688, AD7690, AD7691, AD7693, AD7982.                                                                    |

| JP4                   | ADR43X                                                     | Selection of the reference voltage.                                                                                                                               |

|                       |                                                            | Position ADR43X = on board 5V reference voltage is used.                                                                                                          |

|                       |                                                            | Position VDD = the ADC reference is coming from the VDD supply.                                                                                                   |

| JP5                   | BUF                                                        | Selection of the reference voltage.                                                                                                                               |

|                       |                                                            | Positon NO BUF = refence present on JP4 (ADR43X or VDD) is selected                                                                                               |

|                       |                                                            | Position BUF = buffered reference present on JP4 (ADR43X or VDD) is selected. This buffer (AD8032) can help to filter the VDD when used as the reference voltage. |

| JP6                   | – 5 V                                                      | Selection for negative supply, VDRV.                                                                                                                              |

| JP7                   | 7 V                                                        | Selection for positive supply, VDRV+.                                                                                                                             |

| JP8                   | 12 V                                                       | Selection for reference circuit supply, VREF.                                                                                                                     |

| JP9                   | VDD                                                        | Selection for digital output interface voltage, VIO.                                                                                                              |

| JP10                  | +VA,                                                       | Selection for ADC, U1 and U8 supply VDD.                                                                                                                          |

|                       | +2.5V (for AD798x)                                         |                                                                                                                                                                   |

| JP11                  | 3.3 V                                                      | Selection for FPGA output interface voltage VIO. Must be set at VIO or 3.3V which ever is the lowest.                                                             |

| JP13                  | BUF+                                                       | Selection of JP1 source                                                                                                                                           |

|                       |                                                            | BUF+ = U6 amplifier output.                                                                                                                                       |

|                       |                                                            | SMB+ = direct input from J1, AIN+ (SMB plug).                                                                                                                     |

|                       |                                                            | DIF+ = optional differential amplifer + output.                                                                                                                   |

| JP25                  | BUF-                                                       | Selection of JP2 source                                                                                                                                           |

|                       |                                                            | BUF- = U7 amplifier output.                                                                                                                                       |

|                       |                                                            | SMB- = direct input from J2, AIN-(SMB plug).                                                                                                                      |

|                       |                                                            | DIF- = optional differential amplifer - output.                                                                                                                   |

Table 2. EVAL-AD768x/AD769x/AD794xCB Test Points

| Test Point | Mnemonic | Available Signal        |

|------------|----------|-------------------------|

| TP1        | GND      | Ground                  |

| TP2        | GND      | Ground                  |

| TP3        | SIG+     | ADC Analog input IN+    |

| TP4        | GND      | Ground                  |

| TP5        | REF      | ADC Reference input     |

| TP6        | SDI      | ADC (U1) SDI signal     |

| TP7        | CNV      | ADC CNV signal          |

| TP8        | SCK      | ADC SCK signal          |

| TP9        | SDO      | ADC (U1) SDO signal     |

| TP10       | SDO2     | ADC (U8) SDO signal     |

| TP11       | BBUSY    | Parallel ADC data valid |

| TP12       | GND      | Ground                  |

| TP13       | SIG-     | ADC Analog input        |

Figure 2. Schematic (Analog section)

Rev. Pr G | Page 6 of 18

Figure 3. Schematic (Digital Section)

Rev. Pr G | Page 7 of 18

Figure 4. Schematic (Power Section)

Rev. Pr G | Page 8 of 18

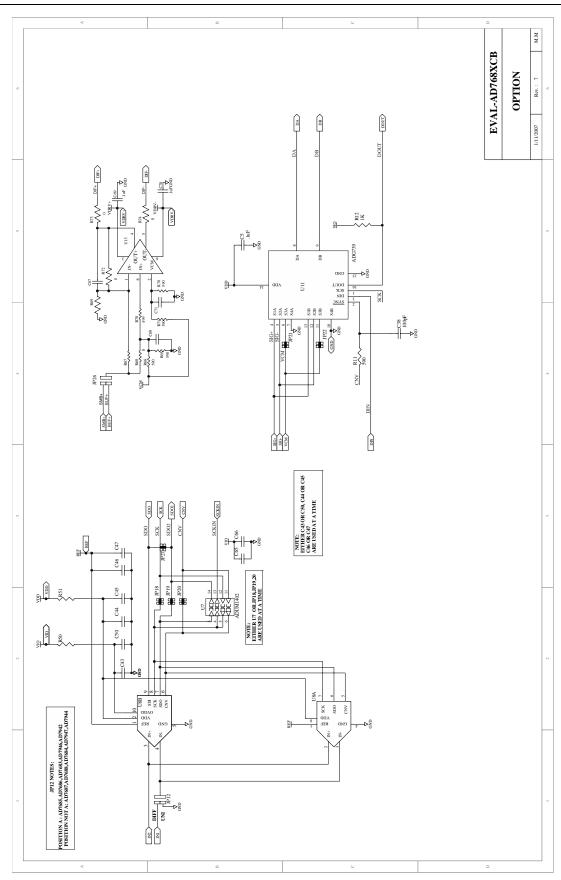

Figure 5. Schematic (Option Section)

Rev. Pr G | Page 9 of 18

Figure 6. Top-Side Silk-Screen (Not to Scale).

Figure 7. Top-Side (Not to Scale).

Figure 8. Ground Layer (Not to Scale).

Figure 9. Shield Layer (Not to Scale).

Figure 10. Bottom-Side Layer (Not to Scale).

Figure 11. Bottom-Side Silk-Screen (Not to Scale).

### **EVAL-AD76XXCB 8/10-Pin**

Figure 12. Setup Screen

The results are displayed in this chart. Also, the cursor

Figure 13. Histogram Screen

Figure 14. FFT Screen

Figure 15. Time-Domain Screen

Figure 16. Decimated (Averaging) Screen

The term AD768x/AD769x/AD794x/AD798x is used in this document to represent all the ADCs listed in the ordering guide.

#### **ORDERING GUIDE**

| <b>Evaluation Board Model</b> | Product          |

|-------------------------------|------------------|

| EVAL-AD7683CBZ                | AD7683BRMZ       |

| EVAL-AD7684CBZ                | AD7684BRMZ       |

| EVAL-AD7685CBZ                | AD7685CRMZ       |

| EVAL-AD7686CBZ                | AD7686CRMZ       |

| EVAL-AD7687CBZ                | AD7687BRMZ       |

| EVAL-AD7688CBZ                | AD7688BRMZ       |

| EVAL-AD7690CBZ                | AD7690BRMZ       |

| EVAL-AD7691CBZ                | AD7691BRMZ       |

| EVAL-AD7693CBZ                | AD7693BRMZ       |

| EVAL-AD7694CBZ                | AD7694BRMZ       |

| EVAL-AD7942CBZ                | AD7942BRMZ       |

| EVAL-AD7946CBZ                | AD7946BRMZ       |

| EVAL-AD7980CBZ                | AD7980BRMZ       |

| EVAL-AD7982CBZ                | AD7982BRMZ       |

| EVAL-CONTROL BRD2             | Controller Board |

| EVAL-CONTROL BRD3             | Controller Board |

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.