# **General Description**

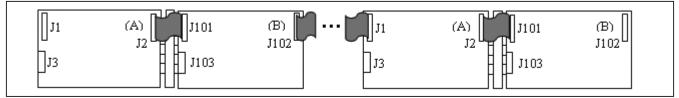

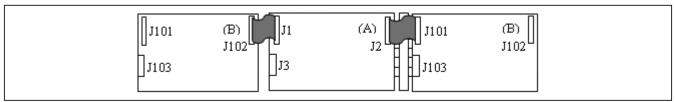

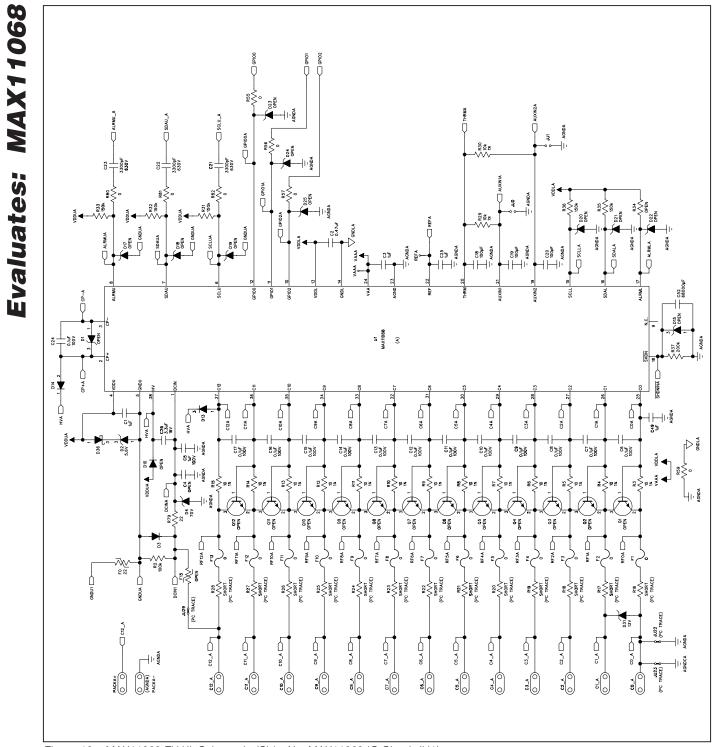

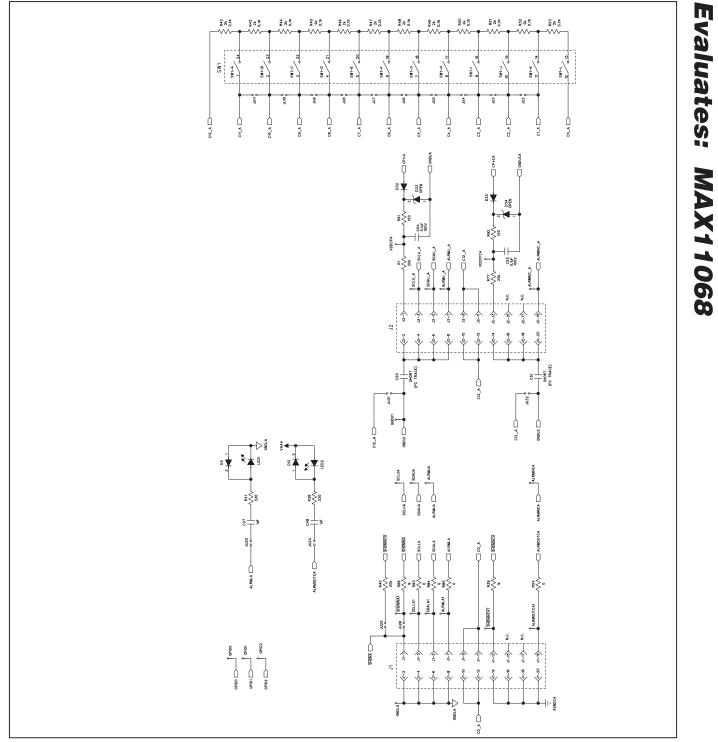

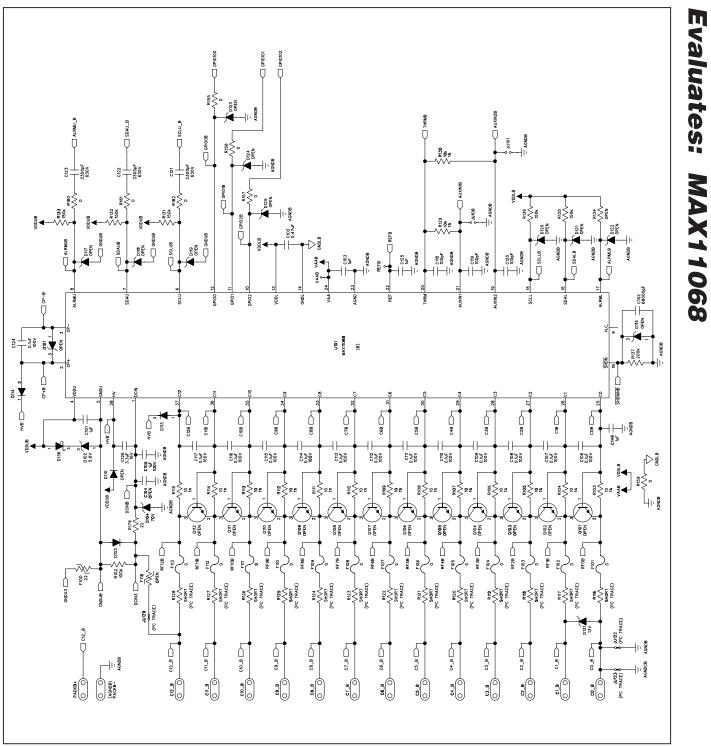

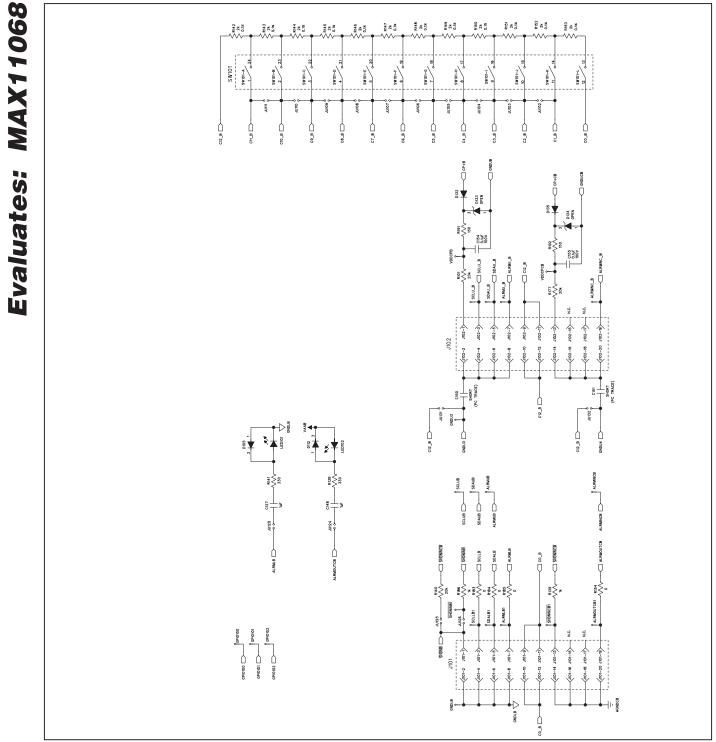

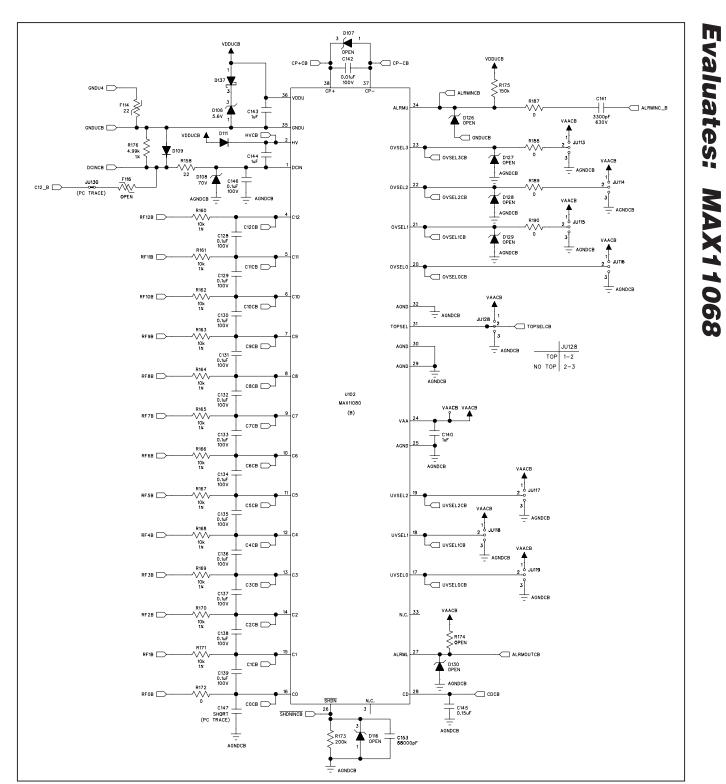

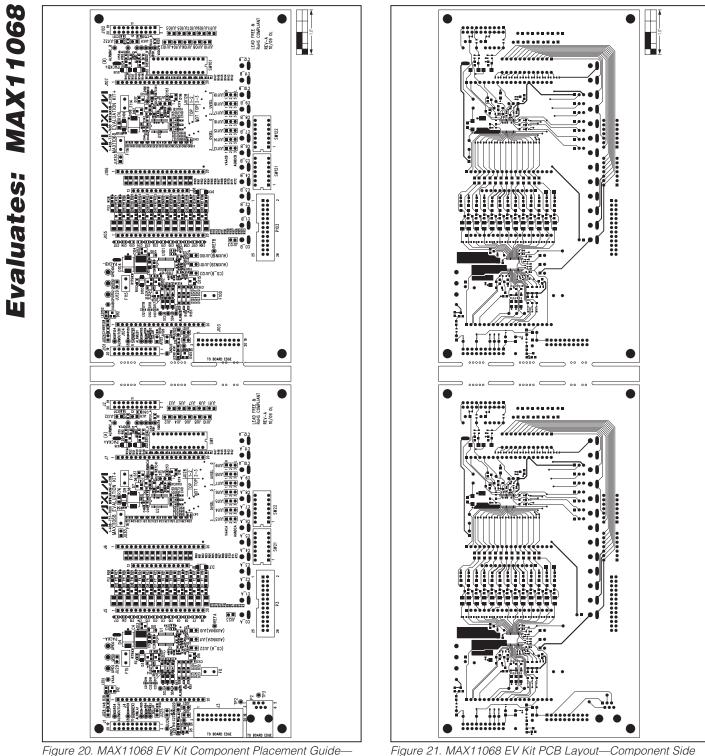

The MAX11068 evaluation kit (EV kit) demonstrates the capabilities of the MAX11068 advanced smart batterypack controller. The EV kit PCB is made up of two boards, each containing nearly identical MAX11068 circuits. The left side of the EV kit is referenced as side (A) and the right side is referenced as side (B). The two-boards-in-one design provides a simple demonstration of the MAX11068's SMBus<sup>™</sup> ladder capability. Additional vertical headers allow for the connection of multiple EV kits, supporting the maximum 31-device ladder capability of the device's I<sup>2</sup>C bus system.

Integrated into the EV kit design are two MAX11080 12-channel high-voltage battery-pack fault monitors. The MAX11080 ICs work in conjunction with the MAX11068 ICs, providing redundant overvoltage and undervoltage monitoring.

The MAX11068 evaluation system (EV system) includes the MAX11068 EV kit and the MINIQUSB command module. The MINIQUSB provides an I<sup>2</sup>C interface to a PC. The supplied command module allows the kit to be evaluated with the MAX11068 EV kit software that can be downloaded from <u>www.maxim-ic.com/evkitsoftware</u>.

# Features

- On-Board Protection Fuse (Optional)

- Battery-Cell String Emulation

- ✤ I<sup>2</sup>C interface (MINIQUSB Connectivity)

- Windows<sup>®</sup> 2000-, Windows XP<sup>®</sup>-, and Windows Vista<sup>®</sup> (32-Bit)-Compatible Software

- Fully Assembled and Tested

# **\_Ordering Information**

| PART                                       | TYPE      |  |  |  |

|--------------------------------------------|-----------|--|--|--|

| MAX11068EVMINIQU+                          | EV System |  |  |  |

| +Denotes lead(Pb)-free and RoHS compliant. |           |  |  |  |

# Component Lists

# MAX11068 EV System

| PART           | QTY | DESCRIPTION          |

|----------------|-----|----------------------|

| MAX11068EVKIT+ | 1   | MAX11068 EV kit      |

| MINIQUSB+      | 1   | Maxim command module |

SMBus is a trademark of Intel Corp. Windows, Windows XP, and Windows Vista are registered trademarks of Microsoft Corp.

#

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# \_Component Lists (continued)

# MAX11068 EV Kit

|                                                                                                                                                                       |                                                                             |                                                                                                    |                                                                                                |     | MAX11068 EV KI                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DESIGNATION                                                                                                                                                           | QTY                                                                         | DESCRIPTION                                                                                        | DESIGNATION                                                                                    | QTY | DESCRIPTION                                                                                                                                                                         |

| ALRMINC_A,<br>ALRMINC_B,<br>ALRMINCA,<br>ALRMINCB,                                                                                                                    | LRMINC_B,<br>LRMINCA,                                                       |                                                                                                    | C5, C105                                                                                       | 2   | 1µF ±10%, 100V X7R ceram-<br>ic capacitors (1206)<br>Murata GRM31CR72A105KA<br>TDK C3216X7R2A105K                                                                                   |

| ALRMLA1,<br>ALRMLB1,<br>ALRMOUTCA1,<br>ALRMOUTCB1,<br>ALRMU_A,                                                                                                        |                                                                             |                                                                                                    | C6-C17, C24, C28-<br>C39, C46, C54,<br>C55, C106-C117,<br>C124, C128-C139,<br>C146, C154, C155 | 56  | 0.1µF ±10%, 100V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R72A104KA                                                                                                         |

| ALRMU_B,<br>ALRMUA, ALRMUB,<br>GNDLA, GNDLB,<br>GNDU1, GNDU3,<br>REFA, REFB,                                                                                          |                                                                             |                                                                                                    | C18, C19, C20,<br>C118, C119, C120                                                             | 6   | 100pF ±5%, 50V C0G<br>ceramic capacitors (0402)<br>Murata GRM1555C1H101J<br>TDK C1005C0G1H101J                                                                                      |

| SCLLA1, SCLLB1,<br>SCLU_A, SCLU_B,<br>SCLUA, SCLUB,<br>SDALA1, SDALB1,<br>SDAU_A, SDAU_B,<br>SDAUA, SDAUB,<br>SHDNINA1,<br>SHDNINB1,<br>SHDNINCA1,<br>SHDNINCB1, TP2, | 44                                                                          | 44 Miniature test points                                                                           | C21, C22, C23,<br>C41, C121, C122,<br>C123, C141                                               | 8   | 3300pF, 630V ceramic<br>capacitors (1206)<br>TDK C3216C0G2J332J<br>(±5%, C0G)<br>Murata GRM31BR72J332KW<br>(±10%, X7R)<br>Murata GCJ31BR72J332K<br>(±10%, X7R, automotive<br>grade) |

| TP3, VAAA, VAAB,<br>VAACA, VAACB,<br>VDDCPA, VDDCPB,<br>VDDCPCA,                                                                                                      |                                                                             |                                                                                                    | C26, C126                                                                                      | 2   | 3.3µF ±10%, 16V X7R<br>ceramic capacitors (0805)<br>Murata GRM21BR71C335K                                                                                                           |

| VDDCPCB<br>C1, C3, C25, C27,                                                                                                                                          |                                                                             |                                                                                                    | C42, C142                                                                                      | 2   | 0.01µF ±10%, 100V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R72A103KA                                                                                                        |

| C40, C43, C44,<br>C48, C49, C101,<br>C103, C125, C127,<br>C140, C143, C144,<br>C148, C149                                                                             | C40, C43, C44,<br>C48, C49, C101,<br>C103, C125, C127,<br>C140, C143, C144, | 1μF ±10%, 16V X7R ceramic<br>capacitors (0603)<br>Murata GRM188R71C105K<br>TDK C1608X7R1C105K      | C45, C145                                                                                      | 2   | 0.15µF ±10%, 10V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R71A154KA<br>TDK C1608X7R1E154K<br>(50V)                                                                          |

| C2, C102                                                                                                                                                              | 2                                                                           | 0.47µF ±10%, 6.3V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R70J474KA<br>TDK C1608X7R1C474K | C47, C50, C51,<br>C147, C150, C151                                                             | 0   | Not installed, ceramic<br>capacitors—short (PC trace)<br>(0603)                                                                                                                     |

| C4, C104                                                                                                                                                              | 0                                                                           | (16V)<br>Not installed, ceramic<br>capacitors (2220)                                               | C52, C53, C152,<br>C153                                                                        | 4   | 68000pF ±5%, 16V X7R<br>ceramic capacitors (0603)<br>Murata GRM188R71C683K                                                                                                          |

| DESIGNATION                                                             | QTY | DESCRIPTION                                                                                  |

|-------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------|

| D1, D7, D15, D16,<br>D33, D34, D101,<br>D107, D115, D116,<br>D133, D134 | 0   | Not installed, zener diodes<br>(SOT23)                                                       |

| D2, D6, D102,<br>D106                                                   | 4   | 5.6V zener diodes (SOT23)<br>Fairchild MMBZ5232B<br>Diodes Inc. MMBZ5232B-7-F                |

| D3, D9, D103,<br>D109                                                   | 4   | 1A, 100V diodes (SMA)<br>Fairchild S1B<br>Diodes Inc. US1B-13-F                              |

| D4, D8, D104,<br>D108                                                   | 4   | 70V zener transient-<br>voltage suppressors (SMC)                                            |

| D5, D12, D13,<br>D105, D112, D113                                       | 6   | Signal diodes (SOT23)<br>Central Semi CMPD1001                                               |

| D10, D110                                                               | 0   | Not installed, signal diodes<br>(SOD123)                                                     |

| D11, D14, D111,<br>D114                                                 | 4   | 100V small-signal diodes<br>(SOD123)<br>Fairchild MMSD4448<br>Diodes Inc. BAY19W-7-F         |

| D17, D18, D19,<br>D26–D29, D117,<br>D118, D119,<br>D126–D129            | 0   | Not installed, zener diodes<br>(SOD123)                                                      |

| D20–D25, D30,<br>D120–D125, D130                                        | 0   | Not installed, zener diodes<br>(SOD123)                                                      |

| D31, D131                                                               | 2   | 13V zener diodes (SMA)<br>Central Semi CMZ5928B                                              |

| D32, D35, D132,<br>D135                                                 | 4   | 1A rectifier diodes (SMA)<br>Fairchild S1A                                                   |

| D36, D37, D136,<br>D137                                                 | 4   | 100V Schottky diodes<br>(SOT23)<br>STMicro BAT46FILM<br>Vishay BAS70-00-V                    |

| F0, F14, F100, F114                                                     | 4   | 22Ω resistors (axial)<br>Optional: PolySwitch <sup>®</sup> , PTC<br>resettable fuse (radial) |

| F1–F13, F101–F113                                                       | 26  | $0\Omega$ resistors (1206)<br>Optional: 250mA fast-acting<br>chip fuse (1206)                |

# Component Lists (continued)

| MAX11068 EV Kit (continued)                                                                                                                           |                             |                                                           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------|--|--|--|

| DESIGNATION                                                                                                                                           | QTY                         | DESCRIPTION                                               |  |  |  |

| F15, F16, F115,<br>F116                                                                                                                               | 0                           | Not installed, resettable fuses (radial)                  |  |  |  |

| GPIO0, GPIO1,<br>GPIO2, GPIO100,<br>GPIO101, GPIO102                                                                                                  | 100, 6 Multipurpose test po |                                                           |  |  |  |

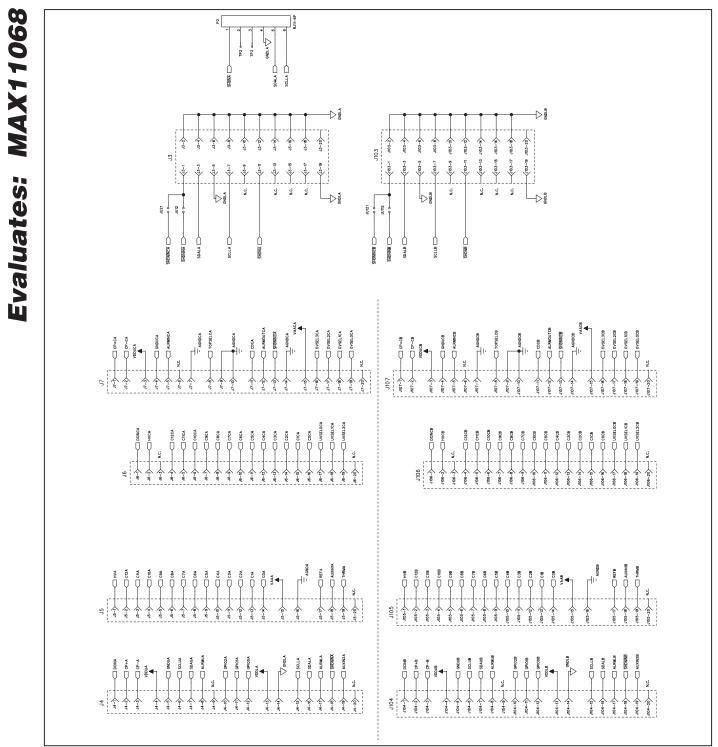

| J1, J2, J101, J102                                                                                                                                    | 4                           | 20-pin (2 x 10) dual-row<br>headers, 0.1in centers        |  |  |  |

| J3, J103                                                                                                                                              | 2                           | 2 x 10 right-angle<br>receptacles                         |  |  |  |

| J4–J7, J104–J107                                                                                                                                      | 0                           | Not installed, 20-pin<br>headers, 0.1in centers           |  |  |  |

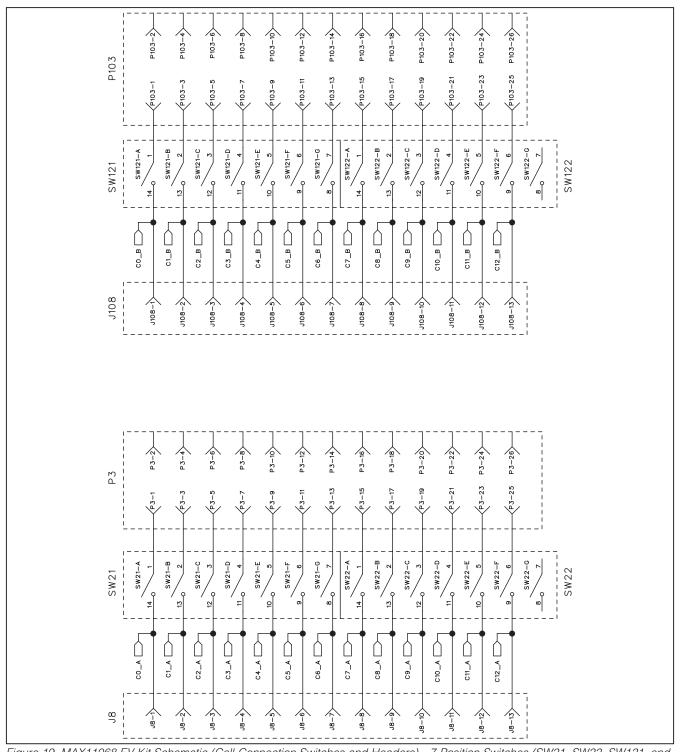

| J8, J108                                                                                                                                              | 2                           | 13-pin headers, 0.1in cen-<br>ters                        |  |  |  |

| JU0–JU11, JU12,<br>JU20, JU21, JU24,<br>JU25, JU26,<br>JU31, JU32,<br>JU100–JU111,<br>JU112, JU120,<br>JU121, JU124,<br>JU125, JU126,<br>JU131, JU132 | 40                          | 2-pin headers, 0.1in centers                              |  |  |  |

| JU13–JU19, JU28,<br>JU113–JU119,<br>JU128                                                                                                             | 16                          | 3-pin headers, 0.1in centers                              |  |  |  |

| JU22, JU23, JU29,<br>JU30, JU122,<br>JU123, JU129,<br>JU130                                                                                           | 0                           | Not installed, 2-pin<br>headers, 0.1in centers            |  |  |  |

| LED1, LED2,<br>LED101, LED102                                                                                                                         | 4                           | Surface-mount LEDs (0805)                                 |  |  |  |

| P2                                                                                                                                                    | 0                           | Not installed, RJ-11 jack<br>(R/A 6 positions/6 contacts) |  |  |  |

| P3, P103                                                                                                                                              | 2                           | 2 x 13-pin shrouded head-<br>ers, 0.1in centers           |  |  |  |

| Q1–Q12, Q101–<br>Q112                                                                                                                                 | 0                           | Not installed, npn bipolar<br>transistors (SOT23)         |  |  |  |

| R1, R101                                                                                                                                              | 2                           | $0\Omega$ resistors (0603)                                |  |  |  |

| R2, R102                                                                                                                                              | 2                           | 100k $\Omega$ ±5% resistors (0603)                        |  |  |  |

| R3–R15, R103–<br>R115                                                                                                                                 | 26                          | 10Ω ±1%, 1/2W resistors<br>(1210)                         |  |  |  |

PolySwitch is a registered trademark of Tyco International Ltd.

# Component Lists (continued)

| DESIGNATION                                                                       | QTY                                       | DESCRIPTION                                          |

|-----------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------|

| R16–R28, R116–<br>R128                                                            | 0                                         | Not installed, resistors—<br>short (PC trace) (0805) |

| R29, R30, R129,<br>R130                                                           | 4                                         | $10k\Omega \pm 1\%$ resistors (0402)                 |

| R31, R32, R33,<br>R35, R36, R75,<br>R131, R132, R133,<br>R135, R136, R175         | R75,<br>R133, 12 150kΩ ±5% resistors (040 |                                                      |

| R34, R74, R134,<br>R174                                                           | 0                                         | Not installed, resistors (0402)                      |

| R37, R137                                                                         | 2                                         | 200k $\Omega$ ±5% resistors (0603)                   |

| R38, R41, R138,<br>R141                                                           | 4                                         | 330Ω ±5%, 1/8W resistors<br>(0805)                   |

| R39, R86, R139,<br>R186                                                           | 4                                         | 1k $\Omega$ ±5% resistors (0402)                     |

| R40, R140                                                                         | 2                                         | 20k $\Omega$ ±5% resistors (0402)                    |

| R42–R53, R142–<br>R153                                                            | 24                                        | $2k\Omega \pm 0.1\%$ resistors (0603)                |

| R54–R57, R59,<br>R80–R85, R87–R90,<br>R154–R157, R159,<br>R180–R185,<br>R187–R190 | 30                                        | $0\Omega$ resistors (0402)                           |

# MAX11068 EV Kit (continued)

| DESIGNATION                 | QTY | DESCRIPTION                                                            |

|-----------------------------|-----|------------------------------------------------------------------------|

| R58, R79, R158,<br>R179     | 4   | $22\Omega \pm 5\%$ resistors (0402)                                    |

| R60–R71,<br>R160–R171       | 24  | 10kΩ ±1%, 1/4W resistors<br>(1206)                                     |

| R72, R172                   | 2   | $0\Omega$ resistors (1206)                                             |

| R73, R173                   | 2   | 200k $\Omega$ ±5% resistors (0402)                                     |

| R76, R176                   | 2   | $4.99$ k $\Omega \pm 1\%$ resistors (1206)                             |

| R77, R177                   | 2   | 20k $\Omega$ ±5% resistors (0603)                                      |

| R91, R92, R191,<br>R192     | 4   | $150\Omega \pm 5\%$ resistors (0603)                                   |

| SW1, SW101                  | 2   | 12-position SPST DIP<br>switches                                       |

| SW21, SW22,<br>SW121, SW122 | 4   | 7-position SPST DIP switch-<br>es                                      |

| U1, U101                    | 2   | Daisy-chainable analog<br>front-ends (38 TSSOP)<br>MAX11068GUU+        |

| U2, U102                    | 2   | High-voltage battery-pack<br>fault monitors (38 TSSOP)<br>MAX11080GUU+ |

|                             | 56  | Shunts                                                                 |

|                             | 1   | PCB: MAX11068<br>EVALUATION KIT+                                       |

# **Component Suppliers**

| SUPPLIER                               | PHONE        | WEBSITE                     |

|----------------------------------------|--------------|-----------------------------|

| Central Semiconductor Corp.            | 631-435-1110 | www.centralsemi.com         |

| Diodes Incorporated                    | 805-446-4800 | www.diodes.com              |

| Fairchild Semiconductor                | 888-522-5372 | www.fairchildsemi.com       |

| Murata Electronics North America, Inc. | 770-436-1300 | www.murata-northamerica.com |

| STMicroelectronics                     | 408-452-8585 | www.us.st.com               |

| TDK Corp.                              | 847-803-6100 | www.component.tdk.com       |

| Vishay                                 | 402-563-6866 | www.vishay.com              |

Note: Indicate that you are using the MAX11068 when contacting these component suppliers.

# MAX11068 EV Kit Files

| FILE                 | DESCRIPTION                                |  |  |

|----------------------|--------------------------------------------|--|--|

| INSTALL.EXE          | Installs the EV kit files on your computer |  |  |

| MAX11068.EXE         | Application program                        |  |  |

| 11068config.csv      | MAX11068 GUI configuration file            |  |  |

| Revision History.txt | Software revision history (read only)      |  |  |

| FTD2XX.INF           | USB device driver file                     |  |  |

| UNINST.INI           | Uninstalls the EV kit software             |  |  |

| USB_Driver_Help.PDF  | USB driver installation help file          |  |  |

# \_Quick Start

# **Recommended Equipment**

MAX11068 EV system

MAX11068 EV kit

MINIQUSB+ command module

MINIQUSB board

MINIQUSB-XHV board

- 6V to 60V dual DC power supplies (refer to the MAX11068 and MAX11080 IC data sheets for recommended operating ranges)

- User-supplied Windows 2000, Windows XP, or Windows Vista PC with a spare USB port

**Note:** In the following sections, software-related items are identified by bolding. Text in **bold** refers to items directly from the EV kit software. Text in **bold and under**<u>lined</u> refers to items from the Windows operating system.

### **Procedure**

The EV kit is fully assembled and tested. Follow the steps below to verify board operation. Caution: Do not plug in the power adapter until all connections are completed.

- Visit <u>www.maxim-ic.com/evkitsoftware</u> to download the latest version of the EV kit software, 11068Rxx.ZIP. Save the EV kit software to a temporary folder and uncompress the ZIP file.

- Install the EV kit software on your computer by running the INSTALL.EXE program inside the temporary folder. The program files are copied and icons are created in the Windows <u>Start I Programs</u> menu.

- Connect the MINIQUSB board to the MINIQUSB-XHV board.

- Connect the USB cable from the PC to the MINIQUSB board. A <u>Building Driver Database</u> window pops up in addition to a <u>New Hardware Found</u> message if this is the first time the EV kit board is connected

to the PC. If a window is not seen that is similar to the one described above after 30s, remove the USB cable from the MINIQUSB and reconnect it. Administrator privileges are required to install the USB device driver on Windows 2000, Windows XP, and Windows Vista.

- 5) Follow the directions of the <u>Add New Hardware</u> <u>Wizard</u> to install the USB device driver. Choose the <u>Search for the best driver for your device</u> option. Specify the location of the device driver to be <u>C:\Program Files\MAX11068</u> (default installation directory) using the <u>Browse</u> button. Refer to the USB\_Driver\_Help.PDF document included with the software for additional information.

- 6) Ensure that all jumper shunts are installed in the default positions, as shown in Table 1.

- 7) Verify that all switches are configured, as shown in Table 2.

- 8) Ensure that a ribbon cable is connected between headers J2 and J101.

- 9) Configure the DC power supplies for 18V each. The power supplies should be isolated. Refer to the MAX11068 and MAX11080 IC data sheets for valid device operating ranges. The MAX11080 also has a minimum per-cell voltage requirement.

- 10) Connect one 18V supply between the PACKA+ and PACKA- PCB pads and the other 18V supply between the PACKB+ and PACKB- PCB pads, respectively.

- 11) Connect the MINIQUSB-XHV board's P3 header to the EV kit's J3 header. The boards should be flush with one another.

- 12) Enable both of the DC power supplies.

- Start the EV kit software by opening its icon in the <u>Start I Programs</u> menu. The EV kit software main window appears, as shown in Figure 7.

- 14) The EV kit software automatically establishes a connection with the EV kit. Once the status bar at the bottom of the window displays **Interface found**, proceed to the next step.

- 15) If checked, uncheck the **SHDN** checkbox.

- 16) Press the Hello ALL button.

- 17) Press the **Roll Call** button once it is activated.

- 18) Press the **Set Last Address** button once it is activated.

- 19) Verify that the **Device Addresses (0x01)** grid contains two device addresses and the status bar at the bottom indicates **Initialization Successful**.

- 20) The EV kit is now ready for further evaluation.

# \_Detailed Description of Software

The MAX11068 EV kit is evaluated in conjunction with the MAX11068 evaluation software. The graphical user interface (GUI) provides a friendly environment for reading and writing to all device registers, as well as executing the seven device commands. The GUI is divided into three sections, **Initialization** group box, register tabs, and command tabs.

The **Initialization** group box provides controls for the HELLOALL, ROLLCALL, and SETLASTADDRESS commands, as well as device-shutdown capability. The command tabs, located in the upper-right section of the GUI, provide controls for executing the WRITEALL, READALL, and STROBEALL commands. This group of tabs also includes a **Device Address** grid that displays

# **Table 1. Default Jumper Settings**

| JUMPER                                                                                                | SHUNT POSITION  |  |  |  |

|-------------------------------------------------------------------------------------------------------|-----------------|--|--|--|

| JU0, JU1, JU20, JU24, JU25, JU26,<br>JU100, JU101, JU120, JU124, JU125,<br>JU126, JU128, JU131, JU132 | 1-2             |  |  |  |

| JU2–JU11, JU12, JU21,<br>JU102–JU112, JU121                                                           | On one pin only |  |  |  |

| JU13, JU16, JU18, JU19, JU113,<br>JU116, JU118, JU119                                                 | 1-2             |  |  |  |

| JU14, JU15, JU17, JU28, JU114,<br>JU115, JU117                                                        | 2-3             |  |  |  |

*Note:* Jumper designators JU27 and JU127 are not used on this EV kit.

the address of each device in the SMBus ladder, a **Communication Log** that displays a summary of bus activity, and a **Short Cuts** tab that provides faster ways of executing useful software functions.

The seven register tabs provide access to all the devices in the SMBus ladder. Each tab includes a grid that is used to display the contents read from the registers. The grid is made of x columns and y rows, where x is the number of registers (shown above each grid) associated with that tab and y is the number of devices in the SMBus ladder. In addition, each tab includes various controls (checkboxes, edit boxes, buttons, labels, etc.) for configuring each device. Refer to the *I*<sup>2</sup>*C Interface* and *Register Map* sections in the MAX11068 IC data sheet for additional interface and register details.

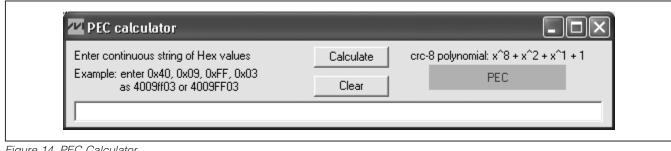

The software also provides a few functions to facilitate the evaluation process. These include a PEC calculator, the capability to save ADC measurements to file, and the ability to save/load register configurations to/from a file. When evaluating the EV kit, the MAX11068 IC data sheet should also be referenced for additional details.

### System Initialization

The SMBus ladder of the EV kit is initialized using the controls provided in the **Initialization** group box on the EV kit software GUI. The recommended initialization sequence is as follows:

- 1) Verify that jumpers JU12, JU25, and JU26 are configured correctly. See the *Device Startup* section.

- 2) Uncheck the **SHDN** checkbox.

# **Table 2. Quick-Start Switch Settings**

| SWITCH                      | SETTING                 |

|-----------------------------|-------------------------|

| SW1, SW101                  | Off (towards the right) |

| SW21, SW22, SW121,<br>SW122 | On (upwards)            |

# Table 3. HELLOALL Command Byte

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 1     | 1     | A0    | A1    | A2    | A3    | A4    | 0     |

- Enter or select the HELLOALL command byte (Table 3) into the combo box adjacent to the Hello ALL button.

- The value entered here contains the address (A[0:4]), least significant bit (LSB) first, of the first device in the SMBus ladder. The A[0:4] value is written to the ADDRESS register of the first device.

- Refer to the *HELLOALL Command* section in the MAX11068 IC data sheet for additional details.

- 4) Press the **Hello ALL** button. Once this command has been executed the **Roll Call** button is enabled.

- 5) Press the **Roll Call** button to determine the number of MAX11068 devices in the SMBus ladder.

- This button sends the ROLLCALL command down the I<sup>2</sup>C bus instructing all devices to send both bytes of their ADDRESS register (0x01). The ROLLCALL command consists of a sequence of 3 bytes sent by the host to the first device.

- When this command sequence is completed, the host determines the address of the last device and the total number of devices in the SMBus ladder. The number of devices is displayed in the **Device Count** edit box.

- See Table 4 and also refer to the *ROLLCALL Command* section in the MAX11068 IC data sheet for additional details.

The BROADCAST address (B[7:1]) is used by the ROLLCALL command and is by default set to 0x40 (0b0100000). After the first initialization of the SMBus ladder, the BROADCAST address can be changed. Refer to the *Address Byte Encoding* sec-

Table 4. ROLLCALL Command

| BROA                     | DCAST                    | ADDRE | ESS (Wi       | tite) |       |       |       |  |  |  |

|--------------------------|--------------------------|-------|---------------|-------|-------|-------|-------|--|--|--|

| Bit 7                    | Bit 6                    | Bit 5 | Bit 4 Bit 3 B |       | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| B7                       | B6                       | B5    | B4            | B3    | B2    | B1    | 0     |  |  |  |

| ADDR                     | ADDRESS REGISTER ADDRESS |       |               |       |       |       |       |  |  |  |

| Bit 7                    | Bit 6                    | Bit 5 | Bit 4         | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| 0                        | 0                        | 0     | 0             | 0     | 0     | 0     | 1     |  |  |  |

| BROADCAST ADDRESS (Read) |                          |       |               |       |       |       |       |  |  |  |

| Bit 7                    | Bit 6                    | Bit 5 | Bit 4         | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

| B7                       | B6                       | B5    | B4            | B3    | B2    | B1    | 1     |  |  |  |

tion in the MAX11068 IC data sheet for complete BROADCAST address details.

Once the address of the last device on the stack is known, the host can issue the SETLASTADDRESS command. The SETLASTADDRESS command should only be issued after the ROLLCALL command has been issued and its sequence is complete.

- 6) Press the Set Last Address button.

- This command writes the address of the last device (LA[4:0]) to the upper 8 bits of each device's 16-bit ADDRESS register. The SETLASTADDRESS command consists of a sequence of 5 bytes sent by the host to the first device.

- See Table 5 and refer to the SETLASTADDRESS Command section in the MAX11068 IC data sheet.

The SMBus ladder has been initialized once all devices have been programmed with the address of the last device. The software is now fully operational and all active devices are configurable. Refer to the *I*<sup>2</sup>*C/SMBus Ladder Initialization Sequence* section in the MAX11068 IC data sheet for additional initial configuration recommendations.

Table 5. SETLASTADDRESS Command

| BROA                                            | BROADCAST ADDRESS (Write)                                     |   |   |   |                     |   |        |  |  |  |  |  |  |

|-------------------------------------------------|---------------------------------------------------------------|---|---|---|---------------------|---|--------|--|--|--|--|--|--|

| Bit 7                                           |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| B7                                              |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| ADDRESS REGISTER ADDRESS                        |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| 0                                               | 0 0 0 0 0 0 0 1                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| ADDRESS REGISTER (Upper 8 bits)                 |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| Bit 15                                          | 15 Bit 14 Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit               |   |   |   |                     |   |        |  |  |  |  |  |  |

| 0                                               | 0 0 0 LA4 LA3 LA2 LA1 LA0                                     |   |   |   |                     |   |        |  |  |  |  |  |  |

| ADDRESS REGISTER (Lower 8 bits)                 |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| Bit 7                                           | Bit 7   Bit 6   Bit 5   Bit 4   Bit 3   Bit 2   Bit 1   Bit 0 |   |   |   |                     |   |        |  |  |  |  |  |  |

| Х                                               | Х                                                             | Х | Х | Х | Х                   | Х | Х      |  |  |  |  |  |  |

| PEC BYTE*                                       |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |                                                               |   |   |   |                     |   |        |  |  |  |  |  |  |

| 8-bit v                                         | -                                                             |   | - |   | ng the f<br>and sec | - | tes of |  |  |  |  |  |  |

\*See the PEC Byte section. X = Don't care.

### **Grid Initialization**

When the SETLASTADDRESS command sequence is complete, the software updates the grids on the **Device** Addresses (0x01) tab and the Thresholds, Voltage Measurement, AIN/DIAG/FMEA, Alert/Status, Enables, Configuration, and Broadcast/Version/Freq tabs.

### Device Addresses Grid

The **Device Addresses (0x01)** tab is initialized after pressing the **Set Last Address** button. The grid contains the addresses of all the detected devices. Selecting a cell that contains a device address updates the **Active Device** drop-down list. For a two-device ladder with a start address of 0x01, the grid would be displayed as shown in Figure 1.

**Note:** A device's address is contained in the lower byte of its ADDRESS register (bit[5:1]), specified LSB first. A device address of 0x01 (A[4:0]) would be stored in the

device's ADDRESS register as 0xA0 (A[0:4]). This relationship is displayed in the **Active Device** drop-down list.

### **Register Grids**

The Thresholds, Voltage Measurement, AIN/DIAG/ FMEA, Alert/Status, Enables, Configuration, and Broadcast/Version/Freq tabs all include grids that display the contents of the selected device registers. These tabs are all updated to contain n number of rows, where n equals the total number of detected devices.

For a two-device ladder with a start address of 0x01, the grids on each tab are configured with two rows, as shown in Figure 2. The number of columns in each grid is set by the number of registers associated with that grid. In addition, each row has an associated device number button that, when pressed, sets that device as the active device, updating the **Active Device** drop-down list.

# Table 6. ADDRESS Register

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| 0      | 0      | 0      | LA4    | LA3    | LA2    | LA1   | LA0   |

| Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 1      | 0      | AO     | A1     | A2     | A3     | A4    | 0     |

| Write<br>Active | Device 1    | : 0x01 (0xA  | 0)       | •          | Active Reg | ister (    | 0x01       |

|-----------------|-------------|--------------|----------|------------|------------|------------|------------|

| Device A        | ddresses (C | )x01)   Writ | e   Read | l/Scan∫ Co | ommunicati | on Log   S | ihort Cuts |

| 1: 0x01         | 2: 0x02     |              |          |            |            |            |            |

|                 |             |              |          |            |            |            |            |

|                 |             |              |          |            |            |            |            |

|                 |             |              |          |            |            |            |            |

|                 |             |              |          |            |            |            |            |

Figure 1. MAX11068 EV Kit Software (Device Address Grid)

| 1   |      |      |  |

|-----|------|------|--|

|     | <br> | <br> |  |

| 2 1 |      |      |  |

Figure 2. MAX11068 EV Kit Software (Device Rows)

|                       | Write       Active Device     1: 0x01 (0x40)       ▼     Active Register |

|-----------------------|--------------------------------------------------------------------------|

|                       | Device Addresses (0x01) Write Read/Scan Communication Log Short Cuts     |

|                       | Single Device All Devices                                                |

|                       | Data: 0x Data: 0x                                                        |

|                       | Write Active Device Write All Devices                                    |

|                       |                                                                          |

| ure 3. Write to Regis | ster Controls                                                            |

| Device Addresses (0x01)       Write       Read/Scan       Communication Log       Short Cuts         Read All Selected       Data Check Byte:       0x??       ALRM       PECERR         Refresh F8       Enable Auto Refresh on tab change       Active Tab         Broadcast/Version/Freq         Enable ADC Scanning:       Interval (msec):       10 | Write     Active Device     1: 0x01 (0xA0)     Active Register     0x01           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Head All Selected       Data Check Byte:       0x??       0       0         Refresh F8       Enable Auto Refresh on tab change       Active Tab<br>Broadcast/Version/Freq                                                                                                                                                                                | Device Addresses (0x01) Write Read/Scan Communication Log Short Cuts              |

| Refresh F8 Enable Auto Refresh on tab change Broadcast/Version/Freq                                                                                                                                                                                                                                                                                      | Read All Selected     Data Check Byte:     0x??     ALRM     PECERR       0     0 |

| Enable ADC Scanning: 🥅 Interval (msec): 10 Set Interval                                                                                                                                                                                                                                                                                                  | Defeate COLL Country Auto Defeate an table shows                                  |

|                                                                                                                                                                                                                                                                                                                                                          | Enable ADC Scanning: 🔲 Interval (msec): 10 Set Interval                           |

Figure 4. Read/Scan Tab Snapshot

### Write Registers

A specific device in the SMBus ladder can be written to by using the **Write** tab, **Active Register** group box, and **Active Device** drop-down list. To perform a write to a specific register of a single device:

- Select the device to be written to from the Active Device drop-down list or from the grid on the Device Addresses (0x01) tab.

- Select the register to be written to from the Active Register group box. The Active Register label also reflects the selected register.

- Enter the hex value (####) into the Data: 0x edit box in the Single Device group box (Figure 3).

- 4) Press the Write Active Device button.

The **Write** tab can also be used to write an entered value into the active register of all the devices in the SMBus ladder. To perform a write to a specific register of all devices:

- 1) Select the register to be written to from the **Active Register** group box.

- Enter the hex value (####) into the Data: 0x edit box in the All Devices group box.

- 3) Press the Write All Devices button.

### **Read Registers**

When performing a read operation, all the devices in the SMBus ladder are accessed. The read operation does not allow only one device to be read. The register checkboxes located on each register tab can be selected to enable a read of the associated register. In addition, each group of register checkboxes has an associated **ALL** checkbox that, when checked/unchecked, selects/ deselects all the register checkboxes on that tab. The select all and deselect all operations can also be executed by selecting the **Actions I Active Tab I Select All Ctrl+A** or **Actions I Active Tab I Select None Ctrl+N** menu item. The read operations are performed using the controls on the **Read/Scan** tab or the keyboard short-

|                | CELLEN    | GPIO      | _      | ACQCFG |

|----------------|-----------|-----------|--------|--------|

| ALL     Device | ✓<br>0x09 | ا<br>A0x0 | ox0B   | Ux0C   |

|                | 0000x0    |           | 0x0000 |        |

| 2              | 0x0000    |           | 0x0000 |        |

Figure 5. Configuration Grid after Executing "Read All Selected"

# Table 7. Read Controls

| CONTROL NAME                                        | CONTROL TYPE         | FUNCTION                                                                                                                                        |

|-----------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Read All Selected<br>Actions I Read All Selected F7 | Button,<br>Menu item | Reads all the selected registers. A register is selected by checking its associated register checkbox.                                          |

| Data Check Byte                                     | Label                | Displays the contents of the data check byte as a hex value                                                                                     |

| ALRM, PECERR                                        | Labels               | Displays the status of the ALRM and PECERR bits of the data check byte                                                                          |

| Actions   Read All Registers                        | Menu item            | Read all registers of all devices in the SMBus ladder, regardless of the state of the register checkboxes                                       |

| Refresh F8<br>Actions   Refresh F8                  | Button,<br>Menu item | Performs a read of all selected registers on the active/visible register tab                                                                    |

| Active Tab                                          | Label                | Displays the name of the active/visible register tab                                                                                            |

| Auto Refresh (tab change)                           | Checkbox             | When checked, the register tab is automatically refreshed when becoming active/visible.                                                         |

| Enable ADC Scanning                                 | Checkbox             | When checked, a scan of the ADC is initiated (STROBE bit set to 1) every x milliseconds, where x is set by the <b>Interval</b> controls below.* |

| Interval (msec)                                     | Edit box             | Used to enter the time interval between ADC scans                                                                                               |

| Set Interval                                        | Button               | Sets the time interval shown in the Interval (msec) edit box                                                                                    |

\*See the ADC Scan section.

cuts listed under the Actions menu. At the completion of a read operation, the grid on the active register tab displays the data of the selected registers. Figure 4 is a snapshot of the Read/Scan tab and Figure 5 shows the result of a "Read All Selected" of the Configuration tab. Table 7 lists the available read controls and their function.

# **Register Tabs**

The 40 device registers are organized onto seven tab sheets: Thresholds, Voltage Measurements, AIN1/ AIN2/DIAG, Alter/Status, Enables, Configuration, and Broadcast/Version/Freq. Each tab provides write access to each device in the SMBus ladder, as well as a grid that displays the contents of the devices' registers. The display grids are updated by performing read operations through the Read/Scan tab. See the Read Registers section for more details. The write operations are performed using the Write tab or the individual write buttons located on each register tab.

### Thresholds Tab

The Thresholds tab (Figure 6) is used to configure the seven threshold registers. The data for the threshold registers are entered and displayed on the GUI as either a voltage or hex value. The threshold registers and their associated GUI controls are listed in Table 8.

The register buttons under the Write to Active Device label are used to write the entered data to the active device. The active device is selected from the Device Addresses (0x01) tab, or through the Active Device drop-down list. The Write All buttons under the Write to ALL Devices label are used to write the entered data to all devices in the SMBus ladder.

### × Communication Log Short Cuts Write to ALL Devices 0×0 Write All Over-Temperature Threshold Over-voltage Threshold High Under-voltage Threshold Low Under-voltage Threshold High Over-voltage Threshold Low Under-Temperature Threshold Active Register Cell Mismatch Threshold > > > > > enter bits [15:4] enter bits [15:4] Data (hex) ð ð Read/Scan Write to Active Device F OVTHRCLR UVTHRCLR OVTHRSET UVTHRSET MSMTCH AINOT AINUT Device Addresses (0x01) | Write | Active Device 1: 0x01 (0x40) Thresholds Voltage Measurements AIN/DIAG/FMEA Alent/Status Enables Configuration Broadcast/Version/Freq 2: 0x02 1: 0x01 Writer < > Initialization Successful (0×00) (0×00) AINUT $0 \times 1F$ VERSION VODRESS ALATUS ALATOVCELL ALATOVCELL ALATOVCELL ALATOVCELL ALATOVCELL ALATOVCELL ALATOVCE ALAT Active Register AINOT OxlE MSMTCH 0x1C L UVTHRCLR 0x1B Broadcast Address ۲ F Device Count OVTHRSET Initialization <u> SHDN</u> 0x1AQ M M 0x40 Actions Options Tools Help MAX11068 Evlaution Kit $| \sim |$ 0x19 Set Last Address Start Here Hello ALL **Boll Call** OVTHRCLR 0x18Interface found Device ALL -2 e E

# **MAX11068 Evaluation System**

Figure 6. MAX11068 Evaluation Kit Software (Thresholds Tab)

Evaluates: MAX11068

# **Table 8. Threshold Registers**

| THRESHOLD REGISTER (ADDRESS)                   | GUI CONTROL | DISPLAY/DATA INPUT FORMAT |

|------------------------------------------------|-------------|---------------------------|

| Overvoltage Clear (0x18)                       | OVTHRCLR    | Voltage*                  |

| Overvoltage Set (0x19)                         | OVTHRSET    | Voltage*                  |

| Undervoltage Set (0x1A)                        | UVTHRSET    | Voltage*                  |

| Undervoltage Clear (0x1B)                      | UVTHRCLR    | Voltage*                  |

| Cell Mismatch (0x1C)                           | MSMTCH      | Voltage*                  |

| Auxiliary Analog Input Overtemperature (0x1E)  | AINOT       | Hex                       |

| Auxiliary Analog Input Undertemperature (0x1F) | AINUT       | Hex                       |

\*The maximum voltage setting is 5.0000V.

# Table 9. AIN1 and AIN2 Controls

| AIN_ GUI CONTROL                  | CONTROL TYPE | DESCRIPTION                                                     |

|-----------------------------------|--------------|-----------------------------------------------------------------|

| Conversion Value                  | Label        | Displays the 12-bit AIN_ conversion value                       |

| Under Temperature Enable (COLDEN) | Checkbox     | Configures the COLDEN bit to enable/disable the ALRTTHOT alarm* |

| Over Temperature Enable (HOTEN)   | Checkbox     | Configures the HOTEN bit to enable/disable the ALRTTCOLD alarm* |

| Update Active Device              | Button       | Configures the COLDEN and HOTEN bits of the active device       |

| Update All Devices                | Button       | Configures the COLDEN and HOTEN bits of all devices             |

\*These bits work in parallel with the ALRMUTEN and ALRMOTEN registers.

For all the threshold registers, the data (D[11:0]) is contained in the upper 12 bits of the 16-bit register. When entering data into the **Under-Temperature Threshold** (AINUT) and **Over-Temperature Threshold** (AINOT) edit boxes, enter only the hex value of the upper 12 bits. The lower nibble of all threshold registers are ignored during a write and are read back as zeros.

### Voltage Measurements Tab

The **Voltage Measurements** tab (Figure 7) displays the results for the ADC conversions on cells 1–12, as well as the results for TOTAL, MAXCELL, and MINCELL. The register contents are displayed in the grid as voltages. The checkboxes at the top of the tab and their associated **Configure Cells (F9)** button are used to enable a cell for measurement. These checkboxes have the same function as the **CELL\_EN** checkboxes on the **Configuration** tab. See the *ADC Scan* section for details on setting up and initiating an ADC scan.

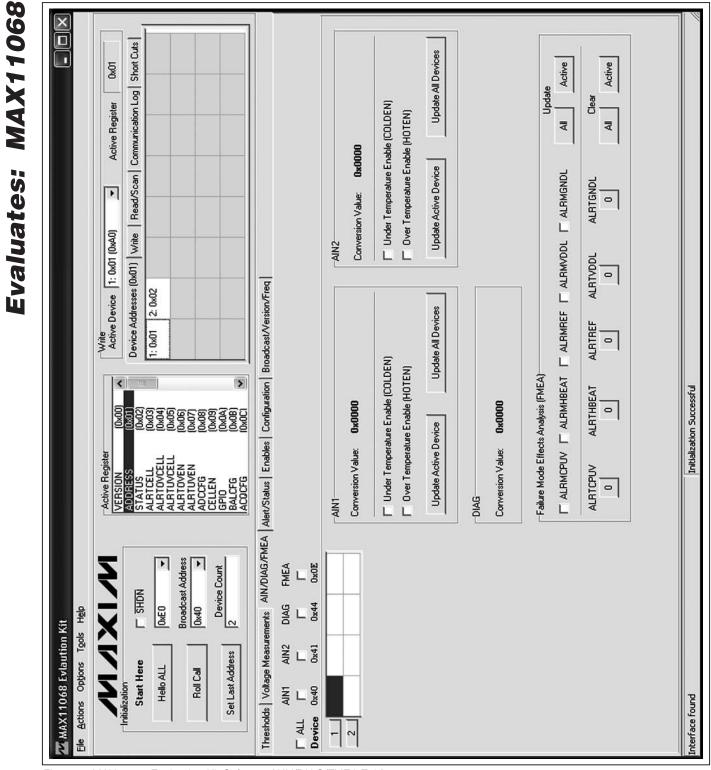

### AIN1/DIAG/FMEA Tab

The auxiliary analog inputs (AIN1 and AIN2), diagnostic (DIAG), and failure mode effects analysis (FMEA) registers are accessed from this tab (Figure 8). The tab is divided into four group boxes: AIN1, AIN2, DIAG, and Failure Mode Effects Analysis (FMEA). The DIAG group box displays the 12-bit result of the self-diagnostic measurement and the FMEA group box displays the FMEA alerts and provides access to their associated mask bits. The AIN\_ group boxes provide the controls listed in Table 9.

The AIN1, AIN2, and DIAG conversions must first be enabled before a valid conversion value can be read from the AIN or DIAG registers. A scan of the AIN\_ channel is enabled by selecting the **AIN\_EN** checkbox located on the **Enables** tab (Figure 10). A self-diagnostics conversion is enabled by selecting the **DIAGEN** checkbox located on the **Enables** tab. See the *Enables Tab* and *ADC Scan* sections.

### MIN CELL Short Cuts 0×12 0×0 MAX CELL 0x11 Communication Log Configure Cells (F9) Active Register TOTAL 0×10 Read/Scan CELL12 F 0x2B F L Device Addresses (0x01) | Write | CELL11 Write Active Device 1: 0x01 (0xA0) L CELL10 L Thresholds Voltage Measurements AIN/DIAG/FMEA Alert/Status Enables Configuration Broadcast/Version/Freq 2: 0x02 CELL9 0x28 1: 0x01 L CELL8 0x27 L > < Initialization Successful (0x00) (0x01) (0x01) (0x03) (0x08) (0 CELL7 L CELL6 Active Register VERSION ADDRESS STATUS ALATTOVELL ALATTOVELL ALATTOVELL ALATTOVEN ALATTOVEN BALOFG BALOFG BALOFG BALOFG BALOFG BALOFG BALOFG BALOFG L CELL5 0x24 L CELL4 L Broadcast Address Þ × **Device Count** CELL3 0x22 L SHDN L X 0×E0 0×40 Eile Actions Options Tools Help W MAX11068 Evlaution Kit N CELL2 0x21 Initialization L Set Last Address Start Here Hello ALL Roll Call GELLI 0x20 L Interface found Device L ALL -2

# **MAX11068 Evaluation System**

Figure 7. MAX11068 Evaluation Kit Software (Voltage Measurements Tab)

**Evaluates: MAX11068**

Figure 8. MAX11068 Evaluation Kit Software (AIN/DIAG/FMEA Tab)

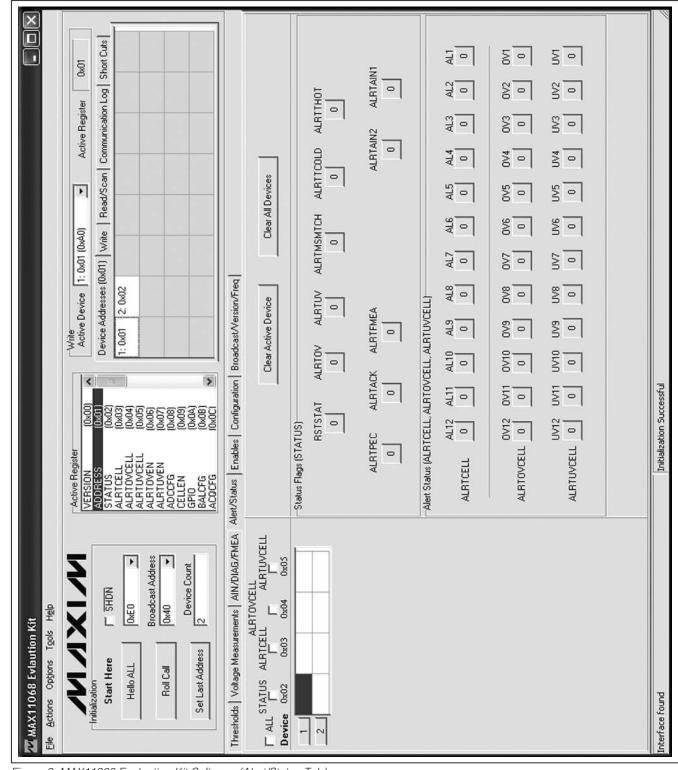

### Alert/Status Tab

All device alerts are monitored from the **Alert/Status** tab (Figure 9). The right side of the tab is divided into two group boxes: **Status Flags (STATUS)** and **Alert Status (ALRTCELL, ALRTOVCELL, ALRTUVCELL)**. The **Status Flags (STATUS)** group box displays the alerts from the STATUS (0x02) register. **The Alert Status (ALRTCELL, ALRTOVCELL, ALRTUVCELL)** group box displays the alerts from the ALRTCELL (0x03), ALRTOV (0x04), and ALRTUV (0x05) registers. Refer to the *Auxiliary Analog Inputs and External Thermistor Supply Pin* and *Self-Diagnostics* sections in the MAX1068 IC data sheet for additional information.

Each group box contains buttons that are associated with that register's alert bits. When performing a read of these alert registers, the state of each alert bit is displayed on the buttons' faces. To clear an alert, a zero must be written to the bit position assigned to that specific alert. An alert is cleared by:

1) Selecting the alerts to be cleared:

- Press the button displaying the alert. The button's label changes from 1 to 0.

- 2) Writing to the alert register(s):

- Press the Clear Active Device button to clear the selected alerts of the active device (see the Active Device drop-down list), or

- Press the **Clear All Devices** button to clear the selected alerts of all devices in the chain.

The alerts can be disabled by setting their associated alarm enable bit(s) to 0. The alarm enable bits for the status alerts are located in the ADCCFG (0x08) register. In addition, the AIN1 and AIN2 registers each contain 2 bits (HOTEN and COLDEN) that provide secondary enabling/disabling of the overtemperatue and undertemperature alerts (ALRTTHOT and ALRTTCOLD).

The alarm enable bits for the ALRTOV and ALRTUV alerts are located in the OVALRTEN (0x06) and UVALRTEN (0x07) registers, respectively. The ALRTCELL alerts result from an ALRTOV or ALRTUV alert. Thus, to disable an ALRTCELL alert, both the ALRTOV and ALRTUV alerts for that cell must be disabled (i.e., to disable cell 12's alert (AL12), the OV12 and UV12 enable bits must be set to 0).

### Enables Tab

The MAX11068 alert and alarm functions are enabled/ disabled by checking/unchecking the **Enables** tab (Figure 10) checkboxes and then pressing either the **Configure Active Device** or the **Configure All Devices** button. When enabled, the overvoltage and undervolt-

age alerts can be monitored and cleared using the buttons on the **Alert/Status** tab. See the *Alert/Status Tab* section. The overvoltage and undervoltage alert enable bits are contained in their register's lower 12 bits (\_VALRTEN[11:0]).

The **General Configuration (ADCCFG)** group box provides **ALRM**\_ checkboxes to enable/disable additional MAX11068 alert functions. These alerts are monitored and cleared using the buttons on the **Alert/Status** tab. The ADCCFG register is also used to enable self-diagnostic measurements (DIAGEN), enable conversions on the AUXIN1 and AUXIN2 inputs (AIN1EN and AIN2EN), and initiate an ADC scan. See the *ADC Scan* section for further scan details and refer to Table 13 in the IC data sheet for ADCCFG bit descriptions.

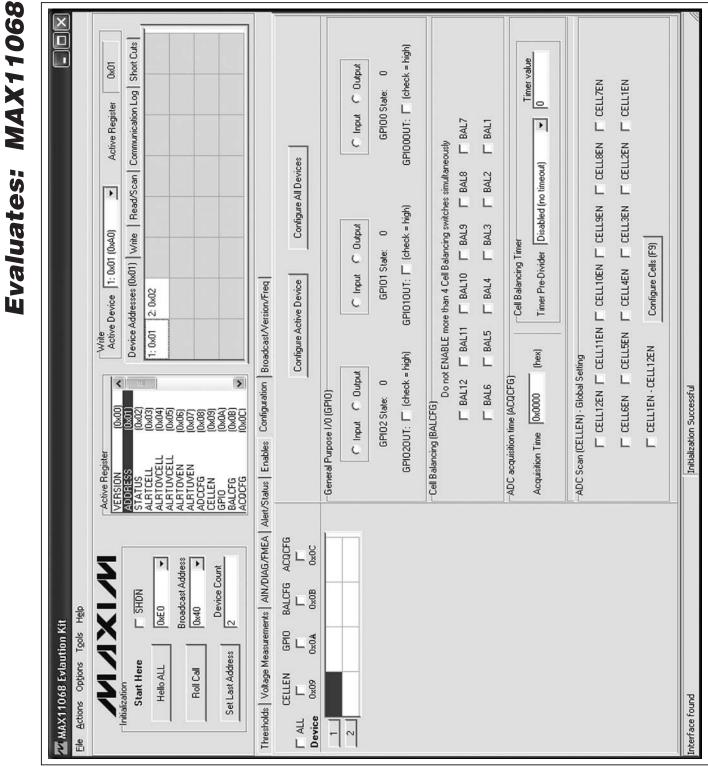

### **Configuration Tab**

The **Configuration** tab (Figure 11) is divided into four group boxes: **General Purpose I/O (GPIO)**, **Cell Balancing (BALCFG)**, **ADC acquisition time (ACQCFG)**, and **ADC Scan (CELLEN) – Global Setting**. Table 10 lists the configuration controls and their functions.

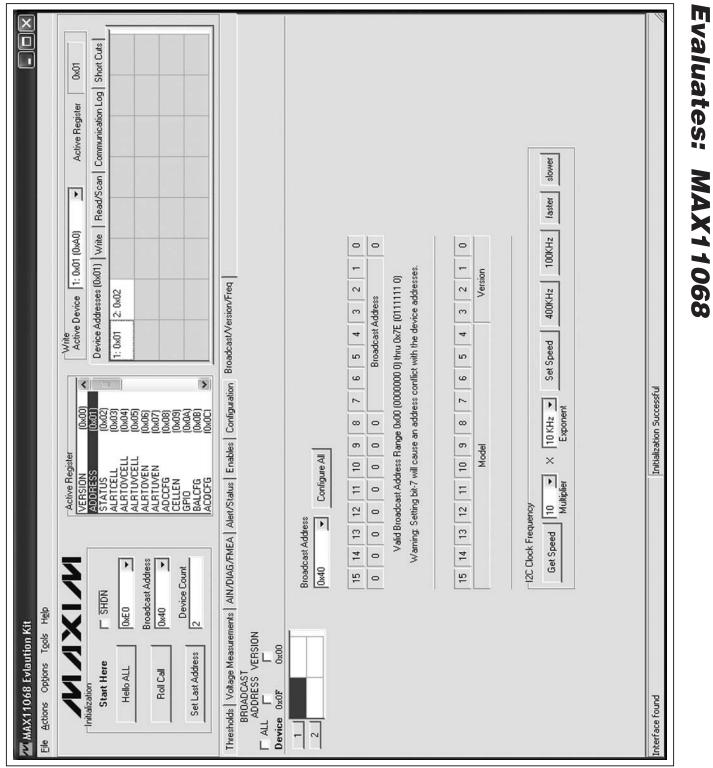

### Broadcast/Version/Freq Tab

This register tab (Figure 12) is used to change the broadcast address, read back each device's version number, and configure the I<sup>2</sup>C clock frequency. The broadcast address and version number are contained in the MAX11068 device registers, whereas the clock frequency is an interface configuration associated with the MINIQUSB command module.

**Broadcast Address:** The broadcast address is used by the host controller to communicate with all the devices in the SMBus ladder. This address is used by the host when executing roll call, write all, and read all commands. The broadcast address is contained in the lower 8 bits ([7:0]) of the 16-bit BROADCAST ADDRESS register and can be set in the 0x00 (0000 0000) through 0x7E (0111 1110) range. The **Broadcast Address** combo box provides a list of selectable addresses and allows a valid address to be entered into the edit box.

**Model and Version Number:** The lower nibble of the Version register (VER[3:0]) contains the IC's version number. The upper 12 bits (VER[15:4]) contain the MAX11068 model number, which is set to 0x068 (0000 0110 1000). The Version register is a read-only register.

**I2C Clock Frequency:** The I<sup>2</sup>C clock frequency is configured using the controls in the **I2C Clock Frequency** group box. The **Multiplier** and **Exponent** drop-down lists show the current or desired clock frequency.

Figure 9. MAX11068 Evaluation Kit Software (Alert/Status Tab)

Evaluates: MAX11068

# **Evaluates: MAX11068**

|                                                                               | Active Register     Mile     Mile     Mile     Mile     Mile     Mile       VERSION     (0x00)     Active Device     1: 0x01 (0x40)     Active Register     0x01       Active Register     (0x01)     Mile     Mile     Active Register     0x01       ALRTUVELL     (0x02)     Active Register     0x01     Mile     Mile       ALRTUVELL     (0x03)     HITUVELL     (0x03)     Mile     Mile       ALRTUVEN     (0x03)     ALRTUVEN     (0x03)     Mile     Mile       ALRTUVEN     (0x03)     ACELEN     (0x03)     Mile     Mile       ADCFG     (0x03)     (0x03)     Mile     Mile     Mile | Enables                                     | Configure Active Device Configure All Devices                                   | Dver Voltage Alet Enables (ALRTOVEN) | ☐ OVALRTEN5 ☐ OVALRTEN4 ☐ OVALRTEN3 ☐ OVALRTEN2 ☐ SELECT ALL | Under Voltage Alett Enables (ALRTUVEN) | 🕝 UVALRTEN12 📄 UVALRTEN11 📄 UVALRTEN10 📄 UVALRTEN9 📄 UVALRTEN8 📄 UVALRTEN7 | 🕝 UVALRTENS 🔽 UVALRTEN5 🔽 UVALRTEN4 📃 UVALRTEN2 🗍 UVALRTEN2 🦵 UVALRTEN1 | General Configuration (ADCCFG) | T ALRMOTEN T ALRMPEC | F DIAGEN F AINZEN F AINTEN | Initialization Successful |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------|----------------------|----------------------------|---------------------------|

| ∕v. MAX11068 Evlaution Kit<br>Ele <u>A</u> ctions Optjons Tools H <u>e</u> lp | Initialization     Start Here     SHDN       Start Here     FHDN       Hello ALL     DxE0       Roll Call     Dadcast Address       Set Last Address     Device Count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Thresholds Voltage Measurements AIN/DIAG/FI | ALRTOVEN ALRTUVEN ADCCFG<br>ALL   C ALL   C  C  C  C  C  C  C  C  C  C  C  C  C | 7                                    |                                                              |                                        |                                                                            |                                                                         |                                |                      |                            | Interface found           |

Figure 10. MAX11068 Evaluation Kit Software (Enables Tab)

Figure 11. MAX11068 Evaluation Kit Software (Configuration Tab)

Figure 12. MAX11068 Evaluation Kit Software (Broadcast/Version/Freq Tab)

# Table 10. Configuration Controls

| CONTROL                        | CONTROL TYPE | FUNCTION                                                                                          |

|--------------------------------|--------------|---------------------------------------------------------------------------------------------------|

| General Purpose I/O (GPIO)     | 1            |                                                                                                   |

| Input                          | Radio button | Configures the GPIO pin as an input                                                               |

| Output                         | Radio button | Configures the GPIO pin as an output                                                              |

| GPIO_ State                    | Label        | Displays the current state of the GPIO pin                                                        |

| GPIO_OUT                       | Checkbox     | Control the GPIO pin when configured as an output                                                 |

| Cell Balancing (BALCFG)        | ·            |                                                                                                   |

| BAL_                           | Checkbox     | Select which cell-balancing switches to enable/disable*                                           |

| ADC acquisition time (ACQCFG)  | ·            |                                                                                                   |

| Acquisition Time               | Edit box     | 6-bit acquisition time for AUXIN1/AUXIN2                                                          |

| ADC Scan (CELLEN) - Global Set | tting        |                                                                                                   |

| CELL_EN                        | Checkbox     | Select which cell to enable for measurement                                                       |

| CELL1EN - CELL12EN             | Checkbox     | Selects all cells for measurement                                                                 |

| Configure Cells (F9)           | Button       | Writes the CELL_EN checkbox settings to CELLEN register                                           |

| Configure Active Device**      | Button       | Writes the configuration settings to the device listed in the <b>Active Device</b> drop-down list |

| Configure All Devices**        | Button       | Writes the configuration settings to all devices in the SMBus ladder                              |

\*Do not enable more than four cell-balancing switches at a time.

\*\*Includes write to CELLCFG register.

# Table 11. Broadcast Address Byte

|        |       |       |       |       |       |       | 1     |

|--------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7* | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| 0      | B6    | B5    | B4    | B3    | B2    | B1    | 0     |

\*Setting bit 7 to 1 causes address conflicts with the device addresses.

# Table 12. Version Register

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0      | 0      | 0      | 0      | 0      | 1      | 1     | 0     | 1     | 0     | 0     | 0     |       | VER   | [3:0] |       |

# Table 13. Read Controls

| CONTROL NAME | CONTROL TYPE   | FUNCTION                                                                            |

|--------------|----------------|-------------------------------------------------------------------------------------|

| Get Speed    | Button         | Determines the current bus speed setting and displays it in the two drop-down lists |

| Multiplier   | Drop-down list | Selectable speed multiplier                                                         |

| Exponent     | Drop-down list | Selectable speed exponent                                                           |

| Set Speed    | Button         | Sets clock frequency = (multiplier x exponent)                                      |

| 400kHz       | Button         | Sets the bus speed to 400kHz                                                        |

| 100kHz       | Button         | Sets the bus speed to 100kHz                                                        |

| faster       | Button         | Increases the bus speed to the next faster setting                                  |

| slower       | Button         | Decreases the bus speed to the next lowest setting                                  |

### **ADC Scan**

An ADC scan measures all enabled cell inputs, all enabled auxiliary inputs, and the self-diagnostics channel (if enabled). The conversion begins once the STROBE bit in the ADCCFG register is set. The following procedure outlines the steps to set up and initiate single or continuous ADC scanning.

### Set Up:

1) Enable the cells to measure:

- Check the CELL\_EN checkboxes on the Configuration tab in the ADC Scan (CELLEN) – Global Setting group box.

- Press the Configure Cells (F9) button.

**Note:** The cell channels can also be enabled with the checkboxes on the **Voltage Measurements** tab.

### 2) Select the cell registers to read:

- Check the **CELL**\_ checkboxes on the **Voltage Measurements** tab.

- 3) Enable the self-diagnostics and auxiliary inputs to measure:

- Check the **DIAGEN**, **AIN2EN**, and **AIN1EN** checkboxes on the **Enables** tab in the **General Configuration (ADCCFG)** group box.

- Press the **Configure Active Device** or the **Configure All Devices** button.

- Select the self-diagnostics and auxiliary input registers for reading:

- Check the AIN1, AIN2, and DIAG checkboxes on the AIN1/DIAG/FMEA tab.

### Initiate a Single ADC Scan:

- Check the SCAN checkbox on the Enables tab, then press the Configure All Devices button, or

- Select the Voltage Measurements tab and press F8 (Refresh) or F7 (Read All Selected) to read the selected cell registers.

**Note:** The STROBE bit is automatically set before a read is done on the **Voltage Measurements** tab.

### Initiate Continuous ADC Scanning:

- 1) Select the Read/Scan tab.

- 2) Enter the time delay between ADC scans into the **Interval (msec)** edit box.

### 3) Check the Enable ADC scanning checkbox.

**Note:** To save the data during a continuous ADC scan, perform the steps from the *Log Scanned Data* section in place of these steps.

### Log Scanned Data

The EV kit software allows the data, measured during continuous ADC scanning, to be saved to file. This feature is available by selecting the **File I Log Scan Data** menu item and should be set up before scanning is started. The steps below explain how to set up data logging:

- 1) Perform steps 1-4 in the ADC Scan section.

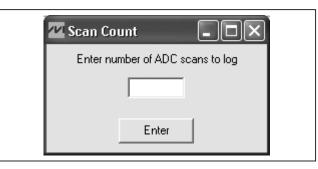

- 2) Select the **File I Log Scan Data menu item** or press CTRL+L. The following window appears:

- 3) Enter the number (n) of ADC scans to record, and then press **Enter**.

- 4) Select the Read/Scan tab.

- 5) Enter the time delay between ADC scans into the **Interval (msec)** edit box.

- Check the Enable ADC scanning checkbox. A red Logging Data label appears, notifying that data is being recorded.

- Once n number of scans have been completed, the Log Complete window appears. Press OK.

A Log Data dialog box appears. The default file name is 11068all and the default file type is .xls (Excel spreadsheet). If a different name or file type is preferred, enter it into the File name edit field. Press Save.

At the completion of this process, data logging is disabled, but the continuous ADC scanning continues until the **Enable ADC Scanning** checkbox is unchecked. The file generated by the software logs the measured data of the enabled channels for all the devices in the SMBus ladder.

Evaluates: MAX11068

| S   |           |     |                   |   |   | DIAG        |                |             |                     |                     |             |                     |                     |             |                     |             |             |             |             |             |             |                     |                    |                            |                    |             |             |    |    |

|-----|-----------|-----|-------------------|---|---|-------------|----------------|-------------|---------------------|---------------------|-------------|---------------------|---------------------|-------------|---------------------|-------------|-------------|-------------|-------------|-------------|-------------|---------------------|--------------------|----------------------------|--------------------|-------------|-------------|----|----|

| œ   |           |     |                   |   |   | AIN1        |                |             |                     |                     |             |                     |                     |             |                     |             |             |             |             |             |             |                     |                    |                            |                    |             |             |    |    |

| C   | i         |     |                   |   |   | AN0         | P <del>1</del> |             |                     |                     |             | _                   | _                   | _           | _                   | _           | _           | _           | _           | _           | _           | _                   | _                  | _                          | _                  | _           | _           |    |    |

| a.  |           |     |                   |   |   | MIN         | ZIXN           | 3 8877 (1)  | 3 8913 (1)          | 3.8889 (1)          | 3.8913 (1)  | 3.8901 (1)          | 3.8913 (1)          | 3.8901 (1)  | 3.8913 (1)          | 3.8901 (1)  | 3.8901 (1)  | 3.8889 (1)  | 3.8913 (1)  | 3.8889 (1)  | 3.8926 (1)  | 3.8889 (1)          | 3.8913 (1)         | 3.8877 (1)                 | 3.8901 (1)         |             | 3.8913 (1)  |    |    |

| 0   |           |     |                   |   |   | MAX<br>0.11 |                | 3 9035 (10) | 46.7827 3.9035 (12) | 46.7705 3.9035 (12) | 3.9023 (12) | 46.7729 3.9035 (12) | 46.7839 3.9035 (12) | 3.9035 (12) | 46.7875 3.9048 (12) | 3.9035 (12) | 3.9035 (12) | 3.9023 (12) | 3.9023 (12) | 3.9023 (12) | 3.9023 (12) | 46.7692 3.9023 (12) | <u>3.9035 (12)</u> | 3.9035 (12)<br>2.2025 (12) | 46.779 3.9U35 (12) | 3.9023 (12) | 3.9023 (12) |    |    |

| z   |           |     |                   |   |   |             |                | 16 7607 JA  | 46 7827             | 46.7705             | 46.7766     | 46.7729             | 46.7839             | 46.768      | 46.7875             | 46.7705     | 46.779      | 46.7656     | 46.7814     | 46.768      | 46.7802 (   |                     | 46.7827            | 46.7692                    | 40.7/9             |             | 46.7851     |    |    |

| Μ   |           |     |                   |   |   | 2           | D X V          | 3 0035      | n co                |                     |             |                     |                     |             |                     |             |             |             |             |             |             |                     |                    | ml                         | ירי                |             | 3.9023      |    |    |