# COP8<sup>TM</sup> MICROCONTROLLER

COP8SAx Designer's Guide

Literature Number 620894-001 January 1997

# **REVISION RECORD**

# REVISION RELEASE DATE SUMMARY OF CHANGES

-001

1/97

First Release

# PREFACE

This manual is written with the intention to serve as a Designer's Guide for those who are considering to use a microcontroller from National's COP8SAx family of devices.

Chapter 1, MICROCONTROLLER BASICS, reviews microcontroller basics, including definitions, building blocks, operation, applications, and programming. Those who are already familiar with microcontrollers can skip this chapter.

Chapter 2, COP8SAx FAMILY, provides a detailed overview of the COP8SAx family of devices. It describes the features, architecture, instruction set, and electrical characteristics. For more detailed information, refer to the COP8 Feature Family User's Manual.

Chapter 3, DEVELOPMENT TOOLS, describes the range of development tools that are available for developing and testing application software that is run on the COP8SAx microcontroller.

Chapter 4, COP8SAx APPLICATION IDEAS, provides an overview of some design examples using the COP8SAx microcontroller. Within these examples, the users can find application hints that may be useful in implementing a design.

The information contained in this manual is for reference only and is subject to change without notice.

No part of this document may be reproduced in any form or by any means without the prior written consent of National Semiconductor Corporation.

COP8, MICROWIRE/PLUS and WATCHDOG are trademarks of National Semiconductor Corporation.

| Chapter 1                                     | MICROCONTROLLER BASICS                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1                                           | WHAT IS A MICROCONTROLLER?                                                                                                                                                                                                                                                                                                                                                                        | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | 1.1.1 CPU                                                                                                                                                                                                                                                                                                                                                                                         | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | 1.1.2 Program Memory                                                                                                                                                                                                                                                                                                                                                                              | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | 1.1.3 Data Memory                                                                                                                                                                                                                                                                                                                                                                                 | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | 1.1.4 Timing                                                                                                                                                                                                                                                                                                                                                                                      | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | 1.1.5 Inputs/Outputs                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.2                                           | WHAT DOES A MICROCONTROLLER REPLACE?                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.3                                           | WHAT ARE MICROCONTROLLER APPLICATIONS?                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.4                                           | WHAT IS THE DIFFERENCE BETWEEN A MICROCONTROLLED                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | AND A MICROPROCESSOR?                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.5                                           | WHAT IS THE ARCHITECTURE OF A MICROCONTROLLER                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.5.1Von Neumann Architecture                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.5.2 Harvard Architecture                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.6                                           | HOW DOES A MICROCONTROLLER OPERATE?                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1.7                                           | DESCRIPTION OF MICROCONTROLLER BUILDING BLOCKS .                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.1 Program Memory                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.2 Data Memory                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.3 Microcontroller CPU                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.4 Timing                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.5 Oscillator Circuits                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.6 Instruction Set                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | 1.7.7 Programming                                                                                                                                                                                                                                                                                                                                                                                 | 1-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 2                                     | COP8SAx7 MICROCONTROLLER                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <b>Chapter 2</b><br>2.1                       |                                                                                                                                                                                                                                                                                                                                                                                                   | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                               | COP8SAx7 MICROCONTROLLER<br>INTRODUCTION<br>KEY FEATURES                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1                                           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                      | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.1                                           | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1                                           | INTRODUCTIONKEY FEATURES2.2.1CPU Features                                                                                                                                                                                                                                                                                                                                                         | 2-1<br>2-2<br>2-3                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.1                                           | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features                                                                                                                                                                                                                                                                                                                                 | 2-1<br>2-2<br>2-3<br>2-3                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2.1                                           | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features                                                                                                                                                                                                                                                                                                                | 2-1<br>2-2<br>2-3<br>2-3<br>2-3                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.1<br>2.2                                    | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development Support                                                                                                                                                                                                                                    | 2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3                                                                                                                                                                                                                                                                                                                                                                                                                |

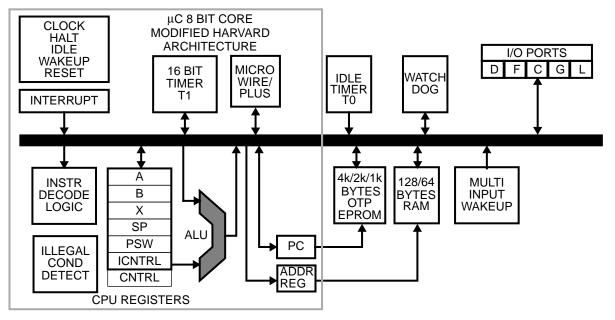

| 2.1<br>2.2<br>2.3                             | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAM                                                                                                                                                                                                                       | 2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-4                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4                      | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTURE                                                                                                                                                                                                           | 2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4                                                                                                                                                                                                                                                                                                                                                                                                         |

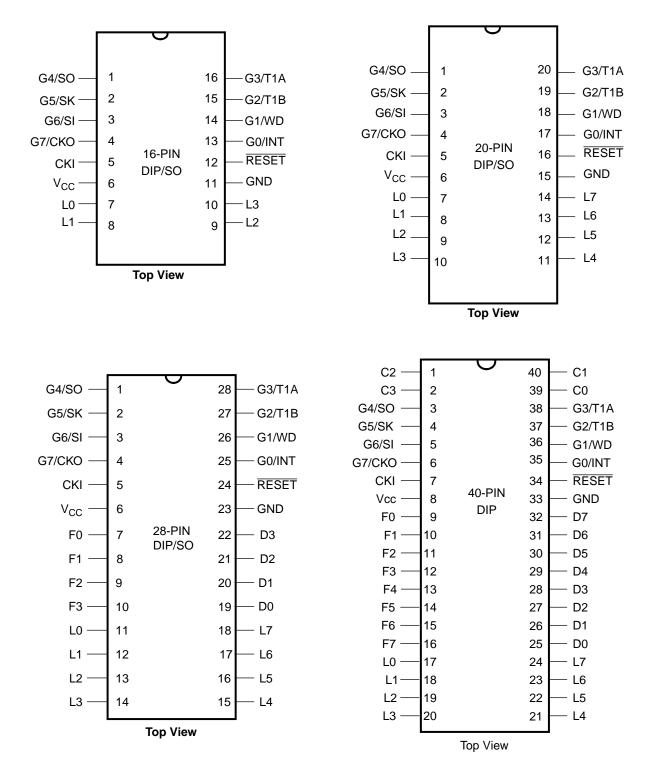

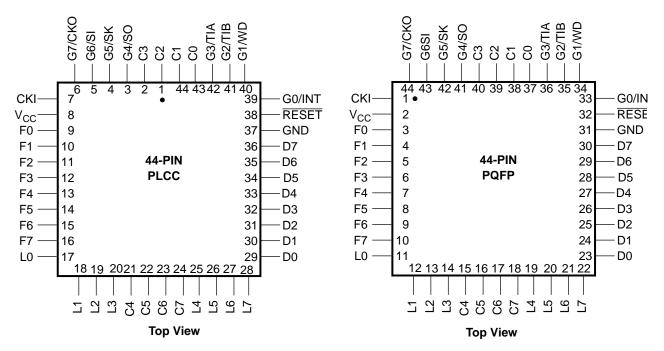

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5               | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCY                                                                                                                                                                                   | 2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-4                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1<br>2.2<br>2.3<br>2.4                      | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS                                                                                                                                                                | 2-1<br>2-2<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-4<br>2-4<br>2-5                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6        | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATION                                                                                                                                       | $\begin{array}{c} \dots 2 \cdot 1 \\ \dots 2 \cdot 2 \\ \dots 2 \cdot 3 \\ \dots 2 \cdot 4 \\ \dots 2 \cdot 4 \\ \dots 2 \cdot 4 \\ \dots 2 \cdot 5 \\ \dots 2 \cdot 7 \end{array}$                                                                                                                                                                                  |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONS                                                                                                                       | $\begin{array}{c} \dots 2 \cdot 1 \\ \dots 2 \cdot 2 \\ \dots 2 \cdot 3 \\ \dots 2 \cdot 4 \\ \dots 2 \cdot 5 \\ \dots 2 \cdot 5 \\ \dots 2 \cdot 7 \\ \dots 2 \cdot 8 \end{array}$                                                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6        | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION                                                                                                 | $\begin{array}{c} \dots 2 - 1 \\ \dots 2 - 2 \\ \dots 2 - 3 \\ \dots 2 - 4 \\ \dots 2 - 5 \\ \dots 2 - 7 \\ \dots 2 - 8 \\ \dots 2 - 11 \end{array}$                                                                                                                                                          |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION2.8.1CPU Registers                                                                               | $\begin{array}{c} \dots 2 - 1 \\ \dots 2 - 2 \\ \dots 2 - 3 \\ \dots 2 - 4 \\ \dots 2 - 4 \\ \dots 2 - 4 \\ \dots 2 - 5 \\ \dots 2 - 5 \\ \dots 2 - 7 \\ \dots 2 - 11 \\ \dots 2 - 11 \end{array}$                                                                                                                                                                        |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION2.8.1CPU Registers2.8.2Program Memory                                                            | $\begin{array}{c} \dots 2 - 1 \\ \dots 2 - 2 \\ \dots 2 - 3 \\ \dots 2 - 4 \\ \dots 2 - 5 \\ \dots 2 - 7 \\ \dots 2 - 7 \\ \dots 2 - 11 \\ \dots 2 - 11 \\ \dots 2 - 12 \end{array}$                                                                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION2.8.1CPU Registers2.8.2Program Memory2.8.3Data Memory                                            | $\begin{array}{c} \dots 2 - 1 \\ \dots 2 - 2 \\ \dots 2 - 3 \\ \dots 2 - 4 \\ \dots 2 - 1 \\ \dots 2 - 11 \\ \dots 2 - 12 \\ \dots 2 - 12 \\ \dots 2 - 12 \end{array}$                                                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAM.ARCHITECTURE.PACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION.2.8.1CPU Registers2.8.2Program Memory2.8.3Data Memory2.8.4ECON (EPROM Configuration) Register | $\begin{array}{c} \dots 2 \cdot 1 \\ \dots 2 \cdot 2 \\ \dots 2 \cdot 3 \\ \dots 2 \cdot 4 \\ \dots 2 \cdot 5 \\ \dots 2 \cdot 11 \\ \dots 2 \cdot 11 \\ \dots 2 \cdot 12 \\ \dots 2 \cdot 12 \\ \dots 2 \cdot 12 \\ \dots 2 \cdot 13 \end{array}$ |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | INTRODUCTIONKEY FEATURES2.2.1CPU Features2.2.2Peripheral Features2.2.3I/O Features2.2.4Fully Static CMOS Design2.2.5Temperature Ranges2.2.6Development SupportBLOCK DIAGRAMARCHITECTUREPACKAGING/PIN EFFICIENCYCONNECTION DIAGRAMS2.6.1ORDERING INFORMATIONPIN DESCRIPTIONSFUNCTIONAL DESCRIPTION2.8.1CPU Registers2.8.2Program Memory2.8.3Data Memory                                            | $\begin{array}{c} \dots 2 - 1 \\ \dots 2 - 2 \\ \dots 2 - 3 \\ \dots 2 - 4 \\ \dots 2 - 5 \\ \dots 2 - 7 \\ \dots 2 - 11 \\ \dots 2 - 11 \\ \dots 2 - 11 \\ \dots 2 - 12 \\ \dots 2 - 12 \\ \dots 2 - 13 \\ \dots 2 - 13 \\ \dots 2 - 13 \end{array}$                                                         |

|      | 2.8.7   | Reset                                       | . 2-15 |

|------|---------|---------------------------------------------|--------|

|      | 2.8.8   | Oscillator Circuits                         | . 2-19 |

|      | 2.8.9   | Control Registers                           | . 2-21 |

| 2.9  | TIMERS  | · · · · · · · · · · · · · · · · · · ·       |        |

|      | 2.9.1   | Timer T0 (IDLE Timer)                       | . 2-23 |

|      | 2.9.2   | Timer T1                                    |        |

| 2.10 | TIMER ( | CONTROL FLAGS                               | . 2-27 |

| 2.11 | POWER   | SAVING FEATURES                             | . 2-28 |

|      | 2.11.1  | HALT Mode                                   | . 2-28 |

|      | 2.11.2  | IDLE Mode                                   | . 2-29 |

| 2.12 | MULTI-  | INPUT WAKEUP                                | . 2-31 |

| 2.13 | INTERR  | UPTS                                        | . 2-33 |

|      | 2.13.1  | Introduction                                | . 2-33 |

|      | 2.13.2  | Maskable Interrupts                         | . 2-34 |

|      | 2.13.3  | VIS Instruction                             | . 2-36 |

|      | 2.13.4  | Non-maskable Interrupt                      | . 2-41 |

|      | 2.13.5  | Port L Interrupts                           | . 2-42 |

|      | 2.13.6  | Interrupt Summary                           | . 2-42 |

| 2.14 | WATCH   | DOG/CLOCK MONITOR                           |        |

|      | 2.14.1  | Clock Monitor                               | . 2-44 |

|      | 2.14.2  | WATCHDOG/Clock Monitor Operation            | . 2-44 |

|      | 2.14.3  | WATCHDOG and Clock Monitor Summary          | . 2-45 |

|      | 2.14.4  | Detection of Illegal Conditions             |        |

| 2.15 | MICROV  | VIRE/PLUS                                   |        |

|      | 2.15.1  | MICROWIRE/PLUS Operation                    | . 2-48 |

| 2.16 | MEMOR   | Y MAP                                       |        |

| 2.17 | INSTRU  | CTION SET                                   | . 2-54 |

|      | 2.17.1  | Introduction                                | . 2-54 |

|      | 2.17.2  | Instruction Features                        | . 2-54 |

|      | 2.17.3  | Addressing Modes                            | . 2-54 |

|      | 2.17.4  | Instruction Types                           |        |

| 2.18 | DETAIL  | ED FUNCTIONAL DESCRIPTIONS OF INSTRUCTIONS. | . 2-62 |

|      | 2.18.1  | ADC— Add with Carry                         | . 2-64 |

|      | 2.18.2  | ADD — Add                                   | . 2-65 |

|      | 2.18.3  | AND — And                                   | . 2-66 |

|      | 2.18.4  | ANDSZ — And, Skip if Zero                   | . 2-67 |

|      | 2.18.5  | CLR — Clear Accumulator                     |        |

|      | 2.18.6  | DCOR — Decimal Correct                      | . 2-69 |

|      | 2.18.7  | DEC — Decrement Accumulator                 | . 2-70 |

|      | 2.18.8  | DRSZ REG# — Decrement Register and Skip     |        |

|      |         | if Result is Zero                           |        |

|      | 2.18.9  | IFBIT — Test Bit                            | . 2-72 |

|      | 2.18.10 | IFBNE # — If B Pointer Not Equal            | . 2-73 |

|      | 2.18.11 | IFC — Test if Carry                         |        |

|      | 2.18.12 | IFEQ — Test if Equal                        |        |

|      | 2.18.13 | IFGT — Test if Greater Than                 | . 2-76 |

|      | 2.18.14 | IFNC — Test If No Carry                     |        |

|      | 2.18.15 | IFNE — Test If Not Equal                    |        |

|      | 2.18.16 | INC — Increment Accumulator                 |        |

|      | 2.18.17 | INTR — Interrupt (Software Trap)            | . 2-80 |

vi CONTENTS

|      | 2.18.18 | JID — Jump Indirect                                                           | 2-81    |

|------|---------|-------------------------------------------------------------------------------|---------|

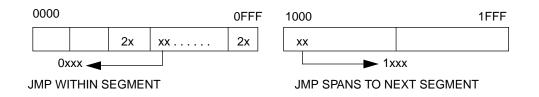

|      | 2.18.19 | JMP — Jump Absolute                                                           | 2-82    |

|      | 2.18.20 | JMPL — Jump Absolute Long                                                     | 2-83    |

|      | 2.18.21 | JP — Jump Relative                                                            |         |

|      | 2.18.22 | JSR — Jump Subroutine                                                         | 2-85    |

|      | 2.18.23 | JSRL — Jump Subroutine Long                                                   | 2-86    |

|      | 2.18.24 | LAID — Load Accumulator Indirect                                              | 2-87    |

|      | 2.18.25 | LD — Load Accumulator                                                         |         |

|      | 2.18.26 | LD — Load B Pointer                                                           | 2-90    |

|      | 2.18.27 | LD — Load Memory                                                              | 2-91    |

|      | 2.18.28 | LD — Load Register                                                            | 2-92    |

|      | 2.18.29 | NOP — No Operation                                                            |         |

|      | 2.18.30 | OR — Or                                                                       |         |

|      | 2.18.31 | POP — Pop Stack                                                               | 2-95    |

|      | 2.18.32 | PUSH — Push Stack                                                             |         |

|      | 2.18.33 | RBIT — Reset Memory Bit                                                       | 2-97    |

|      | 2.18.34 | RC — Reset Carry                                                              |         |

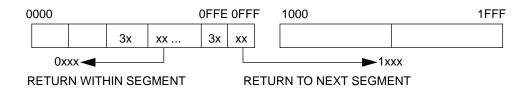

|      | 2.18.35 | RET — Return from Subroutine                                                  |         |

|      | 2.18.36 | RETI — Return from Interrupt                                                  | . 2-100 |

|      | 2.18.37 | RETSK — Return and Skip                                                       |         |

|      | 2.18.38 | RLC — Rotate Accumulator Left Through Carry                                   |         |

|      | 2.18.39 | RPND — Reset Pending                                                          |         |

|      | 2.18.40 | RRC — Rotate Accumulator Right Through Carry                                  |         |

|      | 2.18.41 | SBIT — Set Memory Bit                                                         |         |

|      | 2.18.42 | SC — Set Carry                                                                |         |

|      | 2.18.43 | SUBC — Subtract with Carry                                                    |         |

|      | 2.18.44 | SWAP — Swap Nibbles of Accumulator                                            |         |

|      | 2.18.45 | VIS — Vector Interrupt Select                                                 |         |

|      | 2.18.46 | X — Exchange Memory with Accumulator                                          |         |

|      | 2.18.47 | XOR — Exclusive Or                                                            |         |

|      | 2.18.48 | Register and Symbol Definition                                                |         |

|      | 2.18.49 | Instruction Set Summary                                                       |         |

|      | 2.18.50 | Instruction Execution Time                                                    | . 2-115 |

|      | 2.18.51 | Opcode Table                                                                  |         |

| 2.19 | PROGRA  | AMMING EXAMPLES                                                               | . 2-118 |

|      | 2.19.1  | Clear RAM                                                                     | . 2-118 |

|      | 2.19.2  | Binary/BCD Arithmetic Operations                                              |         |

|      | 2.19.3  | Binary Multiplication                                                         |         |

|      | 2.19.4  | Binary Division                                                               |         |

| 2.20 | ELECTE  | RICAL CHARACTERISTICS                                                         | . 2-125 |

|      | 2.20.1  | DC Electrical Characteristics ( $0^{\circ}C \le TA \le +70^{\circ}C$ unless   |         |

|      |         | otherwise specified)                                                          | . 2-125 |

|      | 2.20.2  | AC Electrical Characteristics ( $0^{\circ}C \le T_A \le +70^{\circ}C$ unless  |         |

|      |         | otherwise specified)                                                          | . 2-127 |

|      | 2.20.3  | DC Electrical Characteristics ( $-40^{\circ}C \le TA \le +85^{\circ}C$ unless |         |

|      |         | otherwise specified)                                                          | . 2-128 |

|      | 2.20.4  | AC Electrical Characteristics ( $-40^{\circ}C \le TA \le +85^{\circ}C$ unless |         |

|      |         | otherwise specified)                                                          | . 2-130 |

|      |         | -                                                                             |         |

|            | 2.20.5 DC Electrical Characteristics ( $-40^{\circ}C \le T_A \le +125^{\circ}C$ unless |

|------------|----------------------------------------------------------------------------------------|

|            | otherwise specified)                                                                   |

|            | 2.20.6 AC Electrical Characteristics ( $-40^{\circ}C \le T_A \le +125^{\circ}C$ unless |

|            | otherwise specified)                                                                   |

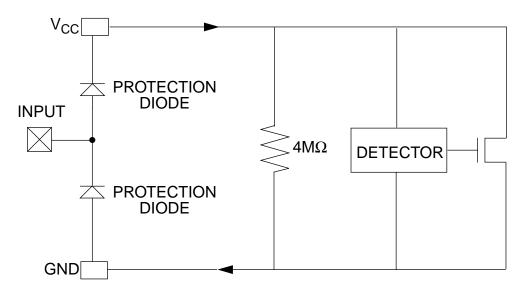

| 2.21       | ESD/EMI CONSIDERATIONS 2-134                                                           |

| 2.22       | INPUT PROTECTION                                                                       |

| 2.23       | ELECTROMAGNETIC INTERFERENCE (EMI)                                                     |

|            | CONSIDERATIONS                                                                         |

|            | 2.23.1 Introduction                                                                    |

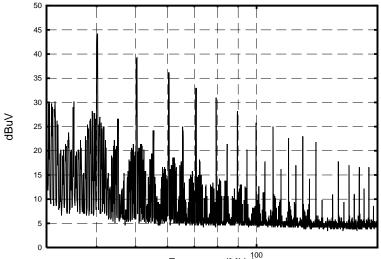

|            | 2.23.2 Emission Predictions                                                            |

|            | 2.23.3 Board Layout                                                                    |

|            | 2.23.4 Decoupling                                                                      |

|            | 2.23.5 Output Series Resistance                                                        |

|            | 2.23.6 Oscillator Control                                                              |

|            | 2.23.7 Mechanical Shielding 2-139                                                      |

| 2.24       | EMI REDUCTION ON THE COP8SAx7 2-140                                                    |

|            | 2.24.1 Silicon Design Changes to Achieve Low EMI                                       |

|            | 2.24.2 Conclusion                                                                      |

| Chantan 9  | DEVELODMENT CUDDODT                                                                    |

| Chapter 3  | DEVELOPMENT SUPPORT                                                                    |

| 3.1<br>3.2 | SUMMARY                                                                                |

| 3.2<br>3.3 | iceMASTER (IM) IN-CIRCUIT EMULATION                                                    |

| 3.3<br>3.4 | IceMASTER EVALUATION PROGRAMMING UNIT (EPU)                                            |

| 5.4        | 3.4.1 Getting Started With the EPU                                                     |

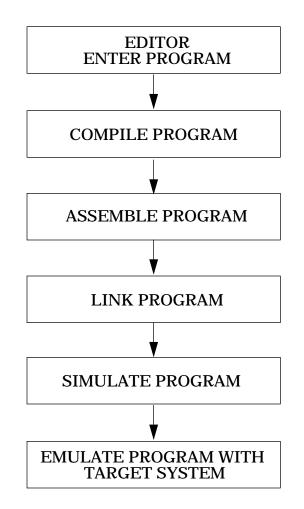

| 3.5        | COP8 ASSEMBLER/LINKER SOFTWARE DEVELOPMENT                                             |

| 0.0        | TOOL KIT                                                                               |

| 3.6        | COP8 C COMPILER                                                                        |

| 3.7        | INDUSTRY WIDE OTP / EPROM PROGRAMMING SUPPORT                                          |

| 3.8        | AVAILABLE LITERATURE                                                                   |

| 3.9        | DIAL-A-HELPER SERVICE                                                                  |

| 3.10       | DIAL-A-HELPER BBS VIA A STANDARD MODEM                                                 |

| 3.11       | NATIONAL SEMICONDUCTOR ON THE WORLDWIDE WEB 3-12                                       |

| 3.12       | CUSTOMER RESPONSE CENTER 3-12                                                          |

|            |                                                                                        |

| Chapter 4  | COP8SAx7 APPLICATION IDEAS                                                             |

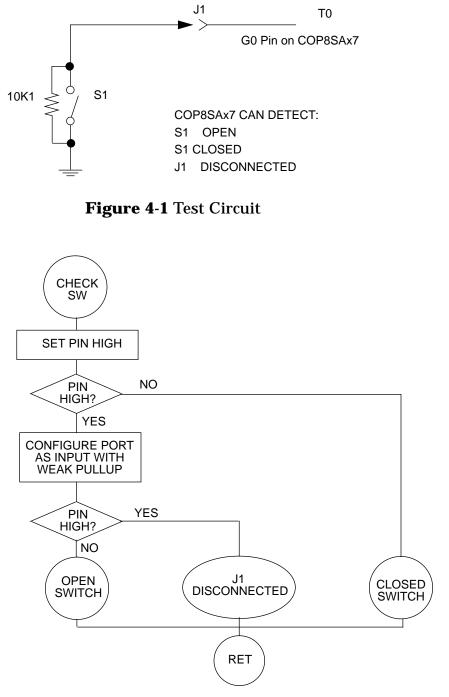

| 4.1        | TESTING A REMOTE NORMALLY OPEN SWITCH FOR                                              |

|            | CONNECTION                                                                             |

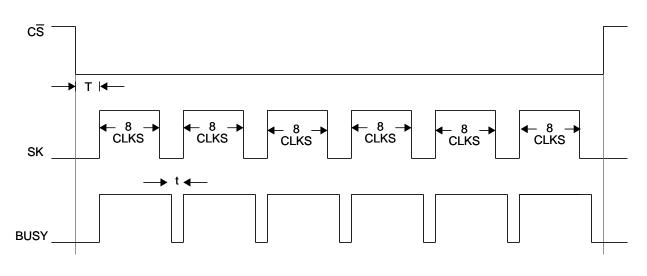

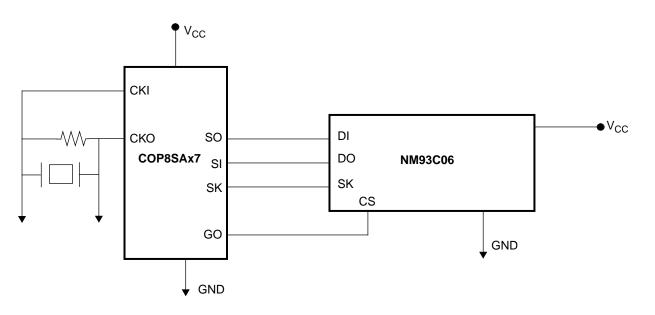

| 4.2        | MICROWIRE/PLUS INTERFACE                                                               |

|            | 4.2.1 MICROWIRE/PLUS Master/Slave Protocol                                             |

| 4.0        | 4.2.2 NM93C06-COP8SAx7 Interface                                                       |

| 4.3        | TIMER APPLICATIONS                                                                     |

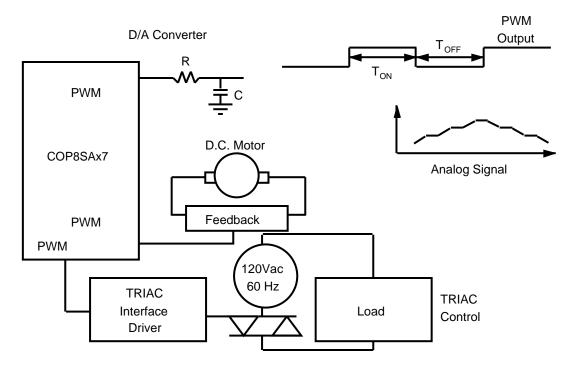

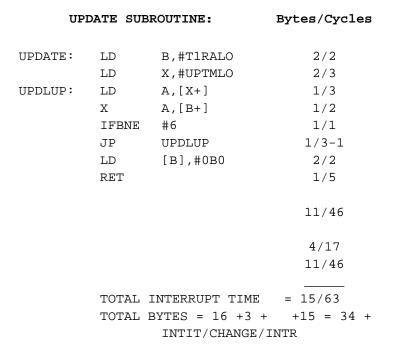

| 4.4        | TIMER PWM APPLICATIONS                                                                 |

|            | 4.4.1 Rudimentary D-A Converter                                                        |

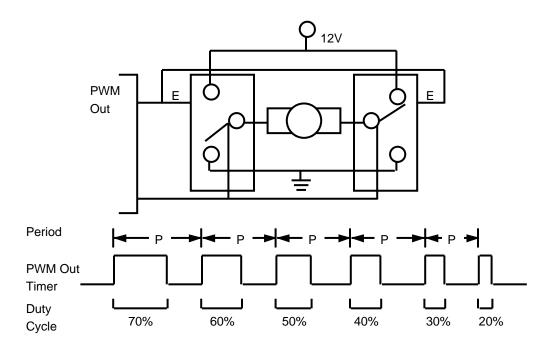

|            | 4.4.2 PWM Motor Control                                                                |

|            | 4.4.3 AC Motor TRIAC Control                                                           |

|            | 4.4.4 Timer Capture Example                                                            |

| 4.5        | 4.4.5 External Event Counter Example                                                   |

| 4 5        | TRIAC CONTROL                                                                          |

viii CONTENTS

| 4.6 EXTERNAL POWER WAKEUP CIRCUIT                  | 4-20                               |  |  |

|----------------------------------------------------|------------------------------------|--|--|

| 4.7 BATTERY-POWERED WEIGHT MEASUREMENT             | BATTERY-POWERED WEIGHT MEASUREMENT |  |  |

| 4.8 ZERO CROSS DETECTION                           | 4-23                               |  |  |

| 4.9 INDUSTRIAL TIMER                               |                                    |  |  |

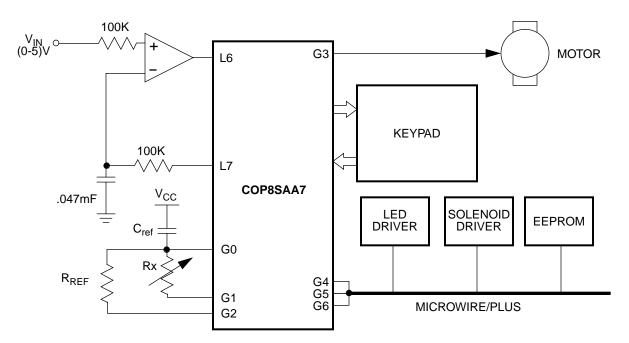

| 4.10 COP8SAA7 ELECTRONIC KEY APPLICATIONS          |                                    |  |  |

| 4.10.1 Typical Applications                        |                                    |  |  |

| 4.10.2 Flexibility                                 |                                    |  |  |

| 4.10.3 Low Cost                                    |                                    |  |  |

| 4.10.4 Small Transmitter Size                      |                                    |  |  |

| 4.10.5 Low-Cost Version for Rolling Code           |                                    |  |  |

| 4.10.6 Receiver Circuit                            |                                    |  |  |

| 4.11 COP8SAx7 DIRECT LED DISPLAY DRIVE APPLICA     | TION 4-29                          |  |  |

| 4.11.1 Improved Brightness                         |                                    |  |  |

| 4.12 CORDLESS PHONE APPLICATION                    |                                    |  |  |

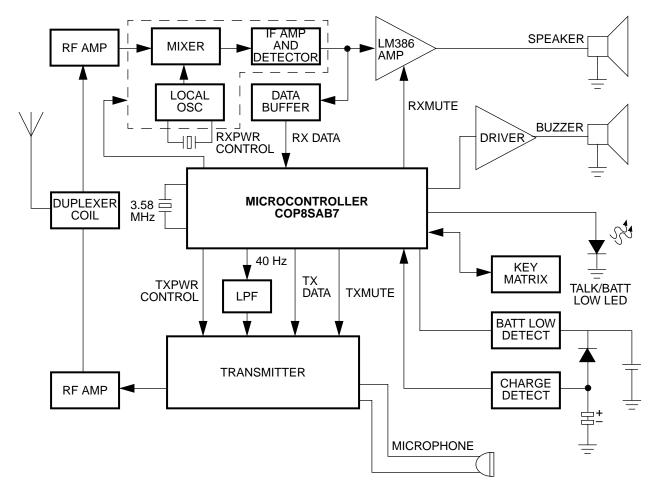

| 4.12.1 Typical Application Requirements            | 4-33                               |  |  |

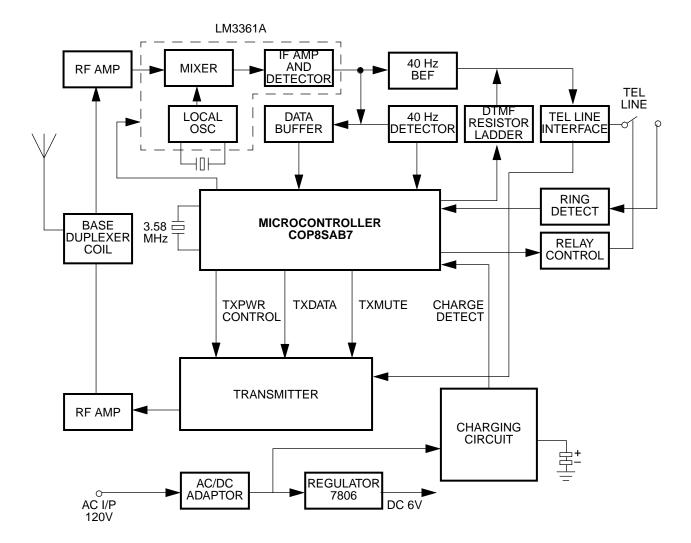

| 4.13 COP8SAC7 BASED AUTOMATED SECURITY/MONT        | TORING                             |  |  |

| APPLICATIONS                                       |                                    |  |  |

| 4.13.1 Typical Application Requirements            | 4-36                               |  |  |

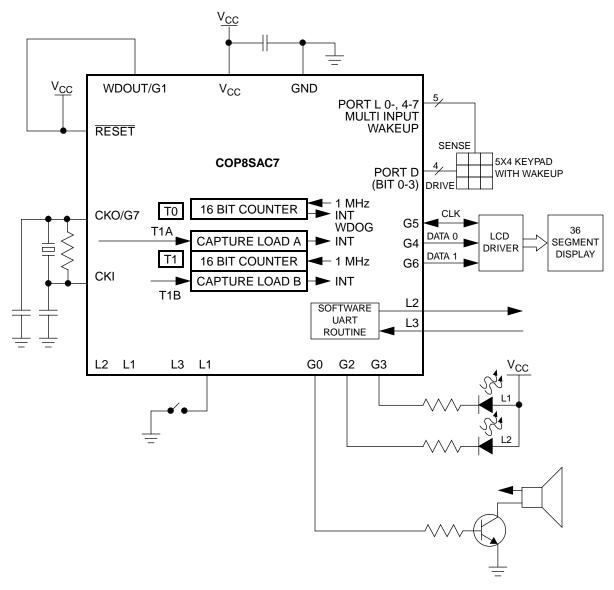

| 4.14 COP8SAC7 Keyboard Applications                | 4-38                               |  |  |

| 4.14.1 Typical Application Requirements            |                                    |  |  |

| 4.14.2 Typical Applications                        |                                    |  |  |

| 4.15 COP8SAA7 CLOSED LOOP TEMPERATURE CONTR        | POL                                |  |  |

| APPLICATIONS                                       |                                    |  |  |

| 4.15.1 Primary System considerations:              | 4-41                               |  |  |

| 4.15.2 Typical Requirements for Motor Control Syst | ems 4-42                           |  |  |

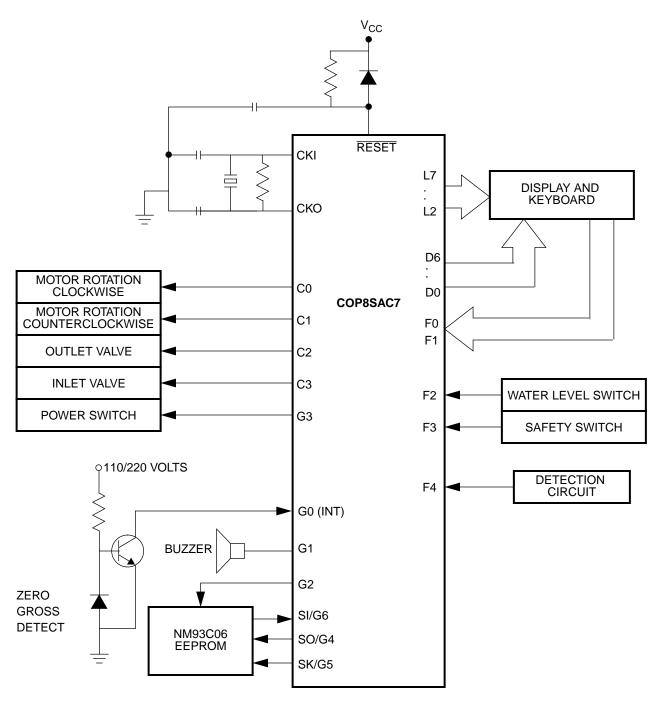

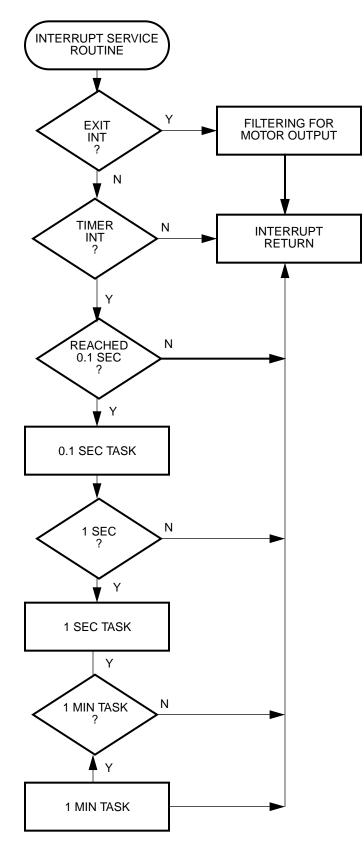

| 4.16 AUTOMATIC WASHING MACHINE                     | 4-43                               |  |  |

| 4.16.1 Reliability and Safety Features             |                                    |  |  |

| 4.16.2 LED or LCD Display Units                    | 4-43                               |  |  |

| 4.16.3 Zero Cross Detection                        | 4-43                               |  |  |

| 4.16.4 Other I/O Functions                         |                                    |  |  |

| 4.16.5 External EEPROM Interface                   |                                    |  |  |

| 4.16.6 Software Considerations                     |                                    |  |  |

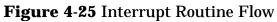

| 4.17 AIR CONDITIONER CONTROLLER                    |                                    |  |  |

| 4.17.1 Temperature Detection                       |                                    |  |  |

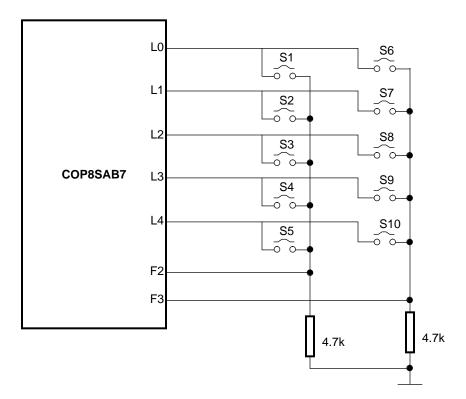

| 4.17.2 Keypad Scanning                             |                                    |  |  |

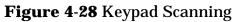

| 4.17.3 Over-Voltage and Under-Voltage Detection .  |                                    |  |  |

|                                                    |                                    |  |  |

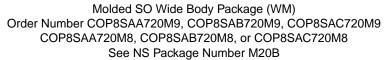

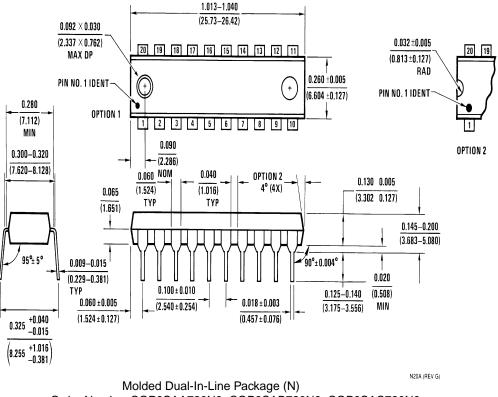

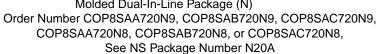

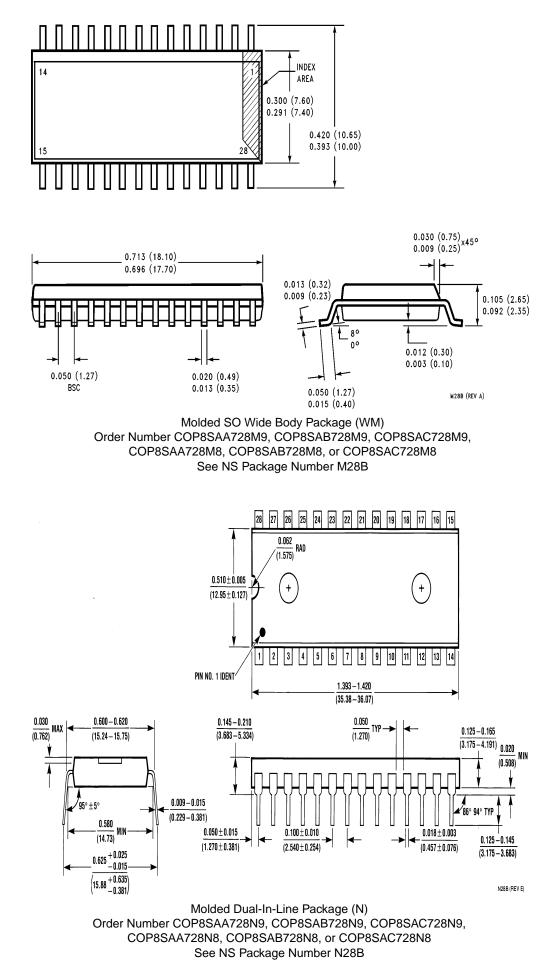

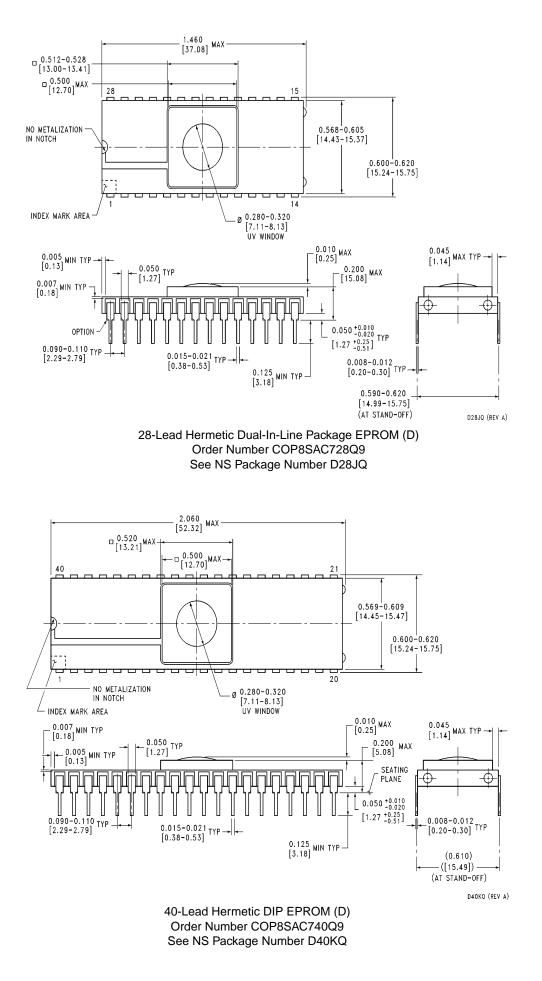

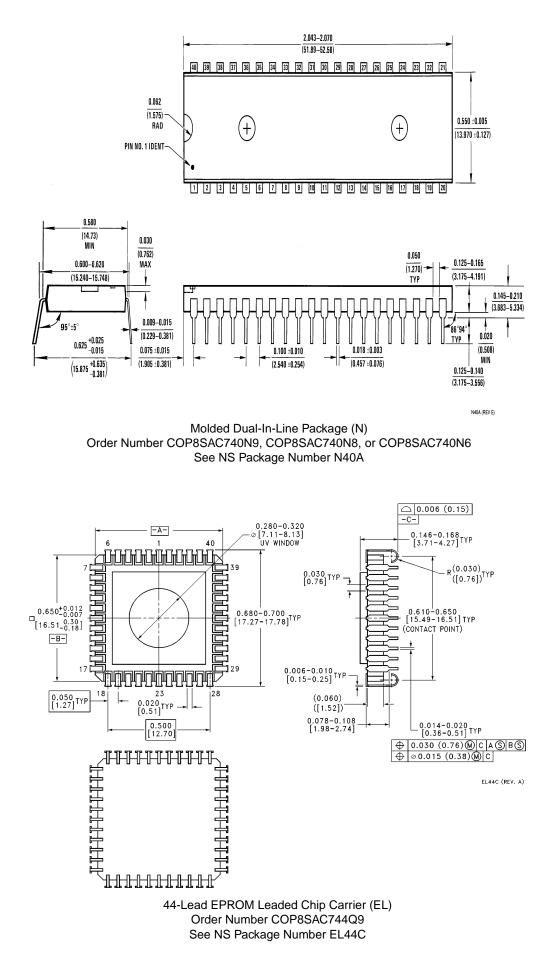

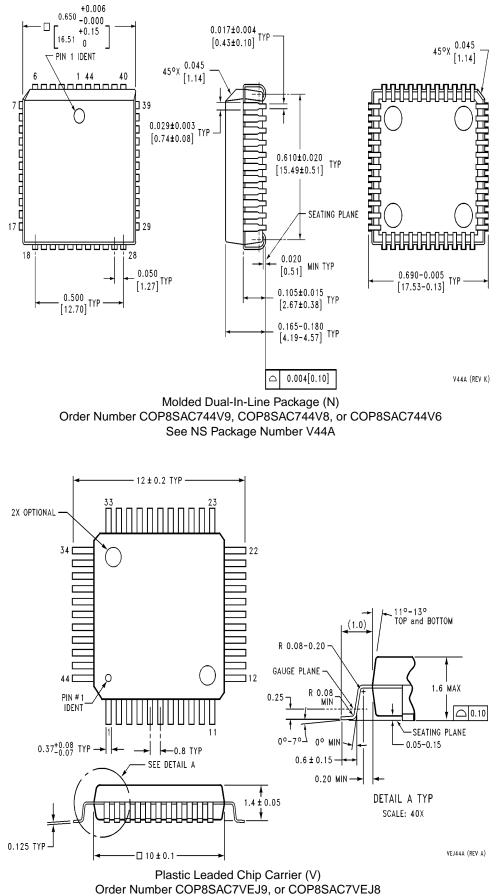

# Appendix A PHYSICAL DIMENSIONS

Index

| Figures     |                                                                    |        |

|-------------|--------------------------------------------------------------------|--------|

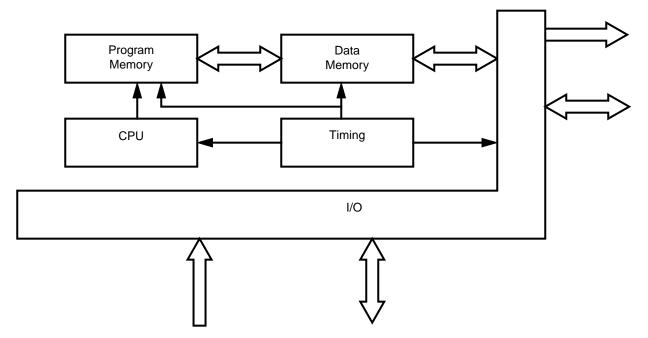

| Figure 1-1  | Microcontroller General Block Diagram.                             | . 1-2  |

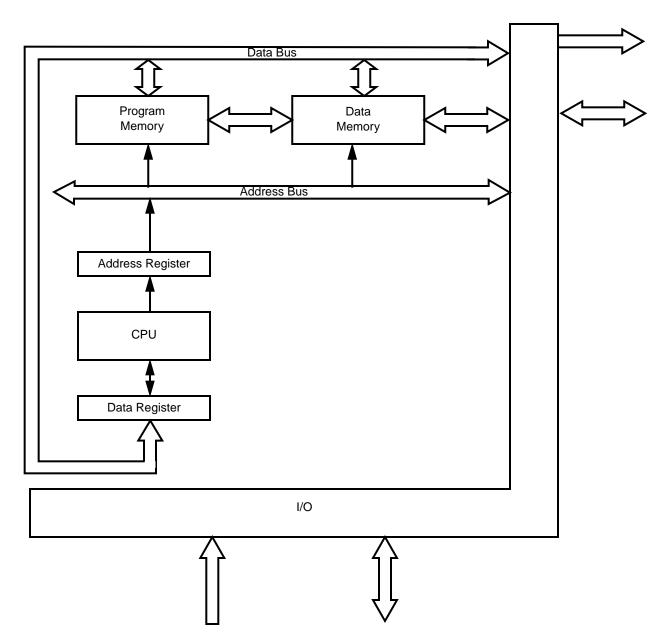

| Figure 1-2  | Microcontroller Operation                                          |        |

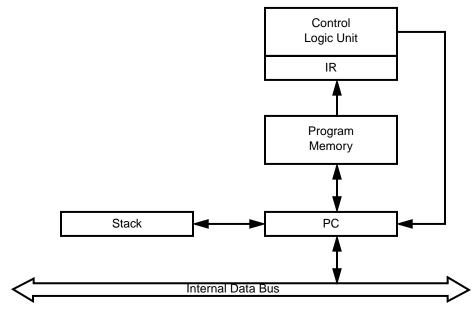

| Figure 1-3  | Program Memory Section                                             | . 1-9  |

| Figure 1-4  | Separate Data and Code Space                                       |        |

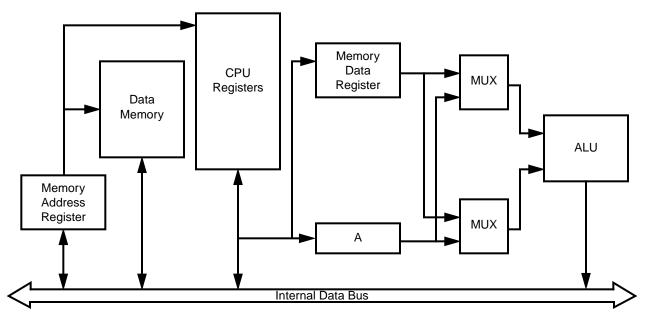

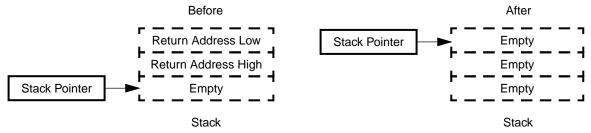

| Figure 1-5  | Adding Two Numbers Using Accumulator Based Machine                 | 1-13   |

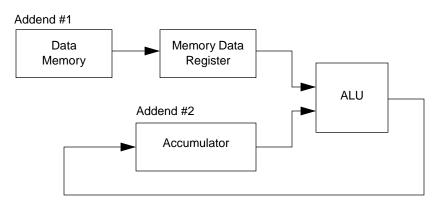

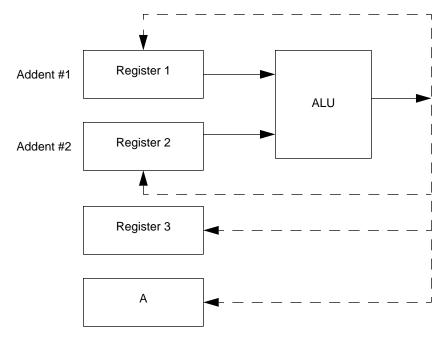

| Figure 1-6  | Adding Two Numbers Using Register Based Machine                    | 1-14   |

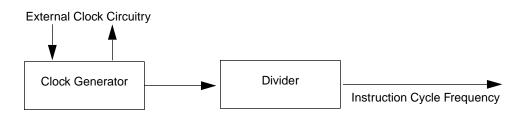

| Figure 1-7  | Clock Generation                                                   | 1-16   |

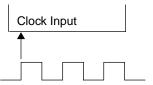

| Figure 1-8  | External Oscillator.                                               | 1-16   |

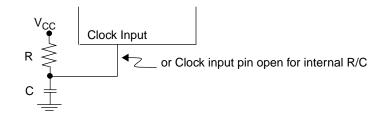

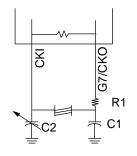

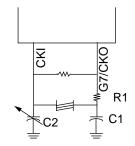

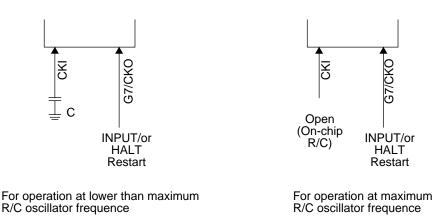

| Figure 1-9  | R/C Oscillator                                                     | 1-16   |

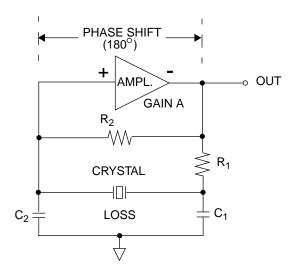

| Figure 1-10 | Phase Shift Oscillator                                             | 1-17   |

| Figure 2-1  | COP8SAx7 Block Diagram                                             | 2-4    |

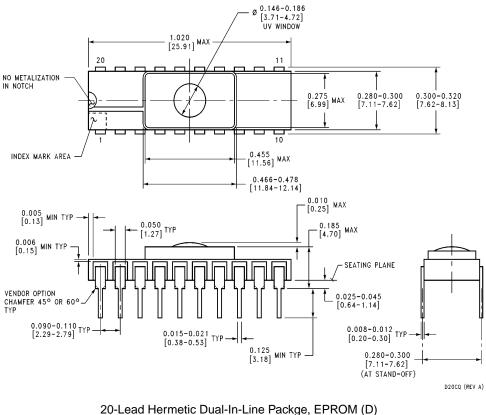

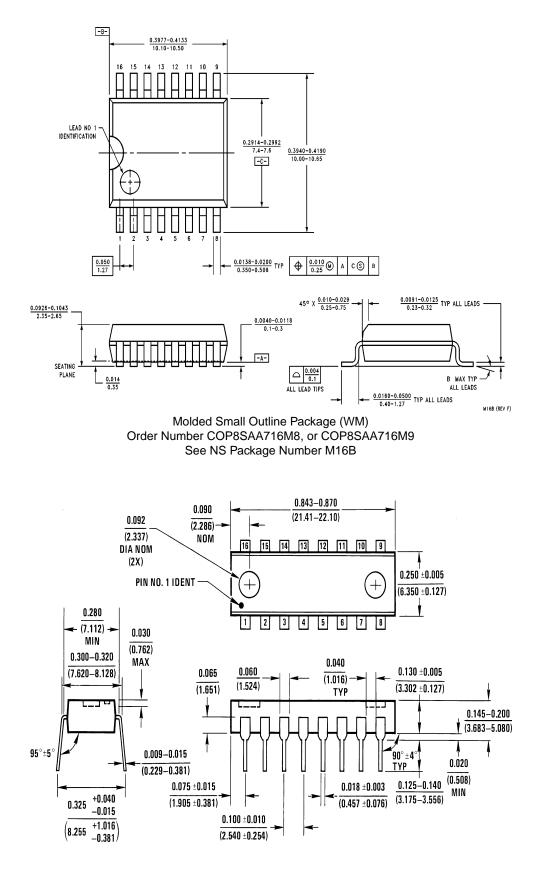

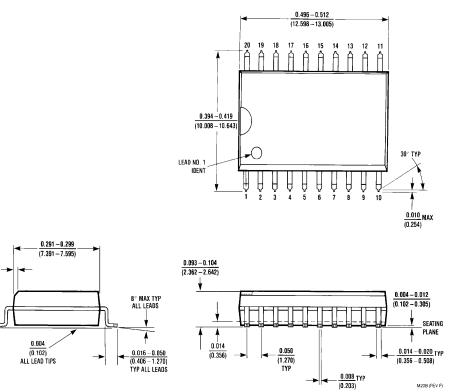

| Figure 2-2  | Connection Diagrams.                                               |        |

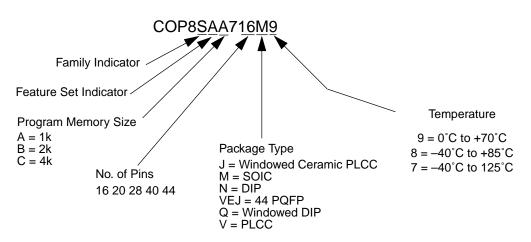

| Figure 2-3  | Part Numbering Scheme                                              |        |

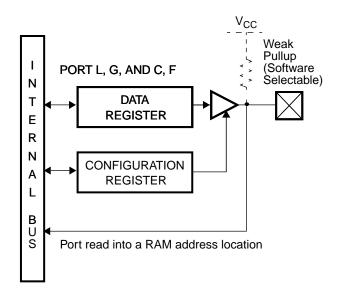

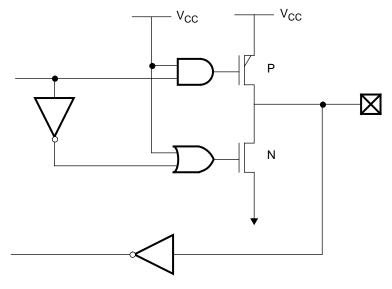

| Figure 2-4  | I/O Port Configurations                                            |        |

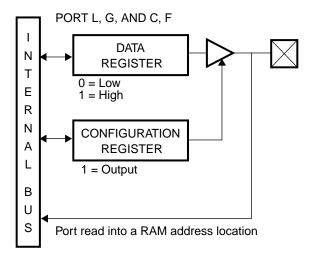

| Figure 2-5  | I/O Port Configurations-Output Mode                                | 2-10   |

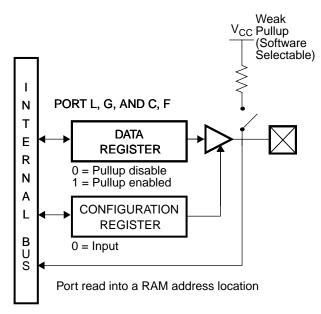

| Figure 2-6  | I/O Port Configurations-Input Mode                                 | 2-11   |

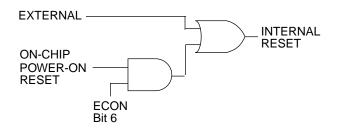

| Figure 2-7  | Reset Logic                                                        |        |

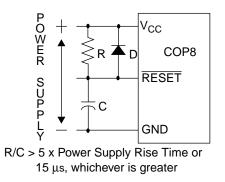

| Figure 2-8  | Reset Circuit Using External Reset                                 |        |

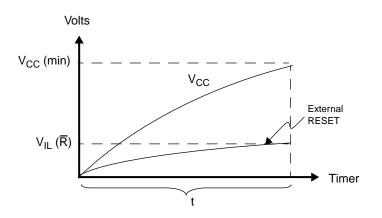

| Figure 2-9  | Dddesired Reset Response Time                                      |        |

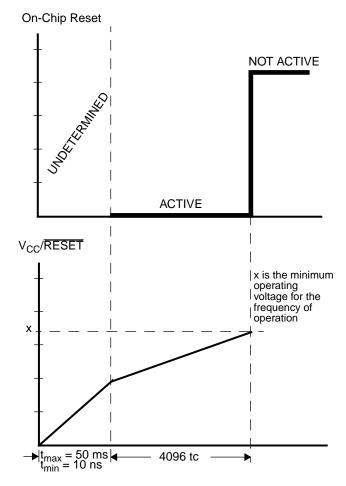

| Figure 2-10 | Reset Timing (Power-On Reset enabled) With $V_{CC}$ Tied to RESET. | 2-18   |

| Figure 2-11 | Reset Circuit Using Power-On Reset                                 | 2-18   |

| Figure 2-12 | Crystal Oscillator                                                 | 2-19   |

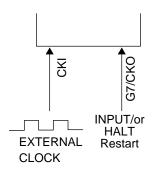

| Figure 2-13 | External Oscillator.                                               |        |

| Figure 2-14 | R/C Oscillator                                                     | 2-21   |

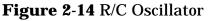

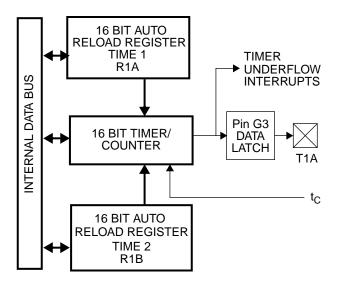

| Figure 2-15 | Timer in PWM Mode                                                  |        |

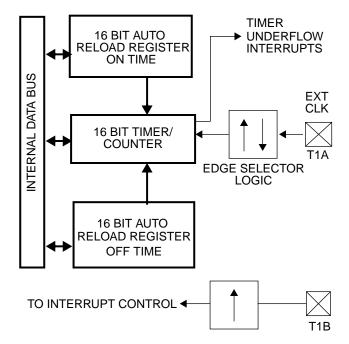

| Figure 2-16 | Timer in External Event Counter Mode                               | 2-25   |

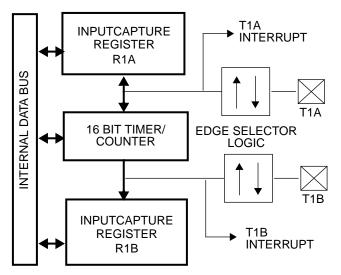

| Figure 2-17 | Timer in Input Capture Mode                                        |        |

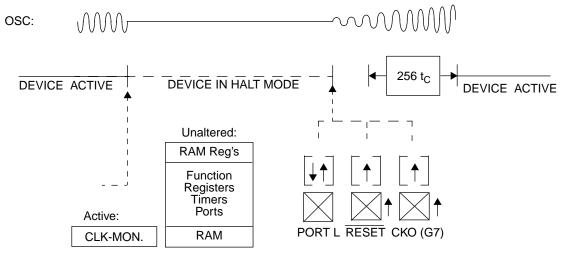

| Figure 2-18 | Wakeup From HALT                                                   | 2-29   |

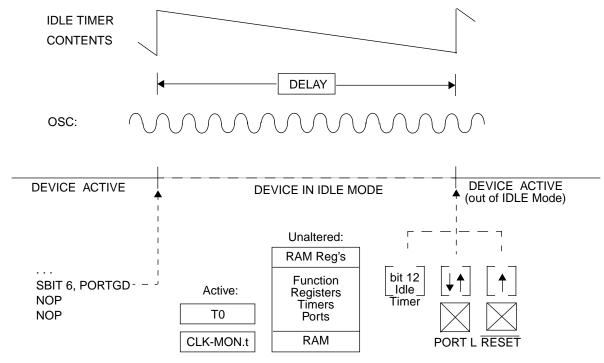

| Figure 2-19 | Wakeup From IDLE                                                   |        |

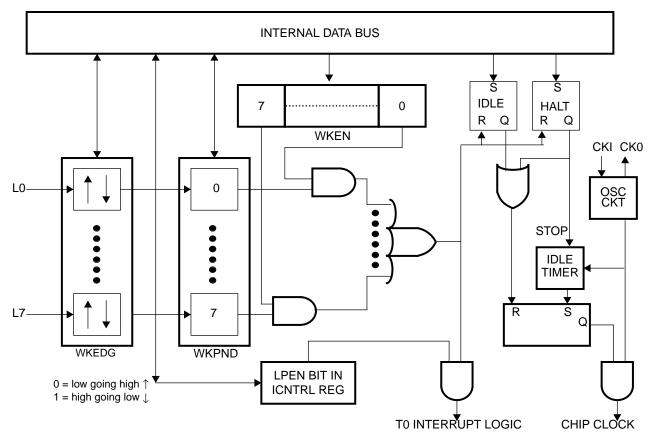

| Figure 2-20 | Multi-Input Wake Up Logic.                                         | 2-31   |

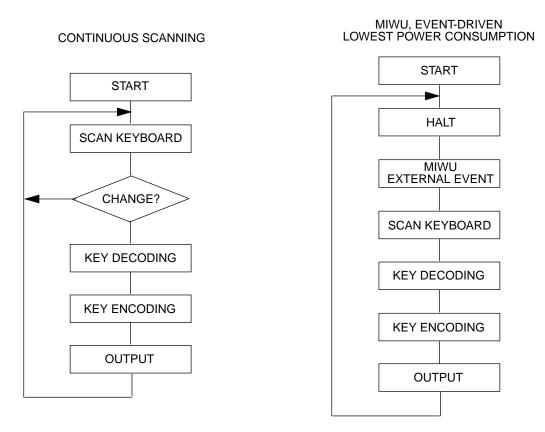

| Figure 2-21 | Keyboard Scanning                                                  | 2-32   |

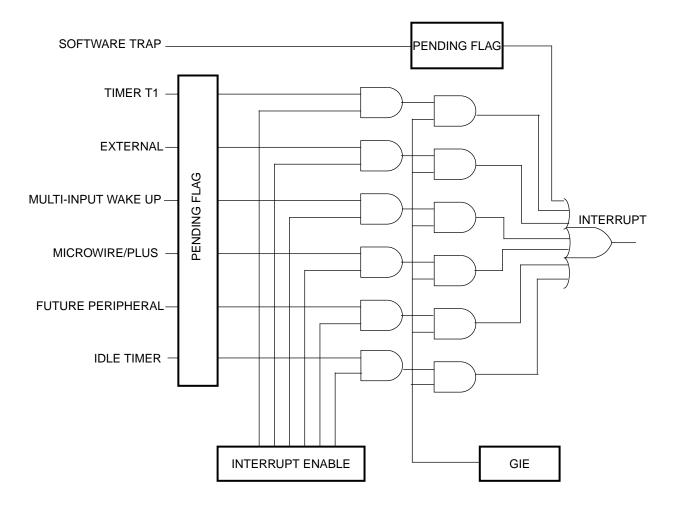

| Figure 2-22 | Interrupt Block Diagram                                            | 2-34   |

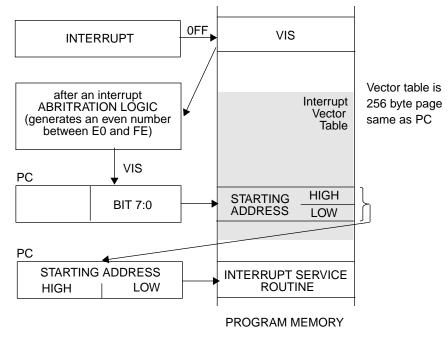

| Figure 2-23 | VIS Operation.                                                     |        |

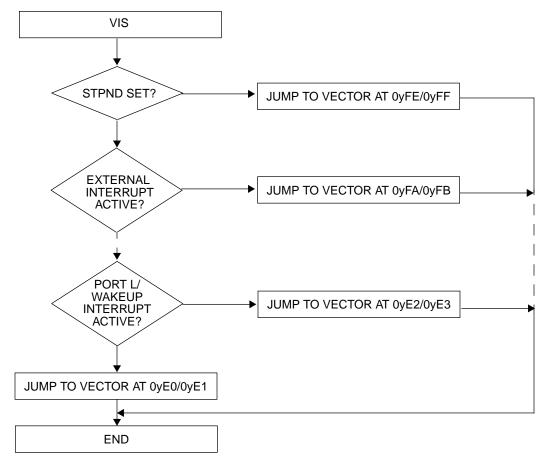

| Figure 2-24 | VIS Flow Chart                                                     |        |

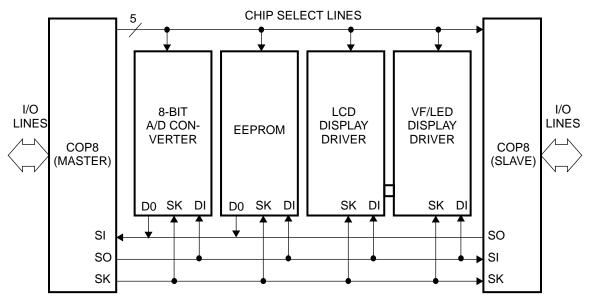

| Figure 2-25 | MICROWIRE/PLUS Application                                         | . 2-47 |

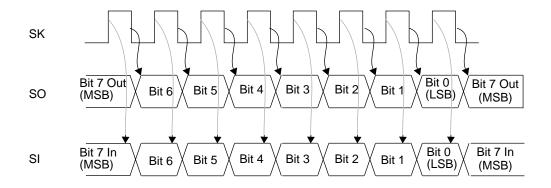

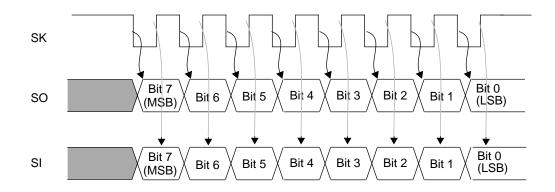

| Figure 2-26 | MICROWIRE/PLUS SPI Mode Interface Timing,                          |        |

|             | Normal SK Mode, SK Idle Phase being Low                            | 2-50   |

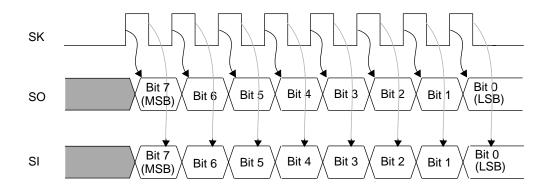

| Figure 2-27 | MICROWIRE/PLUS SPI Mode Interface Timing,                          |        |

|             | Alternate SK Mode, SK Idle Phase being Low                         | 2-50   |

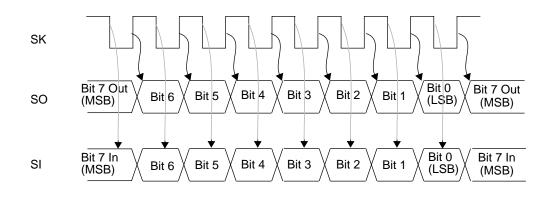

| Figure 2-28 | MICROWIRE/PLUS SPI Mode Interface Timing,                          |        |

|             | Alternate SK Mode, SK Idle Phase being High                        | . 2-51 |

| Figure 2-29 | MICROWIRE/PLUS SPI Mode Interface Timing,                          |        |

|             | Normal SK Mode, SK Idle Phase being High                           |        |

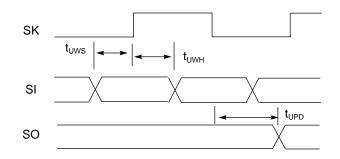

| Figure 2-30 | MICROWIRE/PLUS Timing                                              |        |

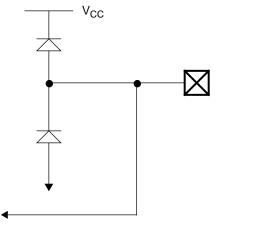

| Figure 2-31 | Ports L/C/G/F Input Protection (Except G6)                         | 2-134  |

| Figure 2-32 | Diode Equivalent of Input Protection                               |        |

| Figure 2-33 | On-Chip ESD Detection/Protection Circuit                           | 2-135  |

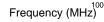

| Figure 2-34 | EMI Improvements                                                   |        |

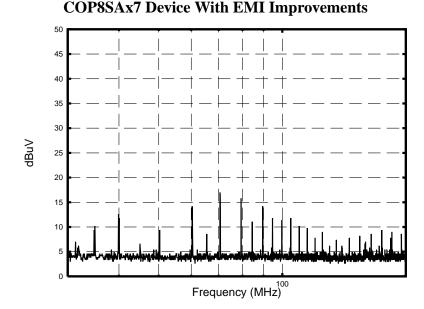

| Figure 2-35 | Block diagram of EMI Circuitry                                     | 2-142  |

x CONTENTS

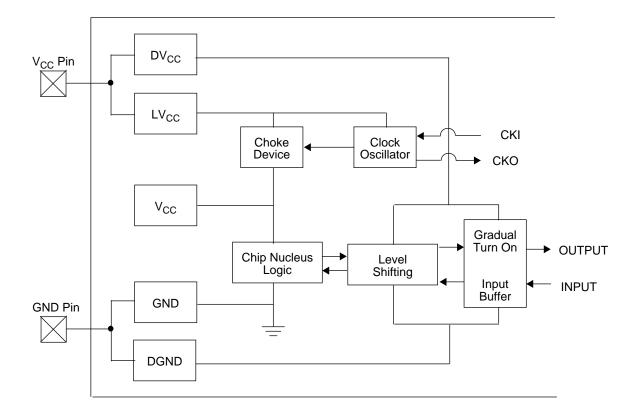

| Figure 3-1  | COP8 iceMASTER Environment                             | . 3-2 |

|-------------|--------------------------------------------------------|-------|

| Figure 3-2  | COP8-DM Environment                                    | . 3-3 |

| Figure 3-3  | EPU-COP8 Tool Environment.                             | . 3-5 |

| Figure 4-1  | Test Circuit.                                          | . 4-2 |

| Figure 4-2  | Flow Chart                                             | . 4-2 |

| Figure 4-3  | MICROWIRE/PLUS Sample Protocol Timing                  | . 4-4 |

| Figure 4-4  | NM93C06-COP8SAx7 Interface                             |       |

| Figure 4-5  | Timer PWM Applications                                 |       |

| Figure 4-6  | PWM Motor Control.                                     | 4-12  |

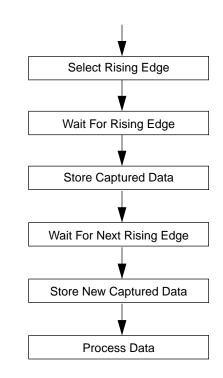

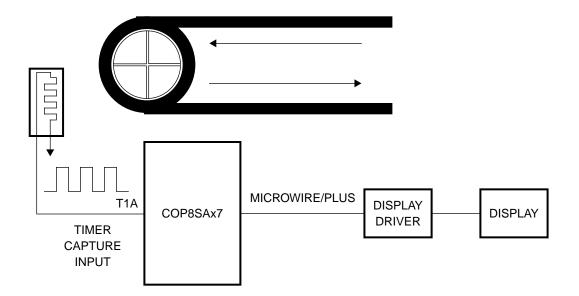

| Figure 4-7  | Timer Capture Application                              | 4-14  |

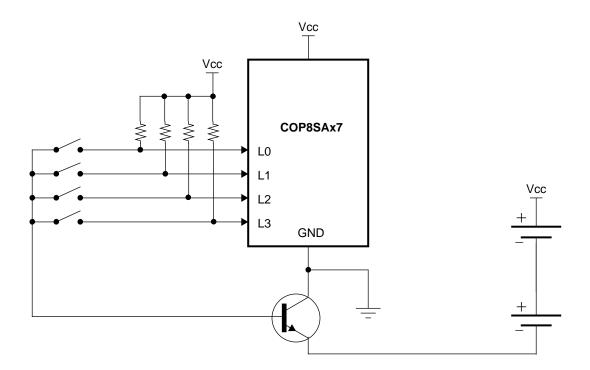

| Figure 4-8  | Power Wakeup Using An NPN Transistor                   | 4-20  |

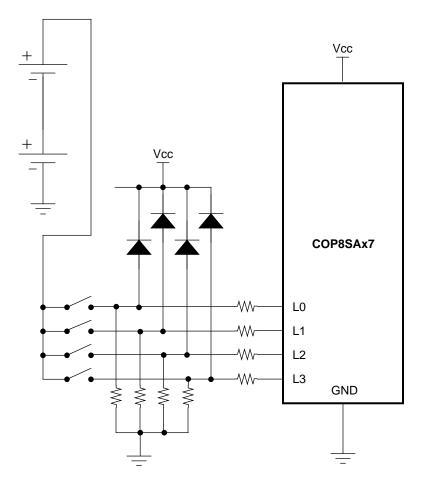

| Figure 4-9  | Power Wakeup Using Diodes And Resistors                | 4-21  |

| Figure 4-10 | Battery-powered Weight Measurement                     |       |

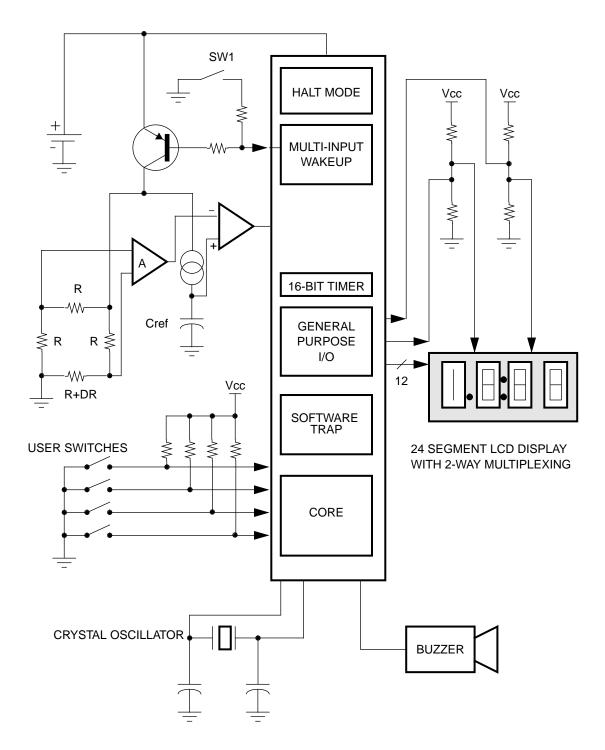

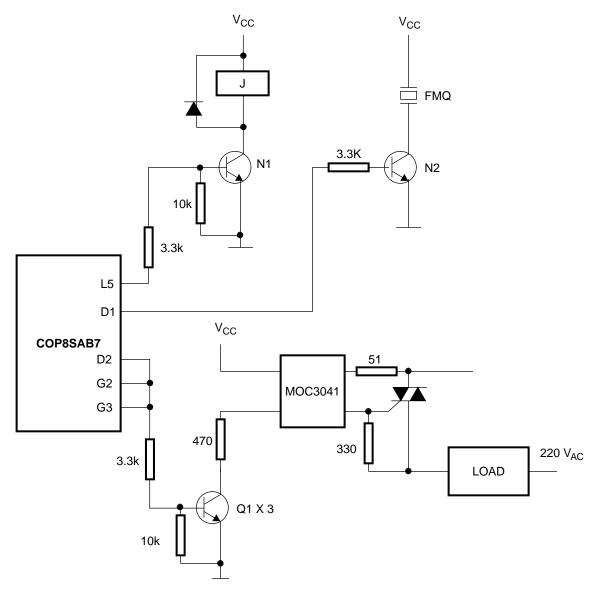

| Figure 4-11 | Industrial Timer Application.                          | 4-24  |

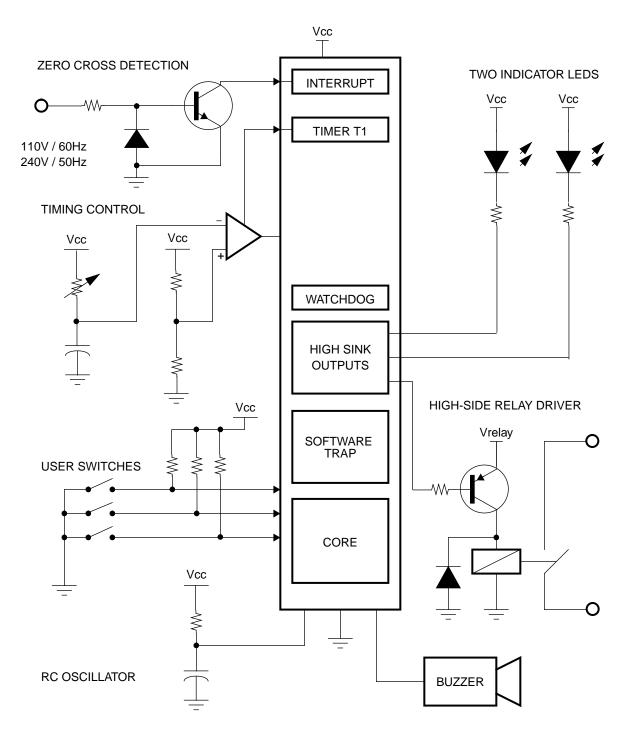

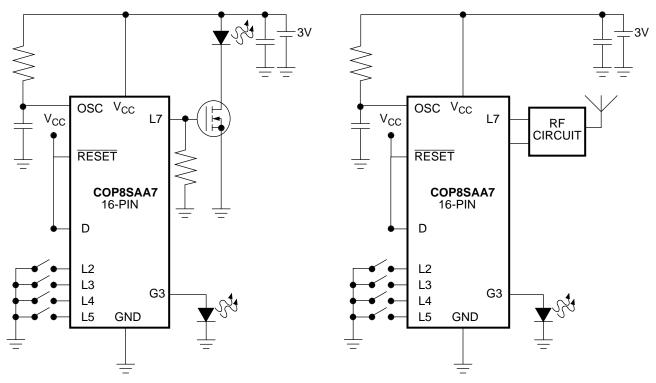

| Figure 4-12 | Transmitter in Single Cell Operation                   | 4-26  |

| Figure 4-13 | Rolling Code IR Transmitter Using External EEPROM      |       |

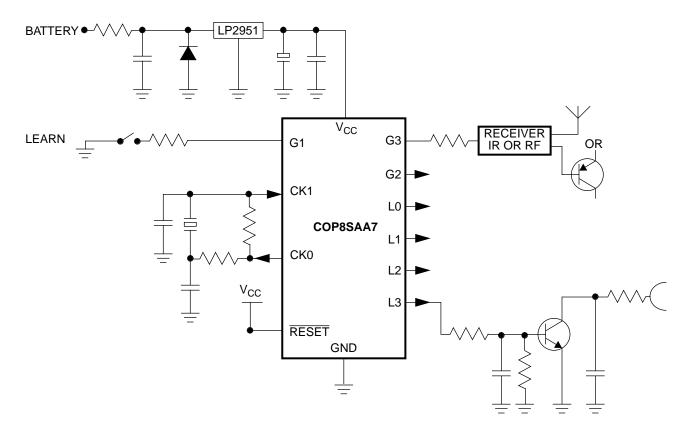

| Figure 4-14 | Rolling Code IR/RF Transmitter Using One-Chip EEPROM   | 4-28  |

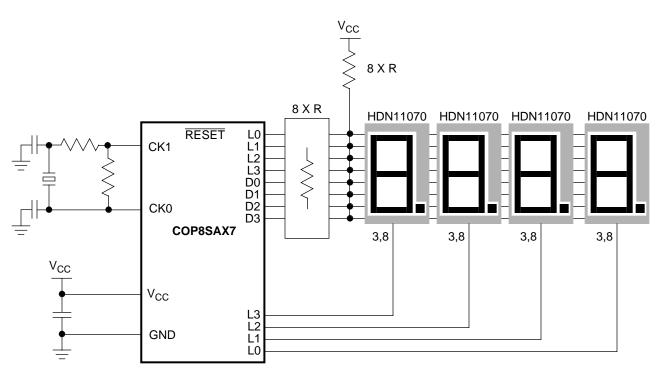

| Figure 4-15 | LED Direct Drive Using COP8SAx7                        | 4-29  |

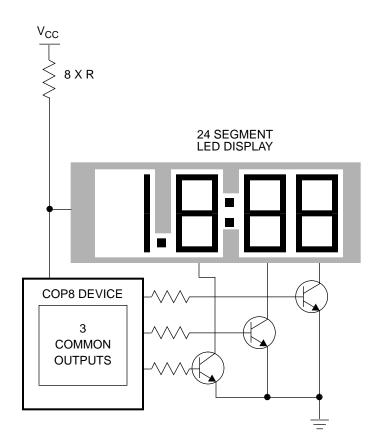

| Figure 4-16 | LED Drive.                                             | 4-30  |

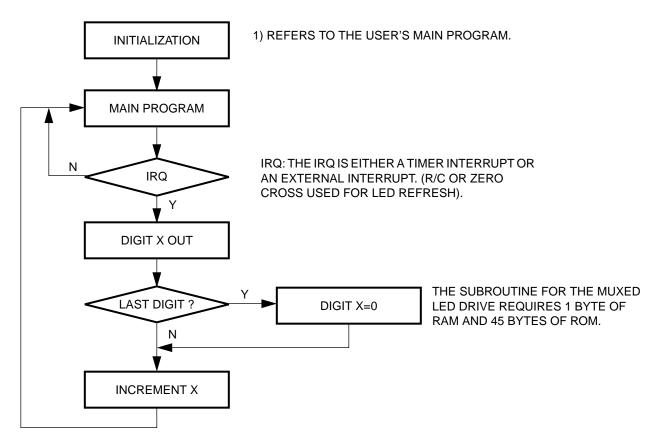

| Figure 4-17 | Four-Way Multiplexed Direct LED Drive                  | 4-31  |

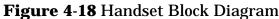

| Figure 4-18 | Handset Block Diagram.                                 | 4-32  |

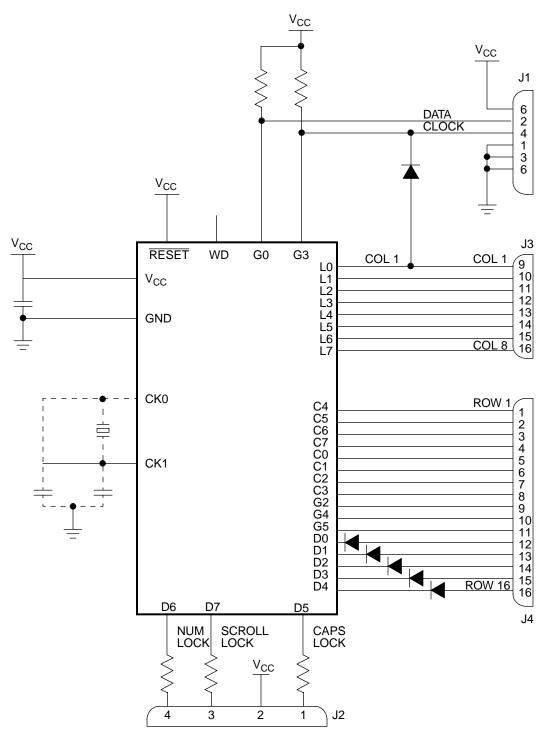

| Figure 4-19 | Base Block Diagram.                                    | 4-33  |

| Figure 4-20 | Example of a Security/Monitoring System                | 4-35  |

| Figure 4-21 | Laptop/Notebook Keyboard Schematics                    | 4-38  |

| Figure 4-22 | Automotive Closed Loop Air Control                     |       |

| Figure 4-23 | Automatic Washing Machine Control Model Using COP8SAC7 |       |

| Figure 4-24 | Main Program Flow                                      | 4-45  |

| Figure 4-25 | Interrupt Routine Flow                                 |       |

| Figure 4-26 | Block Diagram of Air Conditioning Control Module       | 4-47  |

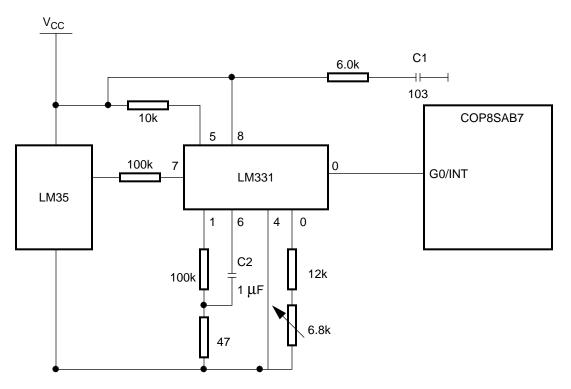

| Figure 4-27 | Temperature Detection Circuit                          | 4-48  |

| Figure 4-28 | Keypad Scanning                                        |       |

| Figure 4-29 | Over-Voltage and Under-Voltage Detection Circuit       | 4-49  |

| Figure 4-30 | Drives Circuits for Fan, Compressor and Buzzer         | 4-50  |

# Tables

| Table 1-1  | Microcontroller Features/Applications Matrix1-4                        |

|------------|------------------------------------------------------------------------|

| Table 2-1  | Program/Data Memory Sizes                                              |

| Table 2-2  | Oscillator Option                                                      |

| Table 2-3  | Crystal Oscillator Configuration, $T_A = 25$ °C, $V_{CC} = 5V$ 2-19    |

| Table 2-4  | R/C Oscillator Configuration, -40°C to +85°C, $V_{CC}$ = 4.5V to 5.5V, |

|            | OSC Freq Variation of ± 35% 2-20                                       |

| Table 2-5  | Interrupt Vector Table                                                 |

| Table 2-6  | WATCHDOG Service Register (WDSVR)2-43                                  |

| Table 2-7  | WATCHDOG Service Window Select                                         |

| Table 2-8  | WATCHDOG Service Actions                                               |

| Table 2-9  | MICROWIRE/PLUS Master Mode Clock Select 2-48                           |

| Table 2-10 | MICROWIRE/PLUS Mode Settings 2-49                                      |

| Table 2-11 | MICROWIRE/PLUS Shift Clock Polarity and Sample/Shift Phase 2-50        |

| Table 2-12 | Electric Field Calculation Results                                     |

#### xii CONTENTS

#### **1.1 WHAT IS A MICROCONTROLLER?**

Microcontroller is an highly integrated single-chip microcomputer. Some of the key elements of a microcontroller include a CPU to process information, program memory to store instructions, data memory to store information, system timing, and input/output sections to communicate with the outside world.

#### 1.1.1 CPU

Central Processing Unit (CPU) is the heart of a microcontroller where all of the arithmetic and logical operations are performed. This is the calculator part of the microcontroller. The CPU gets program instructions from the program memory.

#### 1.1.2 **Program Memory**

Program Memory contains a set of CPU instructions organized into a particular sequence to do a particular task. Program Memory is referred to as Read Only Memory (ROM) or OTP/EPROM. OTP or "One-Time Programmable" can be programmed only once and the program is stored permanently, even when the microcontroller power is turned off. Program memory enables the microcontroller to immediately begin running its program as soon as it is turned on.

#### 1.1.3 Data Memory

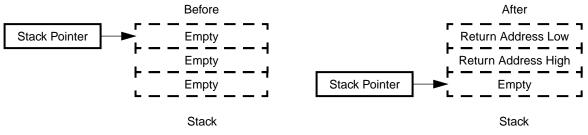

A form of memory that can be both read and written is required for the program stack, data storage, and program variables. This type of memory is commonly referred to as Random Access Memory (RAM). Each memory location has a unique address which the CPU uses to find the information it needs.

A typical microcontroller contains both ROM and RAM type memory.

# 1.1.4 Timing

Microcontrollers use a timing signal, called a clock, to provide a timing reference for program execution, and to determine when data should be written to or read from memory. It also provides timing for on-board peripherals.

# **1.1.5** Inputs/Outputs

Microcontrollers require interface sections to communicate with external circuitry. Input ports allow data and status conditions to be read into the microcontroller while the

output ports allow the microcontroller to affect external logic systems. The interfaces between the microcontroller and the outside world vary with the application, and may include display units, keypads, switches, sensors, relays, motors, and so on.

Figure 1-1 Microcontroller General Block Diagram

# **1.2 WHAT DOES A MICROCONTROLLER REPLACE?**

A microcontroller can do the work of many different types of logic circuits. Discrete logic circuits are permanently wired to perform the function they were designed to do. If the design requirements are changed slightly, an entire printed circuit board or many boards may have to be redesigned to accommodate the change. With a microcontroller performing the logic functions, most changes can be made simply by reprogramming the microcontroller. That is, the software (program) is changed rather than the hardware (logic circuits). This makes the microcontroller a very attractive building block in any digital system. With a microcontroller-based design, the designer can simply add a feature set to the product with minimal software/hardware changes.

Microcontrollers can also be used to replace analog circuitry. Special interface circuits can be used to enable a microcontroller to input and output analog signals.

There are also situations where the designer considers using an ASIC (Application-Specific Integrated Circuit) as logic replacement for control applications. Microcontrollers can efficiently be used as single-chip replacements in such applications with significantly lower development cost and fast time to market.

One of the great benefits of the electronic revolution is that it brought intelligence, and with it adaptability, to traditional electro-mechanical devices. By continuously gathering information on the performance of the device, its operating environment, and other factors, microcontroller intelligence can determine a new and proper strategy and then command the surrounding device to react. The most important of these are the new

#### 1-2 MICROCONTROLLER BASICS

intelligent applications which are adapted in real time to changing conditions, such as the iron that senses when the cloth beneath it has reached the proper temperature and moisture, or the vacuum cleaner that adjusts its speed and brush height automatically to changes in carpet nap.

### **1.3 WHAT ARE MICROCONTROLLER APPLICATIONS?**

Microcontrollers applications are more or less limited only by the user imagination. So pervasive has been this technological revolution that we barely notice it anymore. Microcontrollers now reside in our televisions, keyboards, modems, printers, wristwatches, telephones, cars, household appliances, and every other part of home and work life. The market for microcontrollers continues to expand rapidly, encompassing a wide range of consumer, industrial, automotive, and telecommunications applications. In fact, a typical home today contains over 35 microcontroller-based products — a figure that some sources estimate could grow to almost 250 by the year 2000.

The emergence of new low cost microcontrollers offers a wealth of benefits for today's consumer applications and represent an entirely new profit source for manufacturers. In the past, the high cost of electronics limited the use of microcontrollers to "high tech" applications such as televideo recorders, stereo systems, and high-end durable goods such as washing machines. Today, the application base has broadened to include systems such as coffee machines, irons, shavers, and cleaners, where the introduction of electronics helps to provide product differentiation and allows the inclusion safety features.

| Market Segment |                                              | Applications                                                                                                                                                                                                                        | Applications<br>Features/Functions                                                                                                                                                 | Microcontroller<br>Features Required                                                                                                                                                         |

|----------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Consumer       | Children<br>Toys and<br>Games                | Basketball/Baseball<br>Games<br>Children Electronic<br>Toys<br>Darts<br>Throws<br>Juke Box<br>Pinball<br>Laser Gun                                                                                                                  | Battery Driven<br>Replacing Discrete with<br>Low Cost<br>Driving<br>Piezo/Speaker/LEDs<br>Directly<br>Very Cost Sensitive                                                          | Very Low Price<br>Low Power Consumption<br>Wide Voltage Range<br>High-Current Outputs<br>Small Packages                                                                                      |

|                | Electronic<br>Audio Items                    | Audio Greeting Cards<br>Electronic Musical<br>Equipment                                                                                                                                                                             | Battery Driven<br>Tone Generation<br>Low Power                                                                                                                                     | Wide Voltage Range<br>Low Power Consumption<br>Efficient Table Lookup<br>Flexible Timer                                                                                                      |

|                | Electronic<br>Appliances<br>and Tools        | Small Appliances:<br>Irons<br>Coffee Makers<br>Digital Scales<br>Microwave Ovens<br>Cookers<br>Food Processors<br>Blenders                                                                                                          | Low Cost Power Supply<br>Temp Measurement<br>Safety Features<br>Noise Immunity<br>Driving<br>LEDs/Relays/Heating<br>Elements                                                       | Brown Out Detection<br>On-Board Comparator<br>High-Current Outputs<br>Watchdog/Software<br>Interrupt<br>Schmitt Trigger Inputs<br>16-Bit PWM Timer                                           |