# **AFBR-53D3** RoHS Compliant 850 nm VCSEL 1x9 Fiber Optic Transceivers for Fibre Channel

# **Data Sheet**

# Description

The AFBR-53D3 transceiver family from Avago Technologies allows the system designer to implement a range of solutions for multimode and single mode Fibre Channel applications. The overall Avago Technologies transceiver product consists of three sections: the transmitter and receiver optical subassemblies, an electrical subassembly, and the package housing which incorporates a duplex SC connector receptacle.

## **Transmitter Section**

The transmitter section of the AFBR-53D3 consists of an 850 nm Vertical Cavity Surface Emitting Laser (VCSEL) in an optical subassembly (OSA), which mates to the fiber cable. The OSA is driven by a custom, silicon bipolar IC which converts differential PECL logic signals (ECL referenced to a +5 V supply) into an analog laser diode drive current.

# **Receiver Section**

The receiver of the AFBR-53D3 includes a silicon PIN photodiode mounted together with a custom, silicon bipolar transimpedance preamplifier IC in an OSA. This OSA is mated to a custom silicon bipolar circuit that provides postamplification and quantization.

The post-amplifier also includes a Signal Detect circuit which provides a PECL logic-high output upon detection of a usable input optical signal level. This singleended PECL output is designed to drive a standard PECL input through a 50  $\Omega$  PECL load.

# Features

- AFBR-53D3 is Compliant with ANSI X3.297-1996 Fibre Channel Physical Interface FC-PH-2 Revision 7.4 Proposed Specifications for 100-M5-SN-I and 100-M6-SN-I signal interfaces

- AFBR-53D3 Family Fully RoHS Compliant

- Industry Standard Mezzanine Height 1 x 9 Package Style with Integral Duplex SC Connector

- Performance: AFBR-53D3: 300 m over 62.5/125 μm MMF 500 m over 50/125 μm MMF

- IEC 60825-1 Class 1/CDRH Class I Laser Eye Safe

- Single +5 V Power Supply Operation with PECL Logic Interfaces

- Wave Solderable and Aqueous Wash Process Compatible

## Applications

- Mass Storage Systems I/O

- Computer Systems I/O

- High-speed Peripheral Interface

- High-speed Switching Systems

- Host Adapter I/O

- RAID Cabinets

## **Related Products**

- Physical Layer ICs Available for optical or Copper Interface (HDMP-1536A/46A)

- Versions of this Transceiver Module also available for Gigabit ethernet (AFBR-53D5 Family)

- Gigabit Interface Converters (GBIC) for Fibre Channel (ZX, SX, LX)

## **Package and Handling Instructions**

#### Flammability

The AFBR-53D3 transceiver family housing is made of high strength, heat resistant, chemically resistant, and UL 94V-0 flame retardant plastic.

## **Recommended Solder and Wash Process**

The AFBR-53D3 transceiver family is compatible with industry-standard wave or hand solder processes.

#### **Process plug**

This transceiver is supplied with a process plug (HFBR-5000) for protection of the optical ports within the duplex SC connector receptacle. This process plug prevents contamination during wave solder and aqueous rinse as well as during handling, shipping and storage. It is made of a hightemperature, molded sealing material that can withstand +80°C and a rinse pressure of 110 lbs per square inch.

#### **Recommended Solder fluxes**

Solder fluxes used with the AFBR-53D3 should be water-soluble, organic fluxes. Recommended solder fluxes include Lonco 3355-11 from London Chemical West, Inc. of Burbank, CA, and 100 Flux from Alpha-Metals of Jersey City, NJ.

## **Recommended Cleaning/Degreasing Chemicals**

Alcohols: methyl, isopropyl, isobutyl.

Aliphatics: hexane, heptane. Other: soap solution, naphtha. Do not use partially halogenated hydrocarbons such as 1,1.1 trichloroethane, ketones such as MEK, acetone, chloroform, ethyl acetate, methylene dichloride, phenol, methylene chloride, or N-methylpyrolldone. Also, Avago Technologies does not recommend the use of cleaners that use halogenated hydrocarbons because of their potential environmental harm.

#### **Regulatory Compliance**

(See the Regulatory Compliance Table for transceiver performance) The overall equipment design will determine the certification level. The transceiver performance is offered as a figure of merit to assist the designer in considering their use in equipment designs.

#### Electrostatic Discharge (ESD)

There are two design cases in which immunity to ESD damage is important. The first case is during handling of the transceiver prior to mounting it on the circuit board. It is important to use normal ESD handling precautions for ESD sensitive devices. These precautions include using grounded wrist straps, work benches, and floor mats in ESD controlled areas. The transceiver performance has been shown to provide adequate performance in typical industry production environments. The second case to consider is static discharges to the exterior of the equipment chassis containing the transceiver parts. To the extent that the duplex SC connector receptacle is exposed to the outside of the equipment chassis it may be subject to whatever system-level ESD test criteria that the equipment is intended to meet. The transceiver performance is more robust than typical industry equipment requirements of today.

#### **Electromagnetic Interference (EMI)**

Most equipment designs utilizing these high-speed transceivers from Avago Technologies will be required to meet the requirements of FCC in the United States, CENELEC EN55022 (CISPR 22) in Europe and VCCI in Japan. Refer to EMI section (page 5) for more details.

#### Immunity

Equipment utilizing these transceivers will be subject to radio-frequency electromagnetic fields in some environments. These transceivers have good immunity to such fields due to their shielded design.

#### **Eye Safety**

These laser-based transceivers are classified as AEL Class I (U.S. 21 CFR(J) and AEL Class 1 per EN 60825-1 (+A11). They are eye safe when used within the data sheet limits per CDRH. They are also eye safe under normal operating conditions and under all reasonably foreseeable single fault conditions per EN60825-1. Avago Technologies has tested the transceiver design for compliance with the requirements listed below under normal operating conditions and under single fault conditions where applicable. TUV Rheinland has granted certification to these transceivers for laser eye safety and use in EN 60950 and EN 60825-2 applications. Their performance enables the transceivers to be used without concern for eye safety up to 7 V transmitter VCC.

## **CAUTION:**

There are no user serviceable parts nor any maintenance required for the AFBR-53D3. All adjustments are made at the factory before shipment to our customers. Tampering with or modifying the performance of the AFBR-53D3 will result in voided product warranty. It may also result in improper operation of the AFBR-53D3 circuitry, and possible overstress of the laser source. Device degradation or product failure may result. Connection of the AFBR-53D3 to a nonapproved optical source, operating above the recommended absolute maximum conditions or operating the AFBR-53D3 in a manner inconsistent with its design and function may result in hazardous radiation exposure and may be considered an act of modifying or manufacturing a laser product. The person(s) performing such an act is required by law to recertify and reidentify the laser product under the provisions of U.S. 21 CFR (Subchapter J).

### **Regulatory Compliance**

| Feature                                                   | Test Method                                                                                                                                                                        | Performance                                                                                                                                       |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrostatic Discharge (ESD) to the Electrical Pins      | MIL-STD-883C<br>Method 3015.4                                                                                                                                                      | Class 1 (>2000V).                                                                                                                                 |

| Electrostatic Discharge (ESD) to the Duplex SC Receptacle | Variation of IEC 801-2                                                                                                                                                             | Typically withstand at least 15 kV<br>without damage when the duplex SC<br>connector receptacle is contacted by a<br>Human Body Model probe.      |

| Electromagnetic Interference<br>(EMI)                     | FCC Class B<br>CENELEC EN55022 Class B<br>(CISPR 22A)<br>VCCI Class I                                                                                                              | Margins are dependent on customer<br>board and chassis designs.                                                                                   |

| Immunity                                                  | Variation of IEC 801-3                                                                                                                                                             | Typically show no measurable effect<br>from a 3 V/m field swept from 27 to<br>1000 MHz applied to the transceiver<br>without a chassis enclosure. |

| Laser Eye Safety and Equipment<br>Type Testing            | US 21 CFR, Subchapter J per Paragraphs 1002.10 and 1002.12                                                                                                                         | AEL Class I, FDA/CDRH<br>AFBR-53D3 Accenssion #9720151-03                                                                                         |

|                                                           | EN 60825-1: 1994 +A11<br>EN 60825-2: 1994<br>EN 60950: 1992 + A1 + A2 + A3                                                                                                         | AEL Class 1, TUV Rheinland of North<br>America AFBR-53D3<br>Certificate #E9771047.09<br>Protection Class III                                      |

| Component Recognition                                     | Underwriters Laboratories and Canadian<br>Standards Association Joint Component<br>Recognition for Information Technology<br>Equipment Including Electrical Business<br>Equipment. | UL File E173874                                                                                                                                   |

#### **APPLICATION SUPPORT**

#### **Optical Power Budget and Link Penalties**

The worst-case Optical Power Budget (OPB) in dB for a fiberoptic link is determined by the difference between the minimum transmitter output optical power (dBm avg.) and the lowest receiver sensitivity (dBm avg.). This OPB provides the necessary optical signal range to establish a working fiber-optic link. The OPB is allocated for the fiber-optic cable length and the corresponding link penalties. For proper link performance, all penalties that affect the link performance must be accounted for within the link optical power budget.

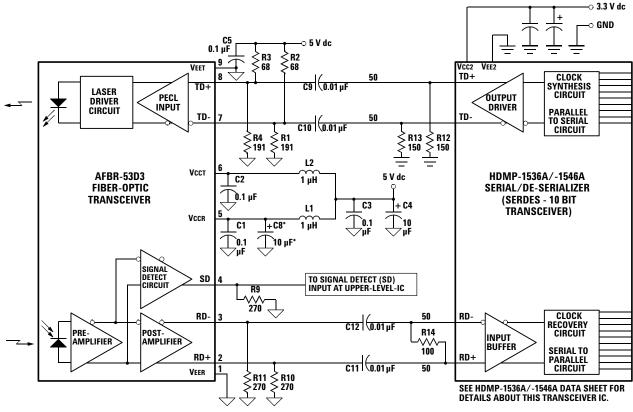

#### **Data Line Interconnections**

Avago Technologies' AFBR-53D3 fiberoptic transceiver is designed to directly couple to +5 V PECL signals. The transmitter inputs are internally dc-coupled to the laser driver circuit from the transmitter input pins (pins 7, 8). There is no internal, capacitivelycoupled 50 Ohm termination resistance within the transmitter input section. The transmitter driver circuit for the laser light source is a dc-coupled circuit. This circuit regulates the output optical power. The regulated light output will maintain a constant output optical power provided the data pattern is reasonably balanced in duty factor. If the data duty factor has long, continuous state times (low or high data duty factor), then the output optical power will gradually change its average output optical power level to its preset value.

As for the receiver section, it is internally AC-coupled between the preamplifier and the postamplifier stages. The actual Data and Data-bar outputs of the postamplifier are DC-coupled to their respective output pins (pins 2, 3). Signal Detect is a single-ended, +5 V PECL output signal that is dc-coupled to pin 4 of the module. Signal Detect should not be accoupled externally to the follow-on circuits because of its infrequent state changes.

Caution should be taken to account for the proper interconnection between the supporting Physical Layer integrated circuits and this AFBR-53D3 transceiver. Figure 3 illustrates a recommended interface circuit for interconnecting to a +5 V dc PECL fiber-optic transceiver.

Some fiber-optic transceiver suppliers' modules include internal capacitors, with or without 50  $\Omega$  termination, to couple their Data and Data-bar lines to the I/O pins of their module. When designing to use these type of transceivers along with Avago Technologies transceivers, it is important that the interface circuit can accommodate either internal or external capacitive coupling with 50  $\Omega$  termination components for proper operation of both transceiver designs. The internal dccoupled design of the AFBR-53D3 I/O connections was done to provide the designer with the most flexibility for interfacing to various types of circuits.

#### **Eye Safety Circuit**

For an optical transmitter device to be eye-safe in the event of a single fault failure, the transmitter must either maintain normal, eyesafe operation or be disabled. In the AFBR-53D3 there are three key elements to the laser driver safety circuitry: a monitor diode, a window detector circuit and direct control of the laser bias. The window detection circuit monitors the average optical power using the monitor diode. If a fault occurs such that the transmitter dc regulation circuit cannot maintain the preset bias conditions for the laser emitter within  $\pm 20\%$ , the transmitter will automatically be disabled. Once this has occurred, only an electrical power reset will allow an attempted turn-on of the transmitter.

#### Signal Detect

The Signal Detect circuit provides a deasserted output signal that implies the link is open or the transmitter is OFF. The Signal Detect threshold is set to transition from a high to low state between the minimum receiver input optional power and -30 dBm avg. input optical power indicating a definite optical fault (e.g. unplugged connector for the receiver or transmitter, broken fiber, or failed far-end transmitter or data source). A Signal Detect indicating a working link is functional when receiving encoded 8B/I0B characters. The Signal Detect does not detect receiver data error or error-rate. Data errors are determined by Signal processing following the transceiver.

#### **Electromagnetic Interference (EMI)**

One of a circuit board designer's foremost concerns is the control of electromagnetic emissions from electronic equipment. Success in controlling generated Electromagnetic Interference (EMI) enables the designer to pass a governmental agency's EMI regulatory standard; and more importantly, it reduces the possibility of interference to neighboring equipment. There are three options available for the AFBR-53D3 with regard to EMI shielding which provide the designer with a means to achieve good EMI performance. The EMI performance of an enclosure using these transceivers is dependent on the chassis design. Avago Technologies encourages using standard RF suppression practices and avoiding poorly EMI-sealed enclosures.

The first configuration is a standard AFBR-53D3 fiber optic transceiver that has no external EMI shield. This unit is for applications where EMI is either not an issue for the designer, the unit resides completely inside a shielded enclosure, or the module is used in a low density, extremely quiet application.

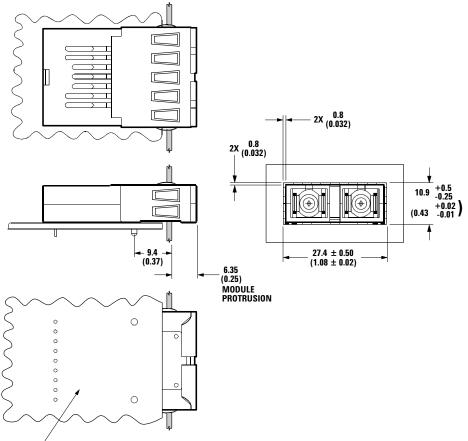

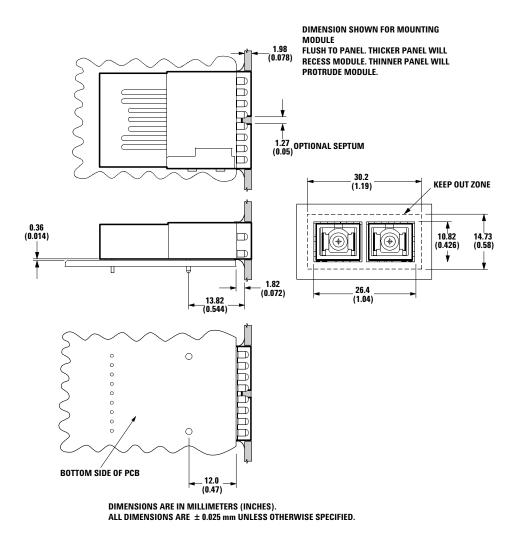

The second configuration, option EZ, is for EMI shielding applications where the position of the transceiver module will extend outside the equipment enclosure. The external metal shield of the transceiver helps locally to terminate EM fields to the chassis to prevent their emissions outside the enclosure. This metal shield contacts the panel or enclosure on the inside of the aperture on all but the bottom side of the shield and provides a good RF connection to the panel. This option can accommodate various panel or enclosure thickness, i.e., .04 in. min. to 0.10 in. max. The reference plane for this panel thickness variation is from the front surface of the panel or enclosure. The recommended length for protruding the AFBR-53D3 EM transceiver beyond the front surface of the panel or enclosure is 0.25 in. With this option, there is flexibility of positioning the module to fit the specific need of the enclosure design. (See Figure 6 for the mechanical drawing dimensions of this shield.)

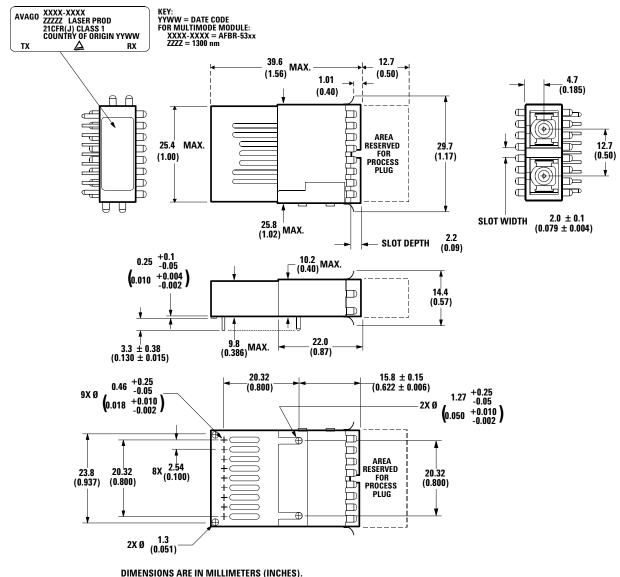

The third configuration, option FZ, is for applications that are designed to have a flush mounting of the module with respect to the front of the panel or enclosure. The flush-mount design accommodates a large variety of panel thickness, i.e., 0.04 in. min. to 0.10 in. max. Note the reference plane for the flushmount design is the interior side of the panel or enclosure. The recommended distance from the centerline of the transceiver front solder posts to the inside wall of the panel is 0.55 in. This option contacts the inside panel or enclosure wall on all four sides of this metal shield.

The two designs are comparable in their shielding effectiveness. Both design options connect only to the equipment chassis and not to the signal or logic ground of the circuit board within the equipment closure. The front panel aperture dimensions are recommended in Figures 7 and 9. When layout of the printed circuit board is done to incorporate these metal-shielded transceivers, keep the area on the printed circuit board directly under the metal shield free of any components and circuit board traces. For additional EMI performance advantage, use duplex SC fiber-optic connectors that have low metal content inside them. This lowers the ability of the metal fiber-optic connectors to couple EMI out through the aperture of the panel or enclosure.

#### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause catastrophic damage to the device. Limits apply to each parameter in isolation, all other parameters having values within the recommended operating conditions. It should not be assumed that limiting values of more than one parameter can be applied to the product at the same time. Exposure to the absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                              | Symbol          | Min. | Тур. | Max.            | Unit | Reference |

|----------------------------------------|-----------------|------|------|-----------------|------|-----------|

| Storage Temperature                    | Ts              | -40  |      | 100             | °C   |           |

| Supply Voltage                         | V <sub>cc</sub> | -0.5 |      | 7.0             | V    | 1         |

| Data Input Voltage                     | V               | -0.5 |      | V <sub>cc</sub> | V    |           |

| Transmitter Differential Input Village | VD              |      |      | 1.6             | V    | 2         |

| Output Current                         | ID              |      |      | 50              | mA   |           |

| Relative Humidity                      | RH              | 5    |      | 95              | %    |           |

## **Recommended Operating Conditions**

| Parameter                              | Symbol                            | Min.   | Тур. | Max.   | Unit       | Reference |

|----------------------------------------|-----------------------------------|--------|------|--------|------------|-----------|

| Ambient Operating Temperature          | T <sub>A</sub>                    | 0      |      | 70     | °C         | 3         |

| Case Temperature                       | Tc                                |        |      | 90     | °C         | 4         |

| Supply Voltage                         | Vcc                               | 4.75   |      | 5.25   | V          |           |

| Power Supply Rejection                 | PSR                               |        | 50   |        | $mV_{P-P}$ | 5         |

| Transmitter Data Input Voltage - Low   | $V_{\text{IL}}$ - $V_{\text{CC}}$ | -1.810 |      | -1.475 | V          | 6         |

| Transmitter Data Input Voltage - High  | V <sub>IH</sub> -V <sub>CC</sub>  | -1.165 |      | -0.880 | V          | 6         |

| Transmitter Differential Input Voltage | VD                                | 0.3    |      | 1.6    | V          |           |

| Data Output Load                       | R <sub>DL</sub>                   | 50     |      |        | Ω          | 7         |

| Signal Detect Output Load              | R <sub>SDL</sub>                  | 50     |      |        | Ω          | 7         |

#### **Process Compatibility**

| Parameter                             | Symbol                            | Min. | Тур. | Max.   | Unit    | Reference |

|---------------------------------------|-----------------------------------|------|------|--------|---------|-----------|

| Hand Lead Soldering Temperature /Time | $T_{\text{SOLD}}/t_{\text{SOLD}}$ |      |      | 260/10 | °C/sec. |           |

| Wave Soldering and Aqueous Wash       | $T_{\text{SOLD}}/t_{\text{SOLD}}$ |      |      | 260/10 | °C/sec. | 8         |

Notes:

1. The transceiver is class 1 eye safe up to VCC = 7 V.

2. This is the maximum voltage that can be applied across the Differential Transmitter Data Inputs without damaging the input circuit.

3. 2 m/s air flow required.

4. Case temperature measurement referenced to the center-top of the internal metal transmitter shield.

6. Compatible with 10 K, 10 KH, and 100 K ECL and PECL input signals.

7. The outputs are terminated to VCC -2 V.

8. Aqueous wash pressure <110 psi.

<sup>5.</sup> Tested with a 50 mVP-P sinusoidal signal in the frequency range from 500 Hz to 1500 kHz on the VCC supply with the recommended power supply filter in place. Typically less than a 0.25 dB change in sensitivity is experienced.

## AFBR-53D3 Family, 850 nm VCSEL

#### **Transmitter Electrical Characteristics**

(TA = 0°C to +70°C, VCC = 4.75 V to 5.25 V)

| Parameter                                             | Symbol                         | Min. | Тур. | Max.   | Unit   | Reference   |

|-------------------------------------------------------|--------------------------------|------|------|--------|--------|-------------|

| Output Optical Power<br>50/125 μm, NA = 0.20 Fiber    | P <sub>OUT</sub>               | -10  |      | -4     | dBm av | ].          |

| Output Optical Power<br>62.5/125 µm, NA = 0.275 Fiber | P <sub>OUT</sub> -10 -4        |      | -4   | dBm av | ].     |             |

| Optical Extinction Ratio                              |                                | 9    |      |        | dB     | 1           |

| Center Wavelength                                     | $\lambda_{c}$                  | 830  | 850  | 860    | nm     |             |

| Spectral Width - rms                                  | σ                              |      |      | 0.85   | nm rms |             |

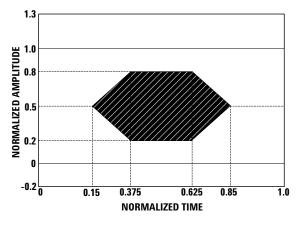

| Optical Rise / Fall Time                              | t <sub>r</sub> /t <sub>f</sub> |      |      | 0.45   | ns     | 2, 3 Fig. 1 |

| RIN <sub>12</sub>                                     |                                |      |      | -116   | dB/Hz  |             |

| Deterministic Transmitter Jitter                      |                                |      |      | 188    | ps     |             |

## **Receiver Electrical Characteristics**

$(TA = 0^{\circ}C \text{ to } +70^{\circ}C, VCC = 4.75 \text{ V to } 5.25 \text{ V})$

| Parameter                           | Symbol                            | Min.   | Тур. | Max.   | Unit | Reference |

|-------------------------------------|-----------------------------------|--------|------|--------|------|-----------|

| Supply Current                      |                                   |        | 105  | 130    | mA   | 2         |

| Power Dissipation                   | P <sub>DISR</sub>                 |        | 0.53 | 0.68   | W    | 2         |

| Data Output Voltage - Low           | $V_{\text{ol}}$ - $V_{\text{cc}}$ | -1.950 |      | -1.620 | V    | 3         |

| Data Output Voltage - High          | V <sub>oh</sub> - V <sub>cc</sub> | -1.045 |      | -0.740 | V    | 3         |

| Data Output Rise Time               | t,                                |        |      | 0.40   | ns   | 4         |

| Data Output Fall Time               | t <sub>f</sub>                    |        |      | 0.40   | ns   | 4         |

| Signal Detect Output Voltage - Low  | $V_{\text{ol}}$ - $V_{\text{cc}}$ | -1.950 |      | -1.620 | V    | 3         |

| Signal Detect Output Voltage - High | V <sub>oh</sub> - V <sub>cc</sub> | -1.045 |      | -0.740 | V    | 3         |

|                                     |                                   |        |      |        |      |           |

Notes:

The Laser Reset Voltage is the voltage level below which the VCCT voltage must be lowered to cause the laser driver circuit to reset from an electrical/optical shutdown condition to a proper electrical/optical operating condition. The maximum value corresponds to the worstcase highest VCC voltage necessary to cause a reset condition to occur. The laser safety shutdown circuit will operate properly with transmitter VCC levels of 3.5 V dc < VCC < 7.0 V dc.</li>

2. Receiver Supply Current and Power Dissipation do not include current and power in external 270 ohm terminating resistors.

3. These outputs are compatible with 10 K, 10 KH, and 100 K ECL and PECL inputs.

4. These are 20-80% values.

## AFBR-53D3 Family, 850 nm VCSEL

### **Transmitter Optical Characteristics**

(TA = 0°C to +70°C, VCC = 4.75 V to 5.25 V)

| Parameter                                             | Symbol                         | Min. | Тур. | Max. | Unit   | Reference   |

|-------------------------------------------------------|--------------------------------|------|------|------|--------|-------------|

| Output Optical Power<br>50/125 μm, NA = 0.20 Fiber    | P <sub>OUT</sub>               | -10  |      | -4   | dBm av | g.          |

| Output Optical Power<br>62.5/125 µm, NA = 0.275 Fiber | P <sub>OUT</sub>               | -10  |      | -4   | dBm av | g.          |

| Optical Extinction Ratio                              |                                | 9    |      |      | dB     | 1           |

| Center Wavelength                                     | $\lambda_{c}$                  | 830  | 850  | 860  | nm     |             |

| Spectral Width - rms                                  | σ                              |      |      | 0.85 | nm rms |             |

| Optical Rise / Fall Time                              | t <sub>r</sub> /t <sub>f</sub> |      |      | 0.45 | ns     | 2, 3 Fig. 1 |

| RIN <sub>12</sub>                                     |                                |      |      | -116 | dB/Hz  |             |

| Deterministic Transmitter Jitter                      |                                |      |      | 188  | ps     |             |

#### **Receiver Optical Characteristics**

$(TA = 0^{\circ}C \text{ to } +70^{\circ}C, VCC = 4.75 \text{ V to } 5.25 \text{ V})$

| Parameter                   | Symbol                          | Min. | Тур. | Max. | Unit    | Reference |

|-----------------------------|---------------------------------|------|------|------|---------|-----------|

| Input Optical Power         | P <sub>IN</sub>                 | -16  |      | 0    | dBm avg | . 4       |

| Operating Center Wavelength | $\lambda_{c}$                   | 770  |      | 860  | nm      |           |

| Return Loss                 |                                 | 12   |      |      | dB      | 5         |

| Signal Detect - Asserted    | P <sub>A</sub>                  |      |      | -18  | dBm avg |           |

| Signal Detect - Deasserted  | PD                              | -30  |      |      | dBm avg |           |

| Signal Detect - Hysteresis  | P <sub>A</sub> - P <sub>D</sub> | 1.5  |      |      | dB      |           |

Notes:

1. Optical Extinction Ratio is defined as the ratio of the average output optical power of the transmitter in the high ("1") state to the low ("0") state. This Optical Extinction Ratio is expressed in decibels (dB) by the relationship 10log(Phigh avg/Plow avg).

2. These are 20-80% values and include the effect of a fourth order filter.

3. Laser transmitter pulse response characteristics are specified by an eye diagram (Figure 1). The characteristics include rise time, fall time, pulse overshoot, pulse undershoot, and ringing, all of which are controlled to prevent excessive degradation of the receiver sensitivity.

4. The receive sensitivity is measured using a worst case extinction ratio penalty while sampling at the center of the eye.

5. Return loss is defined as the minimum attenuation (dB) of received optical power for energy reflected back into the optical fiber.

Figure 1. Transmitter Optical Eye Diagram Mask

# Table 1. Pinout Table

| <ul> <li>embedded in the nonconductive plastic housing and are not connected to the transceiver in circuit, nor is there a guaranteed connection to the metallized housing in the EZ and FZ ver They should be soldered into plated-through holes on the printed circuit board.</li> <li>V<sub>EER</sub> Receiver Signal Ground Directly connect this pin to receiver signal ground plane. (For AFBR-53D3, V<sub>EER</sub> = V<sub>EET</sub>)</li> <li>RD+ Receiver Data Out RD+ is an open-emitter output circuit. Terminate this high-speed differential PECL output wis standard PECL techniques at the follow-on device input pin.</li> <li>RD- Receiver Data Out Bar RD- is an open-emitter output circuit. Terminate this high-speed differential PECL output wis standard PECL techniques at the follow-on device input pin.</li> <li>SD Receiver Data Out Bar RD- is an open-emitter output circuit. Terminate this high-speed differential PECL output wis standard PECL techniques at the follow-on device input pin.</li> <li>SD Signal Detect Normal optical input levels to the receiver result in a logic "1" output, V<sub>OIH</sub>, asserted. Low in optical levels to the receiver result in a fault condition indicated by a logic "0" output V<sub>OII</sub>, deasserted. Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL teer via 50 Qt 0 V<sub>CCR</sub> - 2V. Alternatively, SD can be loaded with a 270Ω resistor to V<sub>EER</sub> to conse electrical power with small compromise to signal quality. If Signal Detect output is not user open-circuited. This Signal Detect output can be used to drive a PECL input on an upstream circuit, such a Detect input p Loss of Signal-bar.</li> <li>V<sub>CCR</sub> Receiver Power Supply Provide +5 Vdc via the recommended receiver power supply filter circuit. Locate the power supply filter circuit as close as possible to the V<sub>CCR</sub> pin.</li> <li>TD- Transmitter Power Supply Provide +5 Vdc via the recommended transmitter power supply filter circuit. Locate the power supply filter circuit as close as possible to the V<sub>CCR</sub> pin.</li></ul> | Pin Syml           | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Directly connect this pin to receiver signal ground plane. (For AFBR-53D3, V <sub>EER</sub> = V <sub>EET</sub> )           2         RD+         Receiver Data Out<br>RD+ is an open-emitter output circuit. Terminate this high-speed differential PECL output w<br>standard PECL techniques at the follow-on device input pin.           3         RD-         Receiver Data Out Bar<br>RD is an open-emitter output circuit. Terminate this high-speed differential PECL output wi<br>standard PECL techniques at the follow-on device input pin.           4         SD         Signal Detect<br>Normal optical input levels to the receiver result in a logic "1" output. V <sub>OH</sub> , asserted. Low ir<br>optical levels to the receiver result in a fault condition indicated by a logic "0" output V <sub>OH</sub> ,<br>deasserted.           Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL tecc<br>via 50 Ω to V <sub>CCR</sub> - 2V. Alternatively, SD can be loaded with a 270Ω resistor to V <sub>EER</sub> to conse<br>electrical power with small compromise to signal quality. If Signal Detect output is not use<br>open-circuited.           5         V <sub>CCR</sub> Receiver Power Supply<br>Provide +5 Vdc via the recommended receiver power supply filter circuit.<br>Locate the power supply           6         V <sub>CCT</sub> Transmitter Data In-Bar<br>Terminate this high-speed differential PECL input with standard PECL techniques at the trai<br>input pin.           8         TD+         Transmitter Data In<br>Terminate this high-speed differential PECL input with standard PECL techniques at the trai<br>input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Mounting F         | The mounting pins are provided for transceiver mechanical attachment to the circuit board. They a embedded in the nonconductive plastic housing and are not connected to the transceiver internal circuit, nor is there a guaranteed connection to the metallized housing in the EZ and FZ versions. They should be soldered into plated-through holes on the printed circuit board.                                                                                                                                                                                                                                                                                               |

| RD+ is an open-emitter output circuit. Terminate this high-speed differential PECL output we standard PECL techniques at the follow-on device input pin.         RD-       Receiver Data Out Bar         RD- is an open-emitter output circuit. Terminate this high-speed differential PECL output wi standard PECL techniques at the follow-on device input pin.         SD       Signal Detect         Normal optical input levels to the receiver result in a logic "1" output. V <sub>OH</sub> , asserted. Low in optical levels to the receiver result in a fault condition indicated by a logic "0" output V <sub>OH</sub> , deasserted.         Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL tecc via 50 Ω to V <sub>CCR</sub> - 2V. Alternatively, SD can be loaded with a 270Ω resistor to V <sub>EER</sub> to conse electrical power with small compromise to signal quality. If Signal Detect output is not user open-circuited.         This Signal Detect output can be used to drive a PECL input on an upstream circuit, such a Detect input pr Loss of Signal-bar.         V <sub>CCR</sub> Receiver Power Supply         Provide +5 Vdc via the recommended receiver power supply filter circuit.         Locate the power supply filter circuit as close as possible to the V <sub>CCR</sub> pin.         V <sub>CCT</sub> Transmitter Data In-Bar         Terminate this high-speed differential PECL input with standard PECL techniques at the trar input pin.         8       TD+         Transmitter Data In         Terminate this high-speed differential PECL input with standard PECL techniques at the trar input pin.         9 <td>1 V<sub>EER</sub></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 V <sub>EER</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <ul> <li>RD- is an open-emitter output circuit. Terminate this high-speed differential PECL output wirstandard PECL techniques at the follow-on device input pin.</li> <li>SD Signal Detect<br/>Normal optical input levels to the receiver result in a logic "1" output, V<sub>DH</sub>, asserted. Low in optical levels to the receiver result in a fault condition indicated by a logic "0" output V<sub>OH</sub>, deasserted.<br/>Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL tec via 50 Ω to V<sub>CCR</sub> - 2V. Alternatively, SD can be loaded with a 270Ω resistor to V<sub>EER</sub> to conse electrical power with small compromise to signal quality. If Signal Detect output is not user open-circuited.<br/>This Signal Detect output can be used to drive a PECL input on an upstream circuit, such a Detect input pr Loss of Signal-bar.</li> <li>V<sub>CCR</sub> Receiver Power Supply<br/>Provide +5 Vdc via the recommended receiver power supply filter circuit.<br/>Locate the power supply filter circuit as close as possible to the V<sub>CCR</sub> pin.</li> <li>TD- Transmitter Power Supply filter circuit as close as possible to the V<sub>CCT</sub> pin.</li> <li>TD- Transmitter Data In-Bar<br/>Terminate this high-speed differential PECL input with standard PECL techniques at the traninput pin.</li> <li>V<sub>EET</sub> Transmitter Signal Ground</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 RD+              | RD+ is an open-emitter output circuit. Terminate this high-speed differential PECL output with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Normal optical input levels to the receiver result in a logic "1" output, V<sub>OH</sub>, asserted. Low in optical levels to the receiver result in a fault condition indicated by a logic "0" output V<sub>OH</sub>, deasserted.</li> <li>Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL tec via 50 Ω to V<sub>CCR</sub> - 2V. Alternatively, SD can be loaded with a 270Ω resistor to V<sub>EER</sub> to conse electrical power with small compromise to signal quality. If Signal Detect output is not user open-circuited.</li> <li>This Signal Detect output can be used to drive a PECL input on an upstream circuit, such a Detect input pr Loss of Signal-bar.</li> <li>V<sub>CCR</sub></li> <li>Receiver Power Supply</li> <li>Provide +5 Vdc via the recommended receiver power supply filter circuit. Locate the power supply filter circuit as close as possible to the V<sub>CCR</sub> pin.</li> <li>V<sub>CCT</sub></li> <li>Transmitter Power Supply</li> <li>Provide +5 Vdc via the recommended transmitter power supply filter circuit. Locate the power supply filter circuit as close as possible to the V<sub>CCT</sub> pin.</li> <li>TD-</li> <li>Transmitter Data In-Bar Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>TD+</li> <li>Transmitter Data In</li> <li>Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>V<sub>EET</sub></li> <li>Transmitter Signal Ground</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3 RD-              | RD- is an open-emitter output circuit. Terminate this high-speed differential PECL output with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Provide +5 Vdc via the recommended receiver power supply filter circuit.<br/>Locate the power supply filter circuit as close as possible to the V<sub>CCR</sub> pin.</li> <li>V<sub>CCT</sub> Transmitter Power Supply<br/>Provide +5 Vdc via the recommended transmitter power supply filter circuit.<br/>Locate the power supply filter circuit as close as possible to the V<sub>CCT</sub> pin.</li> <li>TD- Transmitter Data In-Bar<br/>Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>TD+ Transmitter Data In<br/>Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>TD+ Transmitter Data In<br/>Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>TD+ Transmitter Data In<br/>Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.</li> <li>V<sub>EET</sub> Transmitter Signal Ground</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 SD               | Normal optical input levels to the receiver result in a logic "1" output, $V_{OH}$ , asserted. Low input optical levels to the receiver result in a fault condition indicated by a logic "0" output $V_{OH}$ , deasserted.<br>Signal Detect is a single-ended PECL output. SD can be terminated with standard PECL techniques via 50 $\Omega$ to $V_{CCR}$ - 2V. Alternatively, SD can be loaded with a 270 $\Omega$ resistor to $V_{EER}$ to conserve electrical power with small compromise to signal quality. If Signal Detect output is not used, leave open-circuited.<br>This Signal Detect output can be used to drive a PECL input on an upstream circuit, such as, Signal |

| Provide +5 Vdc via the recommended transmitter power supply filter circuit.<br>Locate the power supply filter circuit as close as possible to the V <sub>CCT</sub> pin.         7       TD-         Transmitter Data In-Bar<br>Terminate this high-speed differential PECL input with standard PECL techniques at the transmitter power pin.         8       TD+         Transmitter Data In<br>Terminate this high-speed differential PECL input with standard PECL techniques at the transmitter power pin.         9       V <sub>EET</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5 V <sub>CCR</sub> | Provide +5 Vdc via the recommended receiver power supply filter circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Terminate this high-speed differential PECL input with standard PECL techniques at the transing provide input pin.         8       TD+         Transmitter Data In Terminate this high-speed differential PECL input with standard PECL techniques at the transing provide input pin.         9       V <sub>EET</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6 V <sub>CCT</sub> | Provide +5 Vdc via the recommended transmitter power supply filter circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Terminate this high-speed differential PECL input with standard PECL techniques at the transinput pin.         9       V <sub>EET</sub> Transmitter Signal Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7 TD-              | Terminate this high-speed differential PECL input with standard PECL techniques at the transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8 TD+              | Terminate this high-speed differential PECL input with standard PECL techniques at the transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9 V <sub>eet</sub> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ○ 1 = V <sub>EER</sub> | 0         |

|------------------------|-----------|

| ○ 2 = RD+              | NIC<br>RX |

| ○ 3 = RD-              |           |

| ○ 4 = SD               |           |

| ○ 5 = V <sub>CCR</sub> |           |

| О 6 = V <sub>сст</sub> |           |

| ○ 7 = TD-              | ⇒ TX      |

| ○ 8 = TD+              |           |

| • 9 = V <sub>eet</sub> | 0         |

|                        | TOP VIEW  |

NIC = NO INTERNAL CONNECTION (MOUNTING PINS) Figure 2. Pin-Out

NOTES:

\*C8 IS AN OPTIONAL BYPASS CAPACITOR FOR ADDITIONAL LOW-FREQUENCY NOISE FILTERING. USE SURFACE-MOUNT COMPONENTS FOR OPTIMUM HIGH-FREQUENCY PERFORMANCE. USE 50 MICROSTRIP OR STRIPLINE FOR SIGNAL PATHS. LOCATE 50 TERMINATIONS AT THE INPUTS OF RECEIVING UNITS.

Figure 3. Recommended Gigabit/sec Ethernet AFBR-53D3 Fiber-Optic Transceiver and HDMP-1536A/1546A SERDES Integrated Circuit Transceiver Interface and Power Supply Filter Circuits.

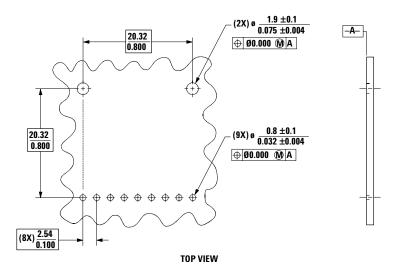

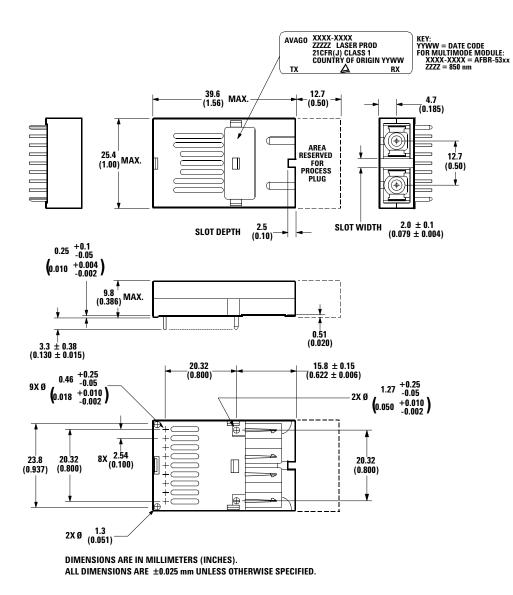

Figure 5. Package Outline Drawing for AFBR-53D3Z.

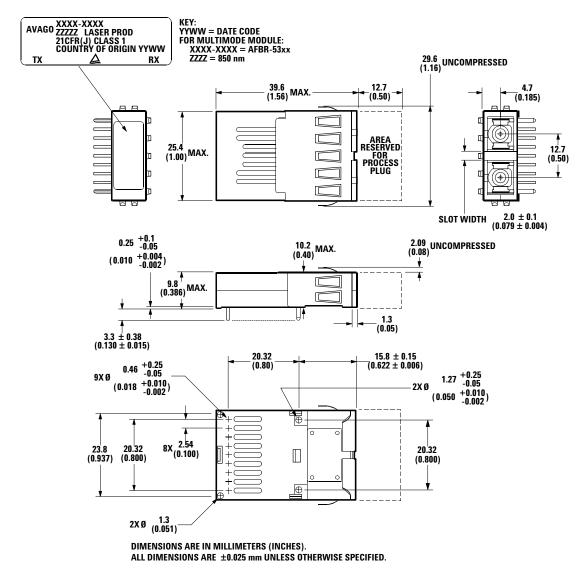

Figure 6. Package Outline for AFBR-53D3EZ.

PCB BOTTOM VIEW

Figure 7. Suggested Module Positioning and Panel Cut-out for AFBR-53D3EZ.

ALL DIMENSIONS ARE ± 0.025 mm UNLESS OTHERWISE SPECIFIED.

Figure 8. Package Outline for AFBR-53D3FZ.

Figure 9. Suggested Module Positioning and Panel Cut-out for AFBR-53D3FZ.

## **Ordering Information**

# 850 nm VCSEL (Short Wavelength Laser)

AFBR-53D3Z No shield, plastic housing. AFBR-53D3EZ Extended/protruding shield. AFBR-53D3FZ Flush shield.

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies, Limited in the United States and other countries. Data subject to change. Copyright © 2006 Avago Technologies Pte. All rights reserved. 5989-3292EN - September 13, 2006