# M0216SD-162SDAR2-1

# **Vacuum Fluorescent Display Module**

**RoHS Compliant**

Newhaven Display International, Inc.

2511 Technology Drive, Suite 101 Elgin IL, 60124 Ph: 847-844-8795 Fax: 847-844-8796

www.newhavendisplay.com nhtech@newhavendisplay.com nhsales@newhavendisplay.com

Downloaded from Elcodis.com electronic components distributor

#### 1.0 SCOPE

This specification applies to VFD module (Model NO: M0216SD-162SDAR2-1).

#### 2.0 FEATURES

\*Since a DC/DC converter is used, only +5Vdc power source is required to operate the module. \*5x8 dot matrix display, DC-DC/AC converter, and controller/driver circuitry.

\*High quality display and luminance.

\*ASCII and Japanese characters (CG-ROM font).

\*The module can be configured for a Motorola M68-type parallel interface, an Intel I80-type parallel interface, or synchronous serial ainterface.

| STANDARD |               | DOCUMENT NO. | REV. NO. | PAGE |

|----------|---------------|--------------|----------|------|

| NAME     | INTERNATIONAL |              | 03       | 2/24 |

# **3.0 SPECIFICATIONS**

#### **3.1 GENERAL SPECIFICATIONS**

| ITEM                               |             | VALUE                                 |

|------------------------------------|-------------|---------------------------------------|

| Number of characters (ch           | nar x line) | 16 x 2                                |

| Character configuration            |             | 5 x 8 dot matrix                      |

| Character height (mm)              |             | 5.34                                  |

| Character width (mm)               |             | 2.10                                  |

| Character pitch (mm)               |             | 3.30                                  |

| Line pitch (mm)                    |             | 6.16                                  |

| Width                              |             | 0.34                                  |

| Dot size (mm)                      | height      | 0.58                                  |

| Dot nitch (mm)                     | width       | 0.44                                  |

| Dot pitch (mm) height              |             | 0.68                                  |

| Peak wavelength of illumination    |             | Green (505 nm) $x = 0.235, y = 0.405$ |

| Luminance (cd/m <sup>2</sup> / fL) | min.        | 350 / 102                             |

| Lummance (cd/m / IL)               | typ.        | 500 / 146                             |

| STANDARD | NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE |

|----------|------------------|--------------|----------|------|

| NAME     | INTERNATIONAL    |              | 03       | 3/24 |

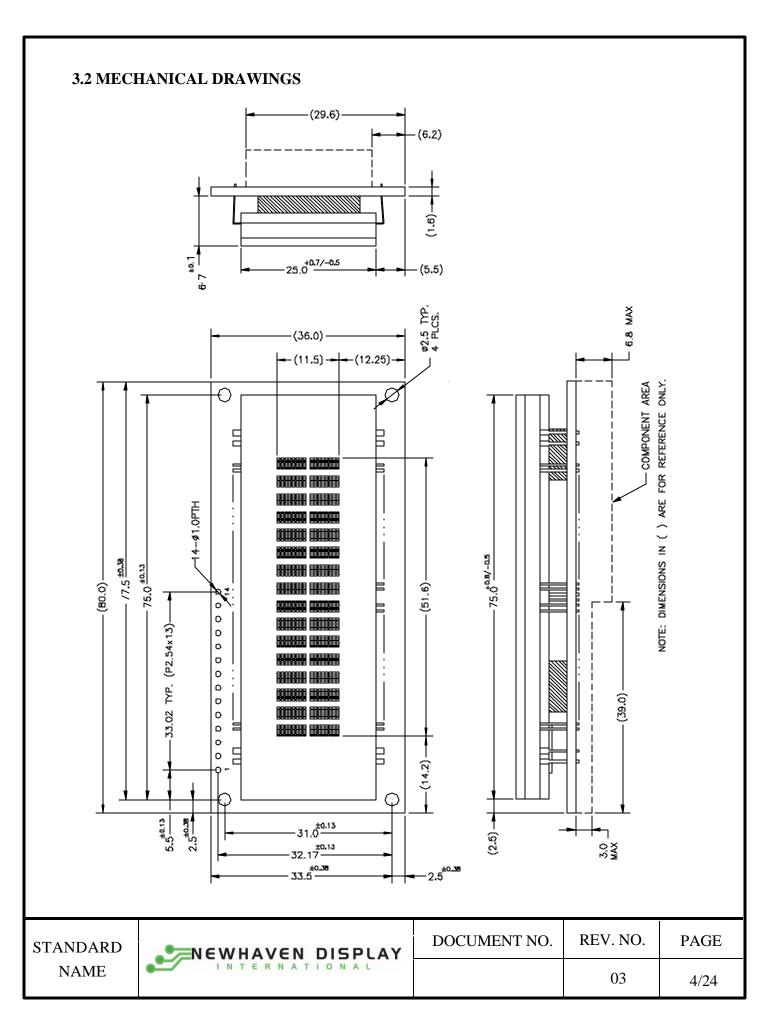

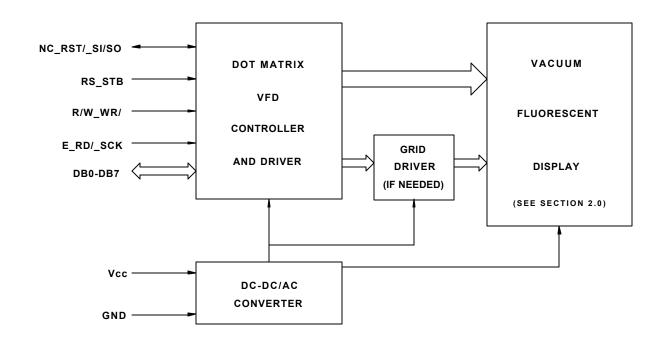

#### 3.3 SYSTEM BLOCK DIAGRAM

#### 3.4 ENVIRONMENTAL SPECIFICATIONS

| Item                  | Symbol | Min. | Max. | Unit | Comment                                                                                                           |

|-----------------------|--------|------|------|------|-------------------------------------------------------------------------------------------------------------------|

| Operating temperature | Topr   | -40  | +85  | °C   |                                                                                                                   |

| Storage temperature   | Tstg   | -50  | +95  | °C   |                                                                                                                   |

| Operating humidity    | Hopr   | 20   | 85   | %RH  | Without condensation                                                                                              |

| Storage humidity      | Hstg   | 20   | 90   | %RH  | Without condensation                                                                                              |

| Vibration             |        |      | 4    | G    | Total amplitude: 1.5mm<br>Freq: 10 - 55 Hz sine wave<br>Sweep time: 1 min./cycle<br>Duration: 2 hrs./axis (X,Y,Z) |

| Shock                 |        |      | 40   | G    | Duration: 11ms<br>Waveform: half sine wave<br>3 times/axis (X,Y,Z,-X,-Y,-Z)                                       |

#### 3.5 ABSOLUTE MAXIMUM SPECIFICATIONS

| Item                 | Symbol          | Min. | Max.                 | Unit |

|----------------------|-----------------|------|----------------------|------|

| Supply voltage       | V <sub>CC</sub> | -0.3 | 6.5                  | V    |

| Input signal voltage | $V_{IN}$        | -0.3 | V <sub>CC</sub> +0.3 | V    |

STANDARD NAME

| NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE |

|------------------|--------------|----------|------|

| INTERNATIONAL    |              | 03       | 5/24 |

#### 3.6 DC ELECTRICAL SPECIFICATIONS

| Item                                                                      | Symbol           | Min.                 | Тур. | Max.                | Unit |

|---------------------------------------------------------------------------|------------------|----------------------|------|---------------------|------|

| Supply voltage                                                            | V <sub>CC</sub>  | 4.5                  | 5.0  | 5.5                 | V    |

| Supply current                                                            | I <sub>CC</sub>  | _                    | 170  | 220                 | mA   |

| High-level input voltage (see Note)<br>(E,RD/,SCK,RST/)                   | V <sub>IH1</sub> | 0.8*V <sub>CC</sub>  | -    | V <sub>CC</sub>     | V    |

| Low-level input voltage (see Note)<br>(E,RD/,SCK,RST/)                    | $V_{IL1}$        | 0.0                  | -    | 0.2*V <sub>CC</sub> | V    |

| High-level input voltage (see Note)<br>(all inputs except E,RD/,SCK,RST/) | V <sub>IH2</sub> | 0.7*V <sub>CC</sub>  | -    | V <sub>CC</sub>     | V    |

| Low-level input voltage (see Note)<br>(all inputs except E,RD/,SCK,RST/)  | V <sub>IL2</sub> | 0.0                  | -    | 0.3*V <sub>CC</sub> | V    |

| High-level output voltage $(I_{OH} = -0.1 \text{mA})$                     | V <sub>OH</sub>  | V <sub>CC</sub> -0.5 | -    | -                   | V    |

| Low-level output voltage $(I_{OL} = 0.1 \text{mA})$                       | V <sub>OL</sub>  | -                    | -    | 0.5                 | V    |

| Input current (see Note)                                                  | II               | -500                 | -    | 1.0                 | uA   |

Note: A 10K ohm pull-up resistor is provided on each input for TTL compatibility.

# 3.7 AC ELECTRICAL SPECIFICATIONS

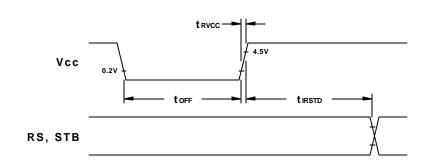

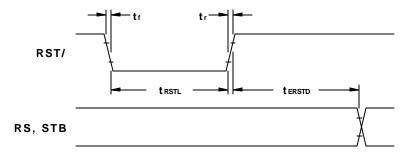

### 3.7.1 RESET TIMING

| (See Figures 1 and 2) |

|-----------------------|

|-----------------------|

| Item                            | Symbol             | Min. | Max. | Unit |

|---------------------------------|--------------------|------|------|------|

| V <sub>CC</sub> rise time       | t <sub>RVCC</sub>  | -    | 10   | ms   |

| V <sub>CC</sub> off time        | t <sub>OFF</sub>   | 1    | -    | ms   |

| Delay time after power-up reset | t <sub>IRSTD</sub> | 100  | -    | us   |

| Delay time after external reset | t <sub>ERSTD</sub> | 100  | -    | us   |

| RST/ pulse width low            | t <sub>RSTL</sub>  | 500  | -    | ns   |

| Input signal fall time          | t <sub>f</sub>     | -    | 15   | ns   |

| Input signal rise time          | t <sub>r</sub>     | -    | 15   | ns   |

Note: All timing is specified using 20% and 80% of  $V_{CC}$  as the reference points.

| STANDARD | NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE |

|----------|------------------|--------------|----------|------|

| NAME     | IN TERNATIONAL   |              | 03       | 6/24 |

Figure 1. Power-up Internal Reset Timing

Figure 2. External Reset Timing

#### 3.7.2 MOTOROLA M68-TYPE PARALLEL INTERFACE TIMING

| Item                   | Symbol            | Min. | Max. | Unit |

|------------------------|-------------------|------|------|------|

| RS, R/W setup time     | t <sub>AS</sub>   | 20   | -    | ns   |

| RS, R/W hold time      | t <sub>AH</sub>   | 10   | -    | ns   |

| Input signal rise time | t <sub>r</sub>    | -    | 15   | ns   |

| Input signal fall time | t <sub>f</sub>    | -    | 15   | ns   |

| E pulse width high     | $PW_{EH}$         | 230  | -    | ns   |

| E pulse width low      | $PW_{EL}$         | 230  | -    | ns   |

| Write data setup time  | t <sub>DS</sub>   | 80   | -    | ns   |

| Write data hold time   | t <sub>DH</sub>   | 10   | -    | ns   |

| E cycle time           | t <sub>CYCE</sub> | 500  | -    | ns   |

| Read data delay time   | t <sub>DD</sub>   | -    | 160  | ns   |

| Read data hold time    | t <sub>DHR</sub>  | 5    | -    | ns   |

PAGE

7/24

03

DOCUMENT NO. REV. NO. STANDARD WHAVEN DISPLAY E RNATIONAL e NAME

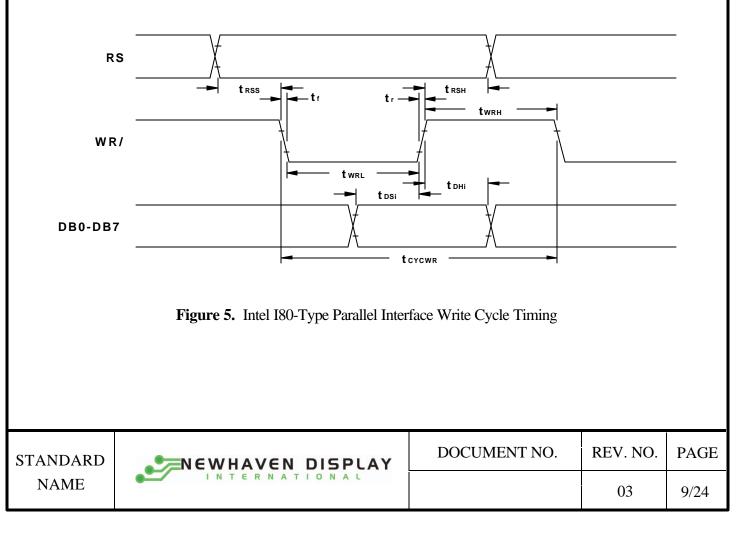

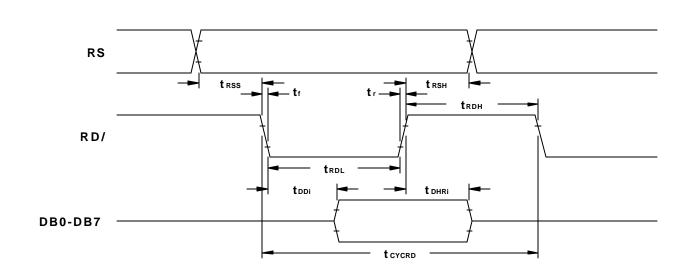

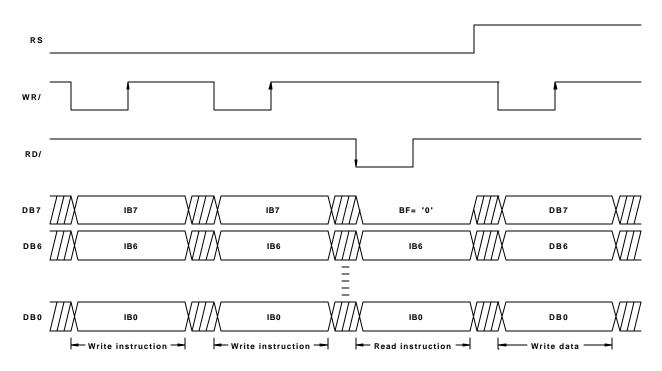

#### 3.7.3 INTEL 180-TYPE PARALLEL INTERFACE TIMING

| Item                   | Symbol             | Min. | Max. | Unit |

|------------------------|--------------------|------|------|------|

| RS setup time          | t <sub>RSS</sub>   | 10   | -    | ns   |

| RS hold time           | t <sub>RSH</sub>   | 10   | -    | ns   |

| Input signal fall time | t <sub>f</sub>     | -    | 15   | ns   |

| Input signal rise time | t <sub>r</sub>     | -    | 15   | ns   |

| WR/ pulse width low    | t <sub>WRL</sub>   | 30   | -    | ns   |

| WR/ pulse width high   | t <sub>WRH</sub>   | 100  | -    | ns   |

| Write data setup time  | t <sub>DSi</sub>   | 30   | -    | ns   |

| Write data hold time   | t <sub>DHi</sub>   | 10   | -    | ns   |

| WR/ cycle time         | t <sub>CYCWR</sub> | 166  | -    | ns   |

| RD/ cycle time         | t <sub>CYCRD</sub> | 166  | -    | ns   |

| RD/ pulse width low    | t <sub>RDL</sub>   | 70   | -    | ns   |

| RD/ pulse width high   | t <sub>RDH</sub>   | 70   | -    | ns   |

| Read data delay time   | t <sub>DDi</sub>   | -    | 70   | ns   |

| Read data hold time    | t <sub>DHRi</sub>  | 5    | 50   | ns   |

(See Figures 5 and 6)

Note: All timing is specified using 20% and 80% of  $V_{CC}$  as the reference points.

Figure 6. Intel I80-Type Parallel Interface Read Cycle Timing

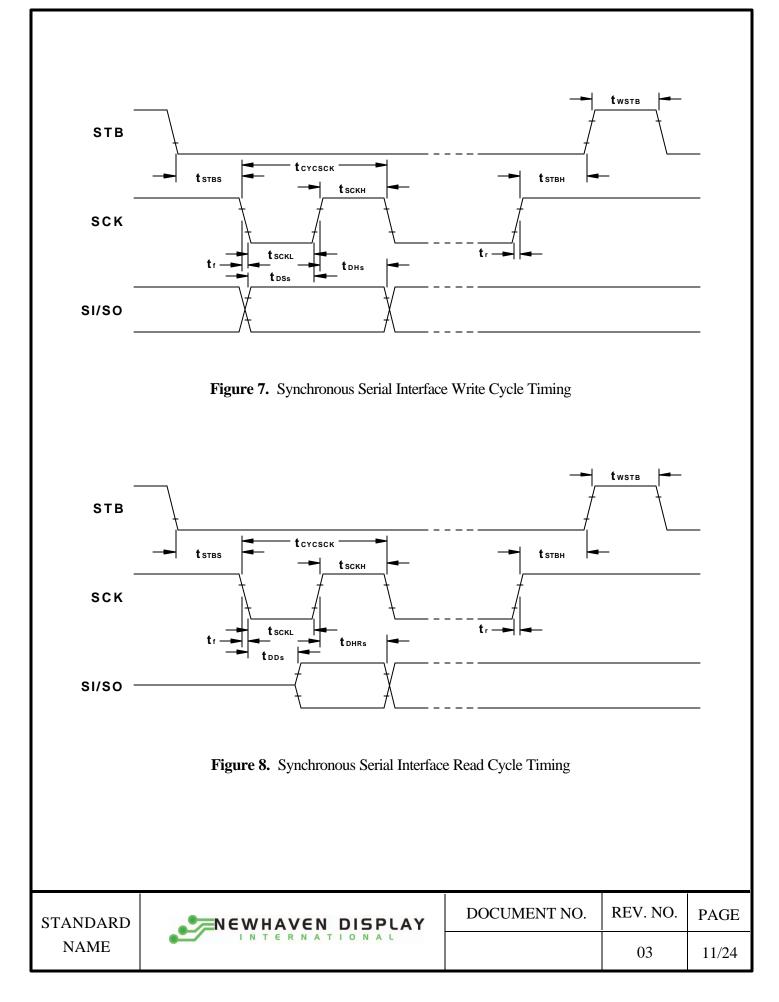

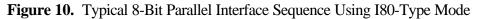

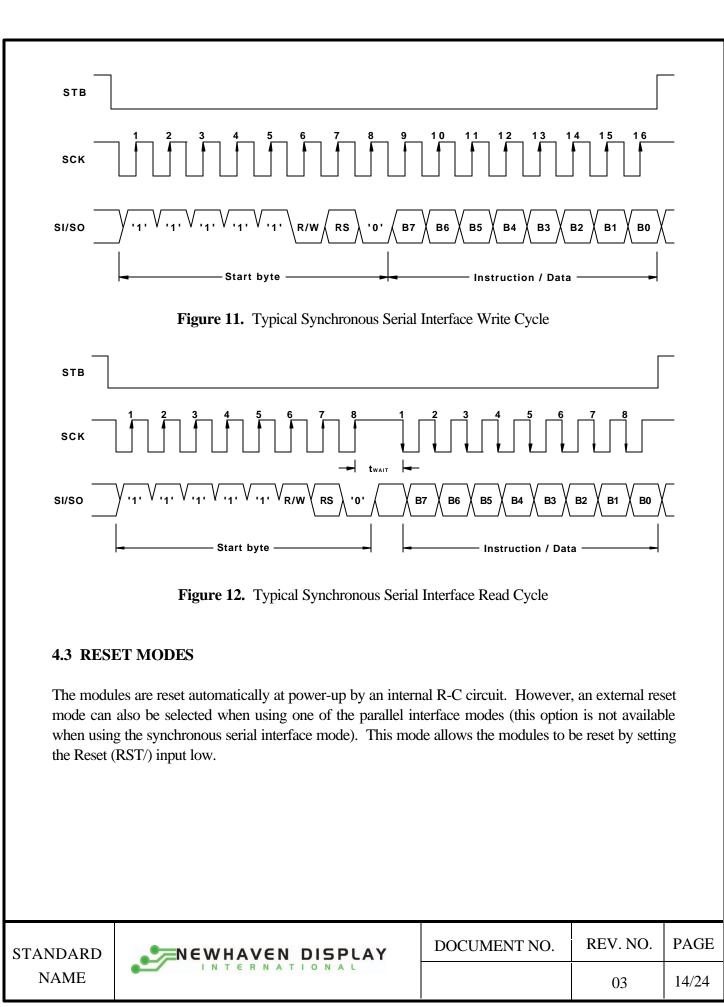

#### 3.7.4 SYNCHRONOUS SERIAL INTERFACE TIMING

| Item                        | Symbol              | Min. | Max. | Unit |

|-----------------------------|---------------------|------|------|------|

| STB setup time              | t <sub>STBS</sub>   | 100  | -    | ns   |

| STB hold time               | t <sub>STBH</sub>   | 500  | -    | ns   |

| Input signal fall time      | t <sub>f</sub>      | -    | 15   | ns   |

| Input signal rise time      | t <sub>r</sub>      | -    | 15   | ns   |

| STB pulse width high        | t <sub>wstb</sub>   | 500  | -    | ns   |

| SCK pulse width high        | t <sub>SCKH</sub>   | 200  | -    | ns   |

| SCK pulse width low         | t <sub>SCKL</sub>   | 200  | -    | ns   |

| SI data setup time          | t <sub>DSs</sub>    | 100  | -    | ns   |

| SI data hold time           | t <sub>DHs</sub>    | 100  | -    | ns   |

| SCK cycle time              | t <sub>CYCSCK</sub> | 500  | -    | ns   |

| SCK wait time between bytes | t <sub>WAIT</sub>   | 1    | -    | us   |

| SO data delay time          | t <sub>DDs</sub>    | _    | 150  | ns   |

| SO data hold time           | t <sub>DHRs</sub>   | 5    | _    | ns   |

(See Figures 7, 8 and 12)

Note: All timing is specified using 20% and 80% of  $V_{CC}$  as the reference points.

| STANDARD | NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|------------------|--------------|----------|-------|

| NAME     | INTERNATIONAL    |              | 03       | 10/24 |

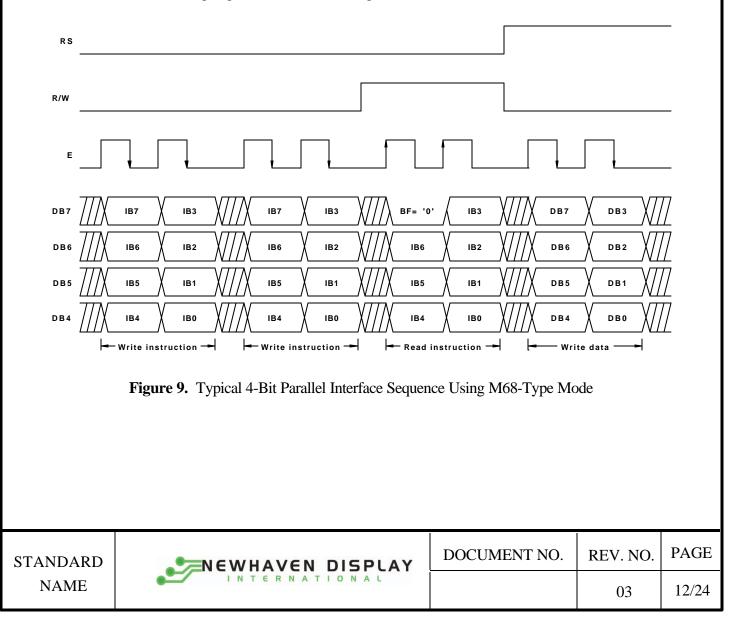

#### 4.0 MODES OF OPERATION

The following modes of operation are selectable via jumpers (see section 8.0 Jumper Settings).

#### 4.1 PARALLEL INTERFACE MODES

In the parallel interface mode, 8-bit instructions and data are sent between the host and the modules using either 4-bit nibbles or 8-bit bytes. Nibbles are transmitted high nibble first on DB4-DB7 (DB0-DB3 are ignored) whereas bytes are transmitted on DB0-DB7. The Register Select (RS) control signal is used to identify DB0-DB7 as an instruction (low) or data (high).

#### 4.1.1 MOTOROLA M68-TYPE MODE

This mode uses the Read/Write (R/W) and Enable (E) control signals to transfer information. Instructions/data are written to the modules on the falling edge of E when R/W is low and are read from the modules after the rising edge of E when R/W is high.

#### 4.1.2 INTEL I80-TYPE MODE

This mode uses the Read (RD/) and Write (WR/) control signals to transfer information. Instructions/data are written to the modules on the rising edge of WR/ and are read from the modules after the falling edge of RD/.

#### 4.2 SYNCHRONOUS SERIAL INTERFACE MODE

In the synchronous serial interface mode, instructions and data are sent between the host and the modules using 8-bit bytes. Two bytes are required per read/write cycle and are transmitted MSB first. The start byte contains 5 high bits, the Read/Write (R/W) control bit, the Register Select (RS) control bit, and a low bit. The following byte contains the instruction/data bits. The R/W bit determines whether the cycle is a read (high) or a write (low) cycle. The RS bit is used to identify the second byte as an instruction (low) or data (high).

This mode uses the Strobe (STB) control signal, Serial Clock (SCK) input, and Serial I/O (SI/SO) line to transfer information. In a write cycle, bits are clocked into the modules on the rising edge of SCK. In a read cycle, bits in the start byte are clocked into the modules on the rising edge of SCK. After the minimum wait time, each bit in the instruction/data byte can be read from the modules after each falling edge of SCK. Each read/write cycle begins on the falling edge of STB and ends on the rising edge. To be a valid read/write cycle, the STB must go high at the end of the cycle.

| STANDARD |                             | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|-----------------------------|--------------|----------|-------|

| NAME     | INTERNATIONAL INTERNATIONAL |              | 03       | 13/24 |

# 5.0 CHARACTER FONT TABLES

|          | UPPER                     |                  | 1             |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

|----------|---------------------------|------------------|---------------|---------------------------------------------------------------------------------------------|---------------------------|------|--------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------|--------------------------------------------------------------------|-----------------------------------------|----------|------------------|--------------------------|------|------|--------|-------|

|          | NIBBLE<br>LOWER<br>NIBBLE | 0000             | 0001          | 0010                                                                                        | 0011                      | 0100 | 0101               | 0110                                                                                             | 0111                                                               | 1000 | 1001                                                               | 1010                                    | 1011     | 1100             | 1101                     | 1110 | 1111 |        |       |

|          | 0000                      | CG<br>RAM<br>(1) | 2 2 2 2 2 2 2 |                                                                                             |                           |      |                    |                                                                                                  | 0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0                                 |      |                                                                    |                                         | 866 8 8  |                  | 888<br>888<br>888<br>888 |      |      |        |       |

|          | 0001                      | CG<br>RAM<br>(2) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      | 8 8 8<br>8 8<br>8 8<br>8 8<br>8 8<br>8 8<br>8 8<br>8 8<br>8 8<br>8 |                                         |          |                  |                          |      |      |        |       |

|          | 0010                      | CG<br>RAM<br>(3) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

|          | 0011                      | CG<br>RAM<br>(4) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

|          | 0100                      | CG<br>RAM<br>(5) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    | 8                                       |          |                  |                          |      |      |        |       |

|          | 0101                      | CG<br>RAM<br>(6) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    | 88                                      |          |                  |                          |      |      |        |       |

|          | 0110                      | CG<br>RAM<br>(7) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      | 2<br>000<br>0000<br>000<br>2                                       | 8 868 8<br>8 868 8<br>8 868 8<br>8<br>8 |          | 88 9<br>8639 9 8 |                          |      |      |        |       |

|          | 0111                      | CG<br>RAM<br>(8) |               | 80                                                                                          | 88888<br>8<br>8<br>8<br>8 |      |                    |                                                                                                  |                                                                    |      |                                                                    | 8 828 8<br>8<br>8<br>8                  |          |                  |                          |      |      |        |       |

|          | 1000                      | CG<br>RAM<br>(1) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

|          | 1001                      | CG<br>RAM<br>(2) |               |                                                                                             |                           |      |                    | 5<br>5<br>5<br>5<br>6<br>6<br>6<br>6<br>6<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |                                                                    |      | 0000<br>0<br>0000<br>0<br>0000<br>0                                |                                         |          |                  |                          |      |      |        |       |

|          | 1010                      | CG<br>RAM<br>(3) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    | 8 000 0<br>8<br>8 000 0                 |          |                  |                          |      |      |        |       |

|          | 1011                      | CG<br>RAM<br>(4) |               | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          | 88   |      |        |       |

|          | 1100                      | CG<br>RAM<br>(5) |               | 80                                                                                          |                           |      |                    |                                                                                                  |                                                                    | °    | 8<br>8<br>8<br>8<br>8<br>8                                         |                                         |          |                  | <b>5</b>                 |      |      |        |       |

|          | 1101                      | CG<br>RAM<br>(6) |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  | -                        |      | 8888 |        |       |

|          | 1110                      | CG<br>RAM<br>(7) |               |                                                                                             | 9<br>9<br>9<br>9          |      | • <sup>98</sup> •• |                                                                                                  | 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8 8                            |      |                                                                    | 2 033<br>5<br>8 035<br>8<br>8 035       |          |                  | 8 <sub>8</sub> 88        |      |      |        |       |

|          | 1111                      | CG<br>RAM<br>(8) |               | <br>                                                                                        |                           |      |                    |                                                                                                  | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

|          | <u> </u>                  | <u>  </u>        | <u> </u>      | <u> </u>                                                                                    |                           |      |                    |                                                                                                  | <u> </u>                                                           |      |                                                                    |                                         | <u> </u> |                  | <u> </u>                 |      |      |        |       |

| STANDARD |                           |                  |               | NC                                                                                          | 14/2                      |      |                    |                                                                                                  |                                                                    |      | V                                                                  | DO                                      | CUN      | MEN              | T N(                     | D.   | RE   | V. NO. | PAGE  |

| NAME     |                           | •                |               |                                                                                             | VV F                      | ER   |                    | тіо                                                                                              | N A                                                                |      | ¥ -                                                                |                                         |          |                  |                          |      |      | 03     | 15/24 |

|          |                           |                  |               |                                                                                             |                           |      |                    |                                                                                                  |                                                                    |      |                                                                    |                                         |          |                  |                          |      |      |        |       |

#### 6.0 FUNCTIONAL DESCRIPTION

#### 6.1 ADDRESS COUNTER (AC)

#### 6.1.1 SINGLE LINE DISPLAYS

The AC stores the address of the data being written to and read from DDRAM or CGRAM. The AC increments by 1 (overflows from 4FH to 00H) or decrements by 1 (underflows from 00H to 4FH) after each DDRAM access. The AC increments by 1 (overflows from 3FH to 00H) or decrements by 1 (underflows from 00H to 3FH) after each CGRAM access. When addressing DDRAM, the value in the AC also represents the cursor position.

#### 6.1.2 MULTIPLE LINE DISPLAYS

The AC stores the address of the data being written to and read from DDRAM or CGRAM. The AC increments by 1 (overflows from 27H to 40H and from 67H to 00H) or decrements by 1 (underflows from 40H to 27H and from 00H to 67H) after each DDRAM access. The AC increments by 1 (overflows from 3FH to 00H) or decrements by 1 (underflows from 00H to 3FH) after each CGRAM access. When addressing DDRAM, the value in the AC also represents the cursor position.

#### 6.2 DISPLAY DATA RAM (DDRAM)

#### 6.2.1 SINGLE LINE DISPLAYS

The DDRAM stores the character code of each character being displayed on the VFD. Valid DDRAM addresses are 00H to 4FH. DDRAM not being used for display characters can be used as general purpose RAM. The tables below show the relationship between the DDRAM address and the character position on the VFD before and after a display shift (with the number of display lines set to 1).

#### 6.2.2 MULTIPLE LINE DISPLAYS

The DDRAM stores the character code of each character being displayed on the VFD. Valid DDRAM addresses are 00H to 27H and 40H to 67H. DDRAM not being used for display characters can be used as general purpose RAM. The tables below show the relationship between the DDRAM address and the character position on the VFD before and after a display shift (with the number of display lines set to 2).

| STANDARD | NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|------------------|--------------|----------|-------|

| NAME     | INTERNATIONAL    |              | 03       | 16/24 |

# 6.3 DISPLAY SHIFT DETAIL

Relationship before a display shift (non-shifted):

|   |    |    | 3  |    | -  | -  |    | -  | -  | -  |    |    | -  |    | -  | -  |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 0F |

| 2 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |

Relationship after a display shift to the left:

|   |    | 2  | 0  |    | -  | -  | -  | -  | -  | 10 |    |    |    |    |    |    |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

|   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | 10 |

| 2 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 |

Relationship after a display shift to the right:

|   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 1 | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 80 | 09 | 0A | 0B | 0C | 0D | 0E |

| 2 | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E |

| STANDARD |               | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|---------------|--------------|----------|-------|

| NAME     | INTERNATIONAL |              | 03       | 17/24 |

#### 6.4 CHARACTER GENERATOR RAM (CGRAM)

The CGRAM stores the pixel information (1 = pixel on, 0 = pixel off) for the eight userdefinable 5x8 characters. Valid CGRAM addresses are 00H to 3FH. CGRAM not being used to define characters can be used as general purpose RAM (lower 5 bits only). Character codes 00H to 07H (or 08H to 0FH) are assigned to the user-definable characters (see section 5.0 Character Font Tables). The table below shows the relationship between the character codes, CGRAM addresses, and CGRAM data for each user-definable character.

| Chara      | cter code     | CGRAM address                                                                       | CGRAM data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |              |

|------------|---------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| D7 D6 D5 D | 4 D3 D2 D1 D0 | A5 A4 A3 A2 A1 A0                                                                   | D7 D6 D5 D4 D3 D2 D1 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| 0 0 0 0    |               | 0 0 0 0 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0<br>1 1 1        | X X X 1 1 1 1 1 1<br>0 0 0 0 1<br>0 0 0 1 0<br>0 1 0 0<br>0 1 0 0<br>1 0 0 0<br>1 0 0 0<br>1 1 1 1 1<br>0 0 0 0 0<br>1 1 1 1 1 1<br>0 0 0 0 0<br>1 1 0 0<br>1 0 0<br>1 1 1 1 1<br>1 1 1 1<br>1 1 1<br>1 1 1 1<br>1 1 1<br>1 1 1<br>1 1 1 1<br>1 1 1 1                                                                                                                                                                                                                                                                                                                      | CGRAM<br>(1) |

| 0 0 0 0    | 0 X 0 0 1     | 0 0 1 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 0 1<br>1 1 0<br>1 1 1 | X X X 1 1 1 1 1 1<br>1 0 0 0 0<br>1 0 0 0 0<br>1 1 1 1 0<br>1 0 0 0 0<br>1 1 1 1 0<br>1 0 0 0 0<br>1 1 1 1 1<br>0 0 0 0<br>1 0 0 0 0<br>1 1 1 1 1<br>0 0 0 0 0<br>1 1 1 1 1<br>0 0 0 0 0<br>1 0 0 0 0<br>1 1 1 1 1<br>0 0 0 0 0<br>1 0 0 0 0<br>0 0 0<br>1 0 0 0 0<br>1 0 0 0 0<br>0 0 0<br>0 0 0<br>0 0 0 0<br>0 0 0<br>0 0 0 0 | CGRAM<br>(2) |

| 0 0 0 0    |               | 1 1 1 0 0 0   0 0 1 0 1   0 1 1 1 0   1 1 0 1 1   1 1 0 1   1 1 1 0   1 1 1 1       | X X X 0 1 1 1 0<br>1 0 0 0 1<br>1 0 0 0 0<br>1 0 0 0 1<br>1 0 0 0 1<br>1 0 0 0 1<br>0 1 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CGRAM<br>(8) |

x = don't care

#### **6.5 INSTRUCTIONS**

| Instruction            | RS | R/W | DB7  | DB6             | DB5 | DB4 | DB3   | DB2   | DB1 | DB0 |

|------------------------|----|-----|------|-----------------|-----|-----|-------|-------|-----|-----|

| Clear display          | 0  | 0   | 0    | 0               | 0   | 0   | 0     | 0     | 0   | 1   |

| Cursor home            | 0  | 0   | 0    | 0               | 0   | 0   | 0     | 0     | 1   | x   |

| Entry mode set         | 0  | 0   | 0    | 0               | 0   | 0   | 0     | 1     | I/D | S   |

| Display on/off control | 0  | 0   | 0    | 0               | 0   | 0   | 1     | D     | С   | В   |

| Cursor/display shift   | 0  | 0   | 0    | 0               | 0   | 1   | S/C   | R/L   | Х   | X   |

| Function set           | 0  | 0   | 0    | 0               | 1   | DL  | Ν     | Х     | BR1 | BR0 |

| CGRAM address set      | 0  | 0   | 0    | 1 CGRAM address |     |     |       |       | SS  |     |

| DDRAM address set      | 0  | 0   | 1    |                 |     | DDR | AM ad | dress |     |     |

| Address counter read   | 0  | 1   | BF=0 |                 |     | AC  | conte | nts   |     |     |

| DDRAM or CGRAM write   | 1  | 0   |      | Write data      |     |     |       |       |     |     |

| DDRAM or CGRAM read    | 1  | 1   |      | Read data       |     |     |       |       |     |     |

x = don't care

| STANDARD NAME:   | DOCUMENT NO. | REV. NO. | PAGE  |

|------------------|--------------|----------|-------|

| NEWHAVEN DISPLAY |              | 03       | 18/24 |

#### 6.5.1 CLEAR DISPLAY

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

This instruction clears the display (without affecting the contents of CGRAM) by performing the following:

- 1) Fills all DDRAM locations with character code 20H (character code for a space).

- 2) Sets the AC to DDRAM address 00H (i.e. sets cursor position to 00H).

- 3) Returns the display to the non-shifted position.

- 4) Sets the I/D bit to 1.

#### 6.5.2 CURSOR HOME

| RS             | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Х   |

| x = don't care |     |     |     |     |     |     |     |     |     |

This instruction returns the cursor to the home position (without affecting the contents of DDRAM or CGRAM) by performing the following:

- 1) Sets the AC to DDRAM address 00H (i.e. sets cursor position to 00H).

- 2) Returns the display to the non-shifted position.

#### 6.5.3 ENTRY MODE SET

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |

This instruction selects whether the AC (cursor position) increments or decrements after each DDRAM or CGRAM access and determines the direction the information on the display shifts after each DDRAM write. The instruction also enables or disables display shifts after each DDRAM write (information on the display does not shift after a DDRAM read or CGRAM access). DDRAM, CGRAM, and AC contents are not affected by this instruction.

- I/D = 0: The AC decrements after each DDRAM or CGRAM access. If S = 1, the information on the display shifts to the right by one character position after each DDRAM write.

- I/D = 1: The AC increments after each DDRAM or CGRAM access. If S = 1, the information on the display shifts to the left by one character position after each DDRAM write.

- S = 0: The display shift function is disabled.

- S = 1: The display shift function is enabled.

| STANDARD |               | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|---------------|--------------|----------|-------|

| NAME     | INTERNATIONAL |              | 03       | 19/24 |

#### 6.5.4 DISPLAY ON/OFF CONTROL

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

This instruction selects whether the display and cursor are on or off and selects whether or not the character at the current cursor position blinks. DDRAM, CGRAM, and AC contents are not affected by this instruction.

- D = 0: The display is off (display blank).

- D = 1: The display is on (contents of DDRAM displayed).

- C = 0: The cursor is off.

- C = 1: The cursor is on (8<sup>th</sup> row of pixels).

- B = 0: The blinking character function is disabled.

- B = 1: The blinking character function is enabled (a character with all pixels on will alternate with the character displayed at the current cursor position at about a 1Hz rate with a 50% duty cycle).

#### 6.5.5 CURSOR/DISPLAY SHIFT

| RS                         | R/W      | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----------------------------|----------|-----|-----|-----|-----|-----|-----|-----|-----|

| 0                          | 0        | 0   | 0   | 0   | 1   | S/C | R/L | х   | x   |

| $\mathbf{x} = \mathbf{do}$ | n't care | •   |     |     |     |     |     |     |     |

This instruction increments or decrements the AC (cursor position) and shifts the information on the display one character position to the left or right without accessing DDRAM or CGRAM. DDRAM and CGRAM contents are not affected by this instruction. If the AC was addressing CGRAM prior to this instruction, the AC will be addressing DDRAM after this instruction. However, if the AC was addressing DDRAM prior to this instruction, the AC will still be addressing DDRAM after this instruction.

| S/C | R/L | AC contents (cursor position) | Information on the display                 |

|-----|-----|-------------------------------|--------------------------------------------|

| 0   | 0   | Decrements by one             | No change                                  |

| 0   | 1   | Increments by one             | No change                                  |

| 1   | 0   | Decrements by one             | Shifts one character position to the left  |

| 1   | 1   | Increments by one             | Shifts one character position to the right |

| STANDARD | NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|------------------|--------------|----------|-------|

| NAME     | INTERNATIONAL    |              | 03       | 20/24 |

#### 6.5.6 FUNCTION SET

|   | RS             | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |

|---|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|

| ſ | 0              | 0   | 0   | 0   | 1   | DL  | N   | Х   | BR1 | BR0 |  |

| 2 | x = don't care |     |     |     |     |     |     |     |     |     |  |

This instruction sets the width of the data bus for the parallel interface modes, the number of display lines, and the luminance level (brightness) of the VFD. It must be the first command sent after any reset. DDRAM, CGRAM, and AC contents are not affected by this instruction.

DL = 0: Sets the data bus width for the parallel interface modes to 4-bit (DB7-DB4).

DL = 1: Sets the data bus width for the parallel interface modes to 8-bit (DB7-DB0).

- N = 0: Sets the number of display lines to 1 (this setting is not recommended for multiple line displays).

- N = 1: Sets the number of display lines to 2 (this setting is not recommended for single line displays).

| BR1,BR0 = 0,0: | Sets the luminance level to 100%. |

|----------------|-----------------------------------|

| 0,1:           | Sets the luminance level to 75%.  |

| 1,0:           | Sets the luminance level to 50%.  |

1,1: Sets the luminance level to 25%.

#### 6.5.7 CGRAM ADDRESS SET

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3  | DB2      | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|------|----------|-----|-----|

| 0  | 0   | 0   | 1   |     | С   | GRAM | /I addre | SS  |     |

This instruction places the 6-bit CGRAM address specified by DB5-DB0 into the AC (cursor position). Subsequent data writes (reads) will be to (from) CGRAM. DDRAM and CGRAM contents are not affected by this instruction.

#### 6.5.8 DDRAM ADDRESS SET

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3   | DB2    | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-------|--------|-----|-----|

| 0  | 0   | 1   |     |     | DDR | AM ac | ldress |     |     |

This instruction places the 7-bit DDRAM address specified by DB6-DB0 into the AC (cursor position). Subsequent data writes (reads) will be to (from) DDRAM. DDRAM and CGRAM contents are not affected by this instruction.

STANDARD<br/>NAMENEWHAVEN DISPLAY<br/>DOCUMENT NO.DOCUMENT NO.REV. NO.PAGE0321/24

#### 6.5.9 ADDRESS COUNTER READ

| RS | R/W | DB7  | DB6 | DB5 | DB4 | DB3     | DB2  | DB1 | DB0 |

|----|-----|------|-----|-----|-----|---------|------|-----|-----|

| 0  | 1   | BF=0 |     |     | A   | C conte | ents |     |     |

This instruction reads the current 7-bit address from the AC on DB6-DB0 and the busy flag (BF) bit (always 0) on DB7. DDRAM, CGRAM, and AC contents are not affected by this instruction. Because the BF is always 0, the host never has to read the BF bit to determine if the modules are busy before sending data or instructions. Therefore, data and instructions can be sent to the modules continuously according to the E, WR/, and SCK cycle times specified in section 3.7 AC Timing Specifications. Due to this feature, the execution times for each instruction are not specified.

#### 6.5.10 DDRAM OR CGRAM WRITE

| RS | R/W | DB7 | DB6 | DB5 | DB4   | DB3    | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-------|--------|-----|-----|-----|

| 1  | 0   |     |     |     | Write | e data |     |     |     |

This instruction writes the 8-bit data byte on DB7-DB0 into the DDRAM or CGRAM location addressed by the AC. The most recent DDRAM or CGRAM Address Set instruction determines whether the write is to DDRAM or CGRAM. This instruction also increments or decrements the AC and shifts the display according to the I/D and S bits set by the Entry Mode Set instruction.

#### 6.5.11 DDRAM OR CGRAM READ

| RS | R/W | DB7 | DB6 | DB5 | DB4  | DB3    | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|------|--------|-----|-----|-----|

| 1  | 1   |     |     |     | Read | l data |     |     |     |

This instruction reads the 8-bit data byte from the DDRAM or CGRAM location addressed by the AC on DB7-DB0. The most recent DDRAM or CGRAM Address Set instruction determines whether the read is from DDRAM or CGRAM. This instruction also increments or decrements the AC and shifts the display according to the I/D and S bits set by the Entry Mode Set instruction. Before sending this instruction, a DDRAM or CGRAM Address Set instruction should be executed to set the AC to the desired DDRAM or CGRAM address to be read.

| STANDARD | NEWHAVEN DISPLAY            | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|-----------------------------|--------------|----------|-------|

| NAME     | INTERNATIONAL INTERNATIONAL |              | 03       | 22/24 |

#### 6.6 RESET CONDITIONS

After either a power-up reset or an external reset, the modules initialize to the following conditions:

- 1) All DDRAM locations are set to 20H (character code for a space).

- 2) The AC is set to DDRAM address 00H (i.e. sets cursor position to 00H).

- 3) The relationship between DDRAM addresses and character positions on the VFD is set to the nonshifted position.

- 4) Entry Mode Set instruction bits:

- I/D = 1: The AC increments after each DDRAM or CGRAM access.

- S = 0: The display shift function is disabled.

- 5) Display On/Off Control instruction bits:

- D = 0: The display is off (display blank).

- C = 0: The cursor is off.

- B = 0: The blinking character function is disabled.

- 6) Function Set instruction bits:

- DL = 1: Sets the data bus width for the parallel interface modes to 8-bit (DB7-DB0).

- N = 1(0): Number of display lines set to 2 for multiple line displays (number of display lines set to 1 for single line displays).

BR1, BR0 = 0,0: Sets the luminance level to 100%.

Note that the function set command must be the first instruction sent to the module after any reset.

#### 6.6.1 INITIALIZATION

The modules can be initialized by using instructions if the modules are not reset according to the reset timing detailed in Section 3.7.1 (Reset Timing). After any reset, the function set command must be the first instruction sent to the module.

| STANDARD |               | DOCUMENT NO. | REV. NO. | PAGE  |

|----------|---------------|--------------|----------|-------|

| NAME     | INTERNATIONAL |              | 03       | 23/24 |

# 7.0 CONNECTOR INTERFACE

| Pin | Comi e 1 | Paralle    | Parallel   | Pin | Paralle | Parallel |            |

|-----|----------|------------|------------|-----|---------|----------|------------|

| NO. | Serial   | (Intel)    | (Motorola) | NO. | Serial  | (Intel)  | (Motorola) |

| 1   | GND      | GND        | GND        | 2   | VCC     | VCC      | VCC        |

| 3   | SI/SO    | NC or RST/ | NC or RST/ | 4   | STB     | RS       | RS         |

| 5   | NC       | WR/        | R/W        | 6   | SCK     | RD/      | Е          |

| 7   | NC       | DB0        | DB0        | 8   | NC      | DB1      | DB1        |

| 9   | NC       | DB2        | DB2        | 10  | NC      | DB3      | DB3        |

| 11  | NC       | DB4        | DB4        | 12  | NC      | DB5      | DB5        |

| 13  | NC       | DB6        | DB6        | 14  | NC      | DB7      | DB7        |

# 8.0 Soldering Land Function

Some soldering lands are prepared on the tear side of PCB, to set operating mond of the Display module. A soldering iron is required to short soldering lands.

| -     |       |       |      |                       |                    |  |  |

|-------|-------|-------|------|-----------------------|--------------------|--|--|

| J6    | J7    | J2    | J3   | FUNCTION              |                    |  |  |

| 0pen  | Short | *     | 0pen | i80 type              | MPU type Selection |  |  |

| Short | 0pen  | *     | 0pen | M68 type              | MFU type Selection |  |  |

|       |       | 0pen  | 0pen | Pin #3: No connection | External Reset     |  |  |

|       |       | Short | 0pen | Pin #3: /RESET        | Section            |  |  |

1. parallel data transfer mode is selected

2. serial data or parallel data transfer mode set

| J5    | J3    | J2   | FUNCTION                    |  |  |  |

|-------|-------|------|-----------------------------|--|--|--|

| 0pen  | 0pen  |      | Parallel data Transfer mode |  |  |  |

| Short | Short | 0pen | Serial data Transfer mode   |  |  |  |

STANDARD NAME

| NEWHAVEN DISPLAY | DOCUMENT NO. | REV. NO. | PAGE  |

|------------------|--------------|----------|-------|

| INTERNATIONAL    |              | 03       | 24/24 |