# Noritake itron

# VACUUM FLUORESCENT DISPLAY MODULE SPECIFICATION

MODEL : CU24025ECPB-W1J

SPECIFICATION NO. : DS-627-0000-01

DATE OF ISSUE: Apr. 3, 1997

R E V I S I O N : Nov. 27, 1997

PUBLISHED BY ISE ELECTRONICS CORP./JAPAN

This specification is subject to change without prior notice.

# 1. General Description

# 1.1 Application:

Readout of computer, micro-computer, communication terminal and automated instruments.

# 1.2 Construction:

Single board display module consists of 48 characters(2 x 24) VFD, one chip controller driver which has character generator ROM and RAM, DC/DC converter.

# 1.3 Scope

Interface level is TTL-8/4 bit parallel and the module can be connected to the CPU bus directly. +5V single power supply is required.

# 2. Absolute Maximum Ratings

| Parameter            | Symbol | Min. | Typ. | Max. | Unit | Condition   |

|----------------------|--------|------|------|------|------|-------------|

| Power Supply Voltage | Vcc    | 0    |      | 5.5  | VDC  |             |

| Logic Input Voltage  | VI     | 0    |      | Vcc  | VDC  | <del></del> |

# 3. Electrical Ratings

Conditions:Ta=25°C

| Parameter           | Symbol | Min. | Тур. | Max. | Unit | Condition |            |

|---------------------|--------|------|------|------|------|-----------|------------|

| Logic Input Voltage | "H"    | ViH  | 2.0  | _    | Vcc  | VDC       | VCC = 5.0V |

| Logic input voltage | "L"    | VIL  | 0    |      | 0.8  | VDC       | VCC - 5.0V |

| Power supply Voltag | Vcc    | 4.75 | 5.00 | 5.25 | VDC  |           |            |

# 4. Electrical Characteristics

Conditions: Ta =25°C, VCC=5.0V

| Parameter            | Symbol | Min.          | Тур. | Мах. | Unit | Condition   |                |

|----------------------|--------|---------------|------|------|------|-------------|----------------|

| Logic Output Voltage | *H"    | H" VOH VCC-0. |      |      | _    | VDC         | IOH = -1.60mA  |

| Logic Output voltage | "["    | Vol           |      | _    | 0.4  | VIC         | IOL = 1.60  mA |

| Power Supply Currer  | ICC 1  | _             | 155  | 225  | mA   | Display ON  |                |

| Power Supply Curre   | ICC 2  |               | 2    | 10   | mA   | Display OFF |                |

Note: ICC1 shows the current, when all dots are turned on.

Slow-start power supply may cause a failure of Power-on reset which is explained in "8.2 Power-on reset". The power supply is recommended to be quick switch-type(quicker than 50ms).

ICC1 might be anticipated twice as usual at power on rush.

5. Optical Characteristics

Number of characters : 48 (2 lines x 24 chars)

Matrix format : 5 x 7 dot with underline

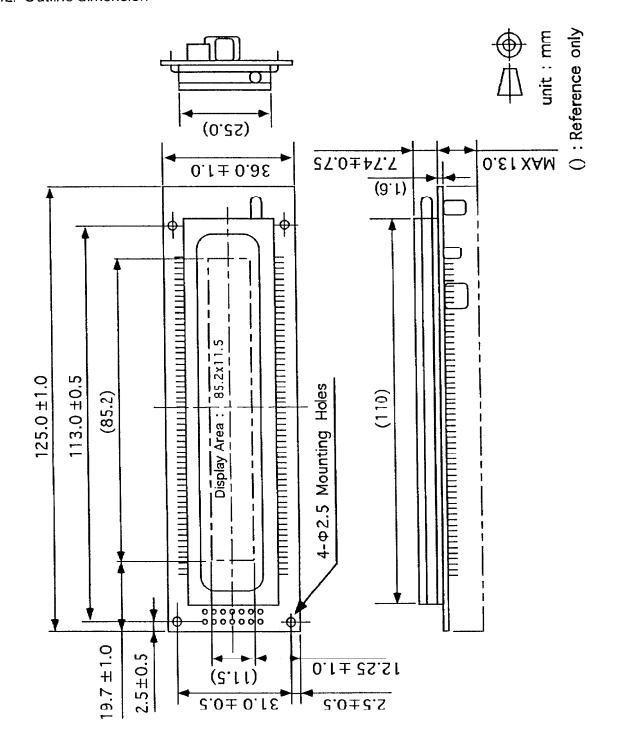

Display area : 85.2 x 11.5mm (X x Y)

Character size : 2.4 x 4.7 mm (X x Y) Underline is not included.

Character pitch : 3.6 mm Line pitch : 6.1 mm

Dot size : 0.4 x 0.5mm (X x Y)

Dot pitch : 0.5 x 0.7mm (X x Y)

Luminance : 350 cd/m<sup>2</sup> (100fL) Min.

Color of illumination : Blue-Green

#### 6. Environmental Conditions

Operating temperature : -40 to +85 ℃ Storage temperature : -40 to +85 ℃

Operating humidity : 20 to 80 % RH (Non condensation)

Vibration(Non operation): 10 to 55 to 10 Hz(Frequency),

1 mm(Total Amplitude) 30 Min.(Duration) X,Y,Z each direction

Shock (Non operation): 539 m/S<sup>2</sup>, 10mS

# 7. Functional Descriptions

# 7.1 Instruction table

| Instruction                  | 011 ( | <u> </u> |     |     | C   | ODE |     |     |     |     | Cycle              | Description                                                                                                                                      |

|------------------------------|-------|----------|-----|-----|-----|-----|-----|-----|-----|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                  | RS    | R/W      | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Time               | Description                                                                                                                                      |

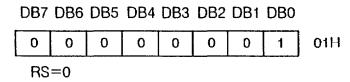

| Display<br>clear             | 0     | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 2.3 ms<br>Max.     | Clears all display<br>and sets DD RAM<br>address 0 in the<br>address counter.                                                                    |

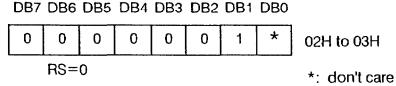

| Cursor<br>home               | 0     | 0        | 0   | 0   | 0   | 0   | 0   | 0   | 1   | *   | 1*tCYC             | Sets DD RAM address 0 in the address counter. Also returns the display being shifted to the original position. DD RAM contents remain unchanged. |

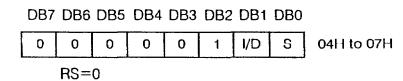

| Entry<br>mode set            | 0     | 0        | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   | 1±tCYC             | Sets the cursor direction and specifies display shift. These operations are performed during writing/reading data.                               |

| Display<br>ON/OFF<br>control | 1     | 0        | 0   | 0   | 0   | 0   | 1   | D   | С   | В   | 1*tCYC             | Sets all display ON/OFF(D), cursor ON/OFF(C), cursor blink of character position (B).                                                            |

| Cursor or display shift      | 0     | 0        | 0   | 0   | 0   | 1   | s/c | R/L | *   | *   | 1*tCYC<br>(2*tCYC) | Shifts displayed<br>cursor,<br>keeping DD RAM<br>contents.                                                                                       |

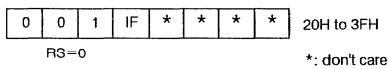

| Function set                 | 0     | 0        | 0   | 0   | 1   | IF  | *   | *   | *   | *   | 1*tCYC             | Sets data length (1F).                                                                                                                           |

| Bright-<br>ness<br>control   | 1     | 0        | *   | *   | *   | *   | *   | *   | BR1 | BR0 | 1*tCYC             | Accepts 1 byte data of just after "Function set" as brightness control data.                                                                     |

# CU24025ECPB-W1J

|                                           |                                      |                     |     |              | CC    | DDE         |     |     |                                  |                    |                                                                                                                                |

|-------------------------------------------|--------------------------------------|---------------------|-----|--------------|-------|-------------|-----|-----|----------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Instruction                               | RS                                   | R/W                 | DB7 | DB6          |       | <del></del> | DB3 | DB2 | DB1 DB0                          | Time               | Description                                                                                                                    |

| CG RAM<br>address<br>setting              | 0                                    | 0                   | 0   | 1            | 1 ACG |             |     |     | •                                | 1∗tCYC<br>(2∗tCYC) | Sets the CG<br>RAM address.                                                                                                    |

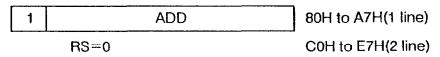

| DD RAM<br>address<br>setting              | 0                                    | 0                   | 1   | ADD          |       |             |     |     |                                  | 1xtCYC<br>(2xtCYC) | Sets the DD<br>RAM address.                                                                                                    |

| Busy flag<br>& address<br>reading         | 0                                    | 1                   | BF  | ACC          |       |             |     |     |                                  | 1+tCYC             | Reads BusyFlag<br>(BF) and<br>address counter.                                                                                 |

| Data<br>writing to<br>CG or DD<br>RAM     | 1                                    | 0                   |     | Data writing |       |             |     |     |                                  | 1+tCYC             | Writes data into<br>CG RAM<br>or DD RAM.                                                                                       |

| Data read-<br>ing from<br>CG or DD<br>RAM | 1                                    | 4                   |     | Data reading |       |             |     |     |                                  | 1+tCYC             | Reads data from<br>CG RAM<br>or DD RAM.                                                                                        |

|                                           | I/D<br>S<br>S/C<br>S/C<br>R/I<br>R/I | I/D = 1 : Increment |     |              |       |             |     |     | 0 : 4 bit<br>1 : Busy<br>0 : Not |                    | DD RAM: Display Data RAM CG RAM: Character Generator RAM ACG: CG RAM address ADD: DD RAM address corresponds to cursor address |

# Note:

\* : don't care

tCYC : tCYC is read/write cycle (Min1us) of HOST SYSTEM.

() : If RAM read is a next operation, needs execution time indicated by "()".

# 7.2 Display Clear

This instruction

- 1. Fills all locations in the display data (DD) RAM with 20H(Blank character).

- 2. Clears the contents of the address counter to 0H.

- Sets the display for zero character shift.

- 4. Sets the address counter to point to the DD RAM.

- 5. If the cursor is displayed, moves the cursor to the left most character in the top line (line 1).

- 6. Sets the address counter to increment on each access of DD RAM of CG RAM.

# 7.3 Cursor Home

This instruction

- 1. Clears the contents of the address counter to 011.

- 2. Sets the address counter to point to the DD RAM.

- 3. Sets the display for zero character shift.

- 4. If the cursor is displayed, moves the left most character in the top line (line 1).

# 7.4 Entry Mode Set

The I/D bit selects the way in which the contents of the address counter are modified after every access to DD RAM or CG RAM.

I/D=1: The address counter is incremented.

I/D=0: The address counter is decremented.

The S bit enables display shift, instead of cursor shift, after each write or read to the DD RAM.

S=1: Display shift enabled.

S=0: Cursor shift enabled.

The direction in which the display is shifted is opposite in sense to that of the cursor. For example if S=0 and I/D=1, the cursor would shift one character to the right after a CPU writes to DD RAM. However if S=1 and I/D=1, the display would

shift one character to the left and the cursor would maintain its position on the panel.

The cursor will already be shifted in the direction selected by I/D during reads of the DD RAM, irrespective of the value of S. Similarly reading and writing the CG RAM always shifts the cursor. Also both lines are shifted simultaneously.

# Cursor move and Display shift by the "Entry Mode Set"

| I/D | S | After writing DD RAM data                                            | After reading DD RAM data                    |

|-----|---|----------------------------------------------------------------------|----------------------------------------------|

| 0   | 0 | The cursor moves one character to the left.                          | The cursor moves one character to the left.  |

| 1   | O | The cursor moves one character to the right.                         | The cursor moves one character to the right. |

| 0   | 1 | The display shifts one character to the right without cursor's move. | The cursor moves one character to the left.  |

| 1   | 1 | The display shifts one character to the left without cursor's move.  | The cursor moves one character to the right. |

# 7.5 Display ON/OFF

| 0 | 0   | 0 | 0 | 1 | D | С | В | 08H to 0FH |

|---|-----|---|---|---|---|---|---|------------|

|   | RS= | 0 | - |   |   |   |   |            |

This instruction controls various features of the display.

The D bit turns the entire display on or off.

D=1: Display on D=0: Display off

Note: When display is turned off, power converter also inhibited and reduce a power consumption.

The C bit turns the cursor on or off.

C=1: Cursor on C=0: Cursor off

The B bit enables blinking of the character the cursor coincides with.

B=1: Blinking on B=0: Blinking off

Blinking is achieved by alternating between a normal and all on display of a character. The cursor blinks with a period of about 1.1 Hz and DUTY 50%.

# 7.6 Cursor/Display Shift

# DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

| O | U   | O | 1 | S/C | R/L | * | * | 10H to 1FH    |

|---|-----|---|---|-----|-----|---|---|---------------|

|   | RS= | 0 |   |     |     |   |   | *: don't care |

This instruction shifts the display and/or moves the cursor, on character to the left or right, regardless of DD RAM write/read.

The S/C bit selects movement of the cursor or movement of both the cursor and the display.

S/C=1: Shift both cursor and display

S/C=0: Shift cursor only

The R/L bit selects left ward or right ward movement of the display and/or cursor.

R/L=1: Shift one character right

R/L=0: Shift one character left

# Cursor move and Display shift by the "Cursor/Display Shift"

| S/C | R/L | Cursor shift                              | Display shift                    |

|-----|-----|-------------------------------------------|----------------------------------|

| 0   | 0   | Move one character to the left            | No shift                         |

| 0   | 1   | Move one character to the right           | No shift                         |

| 1   | 0   | Shift one character to left with display  | Shift one character to the left  |

| 1   | 1   | Shift one character to right with display | Shift one character to the right |

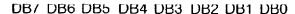

# 7.7 Function Set

This command sets width of data bus line by itself, and sets screen brightness by following one byte data.

# 7.7.1 Function Set Command

# DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

This instruction initializes the system, and must be the first instruction executed after power-on. The IF bit selects between an 8-bit or a 4-bit bus width interface.

IF=1: 8-bit CPU interface using DB7 to DB0 IF=0: 4-bit CPU interface using DB7 to DB4

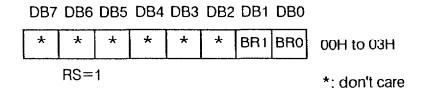

# 7.7.2 Brightness Control

One byte data ( RS=1 ) which follows the "Function Set Command" is considered as brightness data. When a command ( RS=0 ) is written after the "Function Set Command", the brightness control function is not initiated. Screen brightness is as follows:

| BR1 | BR0 | Brightness        |  |  |  |

|-----|-----|-------------------|--|--|--|

| 0   | 0   | 100 % ( Default ) |  |  |  |

| 0   | 1   | 75 %              |  |  |  |

| 1   | 0   | 50 %              |  |  |  |

| 1   | 1   | 25 %              |  |  |  |

#### 7.8 Set CG RAM Address

| 0 | 1   | ACG | 40H to 7ΓΙ1 |

|---|-----|-----|-------------|

|   | RS= | 0   |             |

# This instruction

- 1. Loads a new 6-bit address into the address counter.

- 2. Sets the address counter to address CG RAM.

Once "Set CG RAM Address" has been executed, the contents of the address counter will be automatically modified after every access of CG RAM, as determined by the "7.4 Entry Mode Set" instruction. The active width of the address counter, when it is addressing CG RAM, is 6-bit so the counter will wrap around to 00H from 3FH if more than 64 bytes of data are written to CG RAM.

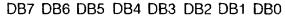

# 7.9 Set DD RAM Address

DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0

# This instruction

- 1. Loads a new 7-bit address into the address counter.

- 2. Sets the address counter to point to the DD RAM.

Once the "Set DD RAM Address" instruction has been executed, the contents of the

address counter will be automatically modified after each access of DD RAM, as selected by the "7.4 Entry Mode Set" instruction.

# Valid DDRAM Address Ranges

|          | Number of Characters | ADR        |  |  |

|----------|----------------------|------------|--|--|

| 1st line | 40                   | 00H to 27H |  |  |

| 2nd line | 40                   | 40H to 67H |  |  |

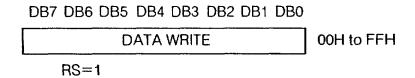

#### 7.10 Write Data

This instruction writes the data in DB7 to DB0 into either the CG RAM or the DD RAM. The RAM space (CG or DD), and the address in that space, that is accessed depends on whether a "Set CG RAM Address" or a "Set DD RAM Address" instruction was last executed, and on the parameters of that instruction. The contents of the address counter will be automatically modified after each "Write Data", as determined by the "7.4 Entry Mode Set". When data is written to the CG RAM, the DB7, DB6 and DB5 bits are not displayed as characters.

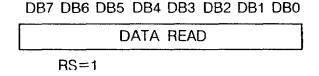

#### 7.11 Read Data

This instruction reads data from either CG RAM or DD RAM, depending on the type of "Set RAM Address" instructions last sent. The address in that space depends on the "Set RAM Address" instructions parameters. Immediately before executing "Read Data", "Set CG RAM Address" or "Set DD RAM Address" must be executed. The contents of the address counter are modified after each "Read Data". as determined by the "7.4 Entry Mode Set".

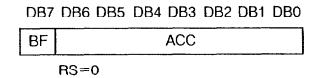

# 7.12 Read Busy Flag/Address Counter

Reading the instruction register yields the current value of the address counter and the busy flag. This instruction must be executed prior to any other instructions. ACC, the

address counter value, will point to a location in either CG RAM or DD RAM, depending on the type of "Set RAM Address" instruction last sent.

In "Busy Flag Check" immediately after executing "Write Data" instruction, a valid address counter value can be ready as soon as BF goes low. The BF bit shows the status of the busy flag.

BF = 1: The display module is busy.

BF = 0: The display module is ready for next instruction.

# 8 Other features

# 8.1 CG RAM

The display module has CG RAM of 320 bit =  $(5x8 \text{ bit /char}) \times 8$  chars which is for user definable character fonts. The character fonts consists of  $5 \times 7$  dots with underline. The number  $1 \sim 36$  corresponds to character fonts.

| Character code | CG RAM address |     |     |     |     |     |     | CG RAM data (character pattern) |     |     |     |     |     |     |

|----------------|----------------|-----|-----|-----|-----|-----|-----|---------------------------------|-----|-----|-----|-----|-----|-----|

|                | DB5            | DB4 | DB3 | DB2 | DB1 | DB0 | DB7 | DB6                             | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|                | 0              | 0   | 0   | 0   | 0   | 0   | *   | *                               | *   | 1   | 2   | 3   | 4   | 5   |

|                | 0              | 0   | 0   | 0   | 0   | 1   | *   | *                               | *   | 6   | 7   | 8   | 9   | 10  |

|                | 0              | 0   | 0   | 0   | 1   | 0   | *   | *                               | *   | 11  | 12  | 13  | 14  | 15  |

| 00H<br>or      | 0              | 0   | 0   | 0   | 1   | 1   | *   | *                               | *   | 16  | 17  | 18  | 19  | 20  |

| (08H)          | 0              | 0   | 0   | 1   | 0   | 0   | *   | *                               | *   | 21  | 22  | 23  | 24  | 25  |

|                | 0              | 0   | 0   | 1   | 0   | 1   | *   | *                               | *   | 26  | 27  | 28  | 29  | 30  |

|                | 0              | 0   | 0   | 1   | 1   | 0   | *   | *                               | *   | 31  | 32  | 33  | 34  | 35  |

|                | 0              | 0   | 0   | 1   | 1   | 1   | *   | *                               | *   | 36  | 0   | 0   | 0   | 0   |

|                | 0              | 0   | 1   | 0   | 0   | 0   | *   | *                               | *   | 1   | 2   | 3   | 4   | 5   |

|                | 0              | 0   | 1   | 0   | 0   | 1   | *   | *                               | *   | 6   | 7   | 8   | 9   | 10  |

|                | 0              | 0   | 1   | 0   | 1   | O   | *   | *                               | *   | 11  | 12  | 13  | 14  | 15  |

| 01H<br>or      | 0              | 0   | 1   | 0   | 1   | 1   | *   | *                               | *   | 16  | 17  | 18  | 19  | 20  |

| (09H)          | 0              | 0   | 1   | 1   | 0   | 0   | *   | *                               | *   | 21  | 22  | 23  | 24  | 25  |

|                | 0              | 0   | 1   | 1   | 0   | 1   | *   | *                               | *   | 26  | 27  | 28  | 29  | 30  |

|                | 0              | 0   | 1   | 1   | 1   | 0   | *   | *                               | *   | 31  | 32  | 33  | 34  | 35  |

|                | 0              | 0   | 1   | 1   | 1   | 1   | *   | *                               | *   | 36  | 0   | 0   | 0   | 0   |

REMARKS; "\*": Don't care "0": Turned off "1": Turned on.

Dot assignment

| 1  | 2  | 3  | 4  | 5  |  |  |  |

|----|----|----|----|----|--|--|--|

| 6  | 7  | 8  | 9  | 10 |  |  |  |

| 11 | 12 | 13 | 14 | 15 |  |  |  |

| 16 | 17 | 18 | 19 | 20 |  |  |  |

| 21 | 22 | 23 | 24 | 25 |  |  |  |

| 26 | 27 | 28 | 29 | 30 |  |  |  |

| 31 | 32 | 33 | 34 | 35 |  |  |  |

| 36 |    |    |    |    |  |  |  |

Dot 36 is an under line.

#### 8.2 Power-on reset

The module is initialized at power-on reset.

The status are as follows;

# 1. Display clear

Fills the DD RAM with 20Hex (Space code).

During executing of "Display Clear" (Max 2 3msec), the busy flag(BF) is "1".

# 2. Clears the address counter to 0H.

Sets the address counter to point the DD RAM.

# 3. Display ON/OFF

D=0: Display OFF

C=0: Cursor OFF

B=0: Blink OFF

# 4. Entry Mode Set

I/D = 1: Increment(+1)

S=0: No display shift

# 5. Function Set

IF=1: 8-bit interface

# 6. Brightness Control

BR0=BR1=0:100%

#### Remarks

There is a possibility that reset doesn't work by slow-start power supply.

Therefore the initializing by commands is needed.

# 8.3 CPU interface

The display module is capable to communicate some different type of bus systems such as i80 or M68,8-bit or 4-bit data.

#### 8.3.1 Select CPU

The module is able to connected to bus of i80 type or M68 type CPU, by setting jumper.

#### 8.3.2 4-Bit CPU interface

If 4-bit interface is used, the 8-bit instruction are written nibble by nibble: the high-order nibble being written first, followed by low-order nibble. It is not necessary to check the busy flag between writing separate nibbles of individual instructions.

See "7.7.1 Function Set Command" for more information.

#### 8.4 Test Mode

Self test functions built into the display module. The test mode is initiated by connecting 2 and 3 pin of 3pin connector(CN2) and power up.

In the test mode checker patterns are displayed on all character position.

In the future, there is a possibility to remove a 3 pin connector (CN2).

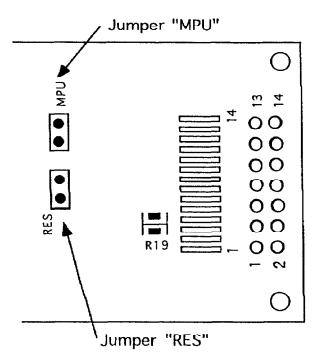

# 8.5 Jumper

Some jumper are prepared on the PCB board, to set operating mode of the display module. A soldering iron is required to short jumper.

The jumper "RES" is used to reset the display module. You can reset the module by shorting the jumper "RES" for some interval which is longer than 10us.

The following figure shows the location of each jumper.

#### Location

The following table shows the function of jumper "MPU".

| MPU   | CPU bus mode | Control signals |

|-------|--------------|-----------------|

| open  | M68 type     | E,R/ W          |

| short | i80 type     | RD,WR           |

When "R19" is short, the third hole of 14 through holes is for reset input. Reset input signal is active when it is low.

The following table shows the function of "R19".

| R19   | third hole of 14 through holes |

|-------|--------------------------------|

| open  | No connection                  |

| short | RESET                          |

The jumper resister "R19" is open at factory.

| %%+0<br>0000 | D 7<br>D 6<br>D 5<br>D 4 | 00000 | 0<br>0<br>0<br>1<br>1                        | 0<br>0<br>1<br>0<br>2                      | 0<br>0<br>1<br>1<br>3 | 0<br>1<br>0<br>0<br>4 | 0<br>1<br>0<br>1<br>5 | 1<br>1<br>0 | 1         | 0            | 1           | 1     | 1       | 0            | 1    | 0     | 1<br>1<br>F |

|--------------|--------------------------|-------|----------------------------------------------|--------------------------------------------|-----------------------|-----------------------|-----------------------|-------------|-----------|--------------|-------------|-------|---------|--------------|------|-------|-------------|

| 0000         | 0                        |       |                                              |                                            |                       | :::                   | :                     | ••          | <b></b> . | : <u>:</u>   |             |       |         | :::          |      | ::::  | ::::        |

| 0001         | 1                        |       | ::                                           | :                                          | ::                    |                       | ::::                  | .:::        | •::::     | ::::         | ::::        | :::   | ::      | ::::         | ·:   | :::   |             |

| 0010         | 2                        |       |                                              | ::                                         | ::::                  |                       |                       | ::          | :         | :::          |             | :"    | :       | •••          | .::  | ::::: |             |

| 0011         | 3                        |       | 6000<br>6000<br>6000<br>6000<br>6000<br>6000 |                                            | :::                   | <b>:</b>              | ::                    | :::         | ·         | .::<br>::::i |             | :     | :::     | .:.          | :::: | ::    | :::         |

| 0100         | 4                        |       | *****                                        | ::::                                       | :::                   | :::                   |                       | :::         |           | :::          |             | ٠.    |         | :.           | :::  | :::   | :::         |

| 0101         | 5                        |       |                                              | :: .:<br>: ::::::::::::::::::::::::::::::: | ::                    | <b></b>               | ii                    | ::::        | 1!        |              | ::::        | ::    | ::      | <b>!</b>     | .::  | ::::  |             |

| 0110         | 6                        |       |                                              | ::::                                       | ::                    |                       | 1                     | #"          | ii        | ::           | -::-        |       |         |              |      | ::    | ::          |

| 0111         | 7                        |       |                                              | :                                          | :                     |                       | 1::                   | ::::        | 11        | :::::        | ::-         | ·;;:  | ::::::: | ;:: <b>:</b> |      | ::::  | :::         |

| 1000         | 8                        |       |                                              | 1.                                         | ::::                  |                       | ;;<br>;::;            | !··:        | :::.      | ::::         | :           | .:    | :::     |              | 1.1  | .;;"  | :::         |

| 1001         | 9                        |       |                                              | :                                          | :::                   | I.                    | 1: ;:                 | :           | ::::      | ::::         | :           | :::;; | •       |              | 11.  | :     | :;          |

| 1010         | Α                        |       | ::::                                         | 1.:.                                       | ::                    |                       |                       | :           |           |              | :::         |       |         | :            | i·   | :     | :           |

| 1011         | В                        |       | :::::                                        |                                            | ::                    | i::                   | :                     | 1::         | :         | : . :        | ::          | :::   | ::      |              |      | ::    | ::-:        |

| 1100         | С                        |       |                                              | :                                          | ::                    |                       | ١                     | 1           |           | 1            | :-          | :::   | :::     | ;            | :::: | :::.  |             |

| 1101         | D                        |       | #                                            |                                            |                       |                       |                       | :::         | ::        | :            |             |       |         | <i>.</i> :   |      | ::    |             |

| 1110         | Ε                        |       | -:                                           | ::                                         |                       |                       |                       | +           | 1.        | 1            | 1.          | :::!  |         |              |      |       |             |

| 1111         | F                        |       | .::                                          |                                            |                       | +                     | +                     |             | :         | ::::         | <del></del> |       | 1       |              | :::  | ::::  | 11111       |

Character Table 0 [ CG57103 ]

Note: Font number 00~07Hex (08~0FHex) is UDF.

# 10. Timing

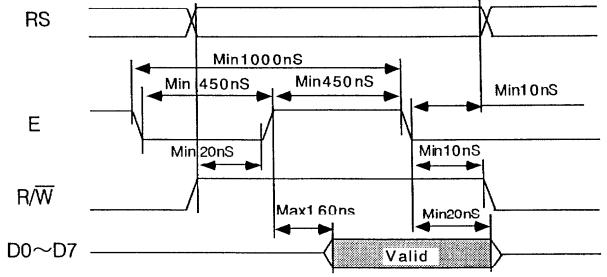

# 10.1 CPU bus write timing (i80 type) RS Min5nS Min5nS Min1000nS Min450nS Min450nS WR Min10nS Min195nS D0~D7 Valid 10.2 CPU bus read timing (i80 type) RS Min5nS Min 5nS Min1000nS Min450nS Min450nS $\overline{RD}$ Min20nS Max 160nS $D0\sim D7$ Valid 10.3 CPU bus write timing (M68 type) RS Min1000nS Min 450nS Min 450nS Min10nS E Min20nS Min10nS R/₩ Min195nS Min10nS

Valid

$D0\sim D7$

# 10.4 CPU bus read timing (M68 type)

# 11. Connector Pin assignment

# 11.1 14pin Connector

Fourteen (14) through holes are prepared for power supply and data communications. A connector or pins may be able to soldered to the holes.

| No. | Terminal   | No. | Terminal |

|-----|------------|-----|----------|

| 1   | GND        | 8   | DB1      |

| 2   | Vcc        | 9   | DB2      |

| 3   | <b>※NC</b> | 10  | DB3      |

| 4   | RS         | 11  | DB4      |

| 5   | R/W (WR)   | 12  | DB5      |

| 6   | E (RD)     | 13  | DB6      |

| 7   | DB0        | 14  | DB7      |

NC: no connection

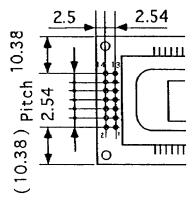

※ The third through hole is for reset input when "R19" is short. Location and dimensions ( Diameter of holes is 1.0mm.)

UNIT: mm

# 11.2 3pin Connector

A three (3) pin connector (CN2) on the board is factory use only, and may be removed in future.

# 12. Outline dimension

#### IMPORTANT PRECAUTIONS

- \* All VFD Modules contain MOS LSI. Anti-Static handling procedures are always required.

Tools required for assembly, such as soldering irons, must be properly grounded.

- \* VF Display consists of Soda-lime glass. Heavy shock more than 100G, thermal shock greater than 10°C/minute, direct hit with hard material to the glass surface --especially to the EXHAUST PIPE -- may CRACK the glass.

- \* Do not PUSH the display strongly. At mounting to the system frame, slight gap between display glass face and front panel is necessary to avoid a contact failure of lead pins of display. Twist or warp mounting will make a glass CRACK around the lead pin of display.

- \* Neither DATA CONNECTOR or POWER CONNECTOR should be connected or disconnected while power is applied. As is often the case with most subsystems, caution should be exercised in selectively disconnecting power within a computer based system. The modules receive high logic on strobe lines as random signals on all data ports. Removal of primary power with logic signals applied may damage input circuitry.

- \* Stress more than specification listed under the Absolute Maximum Ratings may cause PERMANENT DAMAGE of the modules.

- \* +5 volts power line must be regulated completely since all control logics depend on this line. Do not apply slow-start power. Provide sufficient output current power source to avoid trouble of RUSH CURRENT at power on. (At least output current of double figure of Icc, listed on the specification of each module, is required.)

- \* Data cable length between module and host system is recommended within 300 mm to be free from a miss-operation caused by noise.

- \* Do not place the module on the conductive plate just after the power off Due to big capacitors on the module, more than 1 min. of discharging time is required to avoid the failure caused by shorting of power line.

- \* 2 hours pre-running with the test mode operation may help the stability of the brightness of the VFD when power was not applied more than 2 months.

- \* Steady repeating of a fixed (static) message displaying, longer than 5 hours in a day may cause the phosphor burn-out problem.