**TENTATIVE**

#### TOSHIBA SMALL FORM FACTOR CARD

**TENTATIVE**

CompactFlash TM Card

Lead-Free

### **DESCRIPTION**

The THNCFxxxxDG series CompactFlash™ card is a flash technology based on ATA interface flash memory card. It is constructed with flash disk controller chip and NAND-type flash memory device. The CompactFlash™ card operates in both 5-Volt and 3.3-Volt power supplies. It comes in capacity of 128, 256, 512MB and 1GB unformatted for type-I card. Emulating IDE hard disk drives and being certified in accordance with the CompactFlash™ Certification Plan it is a perfect choice of solid-state mass-storage cards for battery backup handheld devices such as Digital Camera, Audio Player, PDA, or industrial application, or the applications that require high environment tolerance with high performance sustained write speed.

### **FEATURES**

- CompactFlash<sup>TM</sup> Compatibility

- 3.3V or 5.0V single power supply.

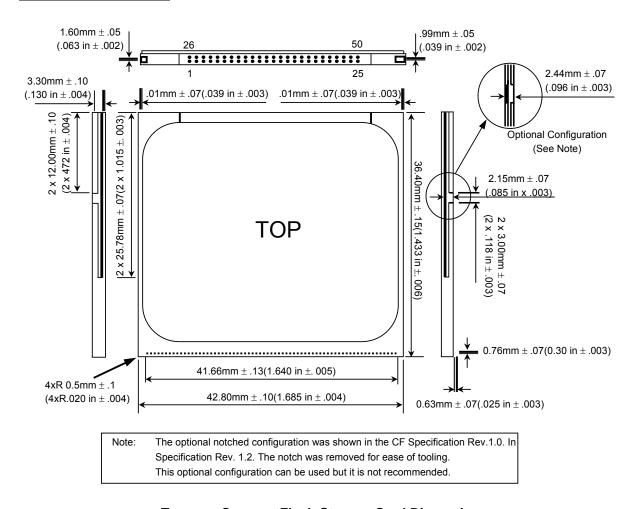

- 50 pin two piece connector with Type-I form factor (3.3mm Thick)

- Support for CIS implemented with 256 bytes of attribute memory

- Interface modes

- PC card memory mode

- PC card I/O mode

- True IDE mode

- High performance

- Interface Transfer speed at PIO mode 4 cycle timing, 16.6 Mbytes/second theoretically

- Sustained write: max 6.0 Mbytes/s in ATA PIO mode 4 cycle timing

- Sustained read: max 6.5 Mbytes/s in ATA PIO mode 4 cycle timing

- Single +5 V or 3.3 V power supply and automatic power management.

Notes: CompactFlash<sup>™</sup> is a trademark of SanDisk Corporation and is licensed royalty-free to the CFA, which in turn will license it royal-free to CFA members.

CFA: CompactFlash<sup>TM</sup> Association.

## **Products Specifications**

#### Line-up:

| Card Density | Model No.   | Cylinder | Head | Sector | Memory capacity *1 |

|--------------|-------------|----------|------|--------|--------------------|

| 128MB        | THNCF128MDG | 978      | 8    | 32     | 128,188,416 Byte   |

| 256MB        | THNCF256MDG | 978      | 16   | 32     | 256,376,832 Byte   |

| 512MB        | THNCF512MDG | 993      | 16   | 63     | 512,483,328 Byte   |

| 1.02GB       | THNCF1G02DG | 1985     | 16   | 63     | 1024,450,560 Byte  |

<sup>\*1:</sup> It is the logical address capacity including the area used for File System.

· Dimensions:

Type I card: 36.4mm(L) x 42.8mm (W) x 3.3mm (H)

• Storage Capacities:

128MB, 256MB, 512MB and 1.02GB (unformatted)

Operating Voltage:

$\begin{array}{c} 3.3V\pm5\%\\ 5.0V\pm0.5V \end{array}$

- Power consumption:

- 5V operation

Active mode:

$\begin{array}{cccc} Write \ operation & : & 28mA & (Typ.) \\ Read \ operation & : & 23mA & (Typ.) \\ Power \ down \ mode & : & 750 \mu A & (Typ.) \end{array}$

• 3.3V operation

Active mode:

$\begin{tabular}{lll} Write operation & : & 25mA & (Typ.) \\ Read operation & : & 21mA & (Typ.) \\ Power down mode & : & 380 \mu A & (Typ.) \\ \end{tabular}$

Environment conditions:

• Operating temperature:  $0^{\circ}C \sim 70^{\circ}C$ • Storage temperature:  $-20^{\circ}C \sim 85^{\circ}C$

• Storage humidity: 95% (max) (No condensation)

# **Electrical Interface**

### · Physical Description:

The host is connected to the CompactFlash™ Storage Card using a standard 50-pin connector. The connector in the host consists of two rows of 25 male contacts each on 50 mil (1.27 mm) centers.

#### Pin Assignments and Pin Type:

The signal/pin assignments are listed in the section "Pin Assignment and Pin Type". Low active signals have a "—" prefix. Pin types are Input, Output or Input/Output. Section "Electrical specification" and "DC characteristics" defines the all input and output type structures.

#### Electrical Description:

The CompactFlash™ Storage Card functions in three basic modes: 1) PC Card ATA using I/O Mode, 2) PC Card ATA using Memory Mode and 3) True IDE Mode, which is compatible with most disk drives. CompactFlash™ Storage Cards are required to support all three modes. The CF Cards normally function in the first and second modes, however they can optionally function in True IDE mode. The configuration of the CompactFlash™ Card will be controlled using the standard PCMCIA configuration registers starting at address 200h in the Attribute Memory space of the storage card. Or for True IDE Mode, pin 9 being grounded. The configuration of the CF Card will be controlled using configuration registers. The configuration registers are starting at the address defined in the Configuration Tuple (CISTPL\_CONFIG) in the Attribute Memory space of the CF Card. Signals, whose source is the host, is designated as inputs while signals that the CompactFlash™ Storage Card sources are outputs. The CompactFlash™ Storage Card logic levels conform to those specified in the PC Card Standard Release 8. Each signal has three possible operating modes:

- 1) PC Card Memory mode

- 2) PC Card I/O mode

- 3) True IDE mode

True IDE mode is required for CompactFlash $^{\text{TM}}$  Storage cards. All outputs from the card are totem pole except the data bus signals that are bi-directional tri-state

As a unique feature, the TOSHIBA CompactFlash $^{TM}$  Storage Card has automatic power down mode. When command process is completed, the card transits to this mode automatically. The card returns to active after receiving next command.

# Pin Assignments and Pin Type

|          | PC Card Me        | emory Mo | de               |          | PC Card           | I/O Mode |                 |          | True ID           | E Mode   |                 |

|----------|-------------------|----------|------------------|----------|-------------------|----------|-----------------|----------|-------------------|----------|-----------------|

| Pin      | Signal<br>Name    | Pin Type | In, Out<br>Type  | Pin      | Signal<br>Name    | Pin Type | In, Out<br>Type | Pin      | Signal<br>Name    | Pin Type | In, Out<br>Type |

| 1        | GND               |          | Ground           | 1        | GND               |          | Ground          | 1        | GND               |          | Ground          |

| 2        | D03               | I/O      | I4Z,OZ1          | 2        | D03               | I/O      | I4Z,OZ1         | 2        | D03               | I/O      | I4Z,OZ1         |

| 3        | D04               | I/O      | I4Z,OZ1          | 3        | D04               | I/O      | I4Z,OZ1         | 3        | D04               | I/O      | I4Z,OZ1         |

| 4        | D05               | I/O      | I4Z,OZ1          | 4        | D05               | I/O      | I4Z,OZ1         | 4        | D05               | I/O      | I4Z,OZ1         |

| 5        | D06               | I/O      | I4Z,OZ1          | 5        | D06               | I/O      | I4Z,OZ1         | 5        | D06               | I/O      | I4Z,OZ1         |

| 6        | D07               | I/O      | I4Z,OZ1          | 6        | D07               | I/O      | I4Z,OZ1         | 6        | D07               | I/O      | I4Z,OZ1         |

| 7        | -CE1              | I        | I3U              | 7        | -CE1              | I        | I3U             | 7        | -CS0              | I        | I3U             |

| 8        | A10               | I        | I3Z              | 8        | A10               | I        | I3Z             | 8        | A10 <sup>2</sup>  | I        | I3Z             |

| 9        | -OE               | I        | I4U              | 9        | -OE               | I        | I4U             | 9        | -ATA SEL          | I        | I4U             |

| 10       | A09               | I        | I3Z              | 10       | A09               | I        | I3Z             | 10       | A09 <sup>2</sup>  | I        | I3Z             |

| 11       | A08               | I        | I3Z              | 11       | A08               | I        | I3Z             | 11       | A08 <sup>2</sup>  | I        | I3Z             |

| 12       | A07               | Į        | I3Z              | 12       | A07               | I        | I3Z             | 12       | A07 <sup>2</sup>  | I        | I3Z             |

| 13       | VCC               |          | Power            | 13       | VCC               |          | Power           | 13       | VCC               |          | Power           |

| 14       | A06               | I        | I3Z              | 14       | A06               | I        | I3Z             | 14       | A06 <sup>2</sup>  | I        | I3Z             |

| 15       | A05               | I        | I3Z              | 15       | A05               | I        | I3Z             | 15       | A05 <sup>2</sup>  | I        | I3Z             |

| 16       | A04               | I        | I3Z              | 16       | A04               | I        | I3Z             | 16       | A04 <sup>2</sup>  | I        | I3Z             |

| 17       | A03               | I        | I3Z              | 17       | A03               | I        | I3Z             | 17       | A03 <sup>2</sup>  | I        | I3Z             |

| 18       | A02               | I        | I3Z              | 18       | A02               | I        | I3Z             | 18       | A02               | I        | I3Z             |

| 19       | A01               | I        | I3Z              | 19       | A01               | I        | I3Z             | 19       | A01               | ı        | I3Z             |

| 20       | A00               | - I      | I3Z              | 20       | A00               | 1        | I3Z             | 20       | A00               | 1        | I3Z             |

| 21       | D00               | I/O      | I4Z,OZ1          | 21       | D00               | I/O      | 14Z,OZ1         | 21       | D00               | 1/0      | I4Z,OZ1         |

| 22       | D01               | I/O      | 14Z,OZ1          | 22       | D01               | 1/0      | 14Z,OZ1         | 22       | D01               | 1/0      | 14Z,OZ1         |

| 23       | D02               | 1/0      | I4Z,OZ1          | 23       | D02               | 1/0      | 14Z,OZ1         | 23       | D02               | 1/0      | 14Z,OZ1         |

| 24<br>25 | WP<br>-CD2        | 0        | OT1              | 24<br>25 | -IOIS16           | 0        | OT1<br>Ground   | 24       | -IOIS16           | 0        | ON1<br>Ground   |

| 26       | -CD2<br>-CD1      | 0        | Ground<br>Ground | 26       | -CD2<br>-CD1      | 0        | Ground          | 25<br>26 | -CD2<br>-CD1      | 0        | Ground          |

| 27       | D11 <sup>1</sup>  | 1/0      | I4Z,OZ1          | 27       | D11 <sup>1</sup>  | 1/0      | I4Z,OZ1         | 27       | D11 <sup>1</sup>  | 1/0      | I4Z,OZ1         |

| 28       | D12 <sup>1</sup>  | 1/0      | 14Z,OZ1          | 28       | D12 <sup>1</sup>  | 1/0      | 14Z,OZ1         | 28       | D12 <sup>1</sup>  | I/O      | 14Z,OZ1         |

| 29       | D13 <sup>1</sup>  | I/O      | 14Z,OZ1          | 29       | D13 <sup>1</sup>  | I/O      | 14Z,OZ1         | 29       | D13 <sup>1</sup>  | I/O      | 14Z,OZ1         |

| 30       | D14 <sup>1</sup>  | I/O      | I4Z,OZ1          | 30       | D14 <sup>1</sup>  | I/O      | 14Z,OZ1         | 30       | D14 <sup>1</sup>  | I/O      | 14Z,OZ1         |

| 31       | D15 <sup>1</sup>  | I/O      | I4Z,OZ1          | 31       | D15 <sup>1</sup>  | I/O      | I4Z,OZ1         | 31       | D15 <sup>1</sup>  | I/O      | I4Z,OZ1         |

| 32       | -CE2 <sup>1</sup> | I        | I3U              | 32       | -CE2 <sup>1</sup> | I        | I3U             | 32       | -CS1 <sup>1</sup> | I        | I3U             |

| 33       | -VS1              | 0        | Ground           | 33       | -VS1              | 0        | Ground          | 33       | -VS1              | 0        | Ground          |

| 34       | -IORD             | I        | I4U              | 34       | -IORD             | 1        | I4U             | 34       | -DIOR             | I        | I4U             |

| 35       | -IOWR             | I        | I4U              | 35       | -IOWR             | I        | I4U             | 35       | -DIOW             | ı        | I4U             |

| 36       | -WE               | I        | I4U              | 36       | -WE               | I        | I4U             | 36       | -WE <sup>3</sup>  | I        | I4U             |

| 37       | READY             | 0        | OT1              | 37       | -IREQ             | 0        | OT1             | 37       | INTRQ             | 0        | OZ1             |

| 38       | VCC               |          | Power            | 38       | VCC               |          | Power           | 38       | VCC               |          | Power           |

| 39       | -CSEL             | I        | I1U              | 39       | -CSEL             | I        | I1U             | 39       | -CSEL             | I        | I1U             |

| 40       | -VS2              | 0        | OPEN             | 40       | -VS2              | 0        | OPEN            | 40       | -VS2              | 0        | OPEN            |

| 41       | RESET             | 1        | I3U              | 41       | RESET             | I        | I3U             | 41       | -RESET            | I        | I3U             |

# **TENTATIVE**

|     | PC Card Me       | emory Mo | de              |     | PC Card          | I/O Mode |                 |     | True ID          | E Mode   |                 |

|-----|------------------|----------|-----------------|-----|------------------|----------|-----------------|-----|------------------|----------|-----------------|

| Pin | Signal<br>Name   | Pin Type | In, Out<br>Type | Pin | Signal<br>Name   | Pin Type | In, Out<br>Type | Pin | Signal<br>Name   | Pin Type | In, Out<br>Type |

| 42  | -WAIT            | 0        | OT1             | 42  | -WAIT            | 0        | OT1             | 42  | IORDY            | 0        | ON1             |

| 43  | -INPACK          | 0        | OT1             | 43  | -INPACK          | 0        | OT1             | 43  | -INPACK          | 0        | OZ1             |

| 44  | -REG             | I        | I3U             | 44  | -REG             | I        | I3U             | 44  | -REG             | 1        | I3U             |

| 45  | BVD2             | I/O      | I4U,OT1         | 45  | -SPKR            | I/O      | I4U,OT1         | 45  | -DASP            | I/O      | I4U,ON1         |

| 46  | BVD1             | I/O      | I4U,OT1         | 46  | -STSCHG          | I/O      | I4U,OT1         | 46  | -PDIAG           | I/O      | I4U,ON1         |

| 47  | D08 <sup>1</sup> | I/O      | 14Z,OZ1         | 47  | D08 <sup>1</sup> | I/O      | I4Z,OZ1         | 47  | D08 <sup>1</sup> | I/O      | I4Z,OZ1         |

| 48  | D09 <sup>1</sup> | I/O      | I4Z,OZ1         | 48  | D09 <sup>1</sup> | I/O      | I4Z,OZ1         | 48  | D09 <sup>1</sup> | I/O      | I4Z,OZ1         |

| 49  | D10 <sup>1</sup> | I/O      | I4Z,OZ1         | 49  | D10 <sup>1</sup> | I/O      | I4Z,OZ1         | 49  | D10 <sup>1</sup> | I/O      | I4Z,OZ1         |

| 50  | GND              |          | Ground          | 50  | GND              |          | Ground          | 50  | GND              |          | Ground          |

Notes: 1. These signals are required only for 16 bit access and not required when installed in 8 bit systems. Devices should allow for 3-state signals not to consume current.

- 2. Should be grounded by the host.

- 3. Should be tied to VCC by the host.

# **Signal Description**

| Signal Name                                                                           | Dir | Pin No.                                    | Description                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 to A0<br>(PC Card Memory Mode)<br>A10 to A0<br>(PC Card I/O Mode)                 | -   | 8,10,11,12,1<br>4,15,16,17,1<br>8,19,20    | Address signals. A10 is the most significant bit, A0 is the least significant bit.                                                                                                                                                                                                                    |

| A2 to A0<br>(True IDE Mode)                                                           |     | 18,19,20                                   | In True IDE Mode only A2~0 are available, the remaining address lines should be grounded by the host.                                                                                                                                                                                                 |

| BVD1<br>(PC Card Memory Mode)                                                         |     |                                            | This signal always outputs high, since battery voltage detection is not supported.                                                                                                                                                                                                                    |

| -STSCHG<br>(PC Card I/O Mode)                                                         | I/O | 46                                         | This signal is asserted low to alert the host to changes in the READY and Write Protect states; while the I/O interface is configured .Its use is controlled by the Card Configuration and Status Register.                                                                                           |

| -PDIAG<br>(True IDE Mode)                                                             |     |                                            | In the True IDE Mode, this signal is bi-directional and used to show diagnostic result in the Master/Slave handshake protocol.                                                                                                                                                                        |

| BVD2<br>(PC Card Memory Mode)                                                         |     |                                            | This signal always outputs high, since battery voltage detection is not supported.                                                                                                                                                                                                                    |

| -SPKR<br>(PC Card I/O Mode)                                                           | I/O | 45                                         | This is the Binary Audio output signal. Since this card does not support the Binary Audio function, this signal always outputs high.                                                                                                                                                                  |

| -DASP<br>(True IDE Mode)                                                              |     |                                            | This bi-directional signal is the Disk Active / Slave Present signal.                                                                                                                                                                                                                                 |

| -CD1, -CD2<br>(PC Card Memory Mode)<br>-CD1, -CD2<br>(PC Card I/O Mode)<br>-CD1, -CD2 | 0   | 26,25                                      | These Card Detect pins are connected to ground on the CompactFlash Storage Card. They are used by the host to determine that the CompactFlash Storage Card is fully inserted into its socket.                                                                                                         |

| (True IDE Mode)  -CE1, -CE2 (PC Card Memory Mode)  -CE1, -CE2 (PC Card I/O Mode)      |     | 7,32                                       | These input signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed. Please refer to Access specifications.                                                                                                                        |

| -CS0, -CS1<br>(True IDE Mode)                                                         |     |                                            | In the True IDE Mode CS0 is the chip select for the task file registers while CS1 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                    |

| -CSEL (PC Card Memory Mode) -CSEL (PC Card I/O Mode) -CSEL (True IDE Mode)            | ı   | 39                                         | This signal is not used for this mode.  This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode.  When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave. |

| D15 to D00<br>(PC Card Memory Mode)<br>D15 to D00<br>(PC Card I/O Mode)               | I/O | 31,30,29,28,<br>27,49,48,47,<br>6,5,4,3,2, | These lines carry the Data, Commands and Status information between the host and the controller. D00 is the LSB of the Even Byte of the Word.D08 is the LSB of the Odd Byte of the Word.                                                                                                              |

| D15 to D00<br>(True IDE Mode)                                                         |     | 23,22,21                                   | True IDE Mode, all Task File operations occur in byte mode on the low order bus D00 to D07 while all data transfers are 16 bit using D00 to D15.                                                                                                                                                      |

| Signal Name                    | Dir | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|--------------------------------|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| -INPACK (PC Card Memory Mode)  |     |         | This signal is not used in this mode. Should not be connected at the host.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| -INPACK<br>(PC Card I/O Mode)  | 0   | 43      | The Input Acknowledge signal is asserted by the CompactFlash Storage Card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enable of any input data buffers between the CompactFlash Storage Card and the CPU.                                                                                                                                     |  |  |  |  |

| -INPACK<br>(True IDE Mode)     |     |         | This signal is not used in this mode. Should not be connected at the host.                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| -IORD<br>(PC Card Memory Mode) |     |         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| -IORD<br>(PC Card I/O Mode)    | ı   | 34      | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the CompcatFlash Storage Card when the card is configured to use the I/O interface.                                                                                                                                                                                                                                                                        |  |  |  |  |

| -DIOR<br>(True IDE Mode)       |     |         | In True IDE Mode, this signal has same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| -IOWR<br>(PC Card Memory Mode) |     |         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| -IOWR<br>(PC Card I/O Mode)    | ı   | 35      | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the CompactFlash Storage Card controller registers when the CompactFlash Storage Card is configured to use the I/O interface.  The clocking will occur on the negative to positive edge of the signal (trailing edge)                                                                                                                                                      |  |  |  |  |

| -DIOW<br>(True IDE Mode)       |     |         | In True IDE Mode, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| -OE<br>(PC Card Memory Mode)   |     |         | This is an Output Enable strobe generated by the host interface is used to read data from the CompactFlash Storage Card Memory Mode and to read the CIS and configuration registers.                                                                                                                                                                                                                                                                      |  |  |  |  |

| -OE<br>(PC Card I/O Mode)      | ı   | 9       | In PC Card I/O Mode, this signal is used to read the CIS and configuration registers.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| -ATA SEL<br>(True IDE Mode)    |     |         | To enable True IDE Mode this input should be grounded by the host .                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| -REG<br>(PC Card Memory Mode)  |     |         | This signal is used during Memory Cycles to distinguish between Common Memory and Register (Attribute) Memory accesses. High for Common Memory, Low for Attribute Memory.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| -REG<br>(PC Card I/O Mode)     | ı   | 44      | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| -REG<br>(True IDE Mode)        |     |         | This signal is not used in this mode.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| READY<br>(PC Card Memory Mode) | 0   | 37      | In Memory Mode, this signal is held high when the CompactFlash Storage Card is ready to accept a operation. When the card is busy, this signal is held low. The Host memory card socket must provide a pull-up resistor.  At power up or at Reset, the READY signal is held low until the CompactFlash Storage Card has completed its power up or reset function. No access of any type should be made to the CompactFlash Storage Card during this time. |  |  |  |  |

| -IREQ<br>(PC Card I/O Mode)    |     |         | This signal is used as interrupt Request. This line is assert low to indicate a interrupt request is issued.                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| INTRQ<br>(True IDE Mode)       |     |         | In True IDE Mode signal is the active high interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Signal Name                                                                   | Dir | Pin No. | Description                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

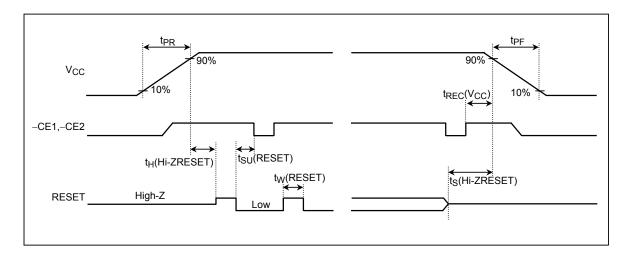

| RESET (PC Card Memory Mode) RESET (PC Card I/O Mode)                          | - 1 | 41      | When the pin is high, this signal Resets the CompactFlasgh Storage Card. The CompactFlash Storage Card is Reset only at power up if this pin is left high or open from power-up .The CompactFlash Storage Card is also Reset when the Soft Reset bit in the Card Configuration Option Register is set. |

| -RESET<br>(True IDE Mode)                                                     |     |         | In the True IDE Mode this input pin is the active low hardware reset from the host.                                                                                                                                                                                                                    |

| GND<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)         | _   | 1,50    | Ground                                                                                                                                                                                                                                                                                                 |

| VCC<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)         | _   | 13,38   | +5V +3.3V power                                                                                                                                                                                                                                                                                        |

| -VS1 / -VS2<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode) | 0   | 33,40   | Voltage Sense SignalsVS1 is grounded so that the CompactFlash Storage Card CIS can be read at 3.3 volts and –VS2 is reserved by PCMCIA for a secondary voltage.                                                                                                                                        |

| -WAIT (PC Card Memory Mode) -WAIT (PC Card I/O Mode)                          | 0   | 42      | The –WAIT signal is driven low by the CompactFlash Storage Card to indicate the host to delay completion of a memory or I/O cycle that is in progress.  This CompactFlash Storage Card outputs always high.                                                                                            |

| IORDY<br>(True IDE Mode)                                                      |     |         | This CompactFlash Storage Card outputs always high.                                                                                                                                                                                                                                                    |

| -WE<br>(PC Card Memory Mode)                                                  |     |         | This is a signal driven by the host and used for strobing memory write data to the registers of the CompactFlash Storage Card when the card is configured I the memory interface mode. It is also used for writing the configuration registers.                                                        |

| -WE<br>(PC Card I/O Mode)                                                     | I   | 36      | In PC Card I/O Mode, this signal is used only for writing the Attribute memory.                                                                                                                                                                                                                        |

| -WE<br>(True IDE Mode)                                                        |     |         | In True IDE Mode this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                                                             |

| WP<br>(PC Card Memory Mode )                                                  |     |         | Memory Mode-The CompactFlash Storage Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                                                                     |

| -IOIS16<br>(PC Card I/O Mode)                                                 | 0   | 24      | This signal is asserted when 16 bit or odd byte access to task file registers is accepted.                                                                                                                                                                                                             |

| -IOIS16<br>(True IDE Mode)                                                    |     |         | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                                                          |

# **Access Specifications**

# 1. Attribute access specifications

When CIS-ROM region or Configuration register region is accessed, read and write operations are executed under the condition of -REG="L" as follows. That region can be accessed by Byte/World/Old-byte modes, which are defined by PC card standard specifications.

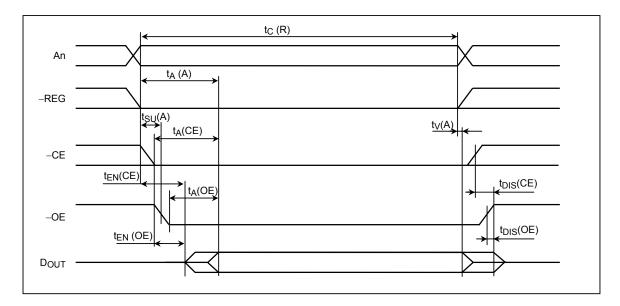

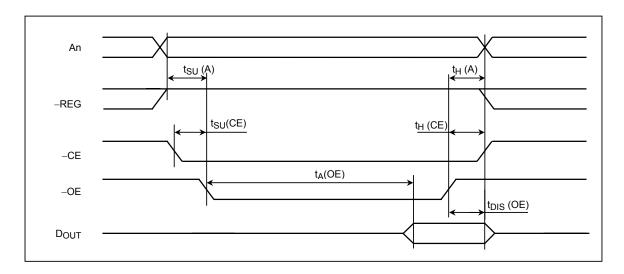

#### Attribute Read Access Mode

| Mode                   | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15 | D0 to D7  |

|------------------------|------|------|------|----|-----|-----|-----------|-----------|

| Standby mode           | Х    | Н    | Н    | Х  | Х   | Х   | High-Z    | High-Z    |

| Duta access (Ohit)     | L    | Н    | L    | L  | L   | Н   | High-Z    | even byte |

| Byte access (8bit)     | L    | н    | L    | Н  | L   | н   | High-Z    | Invalid   |

| Word access (16bit)    | L    | L    | L    | X  | L   | Н   | invalid   | even byte |

| Odd byte access (8bit) | L    | L    | Н    | X  | L   | Н   | invalid   | High-Z    |

Note: X L or H

#### Attribute Write Access Mode

| Mode                   | -REG | -CE2 | -CE1 | A0 | -OE | -WE | D8 to D15  | D0 to D7   |

|------------------------|------|------|------|----|-----|-----|------------|------------|

| Standby mode           | X    | Н    | Н    | Х  | Х   | Х   | Don't care | Don't care |

| D. 4 (0h;4)            | L    | Н    | L    | L  | Н   | L   | Don't care | even byte  |

| Byte access (8bit)     | L    | н    | L    | Н  | Н   | ا ـ | Don't care | Don't care |

| Word access (16bit)    | L    | L    | L    | Х  | Н   | L   | Don't care | even byte  |

| Odd byte access (8bit) | L    | L    | Н    | Х  | Н   | L   | Don't care | Don't care |

Note: X L or H

Write CIS-ROM region is invalid.

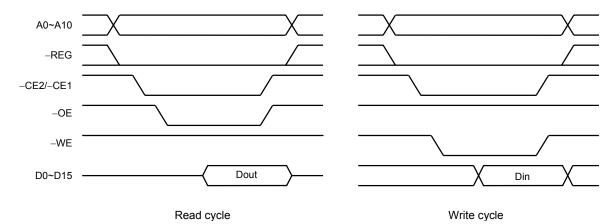

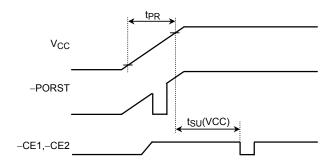

## • Attribute Access Timing Example

### 2. Task File register access specifications

There are two cases of Task File register mapping, one is mapped I/O address area, the other is mapped Memory address area. Each case of Task File registers read and write operations is executed under the condition as follows. That area can be accessed by Byte/World/Odd Byte modes, which are defined by PC card standard specifications.

### • (1) I/O address map

Task File Register Read Access Mode (1)

| Mode                   | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15 | D0 to D7  |

|------------------------|------|------|------|----|-------|-------|-----|-----|-----------|-----------|

| Standby mode           | Х    | Н    | Н    | Х  | Х     | Х     | Х   | Х   | High-Z    | High-Z    |

| Duta aggas (Shit)      | L    | Η    | L    | L  | L     | Н     | Н   | Η   | High-Z    | even byte |

| Byte access (8bit)     | L    | Н    | L    | Н  | L     | Н     | Н   | Н   | High-Z    | odd byte  |

| Word access (16bit)    | L    | L    | L    | Х  | L     | Н     | Н   | Н   | odd byte  | even byte |

| Odd byte access (8bit) | L    | L    | Н    | Х  | L     | Н     | Н   | Н   | odd byte  | High-Z    |

Note: X L or H

### Task File Register Write Access Mode (1)

| Mode                   | -REG | -CE2 | -CE1 | A0 | -IORD | -IOWR | -OE | -WE | D8 to D15  | D0 to D7   |

|------------------------|------|------|------|----|-------|-------|-----|-----|------------|------------|

| Standby mode           | Х    | Н    | Н    | Х  | Х     | Х     | Х   | Х   | Don't care | Don't care |

| Duta aggas (Shit)      | L    | Η    | L    | L  | Н     | L     | Н   | Η   | Don't care | even byte  |

| Byte access (8bit)     | L    | Η    | ــا  | Н  | Н     | L     | Н   | Ι   | Don't care | odd byte   |

| Word access (16bit)    | L    | L    | L    | Х  | Н     | L     | Н   | Н   | odd byte   | even byte  |

| Odd byte access (8bit) | L    | L    | Н    | Х  | Н     | L     | Н   | Н   | odd byte   | Don't care |

Note: X L or H

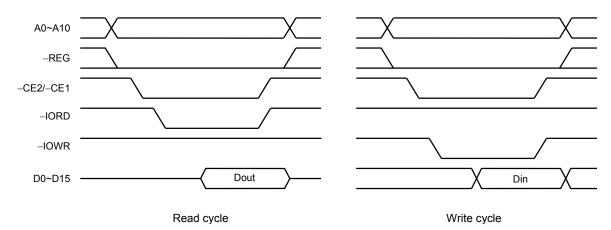

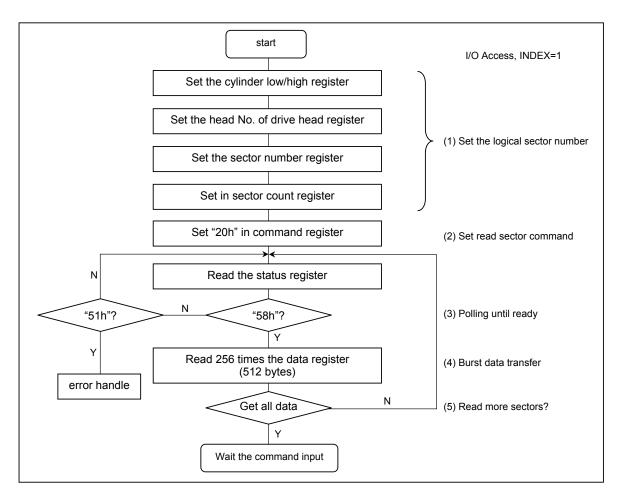

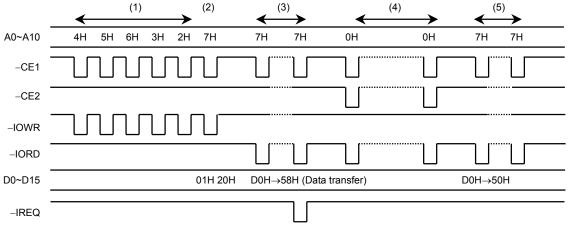

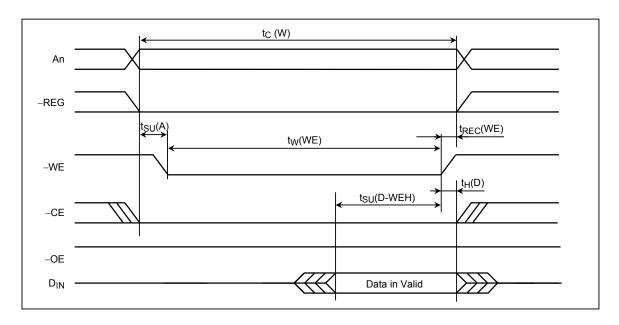

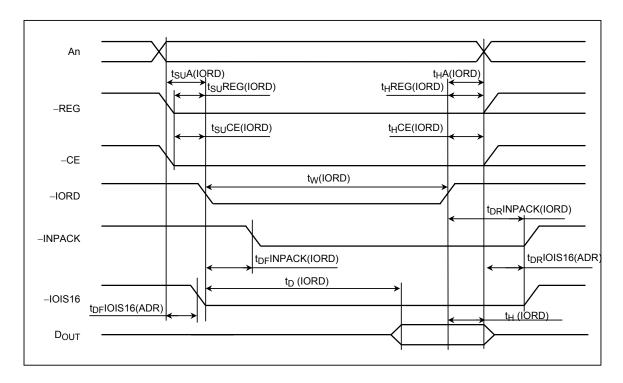

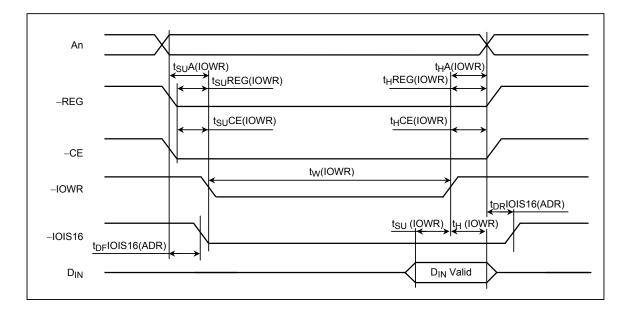

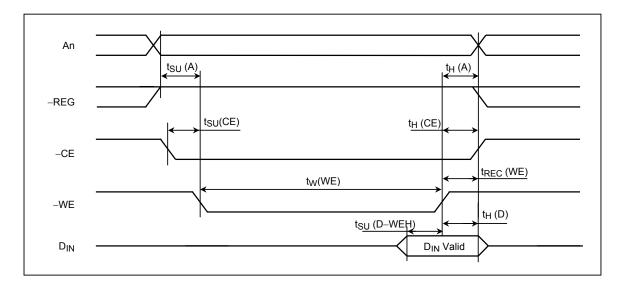

## • Task File Register Access Timing Example (1)

# • (2) Memory address map

Task File Register Read Access Mode (2)

| Mode                   | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15 | D0 to D7  |

|------------------------|------|------|------|----|-----|-----|-------|-------|-----------|-----------|

| Standby mode           | Х    | Н    | Н    | Х  | Х   | Х   | Х     | Х     | High-Z    | High-Z    |

| 5 ( (0) ()             | Н    | Н    | L    | L  | L   | Н   | Н     | Н     | High-Z    | even byte |

| Byte access (8bit)     | Н    | Н    | L    | Н  | L   | Н   | Н     | Н     | High-Z    | odd byte  |

| Word access (16bit)    | Н    | L    | L    | Х  | L   | Н   | Н     | Н     | odd byte  | even byte |

| Odd byte access (8bit) | Н    | L    | Н    | Х  | L   | Н   | Н     | Н     | odd byte  | High-Z    |

Note: X L or H

## Task File Register Write Access Mode (2)

| Mode                   | -REG | -CE2 | -CE1 | A0 | -OE | -WE | -IORD | -IOWR | D8 to D15  | D0 to D7   |

|------------------------|------|------|------|----|-----|-----|-------|-------|------------|------------|

| Standby mode           | Х    | Н    | Н    | Х  | Х   | Х   | Х     | Х     | Don't care | Don't care |

|                        | Н    | Н    | L    | L  | Н   | L   | Н     | Н     | Don't care | even byte  |

| Byte access (8bit)     | Н    | Н    | L    | Н  | Н   | L   | Н     | Н     | Don't care | odd byte   |

| Word access (16bit)    | Н    | L    | L    | Х  | Н   | L   | Н     | Н     | odd byte   | even byte  |

| Odd byte access (8bit) | Н    | L    | Н    | Х  | Н   | L   | Н     | Н     | odd byte   | Don't care |

Note: X L or H

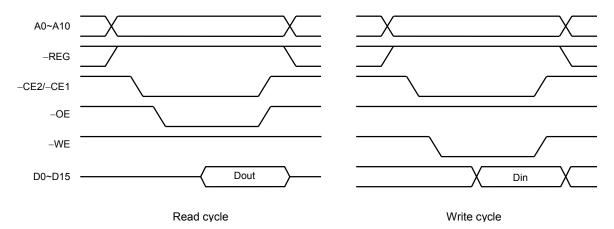

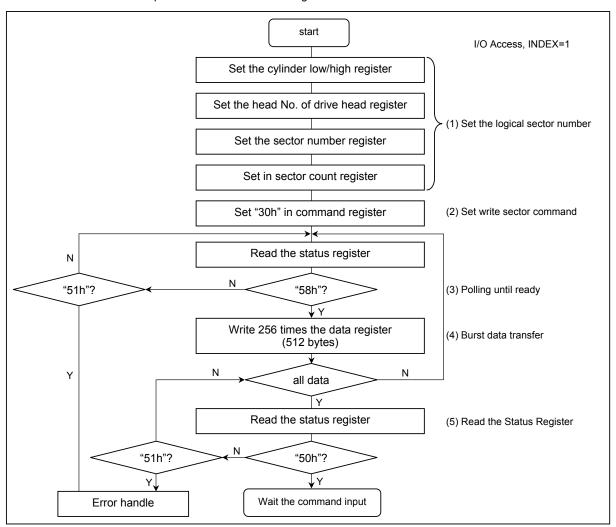

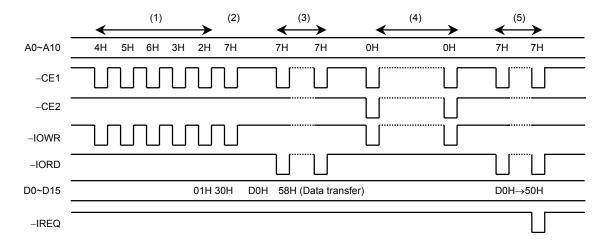

# • Task File Register Access Timing Example (2)

#### 3. True IDE Mode

The card can be configured in a True IDE This card is configured in this mode only when the-OE input signal is asserted GND by the host while power on. In this True IDE mode Attribute Registers are not accessible from the host. Only I/O operation to the task file and data register is allowed. If this card is configured during power on sequence, data register is accessed in word (16-bit). The card permits 8-bit accessed if the user issues a Set Feature Command to put the device in 8-bit mode.

### True IDE Mode Read I/O Function

| Mode                    | -CE2 | -CE1 | A0~A2 | -DIOR | -DIOW | D8 ~ D15 | D0 ~ D7    |

|-------------------------|------|------|-------|-------|-------|----------|------------|

| Invalid mode            | L    | L    | X     | Х     | Х     | High-Z   | High-Z     |

| Standby mode            | Η    | Η    | Х     | X     | Х     | High-Z   | High-Z     |

| Data register access    | Н    | L    | 0     | L     | Н     | Odd byte | even byte  |

| Alternate status access | L    | Н    | 6H    | L     | Н     | High-Z   | Status out |

| Other task file access  | Н    | L    | 1~7H  | L     | Н     | High-Z   | Data       |

Note: X L or H

### True IDE Mode Write I/O Function

| Mode                    | -CE2 | -CE1 | A0~A2 | -DIOR | -DIOW | D8 ~ D15   | D0 ~ D7    |

|-------------------------|------|------|-------|-------|-------|------------|------------|

| Invalid mode            | L    | L    | Х     | Х     | Х     | Don't care | Don't care |

| Standby mode            | Н    | Н    | Х     | Х     | Х     | Don't care | Don't care |

| Data register access    | Н    | L    | 0     | Н     | L     | Odd byte   | even byte  |

| Control register access | L    | Н    | 6H    | Н     | L     | Don't care | Control in |

| Other task file access  | Н    | L    | 1~7H  | Н     | L     | Don't care | Data       |

Note: X L or H

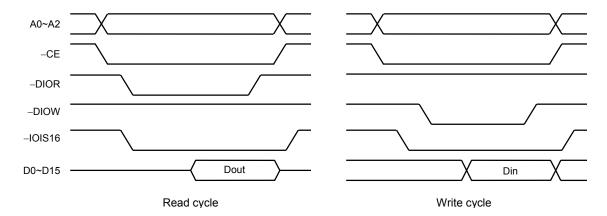

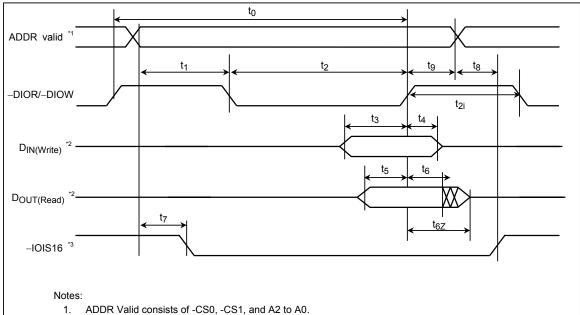

# • True IDE Mode I/O Access Timing Example

# **Configuration register specifications**

This card supports four Configuration registers for the purpose of the configuration and observation of this card. These registers can be used in memory card mode and I/O card mode. In True IDE mode, these registers cannot be used

## 1. Configuration Option register (Address 200h)

This register is used for the configuration of the card configuration status and for the issuing soft reset to the card.

| bit7   | bit6    | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|--------|---------|------|------|------|------|------|------|

| SRESET | LevIREQ |      |      | IND  | EX   |      |      |

Note: initial value 00H

| Name                | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRESET<br>(HOST->)  | R/W | Setting this bit to "1", places the card in the reset state (Card Hard Reset). This operation is equal to Hard Reset, except this bit is not cleared. Then this bit set to "0", places the card in the reset state of Hard Reset (This bit is set to "0" by Hard Reset). Card configuration status is reset and the card internal initialized operation starts when Card Hard Reset is executed, so next access to the card should be the same sequence as the power on sequence. |

| LevIREQ<br>(HOST->) | R/W | This bit sets to "0" when pulse mode interrupt is selected, and "1" when level mode interrupt is selected.                                                                                                                                                                                                                                                                                                                                                                        |

| INDEX<br>(HOST->)   | R/W | This bits is used for select operation mode of the card as follows.  When Power on, Card Hard Reset and Soft Reset, this data is "000000" for the purpose of Memory card interface recognition.                                                                                                                                                                                                                                                                                   |

Note: initial value 00H

## · INDEX bit assignment

#### INDEX bit

| 5 | 4 | 3 | 2 | 1 | 0 | Card mode   | Task file register address | Mapping mode          |

|---|---|---|---|---|---|-------------|----------------------------|-----------------------|

| 0 | 0 | 0 | 0 | 0 | 0 | Memory card | 0H to FH, 400H to 7FFH     | Memory mapped         |

| 0 | 0 | 0 | 0 | 0 | 1 | I/O card    | xx0H to xxFH               | Contiguous I/O mapped |

| 0 | 0 | 0 | 0 | 1 | 0 | I/O card    | 1F0H to 1F7H, 3F6H to 3F7H | Primary I/O mapped    |

| 0 | 0 | 0 | 0 | 1 | 1 | I/O card    | 170H to 177H, 376H to 377H | Secondary I/O mapped  |

2. Configuration and Status register (Address 202h)

This register is used for observing the state of the card.

| bit7  | bit6   | bit5  | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|--------|-------|------|------|------|------|------|

| CHGED | SIGCHG | IOIS8 | 0    | 0    | PWD  | INTR | 0    |

Note: initial value 00H

| Name     | R/W | Function                                                                                                |

|----------|-----|---------------------------------------------------------------------------------------------------------|

| CHGED    |     | This bit indicates that CREADY bit on Pin Replacement register is set to "1". When CHGED bit is         |

| (CARD->) | R   | set to "1", -STSCHG pin is held "L" at the condition of SIGCHG bit set to "1" and the card              |

|          |     | configured for the I/O interface.                                                                       |

| SIGCHG   |     | This bit is set or reset by the host for enabling and disabling the status-change signal (-STSCHG       |

| (HOST->) | R/W | pin). When the card is configured I/O card interface and this bit is set "1", -STSCHG pin is            |

|          |     | controlled by CHGED bit. If this bit is set to "0", -STSCHG pin is kept "H".                            |

| IOIS8    | DAM | The host sets this field to "1" when it can provide I/O cycles only with on 8 bit data bus (D7 to D0).  |

| (HOST->) | R/W |                                                                                                         |

| PWD      |     | When this bit is set to "1", the card enters sleep state (Power Down mode). When this bit is reset      |

| (HOST->) | DAM | to "0", the card transfers to idle state (active mode). RREADY bit on Pin Replacement Register          |

|          | R/W | becomes BUSY when this bit is changed. RREADY will not become Ready until the power state               |

|          |     | requested has been entered.                                                                             |

| INTR     |     | This bit indicates the internal state of the interrupt request. This bit state is available whether I/O |

| (CARD->) |     | card interface has been configured or not. This signal remains true until the condition, which          |

|          | R   | caused the interrupt request, has been serviced. If the -IEN bit in the Device Control Register         |

|          |     | disables interrupts, this bit is a zero.                                                                |

### 3. Pin Replacement register (Address 204H)

This register is used for providing the state of -IREQ signal when the card configured I/O card interface.

**TENTATIVE**

| bit7 | bit6 | bit5   | bit4 | bit3 | bit2 | bit1   | bit0 |

|------|------|--------|------|------|------|--------|------|

| 0    | 0    | CREADY | 0    | 1    | 1    | RREADY | 0    |

Note: initial value 0CH

| Name               | R/W | Function                                                                                               |

|--------------------|-----|--------------------------------------------------------------------------------------------------------|

| CREADY<br>(HOST->) | R/W | This bit is set to "1" when the RREADY bit changes state. The host may also write this bit.            |

| RREADY<br>(HOST->) | R   | When read, this bit indicates READY pin states. When written, this bit is used for CREADY bit masking. |

## 4. Socket and Copy register (Address 206H)

This register is used for identification of the card from the other cards. Host can read and write this register. Host should set this register before this card's Configuration Option register set.

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 0    | DRV# | 0    | 0    | 0    | 0    |

Note: initial value

| Name             | R/W | Function                                                                                                                                                                                                                  |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRV#<br>(HOST->) | R/W | These fields are used for the configuration of the plural cards. When host configures the plural cards, written the card's copy number in this field. In this way, host can perform the card's master/slave organization. |

# **CIS** information

CIS information of Compact Flash card is defined as follows.

| Address | Data | Description of contents               | CIS function |

|---------|------|---------------------------------------|--------------|

| 000H    | 01H  | CISTPL_DEVICE                         | Tuple code   |

| 002H    | 03H  | TPL_LINK                              | Tuple link   |

| 004H    | D9H  | Device information                    | Tuple data   |

| 006H    | 01H  | Device information                    | Tuple data   |

| 008H    | FFH  | END MARKER                            | End of Tuple |

| 00AH    | 1CH  | CISTPL_DEVICE_OC                      | Tuple code   |

| 00CH    | 04H  | TPL_LINK                              | Tuple link   |

| 00EH    | 03H  | Conditions information                | Tuple data   |

| 010H    | D9H  | Device information                    | Tuple data   |

| 012H    | 01H  | Device information                    | Tuple data   |

| 014H    | FFH  | END MARKER                            | End of Tuple |

| 016H    | 18H  | CISTPL_JEDEC_C                        | Tuple code   |

| 018H    | 02H  | TPL_LINK                              | Tuple link   |

| 01AH    | DFH  | PCMCIA's manufacturer's JEDEC ID code | Tuple data   |

| 01CH    | 01H  | PCMCIA's JEDEC device code            | Tuple data   |

| 01EH    | 20H  | CISTPL_MANFID                         | Tuple code   |

| 020H    | 04H  | TPL_LINK                              | Tuple link   |

| 022H    | 98H  | Low byte of manufacturer's ID code    | Tuple data   |

| 024H    | 00H  | High byte of manufacturer's ID code   | Tuple data   |

| 026H    | 00H  | Low byte of product code              | Tuple data   |

| 028H    | 00H  | High byte of product code             | Tuple data   |

| 02AH    | 15H  | CISTPL_VERS_1                         | Tuple code   |

| 02CH    | 20H  | TPL_LINK                              | Tuple link   |

| 02EH    | 04H  | TPLLV1_MAJOR                          | Tuple data   |

| 030H    | 01H  | TPLLV1_MINOR                          | Tuple data   |

| 032H    | 54H  | 'T' (Vender Specific Strings)         | Tuple data   |

| 034H    | 4FH  | 'O' (Vender Specific Strings)         | Tuple data   |

| 036H    | 53H  | 'S' (Vender Specific Strings)         | Tuple data   |

| 038H    | 48H  | ' H ' (Vender Specific Strings)       | Tuple data   |

| 03AH    | 49H  | 'I' (Vender Specific Strings)         | Tuple data   |

| 03CH    | 42H  | ' B ' (Vender Specific Strings)       | Tuple data   |

| 03EH    | 41H  | ' A ' (Vender Specific Strings)       | Tuple data   |

| 040H    | 20H  | ' '(Vender Specific Strings)          | Tuple data   |

| 042H    | 54H  | 'T' (Vender Specific Strings)         | Tuple data   |

| 044H    | 48H  | ' H ' (Vender Specific Strings)       | Tuple data   |

| 046H    | 4EH  | ' N ' (Vender Specific Strings)       | Tuple data   |

| 048H    | 43H  | ' C ' (Vender Specific Strings)       | Tuple data   |

| 04AH    | 46H  | 'F' (Vender Specific Strings)         | Tuple data   |

| 04CH    | Х    | (Card capacity dependent strings)     | Tuple data   |

| 04EH    | Х    | (Card capacity dependent strings)     | Tuple data   |

| 050H    | Х    | (Card capacity dependent strings)     | Tuple data   |

| 052H    | Х    | (Card capacity dependent strings)     | Tuple data   |

| 054H    | 44H  | ' D ' (Vender Specific Strings)       | Tuple data   |

| 056H    | 47H  | ' G ' (Vender Specific Strings)       | Tuple data   |

| Address | Data | Description of contents                    | CIS function |

|---------|------|--------------------------------------------|--------------|

| 058H    | 20H  | , ,                                        | Tuple data   |

| 05AH    | 00H  | Null Terminator                            | Tuple data   |

| 05CH    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 05EH    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 060H    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 062H    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 064H    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 066H    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 068H    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 06AH    | 00H  | Reserved (Vender Specific Strings)         | Tuple data   |

| 06CH    | FFH  | END MARKER                                 | End of Tuple |

| 06EH    | 21H  | CISTPL_FUNCID                              | Tuple code   |

| 070H    | 02H  | TPL_LINK                                   | Tuple link   |

| 072H    | 04H  | IC Card function code                      | Tuple data   |

| 074H    | 01H  | System initialization bit mask             | Tuple data   |

| 076H    | 22H  | CISTPL_FUNCE                               | Tuple code   |

| 078H    | 02H  | TPL_LINK                                   | Tuple link   |

| 07AH    | 01H  | Type of extended data                      | Tuple data   |

| 07CH    | 01H  | Function information                       | Tuple data   |

| 07EH    | 22H  | CISTPL_FUNCE                               | Tuple code   |

| H080    | 03H  | TPL_LINK                                   | Tuple link   |

| 082H    | 02H  | Type of extended data                      | Tuple data   |

| 084H    | 0CH  | Function information                       | Tuple data   |

| 086H    | 0FH  | Function information                       | Tuple data   |

| H880    | 1AH  | CISTPL_CONFIG                              | Tuple code   |

| 08AH    | 05H  | TPL_LINK                                   | Tuple link   |

| 08CH    | 01H  | Size field                                 | Tuple data   |

| 08EH    | 03H  | Index number of last entry                 | Tuple data   |

| 090H    | 00H  | Configuration register base address (Low)  | Tuple data   |

| 092H    | 02H  | Configuration register base address (High) | Tuple data   |

| 094H    | 0FH  | Configuration register present mask        | Tuple data   |

| 096H    | 1BH  | CISTPL_CFTABLE_ENTRY                       | Tuple code   |

| 098H    | 08H  | TPL_LINK                                   | Tuple link   |

| 09AH    | C0H  | Configuration Index Byte                   | Tuple data   |

| 09CH    | C0H  | Interface Descriptor                       | Tuple data   |

| 09EH    | A1H  | Feature Select                             | Tuple data   |

| 0A0H    | 01H  | Vcc Selection Byte                         | Tuple data   |

| 0A2H    | 55H  | Nom V Parameter                            | Tuple data   |

| 0A4H    | 08H  | Memory length (256 byte pages)             | Tuple data   |

| 0A6H    | 00H  | Memory length (256 byte pages)             | Tuple data   |

| 0A8H    | 20H  | Misc features                              | Tuple data   |

| 0AAH    | 1BH  | CISTPL_CFTABLE_ENTRY                       | Tuple code   |

| 0ACH    | 06H  | TPL_LINK                                   | Tuple link   |

| 0AEH    | 00H  | Configuration Index Byte                   | Tuple data   |

| 0B0H    | 01H  | Feature Select                             | Tuple data   |

| 0B2H    | 21H  | Vcc Selection Byte                         | Tuple data   |

| 0B4H    | B5H  | Nom V Parameter                            | Tuple data   |

| Address | Data | Description of contents   | CIS function |

|---------|------|---------------------------|--------------|

| 0B6H    | 1EH  | Nom V Parameter           | Tuple data   |

| 0B8H    | 4DH  | Peak I Parameter          | Tuple data   |

| 0BAH    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 0BCH    | 0AH  | TPL_LINK                  | Tuple link   |

| 0BEH    | C1H  | Configuration Index Byte  | Tuple data   |

| 0C0H    | 41H  | Interface Descriptor      | Tuple data   |

| 0C2H    | 99H  | Feature Select            | Tuple data   |

| 0C4H    | 01H  | Vcc Selection Byte        | Tuple data   |

| 0C6H    | 55H  | Nom V Parameter           | Tuple data   |

| 0C8H    | 64H  | I/O Parameter             | Tuple data   |

| 0CAH    | F0H  | IRQ parameter             | Tuple data   |

| 0CCH    | FFH  | IRQ request mask          | Tuple data   |

| 0CEH    | FFH  | IRQ request mask          | Tuple data   |

| 0D0H    | 20H  | Misc features             | Tuple data   |

| 0D2H    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 0D4H    | 06H  | TPL_LINK                  | Tuple link   |

| 0D6H    | 01H  | Configuration Index Byte  | Tuple data   |

| 0D8H    | 01H  | Feature Select            | Tuple data   |

| 0DAH    | 21H  | Vcc Selection Byte        | Tuple data   |

| 0DCH    | В5Н  | Nom V Parameter           | Tuple data   |

| 0DEH    | 1EH  | Nom V Parameter           | Tuple data   |

| 0E0H    | 4DH  | Peak I Parameter          | Tuple data   |

| 0E2H    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 0E4H    | 0FH  | TPL_LINK                  | Tuple link   |

| 0E6H    | C2H  | Configuration Index Byte  | Tuple data   |

| 0E8H    | 41H  | Interface Descriptor      | Tuple data   |

| 0EAH    | 99H  | Feature Select            | Tuple data   |

| 0ECH    | 01H  | Vcc Selection Byte        | Tuple data   |

| 0EEH    | 55H  | Nom V Parameter           | Tuple data   |

| 0F0H    | EAH  | I/O parameter             | Tuple data   |

| 0F2H    | 61H  | I/O range length and size | Tuple data   |

| 0F4H    | F0H  | Base address              | Tuple data   |

| 0F6H    | 01H  | Base address              | Tuple data   |

| 0F8H    | 07H  | Address length            | Tuple data   |

| 0FAH    | F6H  | Base address              | Tuple data   |

| 0FCH    | 03H  | Base address              | Tuple data   |

| 0FEH    | 01H  | Address length            | Tuple data   |

| 100H    | EEH  | IRQ parameter             | Tuple data   |

| 102H    | 20H  | Misc features             | Tuple data   |

| 104H    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 106H    | 06H  | TPL_LINK                  | Tuple link   |

| 108H    | 02H  | Configuration Index Byte  | Tuple data   |

| 10AH    | 01H  | Feature Select            | Tuple data   |

| 10CH    | 21H  | Vcc Selection Byte        | Tuple data   |

| 10EH    | В5Н  | Nom V Parameter           | Tuple data   |

| 110H    | 1EH  | Nom V Parameter           | Tuple data   |

| 112H    | 4DH  | Peak I Parameter          | Tuple data   |

|         |      |                           |              |

# **TENTATIVE**

| Address | Data | Description of contents   | CIS function |

|---------|------|---------------------------|--------------|

| 114H    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 116H    | 0FH  | TPL_LINK                  | Tuple link   |

| 118H    | СЗН  | Configuration Index Byte  | Tuple data   |

| 11AH    | 41H  | Interface Descriptor      | Tuple data   |

| 11CH    | 99H  | Feature Select            | Tuple data   |

| 11EH    | 01H  | Vcc Selection Byte        | Tuple data   |

| 120H    | 55H  | Nom V Parameter           | Tuple data   |

| 122H    | EAH  | I/O parameter             | Tuple data   |

| 124H    | 61H  | I/O range length and size | Tuple data   |

| 126H    | 70H  | Base address              | Tuple data   |

| 128H    | 01H  | Base address              | Tuple data   |

| 12AH    | 07H  | Address length            | Tuple data   |

| 12CH    | 76H  | Base address              | Tuple data   |

| 12EH    | 03H  | Base address              | Tuple data   |

| 130H    | 01H  | Address length            | Tuple data   |

| 132H    | EEH  | IRQ parameter             | Tuple data   |

| 134H    | 20H  | Misc features             | Tuple data   |

| 136H    | 1BH  | CISTPL_CFTABLE_ENTRY      | Tuple code   |

| 138H    | 06H  | TPL_LINK                  | Tuple link   |

| 13AH    | 03H  | Configuration Index Byte  | Tuple data   |

| 13CH    | 01H  | Feature Select            | Tuple data   |

| 13EH    | 21H  | Vcc Selection Byte        | Tuple data   |

| 140H    | B5H  | Nom V Parameter           | Tuple data   |

| 142H    | 1EH  | Nom V Parameter           | Tuple data   |

| 144H    | 4DH  | Peak I Parameter          | Tuple data   |

| 146H    | 14H  | CISTPL_NO_LINK            | Tuple code   |

| 148H    | 00H  | TPL_LINK                  | Tuple link   |

| 14AH    | FFH  | CISTPL_END                | End of Tuple |

# **Task File Register specification**

These registers are used for reading and writing the storage data in this card. These registers are mapped five types by the configuration of INDEX in Configuration Option register. The decoded addresses are shown as follows.

# Memory map (INDEX=0)

| -REG | A10 | A9~A4 | A3 | A2 | A1 | A0 | Offset | −OE=L                   | -WE=L                   |

|------|-----|-------|----|----|----|----|--------|-------------------------|-------------------------|

| 1    | 0   | Х     | 0  | 0  | 0  | 0  | 0H     | Data register           | Data register           |

| 1    | 0   | Х     | 0  | 0  | 0  | 1  | 1H     | Error register          | Feature register        |

| 1    | 0   | Х     | 0  | 0  | 1  | 0  | 2H     | Sector count register   | Sector count register   |

| 1    | 0   | Х     | 0  | 0  | 1  | 1  | 3H     | Sector number register  | Sector number register  |

| 1    | 0   | Х     | 0  | 1  | 0  | 0  | 4H     | Cylinder low register   | Cylinder low register   |

| 1    | 0   | Х     | 0  | 1  | 0  | 1  | 5H     | Cylinder high register  | Cylinder high register  |

| 1    | 0   | Х     | 0  | 1  | 1  | 0  | 6H     | Drive head register     | Drive head register     |

| 1    | 0   | Х     | 0  | 1  | 1  | 1  | 7H     | Status register         | Command register        |

| 1    | 0   | Х     | 1  | 0  | 0  | 0  | 8H     | Dup. even data register | Dup. even data register |

| 1    | 0   | Х     | 1  | 0  | 0  | 1  | 9H     | Dup.odd data register   | Dup.odd data register   |

| 1    | 0   | Х     | 1  | 1  | 0  | 1  | DH     | Dup.error register      | Dup.feature register    |

| 1    | 0   | Х     | 1  | 1  | 1  | 0  | EH     | Alt. status register    | Device control register |

| 1    | 0   | Х     | 1  | 1  | 1  | 1  | FH     | Drive address register  | Reserved                |

| 1    | 1   | Х     | Х  | Х  | Х  | 0  | 8H     | Even data register      | Even data register      |

| 1    | 1   | Х     | Х  | Х  | Х  | 1  | 9H     | Odd data register       | Odd data register       |

## Contiguous I/O map (INDEX=1)

| -REG | A10~A4 | A3 | A2 | A1 | A0 | Offset | −OE=L                   | -WE=L                   |

|------|--------|----|----|----|----|--------|-------------------------|-------------------------|

| 0    | Х      | 0  | 0  | 0  | 0  | 0H     | Data register           | Data register           |

| 0    | ×      | 0  | 0  | 0  | 1  | 1H     | Error register          | Feature register        |

| 0    | Х      | 0  | 0  | 1  | 0  | 2H     | Sector count register   | Sector count register   |

| 0    | Х      | 0  | 0  | 1  | 1  | 3H     | Sector number register  | Sector number register  |

| 0    | Х      | 0  | 1  | 0  | 0  | 4H     | Cylinder low register   | Cylinder low register   |

| 0    | Х      | 0  | 1  | 0  | 1  | 5H     | Cylinder high register  | Cylinder high register  |

| 0    | Х      | 0  | 1  | 1  | 0  | 6H     | Drive head register     | Drive head register     |

| 0    | Х      | 0  | 1  | 1  | 1  | 7H     | Status register         | Command register        |

| 0    | Х      | 1  | 0  | 0  | 0  | 8H     | Dup. even data register | Dup. even data register |

| 0    | Х      | 1  | 0  | 0  | 1  | 9H     | Dup.odd data register   | Dup.odd data register   |

| 0    | Х      | 1  | 1  | 0  | 1  | DH     | Dup.error register      | Dup.feature register    |

| 0    | Х      | 1  | 1  | 1  | 0  | EH     | Alt. status register    | Device control register |

| 0    | Х      | 1  | 1  | 1  | 1  | FH     | Drive address register  | Reserved                |

# Primary I/O map (INDEX=2)

| -REG | A10 | A9~A4 | A3 | A2 | A1 | A0 | -IORD=L                | -IOWR=L                 |

|------|-----|-------|----|----|----|----|------------------------|-------------------------|

| 0    | Х   | 1FH   | 0  | 0  | 0  | 0  | Data register          | Data register           |

| 0    | Х   | 1FH   | 0  | 0  | 0  | 1  | Error register         | Feature register        |

| 0    | ×   | 1FH   | 0  | 0  | 1  | 0  | Sector count register  | Sector count register   |

| 0    | Х   | 1FH   | 0  | 0  | 1  | 1  | Sector number register | Sector number register  |

| 0    | X   | 1FH   | 0  | 1  | 0  | 0  | Cylinder low register  | Cylinder low register   |

| 0    | X   | 1FH   | 0  | 1  | 0  | 1  | Cylinder high register | Cylinder high register  |

| 0    | X   | 1FH   | 0  | 1  | 1  | 0  | Drive head register    | Drive head register     |

| 0    | X   | 1FH   | 0  | 1  | 1  | 1  | Status register        | Command register        |

| 0    | Х   | 3FH   | 0  | 1  | 1  | 0  | Alt. status register   | Device control register |

| 0    | Х   | 3FH   | 0  | 1  | 1  | 1  | Drive address register | Reserved                |

# Secondary I/O map (INDEX=3)

| -REG | A10 | A9~A4 | A3 | A2 | A1 | A0 | -IORD=L                | -IOWR=L                 |

|------|-----|-------|----|----|----|----|------------------------|-------------------------|

| 0    | Х   | 17H   | 0  | 0  | 0  | 0  | Data register          | Data register           |

| 0    | Х   | 17H   | 0  | 0  | 0  | 1  | Error register         | Feature register        |

| 0    | Х   | 17H   | 0  | 0  | 1  | 0  | Sector count register  | Sector count register   |

| 0    | Х   | 17H   | 0  | 0  | 1  | 1  | Sector number register | Sector number register  |

| 0    | Х   | 17H   | 0  | 1  | 0  | 0  | Cylinder low register  | Cylinder low register   |

| 0    | Х   | 17H   | 0  | 1  | 0  | 1  | Cylinder high register | Cylinder high register  |

| 0    | Х   | 17H   | 0  | 1  | 1  | 0  | Drive head register    | Drive head register     |

| 0    | Х   | 17H   | 0  | 1  | 1  | 1  | Status register        | Command register        |

| 0    | Х   | 37H   | 0  | 1  | 1  | 0  | Alt. status register   | Device control register |

| 0    | Х   | 37H   | 0  | 1  | 1  | 1  | Drive address register | Reserved                |

## True IDE Mode I/O map

| -CE2 | -CE1 | A2 | A1 | A0 | -DMACK | -IORD=L                | -IOWR=L                 |

|------|------|----|----|----|--------|------------------------|-------------------------|

| 1    | 0    | 0  | 0  | 0  | 1      | PIO Data register      | PIO Data register       |

| 1    | 1    | Х  | Х  | Х  | 0      | DMA Data register      | DMA Data register       |

| 1    | 0    | 0  | 0  | 1  | 1      | Error register         | Feature register        |

| 1    | 0    | 0  | 1  | 0  | 1      | Sector count register  | Sector count register   |

| 1    | 0    | 0  | 1  | 1  | 1      | Sector number register | Sector number register  |

| 1    | 0    | 1  | 0  | 0  | 1      | Cylinder low register  | Cylinder low register   |

| 1    | 0    | 1  | 0  | 1  | 1      | Cylinder high register | Cylinder high register  |

| 1    | 0    | 1  | 1  | 0  | 1      | Drive head register    | Drive head register     |

| 1    | 0    | 1  | 1  | 1  | 1      | Status register        | Command register        |

| 0    | 1    | 1  | 1  | 0  | 1      | Alt. status register   | Device control register |

| 0    | 1    | 1  | 1  | 1  | 1      | Drive address register | Reserved                |

#### 1. Data register

This register is a 16-bit register that has read/write ability, and it is used for transferring 1 sector data between the card and the host. This register can be accessed in word mode and byte mode. This register overlaps the Error or Feature register.

| bit15 | bit14     | bit13 | bit12 | bit11 | bit10 | bit9 | bit8 | bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|-----------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

|       | D0 to D15 |       |       |       |       |      |      |      |      |      |      |      |      |      |      |

### 2. Error register

This register is a read only register, and it is used for analyzing the error content at the card accessing. This register is valid when the BSY bit in Status register and Alternate Status register are set to "0" (Ready).

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|------|------|------|------|------|------|------|------|

| BBK  | UNC  | 0    | IDNF | 0    | ABRT | 0    | AMNF |

| bit | Name                                                                                          | Function                                                                                                                             |  |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | 7 BBK(Bad Block detected) This bit is set when a Bad Block is detected in requester ID field. |                                                                                                                                      |  |  |  |  |  |

| 6   | UNC(Data ECC error)                                                                           | This bit is set when Uncorrectable error is occurred at reading the card.                                                            |  |  |  |  |  |

| 4   | IDNF(ID Not Found)                                                                            | The requested sector ID is in error or cannot be found.                                                                              |  |  |  |  |  |

| 2   | ABRT(ABoRTed command)                                                                         | This bit is set if the command has been aborted because of the card status condition.(Not ready, Write fault, Invalid command, etc.) |  |  |  |  |  |