# SPI-4 Exchange Document Issue 1.0

#### Description

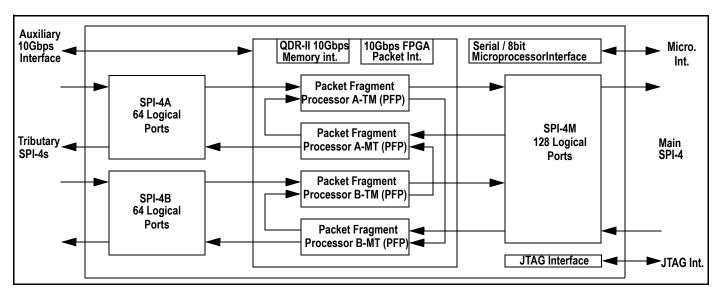

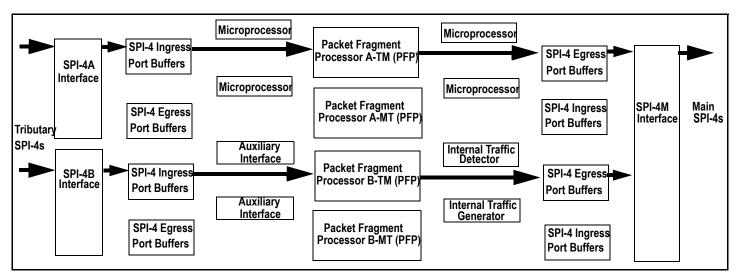

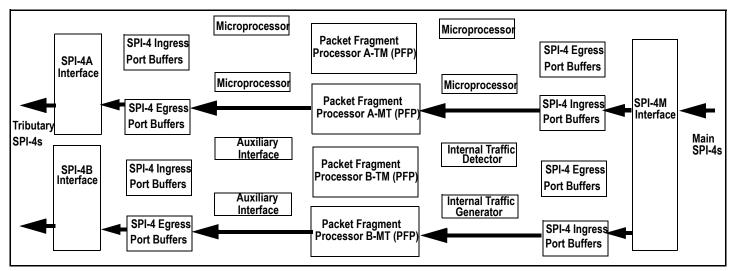

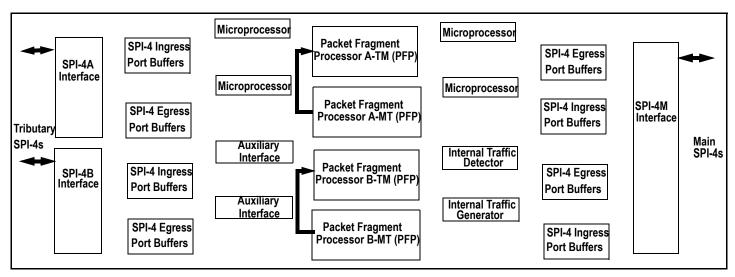

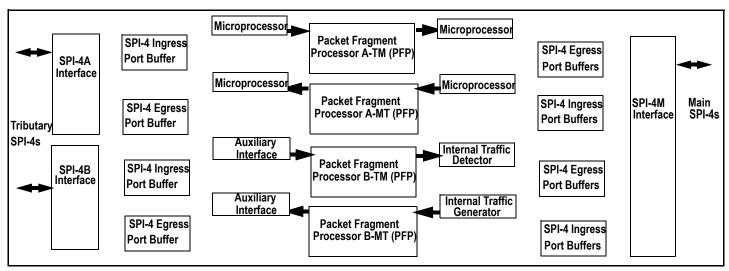

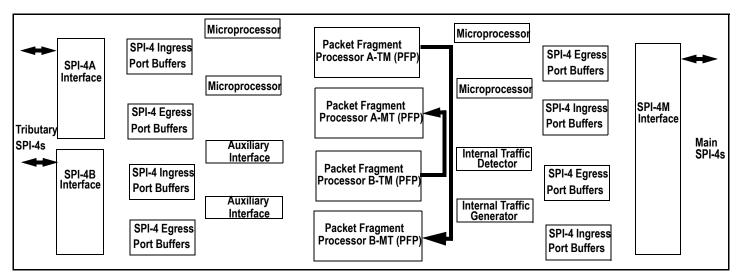

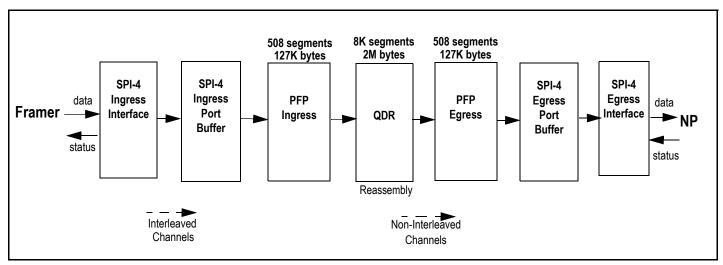

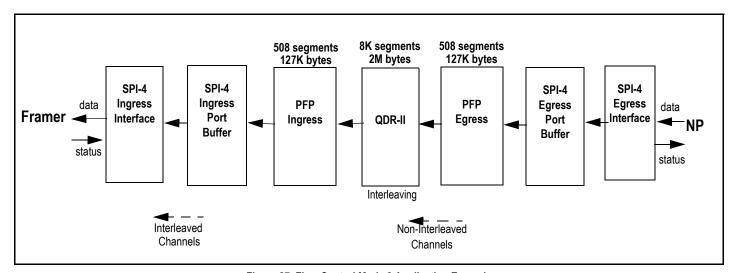

The IDT88K8483 is a 3-port SPI-4 Exchange device. The IDT SPI-4 Exchange devices build on IDT's proven SPI-4 implementation and packet fragment processor (PFP) design. The IDT88K8483 suits applications with slow backpressure response and other advanced networking applications when there is the need for duplicate ports to reroute data multiple times through the packet-exchange and temporary storage for complete in-flight packets.

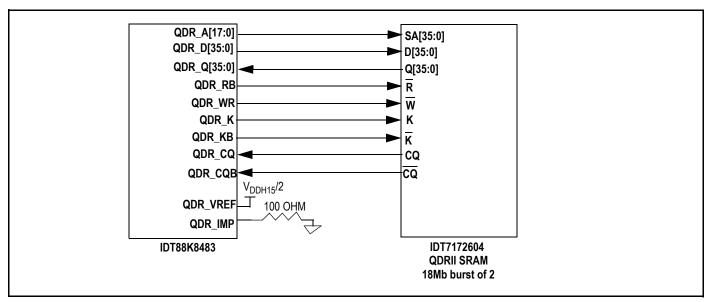

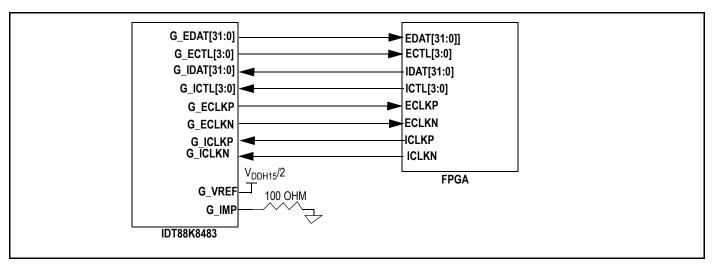

The data on each SPI-4 interface logical port (LP) are mapped to a logical identifier (LID). A data flow between logical port addresses on the various interfaces is accomplished using LID maps that can be dynamically reconfigured. The device enables the connection of two SPI-4 devices to a network processor having one or more SPI-4 interfaces. Up to 18Mbit of additional buffer memory can be provided using the QDRII interface. Alternatively, the HSTL I/O may be used to provide a generic packet interface to a FPGA. The device supports a maximum of 128 logical ports.

#### **Applications**

- Ethernet transport

- SONET / SDH packet transport line cards

- Broadband aggregation

- Multi-service switches

- IP services equipment

- Security firewalls

#### **Features**

#### Functionality

- Multiplexes logical ports (LPs) from SPI-4A and SPI-4B to SPI-4M

- Optionally converts between interleaved packet transfers and whole packet transfers per logical port

- Data redirection per LP between SPI-4A, SPI-4B and 10G FPGA

- Per LP configurable memory allocation

- Per LP memory expansion via QDR-II SRAM interface

- 3 separate clock generators allowing fully flexible, fully integrated clock derivations and generation

#### Standard Interfaces

- Two OIF SPI-4 phase 2: 80 450 MHz, 256 address range, 64 concurrently active LPs per interface

- One OIF SPI-4 phase 2: 80 450 MHz, 256 address range, 128 concurrently active LPs

- SPI-4 FIFO status channel options:

- LVDS full-rate, LVDS quarter-rate, LVTTL quarter-rate

- SPI-4 compatible with Network Processor Streaming Interface (NPSI NPE-Framer mode of operation)

- HSTL Interface with selectable operating mode

160 200 MHz DDR packet interface, 64 concurrently active LPs; or

- QDR-II memory interface: 160 200MHz HSTL

- Serial or parallel microprocessor interface for control and monitoring

- IEEE 1491.1 JTAG

## **Block Diagram**

Figure 1 IDT88K8483 Block Diagram

IDT and the IDT logo are trademarks of Integrated Device Technology, Inc.

1 of 162 October 20, 2006

DSC 6214/-

## **Table Of Contents**

| Description                          | <br>1   |

|--------------------------------------|---------|

| Applications                         | <br>1   |

| Features                             | <br>1   |

| Block Diagram                        | <br>1   |

| Pin Assignment                       | <br>9   |

| Pin Description Table                | <br>28  |

| Functional Description               | <br>33  |

| External Interfaces                  | <br>39  |

| SPI-4 Interface                      | <br>41  |

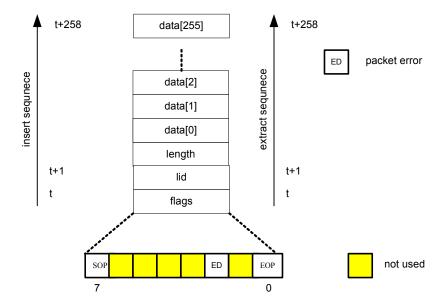

| Insert and Extract paths             | <br>48  |

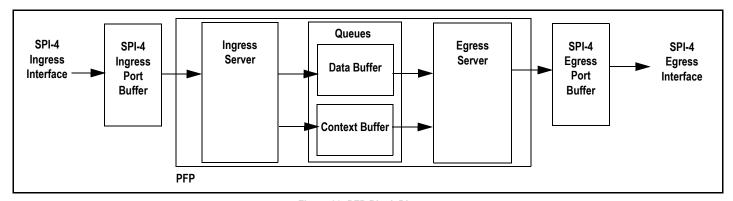

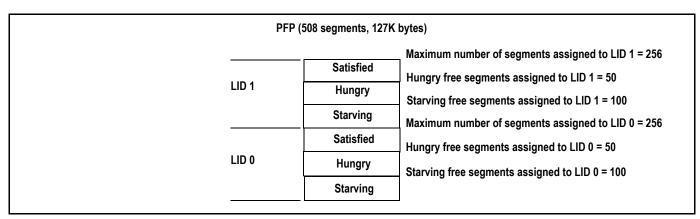

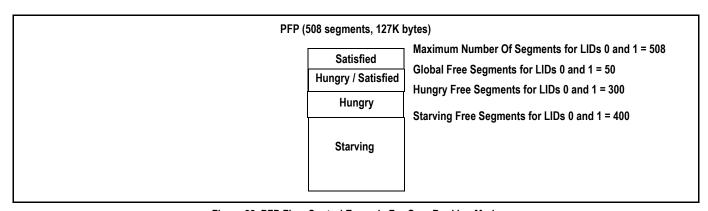

| Packet Fragment Processor (PFP)      | <br>52  |

| QDR-II Interface                     | <br>55  |

| Generic Interface                    | <br>59  |

| Microprocessor Interface             | <br>62  |

| Embedded Processor Download          | <br>62  |

| PMON                                 | <br>65  |

| Clock                                | <br>69  |

| Design Consideration                 | <br>71  |

| Configuration Sequence               | <br>76  |

| Registers                            | <br>77  |

| Register Map                         | <br>80  |

| Direct Registers Description         | <br>90  |

| Indirect Registers Description       | <br>104 |

| Miscellaneous Registers              | <br>145 |

| Electrical and Thermal Specification | <br>147 |

| Mechanical data                      | <br>159 |

| Document Revision History            | <br>160 |

| Ordering Information                 | <br>161 |

# **List of Figures**

| Figure 1.  | IDT88K8483 Block Diagram                                                    |       |

|------------|-----------------------------------------------------------------------------|-------|

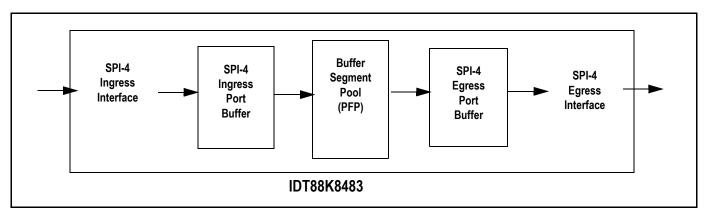

| Figure 2.  | General Data Path                                                           | 33    |

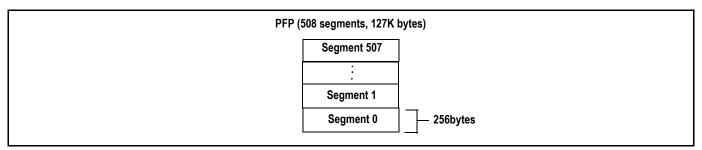

| Figure 3.  | PFP Structure Example                                                       | 34    |

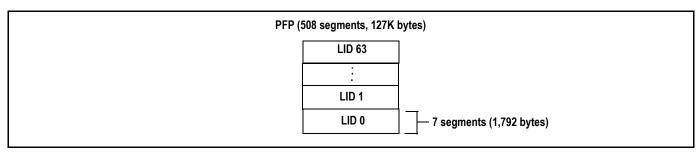

| Figure 4.  | PFP Allocation Example                                                      | 34    |

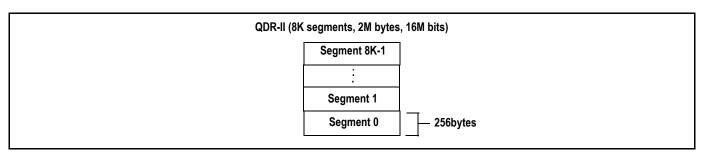

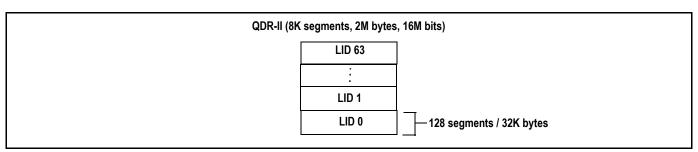

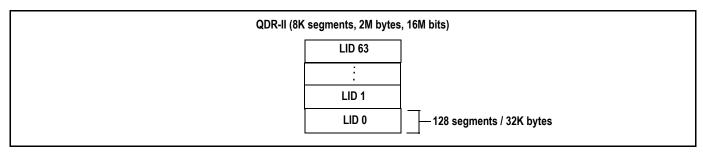

| Figure 5.  | QDR-II SRAM Structure Example                                               | 34    |

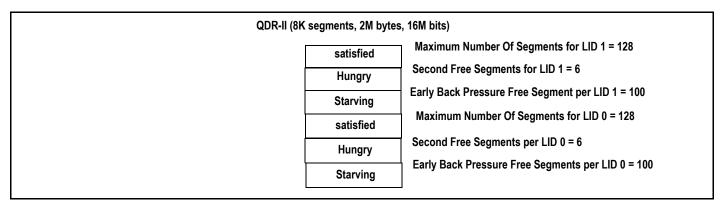

| Figure 6.  | QDR-II Allocation Example                                                   | 34    |

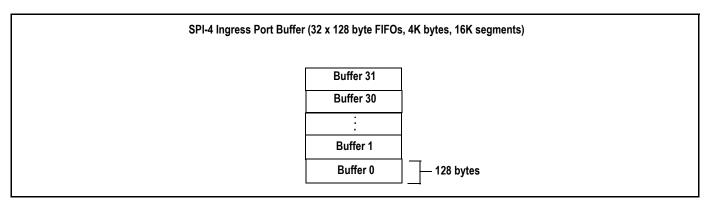

| Figure 7.  | SPI-4 Ingress Port Buffer Structure                                         | 35    |

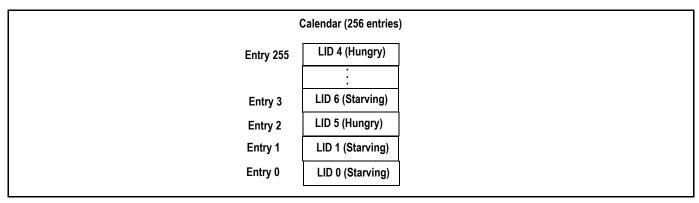

| Figure 8.  | SPI-4 Egress Calendar Example                                               |       |

| Figure 9.  | SPI-4 Tributary to SPI-4 Main Data Path                                     | 36    |

| Figure 10. | SPI-4 main to SPI-4 Tributary Data Path                                     | 37    |

| Figure 11. | PFP Loop Data Path                                                          | 37    |

| Figure 12. | Microprocessor, Auxiliary and Internal Traffic Detector/Generator Data Path | 38    |

|            | PFP Redirect Data Path                                                      |       |

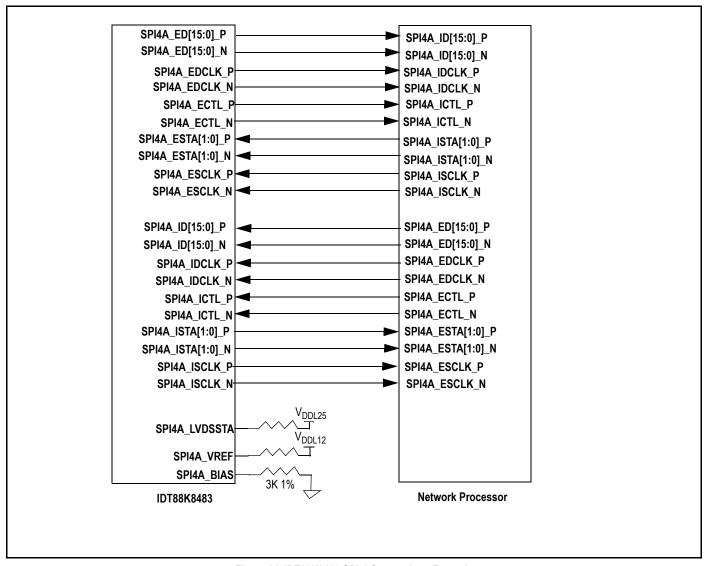

| Figure 14. | IDT88K8483 SPI-4 Connections Example                                        | 42    |

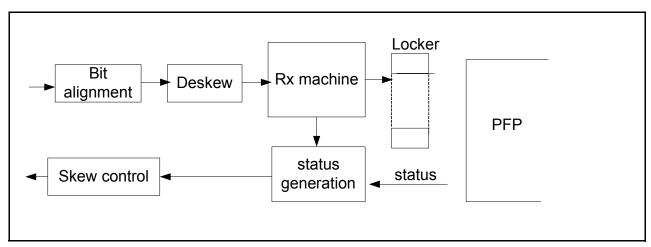

| Figure 15. | SPI-4 Ingress Block Diagram                                                 | 43    |

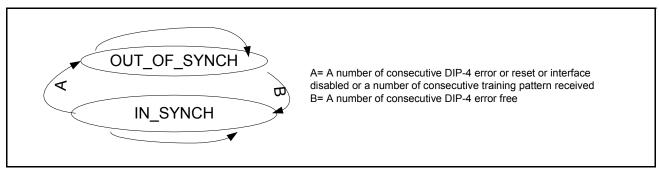

| Figure 16. | SPI-4 Ingress State Machine                                                 | 44    |

| Figure 17. | SPI-4 Egress State Block Diagram                                            | 46    |

|            | Egress word transition state machine                                        |       |

|            | Status Channel State Machine                                                |       |

|            | PFP Block Diagram                                                           |       |

|            | PFP Ingress Flow Control Example                                            |       |

|            | PFP Flow Control Example For Over Booking Mode                              |       |

|            | IDT88K8483 and IDT7172604 QDR-II SRAM connections                           |       |

| Figure 24. | Flow Control Mode 1 Application Example                                     | 57    |

|            | QDR-II FIFOs Allocation Example For Buffering Option                        |       |

|            | QDR-II Flow Control Example For Buffering Option                            |       |

|            | Flow Control Mode 2 Application Example                                     |       |

|            | IDT88K8483 and FPGA connections                                             |       |

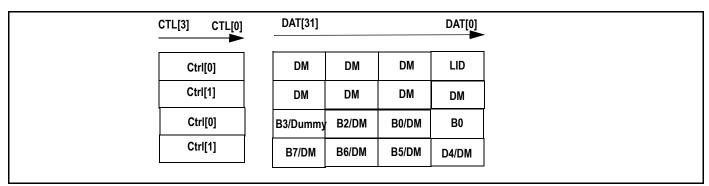

|            | Generic Interface - Transfer Format for Normal Data                         |       |

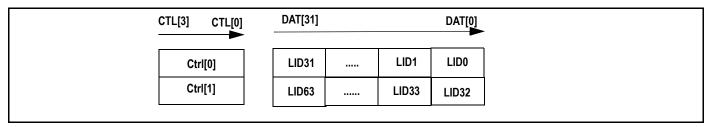

| Figure 30. | Generic Interface - Transfer Format for Stratus Word                        | 60    |

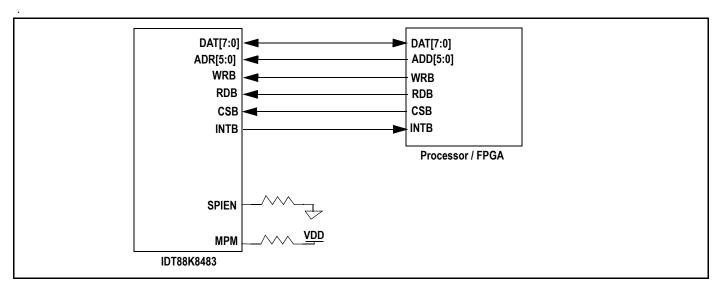

| Figure 31. | Microprocessor Interface - Parallel Mode                                    | 62    |

|            | Interrupt Scheme                                                            |       |

|            | PMON Measure Points                                                         |       |

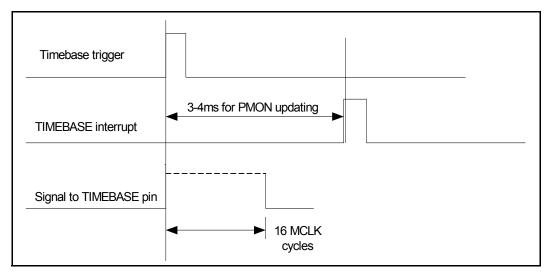

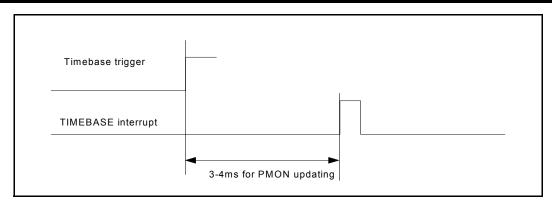

| Figure 34. | Internal PMON Time Base                                                     | 68    |

| Figure 35. | External PMON Time Base                                                     | 69    |

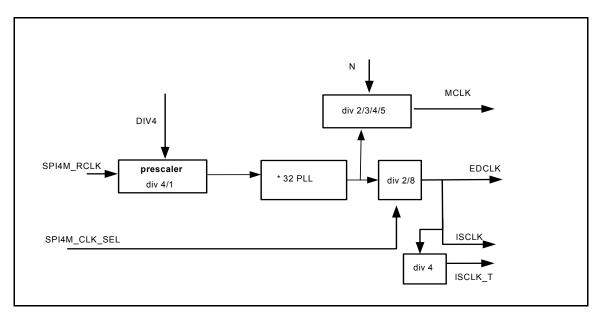

| Figure 36. | Clock Generator Type M                                                      | 70    |

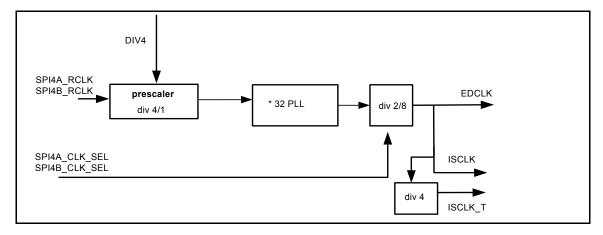

| Figure 37. | Clock Generator Type T                                                      | 70    |

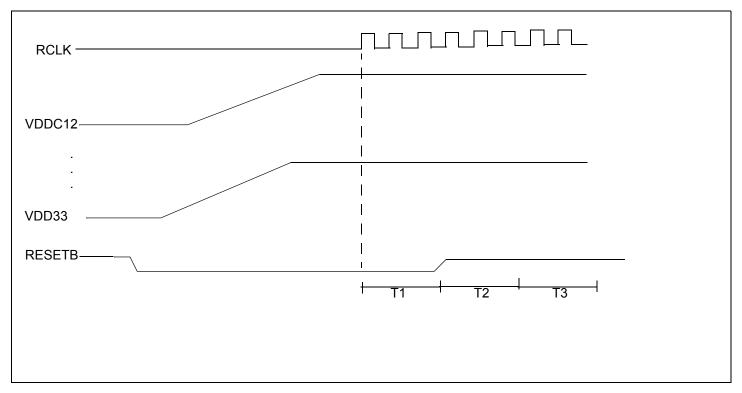

| Figure 38. | Power-on-Reset Sequence                                                     | 71    |

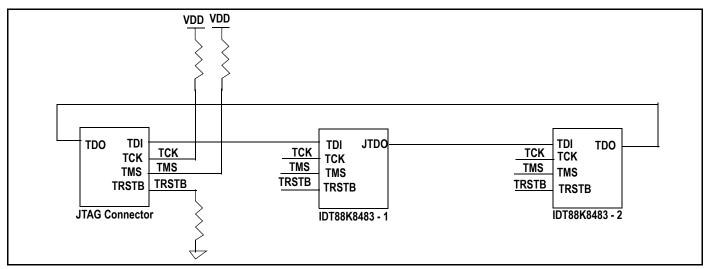

| Figure 39. | JTAG Daisy Chain                                                            | 73    |

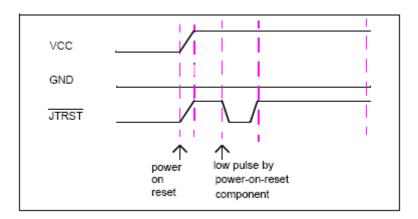

| Figure 40. | TRSTB Signal During Power-On Reset                                          | 73    |

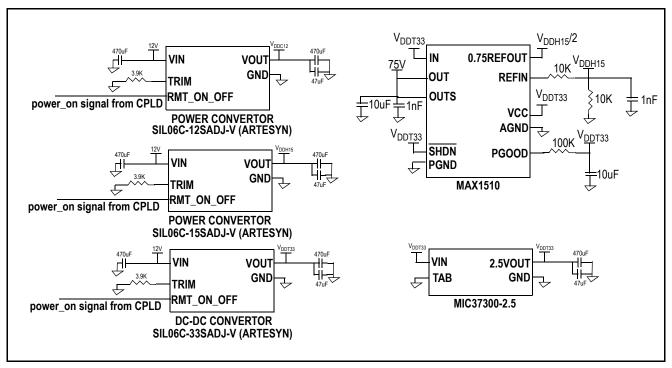

| Figure 41. | IDT88K8483 Power Supply Generation Example                                  | 75    |

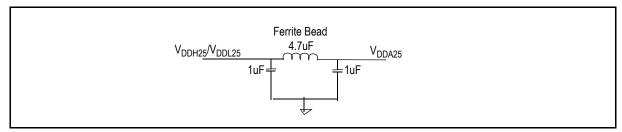

| Figure 42. | IDT88K8483 VDDA25 Filter Circuit                                            | 75    |

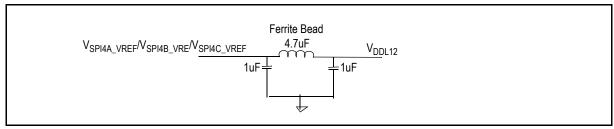

| Figure 43. | IDT88K8483 SPI4x_VREF Filter Circuit                                        | 75    |

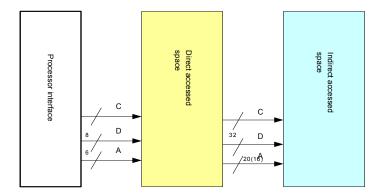

| Figure 44. | Indirect Register Access Scheme                                             | 77    |

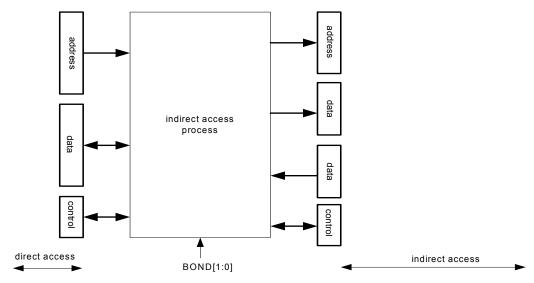

| Figure 45. | Indirect access module                                                      | 79    |

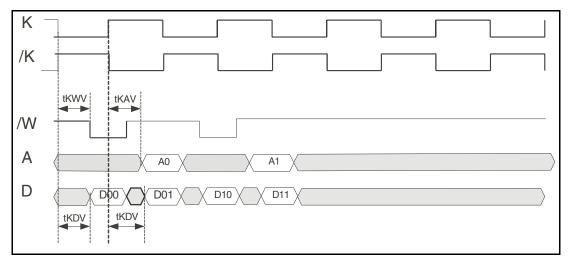

|            | Auxiliary Interface - QDR-II / Generic - Write Access                       |       |

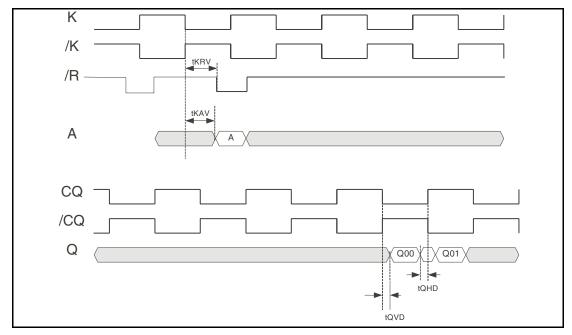

| Figure 47. | Auxiliary Interface - QDR-II / Generic - Read Access                        | . 154 |

|            | MCU Interface - Motorola Mode - Read Access                                 |       |

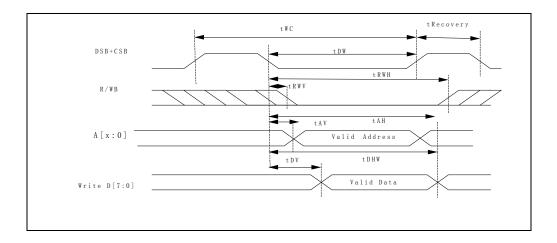

| Figure 49. | MCU Interface - Motorola Mode - Write Access                                | . 155 |

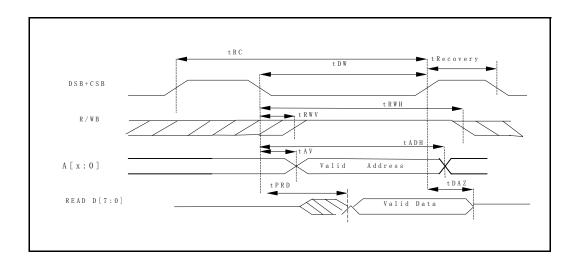

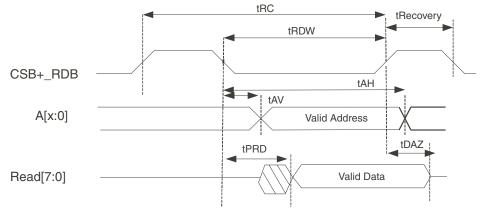

| Figure 50. | MCU Interface - Intel Mode - Read Access                                    | . 156 |

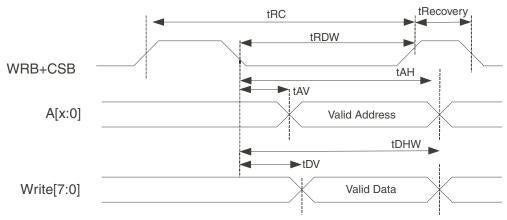

| Figure 51. | MCU Interface - Intel Mode - Write Access                                   | . 156 |

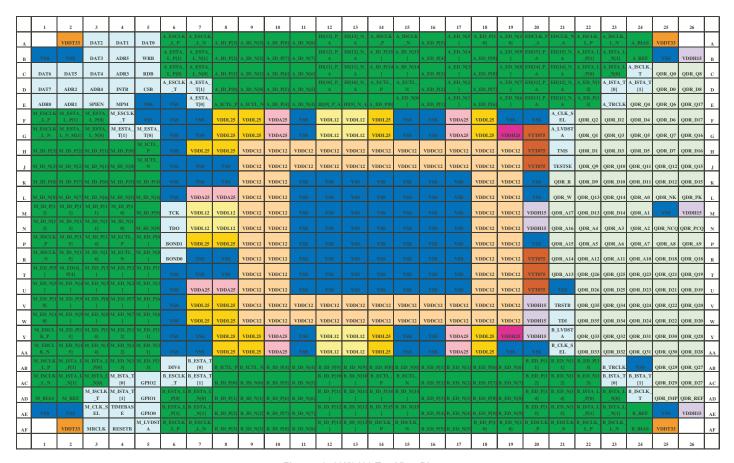

| Figure 52. | 88K8483 Top View Pinout                                                     | . 157 |

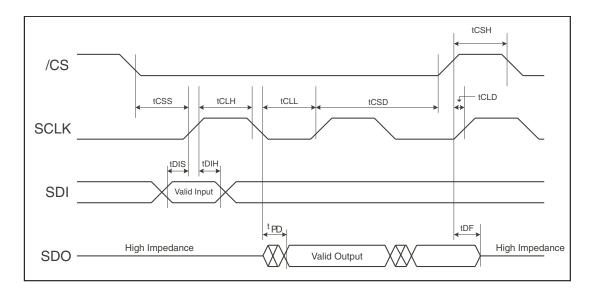

|            | Serial Peripheral Interface                                                 |       |

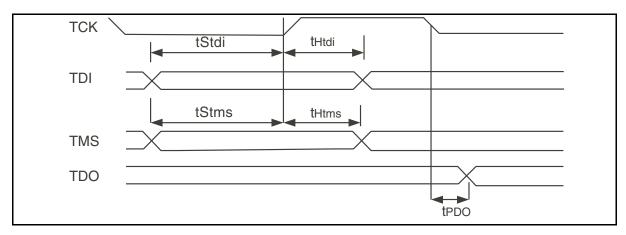

| Figure 54. | JTAG Interface                              | . 158 |

|------------|---------------------------------------------|-------|

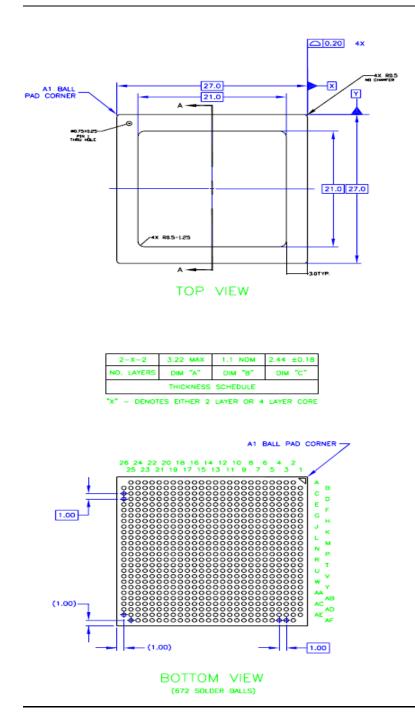

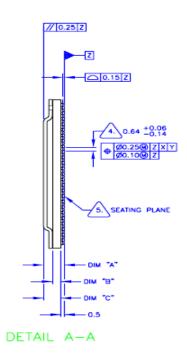

| Figure 55. | BR 672 FCBG Package Outline, RoHS compliant | . 159 |

## **List of Tables**

| Table 1.  | IDT88K8483 Pinout                                                             | 9   |

|-----------|-------------------------------------------------------------------------------|-----|

| Table 2.  | Pin Description                                                               | 28  |

| Table 3.  | SPI-4 Status Information                                                      | 56  |

| Table 4.  | Generic Interface - Control Field Coding                                      | 60  |

| Table 5.  | Field Associated Non-Critical Event List                                      | 65  |

| Table 6.  | Field Associated Critical Event List                                          | 65  |

| Table 7.  | Non Field Associated Event List                                               | 66  |

| Table 8.  | Time Base Source                                                              | 68  |

| Table 9.  | CLK_SEL signals configuration                                                 | 69  |

| Table 10. | DIV4 signal configuration                                                     | 69  |

| Table 11. | JTAG Instruction Code                                                         | 74  |

| Table 12. | JTAG ID                                                                       | 74  |

| Table 13. | Direct Register Table                                                         | 77  |

| Table 14. | Indirect Register Table                                                       |     |

| Table 15. | Direct Registers Map                                                          |     |

| Table 16. | Indirect Registers Map - Segment Base Address                                 |     |

| Table 17. | Indirect Registers Map - Module Base Address                                  |     |

| Table 18. | Indirect Registers Map                                                        |     |

| Table 19. | Global Software Reset Register (Register Offset=0x22)                         |     |

| Table 20. | Microprocessor Mailbox Input FIFO Data Register (Register Offset=0x10)        |     |

| Table 21. | Microprocessor Mailbox Input FIFO Length Register (Register Offset=0x11)      |     |

| Table 22. | Microprocessor Mailbox Input FIFO Status Register (Register Offset=0x14)      |     |

| Table 23. | Microprocessor Mailbox Output FIFO Data Register (Register Offset=0x12)       |     |

| Table 24. | Microprocessor Mailbox Output FIFO Length Register (Register Offset=0x13)     |     |

| Table 25. | Microprocessor Mailbox Input FIFO Status Register (Register Offset=0x15)      |     |

| Table 26. | Embedded Processor State Register (Register Offset=0x16)                      |     |

| Table 27. | Microprocessor Indirect Access Control Register (Register Offset=0x1A)        |     |

| Table 28. | Microprocessor Indirect Access Error Codes                                    |     |

| Table 29. | Microprocessor Indirect Access Data Register -1 (Register Offset=0x1B)        |     |

| Table 30. | Microprocessor Indirect Access Data Register - 2 (Register Offset=0x1C)       |     |

| Table 31. | Microprocessor Indirect Access Data Register - 3 (Register Offset=0x1D)       |     |

| Table 32. | Microprocessor Indirect Access Data Register - 4 (Register Offset=0x1E)       |     |

| Table 33. | Microprocessor Indirect Access Address Register - 1 (Register Offset=0x1F)    |     |

| Table 34. | Microprocessor Indirect Access Address Register - 2 (Register Offset=0x20)    |     |

| Table 35. | Microprocessor Indirect Access Address Register - 3 (Register Offset=0x21)    |     |

| Table 36. | PFP T-M insert control register (Register Offset=0x0)                         |     |

| Table 37. | PFP T-M insert data register (Register Offset=0x1)                            |     |

| Table 38. | PFP T-M extract control register (Register Offset=0x2)                        |     |

| Table 39. | PFP T-M extract data register (Register Offset=0x3)                           |     |

| Table 40. | PFP M-T insert control register (Register Offset=0x4)                         |     |

| Table 41. | PFP M-T insert data register (Register Offset=0x5)                            |     |

| Table 42. | PFP M-T extract control register (Register Offset=0x6)                        |     |

| Table 43. | PFP M-T extract data register (Register Offset=0x7)                           |     |

| Table 44. | Primary Interrupt Indication Register (Register Offset=0x08)                  |     |

| Table 45. | Primary Interrupt Enable Register (Register Offset=0x09)                      |     |

| Table 46. | Secondary Module Indication Register (Register Offset=0x0A.)                  |     |

| Table 47. | Secondary Module Enable Register (Register Offset=0x0B)                       |     |

| Table 48. | Secondary interrupt module B Indication register (Register Offset=0xC)        | 101 |

| Table 49. | Secondary Interrupt module B enable register (Register Offset=0xD)            |     |

| Table 50. | Interrupt secondary COMMON indication register (Register Offset=0xe)          |     |

| Table 51. | Interrupt Secondary COMMON Enable Register (register_offset=0xf)              |     |

| Table 51. | MCLK Divider Sticky Register (Block Base=0x0a00, Register Offset=0x00)        | 104 |

| Table 53  | Clock Control Input Status Register (Block Base=0x0a00, Register Offset=0x01) |     |

| Table 54.  | SPI-4 Ingress LP to LID Mapping Table (Block Base=0x0000, Register Offset=0x00-0xff)          |       |

|------------|-----------------------------------------------------------------------------------------------|-------|

| Table 55.  | SPI-4 Ingress Calendar 0 Table (Block Base=0x0100, Register Offset=0x00-0x3f/0x7f)            |       |

| Table 56.  | Ingress Calendar 1 Table (Block Base=0x0200, Register Offset=0x00-0x3f/0x7f)                  |       |

| Table 57.  | SPI-4 Interface Enable Register (Block Base= 0x0300, Register Offset=0x00)                    |       |

| Table 58.  | SPI-4 Ingress Configuration Register (Block Base=0x0300, Register Offset=0x01)                |       |

| Table 59.  | SPI-4 Ingress Training Parameter Register (Block base=0x0300, Register Offset=0x02)           |       |

| Table 60.  | SPI-4 Ingress Calendar 0 Configuration Register (Block Base=0x0300, Register Offset=0x03)     |       |

| Table 61.  | SPI-4 Ingress Calendar 1 Configuration Register (Block base=0x0300, Register Offset=0x04)     |       |

| Table 62.  | SPI-4 Ingress Status Register (Block base=0x0300, Register Offset=0x05)                       |       |

| Table 63.  | SPI-4 Ingress Diagnostics Register (Block base=0x0300, Register Offset=0x06)                  |       |

| Table 64.  | SPI-4 Ingress Automatic Alignment Control Register (Block base=0x0300, Register Offset=0x07)  |       |

| Table 65.  | SPI-4 Ingress Calendar Switch Control Register (Block base=0x0300, Register Offset=0x08)      |       |

| Table 66.  | Ingress Calendar Switch Register: Bit CAL_SEL                                                 |       |

| Table 67.  | Ingress calendar Switch Register: Bit I_DIP_CSW                                               |       |

| Table 68.  | SPI-4 Ingress Fill Level Register (Block base=0x0300, Register offset=0x0B-0x0C)              |       |

| Table 69.  | SPI-4 Ingress Max Fill Level Register (Block Base=0x0300, Register Offset=0x0D-0x0E           |       |

| Table 70.  | SPI-4 Ingress Watermark Register (Block Base=0x0300, Register Offset=0x0F-0x10)               |       |

| Table 71.  | Ingress Training to out of sync threshold Registe(Block Base=0x0300,Register Offset=0x13)     |       |

| Table 72.  | SPI-4 Egress LID To LP Mapping Table (Block Base=0x0400, Register Offset=0x00-0x3F/0x7F)      |       |

| Table 73.  | SPI-4 Egress Calendar 0 Table (Block Base=0x0500, Register Offset=0x00-0x3F/0x7F)             |       |

| Table 74.  | SPI-4 Egress Calendar 1 Table (Block Base=0x0600, Register Offset=0x00-0x3F/0x7F)             |       |

| Table 75.  | SPI-4 Egress Configuration Register (Block Base=0x0800, Register Offset=0x01)                 |       |

| Table 76.  | SPI-4 Egress Training Parameter Register (Block Base=0x0800, Register Offset=0x02)            |       |

| Table 77.  | SPI-4 Egress Calendar 0 Configuration Register (Block Base=0x0800, Register Offset=0x03)      |       |

| Table 78.  | SPI-4 Egress Calendar 1 Configuration Register (Block Base=0x0800, Register Offset=0x04)      |       |

| Table 79.  | SPI-4 Egress Status Register (Block Base=0x0800, Register Offset=0x05)                        |       |

| Table 80.  | SPI-4 Egress Diagnostics Register (Block Base=0x0800, Register Offset=0x06)                   |       |

| Table 81.  | SPI-4 Egress Automatic Alignment Control Register (Block Base=0x0800, Register Offset=0x07)   |       |

| Table 82.  | SPI-4 Egress Calendar Switch Control Register (Block Base = 0x0800, Register Offset=0x08)     |       |

| Table 83.  | SPI-4 Egress Fill Level Register (Block Base=0x0800, Register Offset = 0x0B and 0x0C)         |       |

| Table 84.  | SPI-4 Egress Max Fill Level Register (Block Base =0x0800, Register Offset = 0x0D and 0x0E)    |       |

| Table 85.  | SPI-4 Histogram Measure Launch Register (Block Base=0x0900 Register Offset=0x00)              |       |

| Table 86.  | SPI-4 Histogram Measure Status Register (Block Base=0x0900 Register Offset=0x01)              |       |

| Table 87.  | SPI-4 Histogram Counter Register (Block Base=0x0900 Register Offset=0x02-0x0B)                |       |

| Table 88.  | SPI-4 Bit Alignment Result Register (Block Base=0x0900 Register Offset=0x0C-0x1E)             |       |

| Table 89.  | SPI-4 Egress Data Lane Timing Control (Block Base=0x0900, Register Offset=0x2A)               |       |

| Table 90.  | SPI-4 Egress Data Control Lane Timing Control (Block Base=0x0900, Register Offset=0x2B)       |       |

| Table 91.  | SPI-4 Egress Data Clock Timing Control (BlockBase=0x0900, Register Offset=0x2C)               |       |

| Table 92.  | SPI-4 Egress Status Timing Control (Block Base=0x0900, Register Offset=0x2D)                  |       |

| Table 93.  | SPI-4 Egress Status Clock Timing Control (Block Base=0x0900, Register Offset=0x2E)            |       |

| Table 94.  | PFP Buffer Segment Assign Table (Block Base=0x01000/0x1800, Register Offset=0x00-0x3F)        |       |

| Table 95.  | PFP Packet Length Thresholds (Block Base=0x1100/0x1900, Register Offset=0x00-03F)             |       |

| Table 96.  | PFP Queue Diagnose Table (Block Base=0x1200/0x1A00, Register Offset=0x00-0x3F)                |       |

| Table 97.  | PFP Packet Diagnose Table (Block Base=0x1300/0x1B00, Register Offset=0x00-03F)                |       |

| Table 98.  | PFP Egress Burst Size Table (Block Base=0x1400/0x1C00, Register Offset=0x00-0x3F)             |       |

| Table 99.  | PFP Egress Weight And Direction Register (Block Base=0x1500/0x1D00, Register Offset=0x00-03F) |       |

|            | PFP Egress Packet Mode Control Register (Block Base=0x1600/0x1E00, Register Offset=0x00-0x3F) |       |

|            | PFP Link Number Configuration Register (Block Base=0x1700/0x1F00, Register Offset=0x00)       |       |

|            | PFP Buffer Management Configuration Register (Block Base=0x1700/0x1F00, Register Offset=0x01) |       |

|            | PFP Queue Weighting Enable Register (Block Base=0x1700/0x1F00, Register Offset=0x02)          |       |

|            | PFP Flow Control Register (Block Base=0x1700/0x1F00, Register Offset=0x03)                    |       |

|            | PFP Test Register (Block Base=0x1700/0x1F00, Register Offset=0x04)                            |       |

|            | PFP Ingress Status Monitor Register - 1 (Block Base=0x1700/0x1F00, Register Offset=0x05)      |       |

| rable 107. | PFP Ingress Status Monitor Register - 2 (Block Base=0x1700/0x1F00, Register Offset=0x06)      | . 120 |

|            | PFP Ingress Status Monitor Register - 3 (Block Base=0x1700/0x1F00, Register Offset=0x07)           |     |

|------------|----------------------------------------------------------------------------------------------------|-----|

|            | PFP Ingress Status Monitor Register - 4 (Block Base=0x1700/0x1F00, Register Offset=0x08)           |     |

|            | PFP Egress Status Monitor Register - 1 (Block Base=0x1700/0x1F00, Register Offset=0x09)            |     |

|            | PFP Egress Status Monitor Register - 2 (Block Base=0x1700/0x1F00, Register Offset=0x0A)            |     |

|            | PFP Egress Status Monitor Register - 3 (Block Base=0x1700/0x1F00, Register Offset=0x0B)            |     |

|            | PFP Egress Status Monitor Register - 4 (Block Base=0x1700/0x1F00, Register Offset=0x0C)            |     |

| Table 114. | PFP Internal Parity Error Indication Register (Block Base=0x1700/0x1F00, Register Offset=0x0D)     | 127 |

| Table 115. | PFP Maximum Packet Length Register (Block Base=0x1700/0x1F00, Register Offset=0x0E)                | 128 |

| Table 116. | Auxiliary Interface Enable Register (Block Base=0x0A00, Register Offset=0x00)                      | 129 |

| Table 117. | Auxiliary Interface Configuration Register (Block Base=0x0A00, Register Offset=0x01)               | 129 |

| Table 118. | Auxiliary Extension Buffer Configuration Register (Block Base=0x0A00, Register Offset=0x02)        | 129 |

|            | Auxiliary Clock Monitor Status Register (Block Base=0x0A00, Register Offset=0x03)                  |     |

| Table 121. | External Memory Test Control Register (Block Base=0x0A00, Register Offset=0x04)                    | 130 |

|            | External Memory Segmentation                                                                       |     |

| Table 122. | External Memory Test Results Register (Block Base=0x0A00, Register Offset=0x05)                    | 131 |

| Table 123. | Auxiliary Early Backpressure Threshold Register (Block Base=0x0A00, Register Offset=0x07)          | 131 |

|            | Auxiliary Packet Mode Configuration Register (Block Base=0x0A00, Register Offset=0x08)             |     |

|            | Auxiliary HSTL Receiver Test Control Register (Block Base=0x0A00, Register Offset=0x0E)            |     |

|            | Auxiliary Automatic Impedance Matching Control Register (Block Base=0x0A00, Register Offset=0x0F)  |     |

|            | Auxiliary Synchronization Status Register (Block Base=0x0A00, Register Offset=0x12)                |     |

| Table 128. | Auxiliary Initialization Control Register (Block Base=0x0A00, Register Offset=0x013)               | 133 |

|            | Enable Control Register (Block Base=0x0B00, Register Offset=0x00)                                  |     |

|            | Feedback Configuration Register (Block Base=0x0B00, Register Offset=0x01)                          |     |

|            | Bandwidth Control Register (Block Base=0x0B00, Register Offset=0x02)                               |     |

|            | Bandwidth level as per field BW                                                                    |     |

|            | Packet Length Register (Block Base=0x0B00, Register Offset=0x03)                                   |     |

| Table 134. | Burst Size Register (Block Base=0x0B00, Register Offset=0x04)                                      | 134 |

| Table 135. | Random Control Register (Block Base=0x0B00, Register Offset=0x05)                                  | 134 |

| Table 136. | LID Register (Block Base=0x0B00, Register Offset=0x06)                                             | 135 |

|            | Synchronization Register (Block Base=0x0B00, Register Offset=0x07)                                 |     |

|            | Bit Error Insertion Register (Block Base=0x0B00, Register Offset=0x08)                             |     |

|            | PMON Event Interrupt Indication Register (Block Base=0x0F00, Register Offset=0x00)                 |     |

|            | PMON Event Interrupt Enable Register (Block Base=0x0F00, Register Offset=0x01)                     |     |

|            | PMON Buffer T-M Overflow Indication Register (Block Base=0x0F00, Register Offset=0x02-0x03)        |     |

|            | PMON Buffer M-T Overflow Indication Register (Block Base=0x0F00, Register Offset=0x04-0x05)        |     |

|            | PMON Buffer T-M Overflow Interrupt Control Register (Block Base=0x0F00, Register Offset=0x06-0x07) |     |

|            | PMON Buffer M-T Overflow Interrupt Control Register (Block Base=0x0F00, Register Offset=0x08-0x09) |     |

|            | PMON Buffer Overflow Source Register (Block Base=0x0F00, Register Offset=0x0A)                     |     |

|            | PMON T-M Inactive Transfer LP Field Register (Block Base=0x0F00, Register Offset=0x0B)             |     |

|            | PMON M-T Inactive Transfer LP Field Register (Block Base=0x0F00, Register Offset=0x0C)             |     |

|            | PMON T-M Illegal SOP Event Field Register (Block Base=0x0F00, Register Offset=0x0D)                |     |

|            | PMON T-M Illegal EOP Event Field Register (Block Base=0x0F00, Register Offset=0x0E)                |     |

|            | PMON M-T Illegal SOP Event Field Register (Block Base=0x0F00, Register Offset=0x0F)                |     |

|            | PMON M-T Illegal EOP Event Field Register (Block Base=0x0F00, Register Offset=0x10)                |     |

|            | PMON T-M Packet Cut-Down LID Field Register (Block Base=0x0F00, Register Offset=0x11)              |     |

|            | PMON M-T Packet Cut-Down LID Field Register (Block Base=0x0F00, Register Offset=0x12)              |     |

|            | PMON Per LID Counter Table (Block Base=0x0C00, Register Offset=0x00-0x17F)                         |     |

|            | PMON Per Module/Interface Counter Table (Block Base=0x0E00 Register Offset=0x00-0x10               |     |

|            | PMON Timebase Control Register (Block Base=0x8B00, Register Offset=0x00)                           |     |

|            | Timebase source table                                                                              |     |

|            | PMON 1ms Timer Register (Block Base=0x8B00, Register Offset=0x01)                                  |     |

|            | GPIO Direction Register (Block Base=0x8B00, Register Offset=0x10-0x12)                             |     |

|            | GPIO Level Register (Block Base=0x8B00, Register Offset=0x13-0x15)                                 |     |

| Table 161. | GPIO Link Table (Block Base=0x8B00, Register Offset=0x16-0x18)                                     | 146 |

| Table 162. | Version Number Register (Block Base=0x8B00, Register Offset=0x30) | 146 |

|------------|-------------------------------------------------------------------|-----|

| Table 163. | Version Number Register (Block Base=0x8B00, Register Offset=0x32) | 146 |

| Table 164. | Absolute Maximum Ratings                                          | 147 |

| Table 165. | Recommended Operating Conditions                                  | 147 |

| Table 166. | Thermal Characteristics                                           | 148 |

| Table 167. | DC Characteristics                                                | 149 |

| Table 168. | AC Characteristics                                                | 150 |

| Table 169. | Document Revision History                                         | 160 |

| Table 170  | Ordering Information                                              | 161 |

## **Pin Assignment**

The following table shows the IDT88K8483 pins and their corresponding symbols.

| Function | Pin |

|----------|-----|

| ADR0     | E1  |

| ADR1     | E2  |

| ADR2     | D2  |

| ADR3     | C4  |

| ADR4     | D3  |

| ADR5     | B4  |

| BOND0    | R6  |

| BOND1    | P6  |

| CSB      | D5  |

| DAT0     | A5  |

| DAT1     | A4  |

| DAT2     | A3  |

| DAT3     | B3  |

| DAT4     | C3  |

| DAT5     | C2  |

| DAT6     | C1  |

| DAT7     | D1  |

| DIV4     | AB6 |

| GPIO0    | AE5 |

| GPIO1    | AD5 |

| GPIO2    | AC5 |

| INTB     | D4  |

| MPM      | E4  |

| QDR_A0   | L24 |

| QDR_A1   | M24 |

| QDR_A10  | R24 |

| QDR_A11  | R23 |

| QDR_A12  | R22 |

| QDR_A13  | T21 |

| QDR_A14  | R21 |

| QDR_A15  | P21 |

| QDR_A16  | N21 |

| QDR_A17  | M21 |

| QDR_A2   | N24 |

Table 1 IDT88K8483 Pinout (Part 1 of 19)

9 of 162

October 20, 2006

| Function | Pin  |

|----------|------|

| QDR_A3   | N23  |

| QDR_A4   | N22  |

| QDR_A5   | P22  |

| QDR_A6   | P23  |

| QDR_A7   | P24  |

| QDR_A8   | P25  |

| QDR_A9   | P26  |

| QDR_CQ   | N26  |

| QDR_CQB  | N25  |

| QDR_D0   | D25  |

| QDR_D1   | H22  |

| QDR_D10  | K23  |

| QDR_D11  | K24  |

| QDR_D12  | K25  |

| QDR_D13  | M22  |

| QDR_D14  | M23  |

| QDR_D15  | K26  |

| QDR_D16  | H26  |

| QDR_D17  | F26  |

| QDR_D18  | R25  |

| QDR_D19  | U26  |

| QDR_D2   | F23  |

| QDR_D20  | W26  |

| QDR_D21  | U25  |

| QDR_D22  | W25  |

| QDR_D23  | U24  |

| QDR_D24  | W24  |

| QDR_D25  | U23  |

| QDR_D26  | U22  |

| QDR_D27  | AC26 |

| QDR_D28  | AA26 |

| QDR_D29  | AC25 |

| QDR_D3   | H23  |

| QDR_D30  | Y25  |

| QDR_D31  | Y24  |

| QDR_D32  | AA23 |

| QDR_D33  | AA22 |

Table 1 IDT88K8483 Pinout (Part 2 of 19)

| Function | Pin  |

|----------|------|

| QDR_D34  | W23  |

| QDR_D35  | W22  |

| QDR_D4   | F24  |

| QDR_D5   | H24  |

| QDR_D6   | F25  |

| QDR_D7   | H25  |

| QDR_D8   | D26  |

| QDR_D9   | K22  |

| QDR_IMP  | AD25 |

| QDR_K    | L26  |

| QDR_KB   | L25  |

| QDR_Q0   | C25  |

| QDR_Q1   | G22  |

| QDR_Q10  | J23  |

| QDR_Q11  | J24  |

| QDR_Q12  | J25  |

| QDR_Q13  | L22  |

| QDR_Q14  | L23  |

| QDR_Q15  | J26  |

| QDR_Q16  | G26  |

| QDR_Q17  | E26  |

| QDR_Q18  | R26  |

| QDR_Q19  | T26  |

| QDR_Q2   | F22  |

| QDR_Q20  | V26  |

| QDR_Q21  | T25  |

| QDR_Q22  | V25  |

| QDR_Q23  | T24  |

| QDR_Q24  | V24  |

| QDR_Q25  | T23  |

| QDR_Q26  | T22  |

| QDR_Q27  | AB26 |

| QDR_Q28  | Y26  |

| QDR_Q29  | AB25 |

| QDR_Q3   | G23  |

| QDR_Q30  | AA25 |

| QDR_Q31  | AA24 |

Table 1 IDT88K8483 Pinout (Part 3 of 19)

| Function           | Pin  |

|--------------------|------|

| QDR_Q32            | Y23  |

| QDR_Q33            | Y22  |

| QDR_Q34            | V23  |

| QDR_Q35            | V22  |

| QDR_Q4             | E24  |

| QDR_Q5             | G24  |

| QDR_Q6             | E25  |

| QDR_Q7             | G25  |

| QDR_Q8             | C26  |

| QDR_Q9             | J22  |

| QDR_RB             | K21  |

| QDR_VREF           | AD26 |

| QDR_WB             | L21  |

| RDB                | C5   |

| RESETB             | AF4  |

| SPI4A_BIAS         | A24  |

| SPI4A_CLK_SEL      | F21  |

| SPI4A_ECTL_N       | D15  |

| SPI4A_ECTL_P       | D14  |

| SPI4A_ED[0]_N      | E15  |

| SPI4A_ED[0]_P      | E14  |

| SPI4A_ED[1]_N      | E17  |

| SPI4A_ED[1]_P      | E16  |

| SPI4A_ED[10]_N     | A19  |

| SPI4A_ED[10_P      | A18  |

| SPI4A_ED[11]_N     | E21  |

| SPI4A_ED[11]_P     | E20  |

| SPI4A_ED[12]_N     | D21  |

| SPI4A_ED[12]_P     | D20  |

| SPI4A_ED[13]_N     | D22  |

| SPI4A_ED[13]_P     | E22  |

| SPI4A_ED[14]_N     | C21  |

| SPI4A_ED[14]_P     | C20  |

| SPI4A_ED[15]_N     | B21  |

| SPI4A_ED[15]_P     | B20  |

| SPI4A_ED[2]_N      | D17  |

| SPI4A_ED[2]_P      | D16  |

| Table 4 IDT00V0402 |      |

Table 1 IDT88K8483 Pinout (Part 4 of 19)

| Function           | Pin |

|--------------------|-----|

| SPI4A_ED[3]_N      | C17 |

| SPI4A_ED[3]_P      | C16 |

| SPI4A_ED[4]_N      | B17 |

| SPI4A_ED[4]_P      | B16 |

| SPI4A_ED[5]_N      | A17 |

| SPI4A_ED[5]_P      | A16 |

| SPI4A_ED[6]_N      | E19 |

| SPI4A_ED[6]_P      | E18 |

| SPI4A_ED[7]_N      | D19 |

| SPI4A_ED[7]_P      | D18 |

| SPI4A_ED[8]_N      | C19 |

| SPI4A_ED[8]_P      | C18 |

| SPI4A_ED[9]_N      | B19 |

| SPI4A_ED[9]_P      | B18 |

| SPI4A_EDCLK_N      | A21 |

| SPI4A_EDCLK_P      | A20 |

| SPI4A_ESCLK_N      | A7  |

| SPI4A_ESCLK_P      | A6  |

| SPI4A_ESCLK_T      | D6  |

| SPI4A_ESTA[0]_N    | C7  |

| SPI4A_ESTA[0]_P    | C6  |

| SPI4A_ESTA[1]_N    | B7  |

| SPI4A_ESTA[1]_P    | B6  |

| SPI4A_ESTA_T0      | E7  |

| SPI4A_ESTA_T1      | D7  |

| SPI4A_ICTL_N       | E9  |

| SPI4A_ICTL_P       | E8  |

| SPI4A_ID[0]_N      | D9  |

| SPI4A_ID[0]_P      | D8  |

| SPI4A_ID[1]_N      | C9  |

| SPI4A_ID[1]_P      | C8  |

| SPI4A_ID[10]_N     | D13 |

| SPI4A_ID[10]_P     | D12 |

| SPI4A_ID[11]_N     | C13 |

| SPI4A_ID[11]_P     | C12 |

| SPI4A_ID[12]_N     | B13 |

| SPI4A_ID[12]_P     | B12 |

| Table 4 IDT00K0402 |     |

Table 1 IDT88K8483 Pinout (Part 5 of 19)

| Function        | Pin  |

|-----------------|------|

| SPI4A_ID[13]_N  | A13  |

| SPI4A_ID[13]_P  | A12  |

| SPI4A_ID[14]_N  | C15  |

| SPI4A_ID[14]_P  | C14  |

| SPI4A_ID[15]_N  | B15  |

| SPI4A_ID[15]_P  | B14  |

| SPI4A_ID[2]_N   | B9   |

| SPI4A_ID[2]_P   | B8   |

| SPI4A_ID[3]_N   | A9   |

| SPI4A_ID[3]_P   | A8   |

| SPI4A_ID[4]_N   | E11  |

| SPI4A_ID[4]_P   | E10  |

| SPI4A_ID[5]_N   | D11  |

| SPI4A_ID[5]_P   | D10  |

| SPI4A_ID[6]_N   | C11  |

| SPI4A_ID[6]_P   | C10  |

| SPI4A_ID[7]_N   | B11  |

| SPI4A_ID[7]_P   | B10  |

| SPI4A_ID[8]_N   | A11  |

| SPI4A_ID[8]_P   | A10  |

| SPI4A_ID[9]_N   | E13  |

| SPI4A_ID[9]_P   | E12  |

| SPI4A_IDCLK_N   | A15  |

| SPI4A_IDCLK_P   | A14  |

| SPI4A_ISCLK_N   | A23  |

| SPI4A_ISCLK_P   | A22  |

| SPI4A_ISCLK_T   | C24  |

| SPI4A_ISTA[0]_N | C23  |

| SPI4A_ISTA[0]_P | C22  |

| SPI4A_ISTA[1]_N | B23  |

| SPI4A_ISTA[1]_P | B22  |

| SPI4A_ISTA_T0   | D23  |

| SPI4A_ISTA_T1   | D24  |

| SPI4A_LVDSSTA   | G21  |

| SPI4A_RCLK      | E23  |

| SPI4A_VREF      | B24  |

| SPI4B_BIAS      | AF24 |

Table 1 IDT88K8483 Pinout (Part 6 of 19)

| Function       | Pin  |

|----------------|------|

| SPI4B_CLK_SEL  | AA21 |

| SPI4B_ECTL_N   | AC15 |

| SPI4B_ECTL_P   | AC14 |

| SPI4B_ED[0]_N  | AB15 |

| SPI4B_ED[0]_P  | AB14 |

| SPI4B_ED[1]_N  | AB17 |

| SPI4B_ED[1]_P  | AB16 |

| SPI4B_ED[10]_N | AF19 |

| SPI4B_ED[10_P  | AF18 |

| SPI4B_ED[11]_N | AB21 |

| SPI4B_ED[11]_P | AB20 |

| SPI4B_ED[12]_N | AC21 |

| SPI4B_ED[12]_P | AC20 |

| SPI4B_ED[13]_N | AC22 |

| SPI4B_ED[13]_P | AB22 |

| SPI4B_ED[14]_N | AD21 |

| SPI4B_ED[14]_P | AD20 |

| SPI4B_ED[15]_N | AE21 |

| SPI4B_ED[15]_P | AE20 |

| SPI4B_ED[2]_N  | AC17 |

| SPI4B_ED[2]_P  | AC16 |

| SPI4B_ED[3]_N  | AD17 |

| SPI4B_ED[3]_P  | AD16 |

| SPI4B_ED[4]_N  | AE17 |

| SPI4B_ED[4]_P  | AE16 |

| SPI4B_ED[5]_N  | AF17 |

| SPI4B_ED[5]_P  | AF16 |

| SPI4B_ED[6]_N  | AB19 |

| SPI4B_ED[6]_P  | AB18 |

| SPI4B_ED[7]_N  | AC19 |

| SPI4B_ED[7]_P  | AC18 |

| SPI4B_ED[8]_N  | AD19 |

| SPI4B_ED[8]_P  | AD18 |

| SPI4B_ED[9]_N  | AE19 |

| SPI4B_ED[9]_P  | AE18 |

| SPI4B_EDCLK_N  | AF21 |

| SPI4B_EDCLK_P  | AF20 |

Table 1 IDT88K8483 Pinout (Part 7 of 19)

| Function        | Pin  |

|-----------------|------|

| SPI4B_ESCLK_N   | AF7  |

| SPI4B_ESCLK_P   | AF6  |

| SPI4B_ESCLK_T   | AC6  |

| SPI4B_ESTA[0]_N | AD7  |

| SPI4B_ESTA[0]_P | AD6  |

| SPI4B_ESTA[1]_N | AE7  |

| SPI4B_ESTA[1]_P | AE6  |

| SPI4B_ESTA_T0   | AB7  |

| SPI4B_ESTA_T1   | AC7  |

| SPI4B_ICTL_N    | AB9  |

| SPI4B_ICTL_P    | AB8  |

| SPI4B_ID[0]_N   | AC9  |

| SPI4B_ID[0]_P   | AC8  |

| SPI4B_ID[1]_N   | AD9  |

| SPI4B_ID[1]_P   | AD8  |

| SPI4B_ID[10]_N  | AC13 |

| SPI4B_ID[10]_P  | AC12 |

| SPI4B_ID[11]_N  | AD13 |

| SPI4B_ID[11]_P  | AD12 |

| SPI4B_ID[12]_N  | AE13 |

| SPI4B_ID[12]_P  | AE12 |

| SPI4B_ID[13]_N  | AF13 |

| SPI4B_ID[13]_P  | AF12 |

| SPI4B_ID[14]_N  | AD15 |

| SPI4B_ID[14]_P  | AD14 |

| SPI4B_ID[15]_N  | AE15 |

| SPI4B_ID[15]_P  | AE14 |

| SPI4B_ID[2]_N   | AE9  |

| SPI4B_ID[2]_P   | AE8  |

| SPI4B_ID[3]_N   | AF9  |

| SPI4B_ID[3]_P   | AF8  |

| SPI4B_ID[4]_N   | AB11 |

| SPI4B_ID[4]_P   | AB10 |

| SPI4B_ID[5]_N   | AC11 |

| SPI4B_ID[5]_P   | AC10 |

| SPI4B_ID[6]_N   | AD11 |

| SPI4B_ID[6]_P   | AD10 |

Table 1 IDT88K8483 Pinout (Part 8 of 19)

| Function        | Pin  |

|-----------------|------|

| SPI4B_ID[7]_N   | AE11 |

| SPI4B_ID[7]_P   | AE10 |

| SPI4B_ID[8]_N   | AF11 |

| SPI4B_ID[8]_P   | AF10 |

| SPI4B_ID[9]_N   | AB13 |

| SPI4B_ID[9]_P   | AB12 |

| SPI4B_IDCLK_N   | AF15 |

| SPI4B_IDCLK_P   | AF14 |

| SPI4B_ISCLK_N   | AF23 |

| SPI4B_ISCLK_P   | AF22 |

| SPI4B_ISCLK_T   | AD24 |

| SPI4B_ISTA[0]_N | AD23 |

| SPI4B_ISTA[0]_P | AD22 |

| SPI4B_ISTA[1]_N | AE23 |

| SPI4B_ISTA[1]_P | AE22 |

| SPI4B_ISTA_T0   | AC23 |

| SPI4B_ISTA_T1   | AC24 |

| SPI4B_LVDSTA    | Y21  |

| SPI4B_RCLK      | AB23 |

| SPI4B_VREF      | AE24 |

| SPI4M_BIAS      | AD1  |

| SPI4M_CLK_SEL   | AE3  |

| SPI4M_ECTL_N    | R4   |

| SPI4M_ECTL_P    | P4   |

| SPI4M_ED[0]_N   | R5   |

| SPI4M_ED[0]_P   | P5   |

| SPI4M_ED[1]_N   | U5   |

| SPI4M_ED[1]_P   | T5   |

| SPI4M_ED[10]_N  | W1   |

| SPI4M_ED[10_P   | V1   |

| SPI4M_ED[11]_N  | AA5  |

| SPI4M_ED[11]_P  | Y5   |

| SPI4M_ED[12]_N  | AA4  |

| SPI4M_ED[12]_P  | Y4   |

| SPI4M_ED[13]_N  | AB4  |

| SPI4M_ED[13]_P  | AB5  |

| SPI4M_ED[14]_N  | AA3  |

Table 1 IDT88K8483 Pinout (Part 9 of 19)

| Function        | Pin |

|-----------------|-----|

| SPI4M_ED[14]_P  | Y3  |

| SPI4M_ED[15]_N  | AA2 |

| SPI4M_ED[15]_P  | Y2  |

| SPI4M_ED[2]_N   | U4  |

| SPI4M_ED[2]_P   | T4  |

| SPI4M_ED[3]_N   | U3  |

| SPI4M_ED[3]_P   | Т3  |

| SPI4M_ED[4]_N   | U2  |

| SPI4M_ED[4]_P   | T2  |

| SPI4M_ED[5]_N   | U1  |

| SPI4M_ED[5]_P   | T1  |

| SPI4M_ED[6]_N   | W5  |

| SPI4M_ED[6]_P   | V5  |

| SPI4M_ED[7]_N   | W4  |

| SPI4M_ED[7]_P   | V4  |

| SPI4M_ED[8]_N   | W3  |

| SPI4M_ED[8]_P   | V3  |

| SPI4M_ED[9]_N   | W2  |

| SPI4M_ED[9]_P   | V2  |

| SPI4M_EDCLK_N   | AA1 |

| SPI4M_EDCLK_P   | Y1  |

| SPI4M_ESCLK_N   | G1  |

| SPI4M_ESCLK_P   | F1  |

| SPI4M_ESCLK_T   | F4  |

| SPI4M_ESTA[0]_N | G3  |

| SPI4M_ESTA[0]_P | F3  |

| SPI4M_ESTA[1]_N | G2  |

| SPI4M_ESTA[1]_P | F2  |

| SPI4M_ESTA_T0   | G5  |

| SPI4M_ESTA_T1   | G4  |

| SPI4M_ICTL_N    | J5  |

| SPI4M_ICTL_P    | H5  |

| SPI4M_ID[0]_N   | J4  |

| SPI4M_ID[0]_P   | H4  |

| SPI4M_ID[1]_N   | J3  |

| SPI4M_ID[1]_P   | H3  |

| SPI4M_ID[10]_N  | N4  |

Table 1 IDT88K8483 Pinout (Part 10 of 19)

| Function           | Pin                    |

|--------------------|------------------------|

| SPI4M_ID[10]_P     | M4                     |

| SPI4M_ID[11]_N     | N3                     |

| SPI4M_ID[11]_P     | M3                     |

| SPI4M_ID[12]_N     | N2                     |

| SPI4M_ID[12]_P     | M2                     |

| SPI4M_ID[13]_N     | N1                     |

| SPI4M_ID[13]_P     | M1                     |

| SPI4M_ID[14]_N     | R3                     |

| SPI4M_ID[14]_P     | P3                     |

| SPI4M_ID[15]_N     | R2                     |

| SPI4M_ID[15]_P     | P2                     |

| SPI4M_ID[2]_N      | J2                     |

| SPI4M_ID[2]_P      | H2                     |

| SPI4M_ID[3]_N      | J1                     |

| SPI4M_ID[3]_P      | H1                     |

| SPI4M_ID[4]_N      | L5                     |

| SPI4M_ID[4]_P      | K5                     |

| SPI4M_ID[5]_N      | L4                     |

| SPI4M_ID[5]_P      | K4                     |

| SPI4M_ID[6]_N      | L3                     |

| SPI4M_ID[6]_P      | K3                     |

| SPI4M_ID[7]_N      | L2                     |

| SPI4M_ID[7]_P      | K2                     |

| SPI4M_ID[8]_N      | L1                     |

| SPI4M_ID[8]_P      | K1                     |

| SPI4M_ID[9]_N      | N5                     |

| SPI4M_ID[9]_P      | M5                     |

| SPI4M_IDCLK_N      | R1                     |

| SPI4M_IDCLK_P      | P1                     |

| SPI4M_ISCLK_N      | AC1                    |

| SPI4M_ISCLK_P      | AB1                    |

| SPI4M_ISCLK_T      | AD3                    |

| SPI4M_ISTA[0]_N    | AC3                    |

| SPI4M_ISTA[0]_P    | AB3                    |

| SPI4M_ISTA[1]_N    | AC2                    |

| SPI4M_ISTA[1]_P    | AB2                    |

| SPI4M_ISTA_T0      | AC4                    |

| Table 4 IDT00V0402 | Dinaut (Dart 11 of 10) |

Table 1 IDT88K8483 Pinout (Part 11 of 19)

| Function      | Pin  |

|---------------|------|

| SPI4M_ISTA_T1 | AD4  |

| SPI4M_LVDSTA  | AF5  |

| SPI4M_RCLK    | AF3  |

| SPI4M_VREF    | AD2  |

| SPIEN         | E3   |

| TCK           | M6   |

| TDI           | W21  |

| TDO           | N6   |

| TESTSE        | J21  |

| TIMEBASE      | AE4  |

| TMS           | H21  |

| TRSTB         | V21  |

| WRB           | B5   |

| VDDA25        | AA17 |

| VDDA25        | AA10 |

| VDDA25        | F17  |

| VDDA25        | F10  |

| VDDA25        | G17  |

| VDDA25        | G10  |

| VDDA25        | L8   |

| VDDA25        | L7   |

| VDDA25        | U8   |

| VDDA25        | U7   |

| VDDA25        | Y17  |

| VDDA25        | Y10  |

| VDDC12        | H17  |

| VDDC12        | H16  |

| VDDC12        | H15  |

| VDDC12        | H14  |

| VDDC12        | H13  |

| VDDC12        | H12  |

| VDDC12        | H11  |

| VDDC12        | H10  |

| VDDC12        | H9   |

| VDDC12        | H19  |

| VDDC12        | H18  |

| VDDC12        | J17  |

Table 1 IDT88K8483 Pinout (Part 12 of 19)

| Function                                  | Pin |

|-------------------------------------------|-----|

| VDDC12                                    | J16 |

| VDDC12                                    | J15 |

| VDDC12                                    | J14 |

| VDDC12                                    | J13 |

| VDDC12                                    | J12 |

| VDDC12                                    | J11 |

| VDDC12                                    | J10 |

| VDDC12                                    | J9  |

| VDDC12                                    | J19 |

| VDDC12                                    | J18 |

| VDDC12                                    | K10 |

| VDDC12                                    | K9  |

| VDDC12                                    | K19 |

| VDDC12                                    | K18 |

| VDDC12                                    | L10 |

| VDDC12                                    | L9  |

| VDDC12                                    | L19 |

| VDDC12                                    | L18 |

| VDDC12                                    | M10 |

| VDDC12                                    | M9  |

| VDDC12                                    | M19 |

| VDDC12                                    | M18 |

| VDDC12                                    | N10 |

| VDDC12                                    | N9  |

| VDDC12                                    | N19 |

| VDDC12                                    | N18 |

| VDDC12                                    | P10 |

| VDDC12                                    | P9  |

| VDDC12                                    | P19 |

| VDDC12                                    | P18 |

| VDDC12                                    | R10 |

| VDDC12                                    | R9  |

| VDDC12                                    | R19 |

| VDDC12                                    | R18 |

| VDDC12                                    | T10 |

| VDDC12                                    | Т9  |

| VDDC12                                    | T19 |

| Table 4 IDT00K0402 Dinaut (Dart 12 of 10) |     |

Table 1 IDT88K8483 Pinout (Part 13 of 19)

| VDDC12         T18           VDDC12         U10           VDDC12         U9           VDDC12         U19           VDDC12         U18           VDDC12         V16           VDDC12         V15           VDDC12         V14           VDDC12         V14           VDDC12         V11           VDDC12         V11           VDDC12         V10           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W14           VDDC12         W13           VDDC12         W14           VDDC12         W11           VDDC12         W10           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W19           VDDC12         W19           VDDC12         W19           VDDC12         W19           VDDC15         W20           VDDH15         M26 <th>Function</th> <th>Pin</th>     | Function | Pin  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|

| VDDC12         U19           VDDC12         U19           VDDC12         U18           VDDC12         V17           VDDC12         V16           VDDC12         V15           VDDC12         V14           VDDC12         V13           VDDC12         V11           VDDC12         V11           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDH15         AE26           VDDH15         M26           VDDH15         M20           VDDH15         W20           VDDH15         W20           VDDH15         W20 </td <td>VDDC12</td> <td>T18</td> | VDDC12   | T18  |

| VDDC12         U18           VDDC12         V17           VDDC12         V16           VDDC12         V16           VDDC12         V15           VDDC12         V14           VDDC12         V13           VDDC12         V11           VDDC12         V11           VDDC12         V19           VDDC12         V19           VDDC12         V19           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH25         G19 </td <td>VDDC12</td> <td>U10</td> | VDDC12   | U10  |

| VDDC12         U18           VDDC12         V17           VDDC12         V16           VDDC12         V15           VDDC12         V14           VDDC12         V13           VDDC12         V11           VDDC12         V10           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W11           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         M20           VDDH15         M20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH25         G19 <td>VDDC12</td> <td>U9</td>        | VDDC12   | U9   |

| VDDC12         V16           VDDC12         V16           VDDC12         V15           VDDC12         V14           VDDC12         V13           VDDC12         V11           VDDC12         V11           VDDC12         V10           VDDC12         V19           VDDC12         V19           VDDC12         V18           VDDC12         W16           VDDC12         W16           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W10           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         M20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH15         W20           VDDH15         W20 </td <td>VDDC12</td> <td>U19</td> | VDDC12   | U19  |

| VDDC12         V15           VDDC12         V15           VDDC12         V14           VDDC12         V13           VDDC12         V12           VDDC12         V11           VDDC12         V10           VDDC12         V9           VDDC12         V18           VDDC12         V18           VDDC12         W16           VDDC12         W16           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         N20           VDDH15         W20           VDDH15         W20           VDDH25         G19                                                                                                                                                                                     | VDDC12   | U18  |

| VDDC12         V14           VDDC12         V14           VDDC12         V13           VDDC12         V12           VDDC12         V11           VDDC12         V10           VDDC12         V9           VDDC12         V18           VDDC12         W16           VDDC12         W16           VDDC12         W15           VDDC12         W13           VDDC12         W11           VDDC12         W11           VDDC12         W11           VDDC12         W19           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         N20           VDDH15         N20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                  | VDDC12   | V17  |

| VDDC12         V14           VDDC12         V13           VDDC12         V11           VDDC12         V11           VDDC12         V10           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W18           VDDC12         W18           VDDH15         AE26           VDDH15         AE26           VDDH15         N20           VDDH15         N20     <                            | VDDC12   | V16  |

| VDDC12         V12           VDDC12         V12           VDDC12         V11           VDDC12         V10           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                               | VDDC12   | V15  |

| VDDC12         V11           VDDC12         V11           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W16           VDDC12         W16           VDDC12         W14           VDDC12         W13           VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         Y20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                            | VDDC12   | V14  |

| VDDC12         V10           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W13           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W18           VDDC12         W18           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                  | VDDC12   | V13  |

| VDDC12         V9           VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         W20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                          | VDDC12   | V12  |

| VDDC12         V9           VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                | VDDC12   | V11  |

| VDDC12         V19           VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDC12         W18           VDDH15         M26           VDDH15         M26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDC12   | V10  |

| VDDC12         V18           VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDC12         W18           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         W20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                            | VDDC12   | V9   |

| VDDC12         W17           VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDDC12   | V19  |

| VDDC12         W16           VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDC12   | V18  |

| VDDC12         W15           VDDC12         W14           VDDC12         W13           VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDC12   | W17  |

| VDDC12         W14           VDDC12         W13           VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VDDC12   | W16  |

| VDDC12         W13           VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDC12   | W15  |

| VDDC12         W12           VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDC12   | W14  |

| VDDC12         W11           VDDC12         W10           VDDC12         W9           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VDDC12   | W13  |

| VDDC12         W10           VDDC12         W9           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VDDC12   | W12  |

| VDDC12         W9           VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDDC12   | W11  |

| VDDC12         W19           VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         B26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VDDC12   | W10  |

| VDDC12         W18           VDDH15         M26           VDDH15         AE26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VDDC12   | W9   |

| VDDH15         M26           VDDH15         AE26           VDDH15         B26           VDDH15         M20           VDDH15         V20           VDDH15         W20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VDDC12   | W19  |

| VDDH15         AE26           VDDH15         B26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VDDC12   | W18  |

| VDDH15         B26           VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | VDDH15   | M26  |

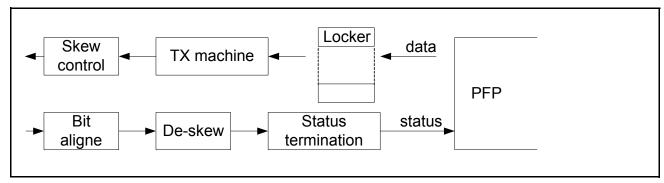

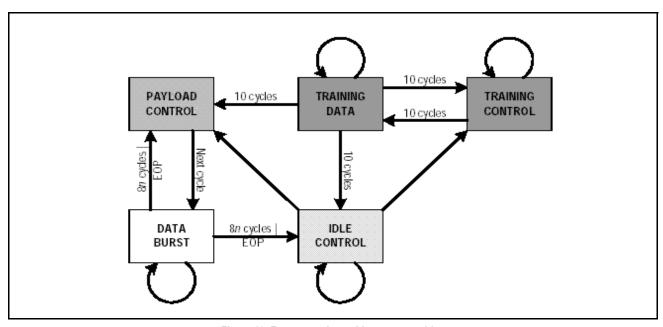

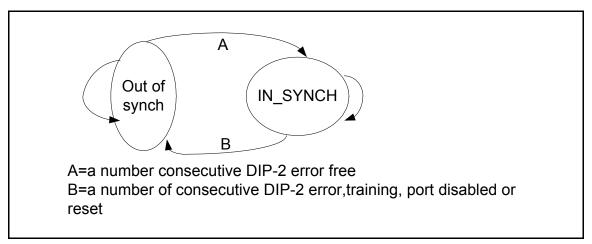

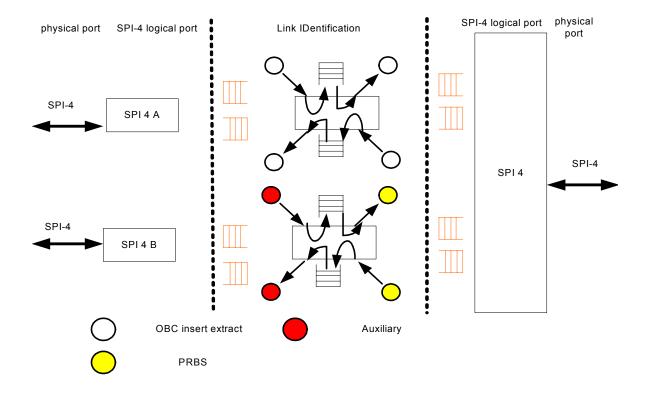

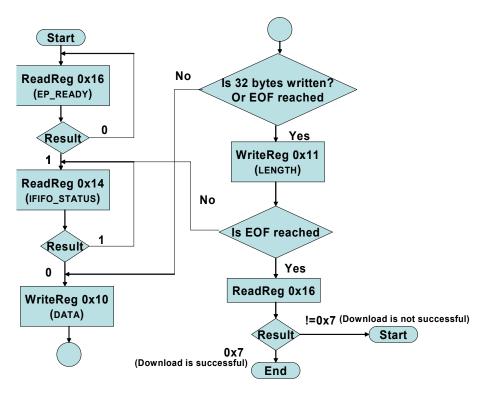

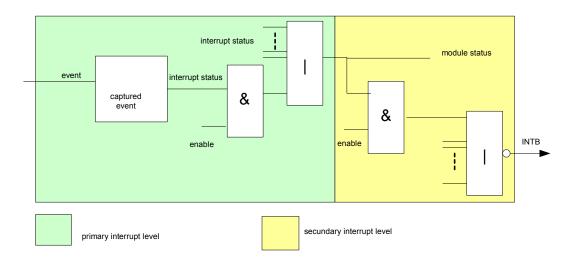

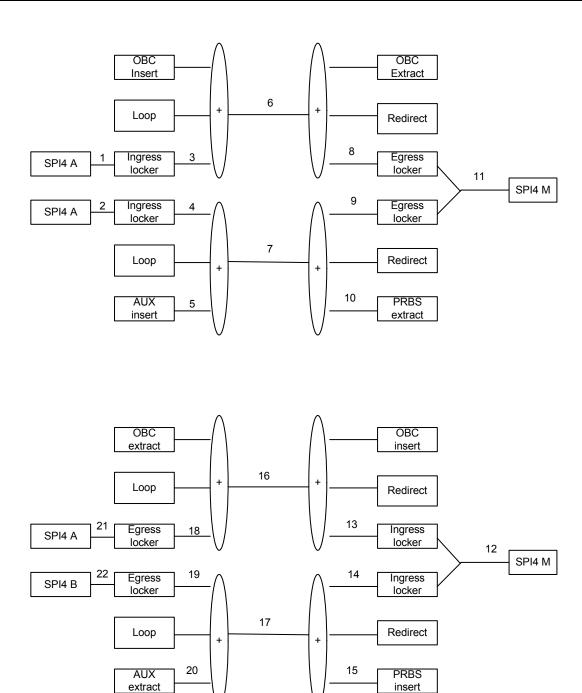

| VDDH15         M20           VDDH15         N20           VDDH15         V20           VDDH15         W20           VDDH15         Y20           VDDH25         G19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VDDH15   | AE26 |