# LM8322

# Mobile I/O Companion Supporting Key-Scan, I/O Expansion, PWM, and ACCESS.bus Host Interface

# 1.0 General Description

The LM8322 Mobile I/O Companion is a dedicated device to unburden a host processor from scanning a matrix-addressed keypad. In addition, the LM8322 provides general-purpose I/O expansion, and PWM outputs useful for dynamic LED brightness modulation.

It communicates with the host through an I<sup>2</sup>C-compatible ACCESS.bus interface. An interrupt output is available for signaling key-press and key-release events. Communication frequencies up to 400 kHz (Fast-mode) bus speed are supported. The LM8322 supports a predefined set of commands. These commands enable a host device to keep control over all functions.

## 2.0 Features

#### **Key Features**

- Supports keypad matrices of up to 8 x 12 keys plus 8 special-function (SF) keys for a total of 104 keys. SF keys pull keypad scan inputs directly to ground, rather than connecting to a keypad scan output.

- Supports I<sup>2</sup>C-compatible ACCESS.bus interface in slave mode up to 400 kHz (Fast-mode).

- Three host-programmable PWM outputs useful for smooth LED brightness modulation.

- Supports general-purpose I/O expansion on pins not otherwise used for keypad interface.

- Key-scan event storage in a FIFO buffer for up to 15 events.

- Key events, errors, and dedicated hardware interrupts request host service by asserting the IRQ output.

- The correct reception of a command may be assumed, if no error is reported from the LM8322 after receiving a command.

- Wake-up from Halt mode on any matrix key-scan event, any use of the SF keys, or any activity on the ACCESS.bus interface.

# 3.0 Applications

- Mobile phones

- Personal Digital Assistants (PDAs)

- Smart handheld devices

- Personal media players

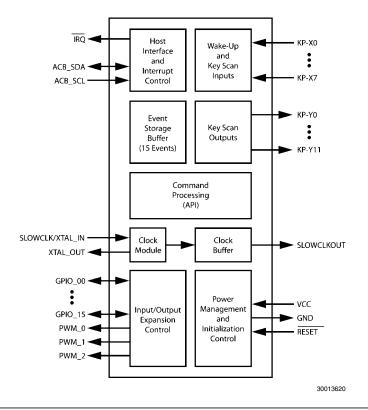

# 4.0 Block Diagram

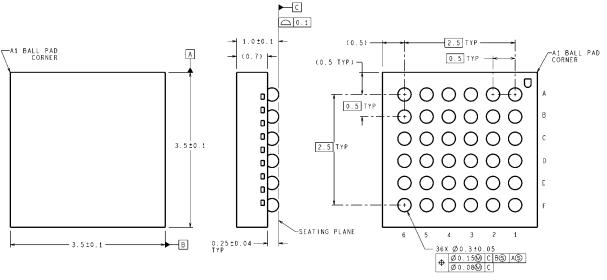

# **5.0 Ordering Information**

| NSID        | Spec. | No. of Pins | Package Type | Temperature   | Package Method       |

|-------------|-------|-------------|--------------|---------------|----------------------|

| LM8322JGR8  | NOPB  | 36          | Micro-Array  | −40 to + 85°C | 1000 pcs Tape & Reel |

| LM8322JGR8X | NOPB  | 36          | Micro-Array  | −40 to + 85°C | 3500 pcs Tape & Reel |

NOPB = No PB (No Lead)

# **6.0 Pin Assignments**

|   | 1        | 2       | 3       | 4        | 5          | 6        |

|---|----------|---------|---------|----------|------------|----------|

| Α | KP-Y5    | KP-X4   | KP-X6   | VCC<br>O | KP-X1      | KP-X0    |

| В | KP-Y6    | KP-Y4   | KP-X5   | KP-X7    | Kb-7.3     | KP-Y2    |

| С | RESET    | KP-Y7   | GND     | GND      | KP-Y1      | KP-Y0    |

| D | XTAL_OUT | SLOWCLK | GND     | GND      | O<br>Kb-Aa | CONFIG_1 |

| E | ACB_SCL  | ACB_SDA | KP-Y8   | PWM_0    | PWM_2      | KP-Y10   |

| F | KP-X2    | KP-X3   | RQ<br>○ | VCC<br>O | PWM_1      | KP-Y11   |

|   |          |         |         |          |            | 30013621 |

Top View 36-Pin MICRO-ARRAY Package See NS Package Number GRA36A

# **Table of Contents**

| 1.0 General Description                                               | 1  |

|-----------------------------------------------------------------------|----|

| 2.0 Features                                                          |    |

| 3.0 Applications                                                      | 1  |

| 4.0 Block Diagram                                                     | 1  |

| 5.0 Ordering Information                                              | 2  |

| 6.0 Pin Assignments                                                   | 2  |

| 7.0 Signal Descriptions                                               | 5  |

| 7.1 TERMINATION OF UNUSED SIGNALS                                     | 6  |

| 8.0 Application Example                                               | 7  |

| 8.1 FEATURES                                                          | 7  |

| 9.0 Clocks                                                            | 8  |

| 9.1 INTERNAL EXECUTION CYCLE                                          | 8  |

| 9.2 BUFFERED CLOCK                                                    | 8  |

| 9.3 CLOCK CONFIGURATION                                               |    |

| 10.0 Reset                                                            | 10 |

| 10.1 EXTERNAL RESET                                                   | 10 |

| 10.2 POWER-ON RESET (POR)                                             | 10 |

| 10.3 PIN CONFIGURATION AFTER RESET                                    | 10 |

| 10.4 DEVICE CONFIGURATION AFTER RESET                                 |    |

| 10.5 CONFIGURATION INPUTS                                             | 11 |

| 10.6 INITIALIZATION                                                   | 11 |

| 10.7 INITIALIZATION EXAMPLE                                           |    |

| 11.0 Halt Mode                                                        | 13 |

| 11.1 ACCESS.bus ACTIVITY                                              | 13 |

| 12.0 Keypad Interface                                                 | 14 |

| 12.1 EVENT CODE ASSIGNMENT                                            | 14 |

| 12.2 KEYPAD SCAN CYCLES                                               | 14 |

| 12.2.1 Timing Parameters                                              | 15 |

| 12.2.2 Multiple Key Pressings                                         | 15 |

| 12.3 EXAMPLE KEYPAD CONFIGURATION                                     | 15 |

| 13.0 General-Purpose I/O Ports  13.1 USING THE CONFIG_X PINS FOR GPIO | 10 |

| 13.2 GPIO TIMING                                                      | 17 |

| 14.0 PWM Output Generation                                            | 10 |

| 14.1 COMMAND QUEUE                                                    | 10 |

| 14.1 COMMAND QUEUE                                                    | 10 |

| 14.3 PWM SCRIPT COMMANDS                                              | 10 |

| 14.4 RAMP COMMAND                                                     | 20 |

| 14.5 SET PWM COMMAND                                                  |    |

| 14.6 GO_TO_START COMMAND                                              |    |

| 14.7 BRANCH COMMAND                                                   | 20 |

| 14.8 END COMMAND                                                      |    |

| 14.9 TRIGGER COMMAND                                                  |    |

| 14.10 PWM SCRIPT EXAMPLE                                              |    |

| 14.10.1 PWM Channel 0 Script                                          |    |

| 14.10.2 PWM Channel 1 Script                                          |    |

| 14.10.3 PWM Channel 2 Script                                          |    |

| 14.11 SELECTABLE SCRIPT EXAMPLE                                       | 23 |

| 15.0 Digital Multiplexers                                             | 24 |

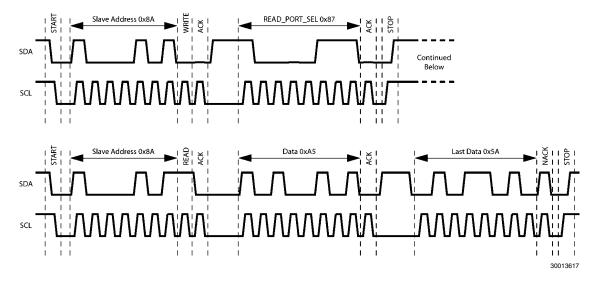

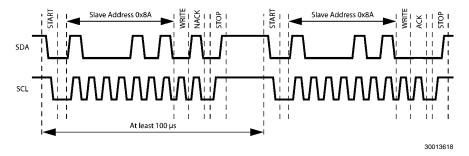

| 16.0 Host Interface                                                   | 25 |

| 16.1 START AND STOP CONDITIONS                                        | 25 |

| 16.2 CONTINUOUS COMMAND STRINGS                                       | 25 |

| 16.3 DEVICE ADDRESS                                                   |    |

| 16.4 HOST WRITE COMMANDS                                              | 25 |

| 16.5 HOST READ COMMANDS                                               | 26 |

| 16.6 INTERRUPTS                                                       | 26 |

| 16.7 INTERRUPT CODE                                                   |    |

| 16.8 ERROR CODE                                                       | 27 |

| 16.9 WAKE-UP FROM HALT MODE                                           |    |

| 17.0 Host Commands                                                    |    |

| 17.1 READ_ID COMMAND                                                  |    |

| 17.2 WRITE_CFG COMMAND                                                |    |

| 17.3 READ_INT COMMAND                                                 |    |

| 17.4 RESET COMMAND                                                    | 30 |

| 17.5 WRITE_PULL_DOWN COMMAND       | 31 |

|------------------------------------|----|

| 17.6 WRITE_PORT_SEL COMMAND        | 31 |

| 17.7 WRITE_PORT_STATE COMMAND      | 32 |

| 17.8 READ_PORT_SEL COMMAND         | 32 |

| 17.9 READ_PORT_STATE COMMAND       | 33 |

| 17.10 READ_FIFO COMMAND            | 33 |

| 17.11 RPT_READ_FIFO COMMAND        | 33 |

| 17.12 SET_ACTIVE COMMAND           | 34 |

| 17.13 READ_ERROR COMMAND           | 34 |

| 17.14 SET_DEBOUNCE COMMAND         | 35 |

| 17.15 SET_KEY_SIZE COMMAND         | 35 |

| 17.16 READ_KEY_SIZE COMMAND        | 35 |

| 17.17 READ_CFG COMMAND             | 36 |

| 17.18 WRITE_CLOCK COMMAND          | 36 |

| 17.19 READ_CLOCK COMMAND           | 36 |

| 17.20 PWM_WRITE COMMAND 3          | 37 |

| 17.21 PWM_START COMMAND (          | 37 |

| 17.22 PWM_STOP COMMAND             | 37 |

| 18.0 Absolute Maximum Ratings      | 38 |

| 19.0 DC Electrical Characteristics | 38 |

| 20.0 AC Electrical Characteristics | 39 |

| 21 0 Physical Dimensions           | 41 |

# 7.0 Signal Descriptions

| Pin  | Function   | I/O    | Description                             |

|------|------------|--------|-----------------------------------------|

| A6   | KP-X0      | Input  | Wake-up input/Keyboard scanning input 0 |

| A5   | KP-X1      | Input  | Wake-up input/Keyboard scanning input 1 |

| F1   | KP-X2      | Input  | Wake-up input/Keyboard scanning input 2 |

| F0   | KP-X3      | Input  | Wake-up input/Keyboard scanning input 3 |

| F2   | GPIO_13    | I/O    | General-purpose I/O port 13             |

| 40   | KP-X4      | Input  | Wake-up input/Keyboard scanning input 4 |

| A2   | GPIO_12    | I/O    | General-purpose I/O port 12             |

| В3   | KP-X5      | Input  | Wake-up input/Keyboard scanning input 5 |

| В    | GPIO_11    | I/O    | General-purpose I/O port 11             |

| А3   | KP-X6      | Input  | Wake-up input/Keyboard scanning input 6 |

| AS   | GPIO_10    | I/O    | General-purpose I/O port 10             |

| D4   | KP-X7      | Input  | Wake-up input/Keyboard scanning input 7 |

| B4   | GPIO_09    | Input  | General-purpose I/O port 9              |

| C6   | KP_Y0      | Output | Keyboard scanning output 0              |

| C5   | KP-Y1      | Output | Keyboard scanning output 1              |

| B6   | KP-Y2      | Output | Keyboard scanning output 2              |

| D.C. | KP-Y3      | Output | Keyboard scanning output 3              |

| B5   | GPIO_08    | I/O    | General-purpose I/O port 8              |

| DO.  | KP-Y4      | Output | Keyboard scanning output 4              |

| B2   | GPIO_07    | I/O    | General-purpose I/O port 7              |

| A 4  | KP-Y5      | Output | Keyboard scanning output 5              |

| A1 - | GPIO_06    | I/O    | General-purpose I/O port 6              |

| D4   | KP-Y6      | Output | Keyboard scanning output 6              |

| B1 - | GPIO_05    | I/O    | General-purpose I/O port 5              |

| C2   | KP-Y7      | Output | Keyboard scanning output 7              |

| C2   | GPIO_04    | I/O    | General-purpose I/O port 4              |

|      | KP-Y8      | Output | Keyboard scanning output 8              |

| E3   | SLOWCLKOUT | Output | 32.768 kHz clock output                 |

|      | GPIO_03    | I/O    | General-purpose I/O port 3              |

|      | KP-Y9      | Output | Keyboard scanning output 9              |

| D5   | MUX2_IN1   | Input  | Multiplexer 2 input 1                   |

|      | GPIO_02    | I/O    | General-purpose I/O port 2              |

|      | KP-Y10     | Output | Keyboard scanning output 10             |

| E6   | MUX2_IN2   | Input  | Multiplexer 2 input 2                   |

|      | GPIO_01    | I/O    | General-purpose I/O port 1              |

|      | KP-Y11     | Output | Keyboard scanning output 11             |

| F6   | MUX2_OUT   | Output | Multiplexer 2 output                    |

|      | GPIO_00    | I/O    | General-purpose I/O port 0              |

| E2   | ACB_SDA    | I/O    | ACCESS.bus data signal                  |

| E1   | ACB_SCL    | I/O    | ACCESS.bus clock signal                 |

| E4 - | PWM_0      | Output | Pulse-width modulated output 0          |

|      | MUX_IN1    | Input  | Multiplexer 1 input 1                   |

| E5   | PWM_1      | Output | Pulse-width modulated output 1          |

| F5 - | MUX_IN2    | Input  | Multiplexer 1 input 2                   |

|      | PWM_2      | Output | Pulse-width modulated output 2          |

|      | MUX1_OUT   | Output | Multiplexer 1 output                    |

| E5   | CONFIG_2   | Input  | Slave address select input 2            |

|      | GPIO_15    | I/O    | General-purpose I/O port 15             |

| Pin               | Function        | I/O    | Description                  |

|-------------------|-----------------|--------|------------------------------|

| D6                | CONFIG_1        | Input  | Slave address select input 1 |

| Do                | GPIO_14         | I/O    | General-purpose I/O port 14  |

| D1                | XTAL_OUT        | Input  | 32.768 kHz crystal output    |

| D2                | SLOWCLK         | Input  | 32.768 kHz clock             |

| DZ                | XTAL_IN         | Input  | 32.768 kHz crystal input     |

| F3                | ĪRQ             | Output | Interrupt request output     |

| C1                | RESET           | Input  | Reset Input                  |

| A4, F4            | V <sub>cc</sub> | n.a.   | V <sub>CC</sub>              |

| C3, C4,<br>D3, D4 | GND             | n.a.   | Ground                       |

# 7.1 TERMINATION OF UNUSED SIGNALS

**TABLE 1. Termination of Unused Signals**

| Signal     | Termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET      | Connect to V <sub>CC</sub> if not driven from an external Supervisory circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CONFIG_1   | Connect to $V_{CC}$ or GND through a pullup or pulldown resistor because the slave address is selected by the level on this pin. This pin cannot be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTAL_IN    | This pin is a high-impedance input and must be connected to V <sub>CC</sub> or GND if it is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTAL_OUT   | This pin has a weak pullup and can be left open-circuit if it is unused.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| KP-X[2:0]  | These pins are dedicated keypad pins. In the minimum configuration, these pins are keypad inputs with weak pullups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| KP-X[7:3]  | These pins are in high-impedance mode after power-on initialization. There are two ways to handle these pins if unused:  Connect to V <sub>CC</sub> or GND.  Program as inputs with weak pullups or outputs.  Care must be taken when connecting to V <sub>CC</sub> or GND. Erroneous parameters sent with the WRITE_PORT_SEL or WRITE_PORT_STATE commands could cause excessive current consumption. A better approach is to leave unused keyboard inputs open-circuit and use the WRITE_PORT_SEL and WRITE_PORT_STATE commands to configure the pins as inputs with weak pullups or outputs.  KP-X7 can only be an input. This pin should be programmed as an input with a weak pullup. |

| KP-Y[2:0]  | These pins are dedicated keypad pins. In the minimum configuration, these pins are keypad outputs driven low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| KP-Y[11:3] | These pins are in high-impedance mode after power-on initialization. There are two ways to handle these pins if unused:  • Connect to V <sub>CC</sub> or GND.  • Program as inputs with weak pullups or outputs  Care must be taken when connecting to V <sub>CC</sub> or GND. Erroneous parameters sent with the WRITE_PORT_SEL or WRITE_PORT_STATE commands could cause excessive current consumption. A better approach is to leave unused keyboard inputs open-circuit and use the WRITE_PORT_SEL and WRITE_PORT_STATE commands to configure the pins as inputs with weak pullups or outputs.                                                                                         |

| PWM_0,     | These pins must be connected to V <sub>CC</sub> or GND if they are not used for any optional function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PWM_1      | described in the datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PWM_2/     | Connect to $V_{CC}$ or GND through a pullup or pulldown resistor because the slave address is selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CONFIG_2   | by the level on this pin. This pin cannot be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ĪRQ        | This pin must be connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

6

# 8.0 Application Example

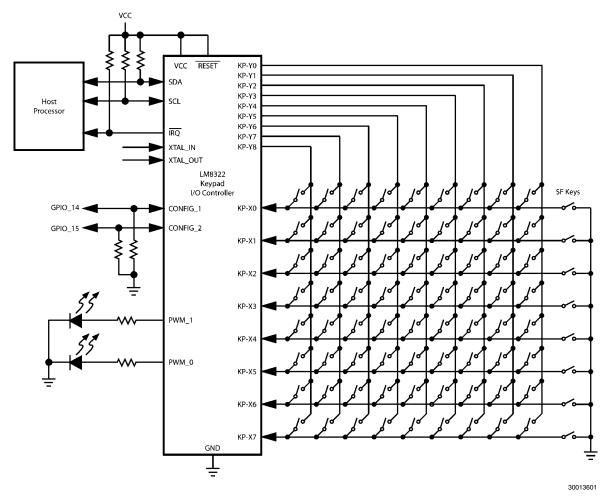

**FIGURE 1. Typical Application**

#### **8.1 FEATURES**

The application example shown in *Figure 1* supports the following features:

- 8 x 9 standard keys.

- 8 special function keys (SF keys) with wake-up capability by forcing a WAKE\_INx pin to ground. Pressing a SF key overrides any other key in the same row.

- ACCESS.bus (I<sup>2</sup>C-compatible) interface for communication with the host.

- Hardware IRQ interrupt to host to signal keypad, error, and status events. By default, this is an open-drain output, so an external pullup resistor may be required to avoid false assertion. The host can program this output for push-pull mode, in which case the pullup might not be required, if the host can ignore a false assertion before the LM8322 has been programmed.

- Two LEDs driven by PWM outputs with programmable ramp-up and ramp-down. PWM\_2 (shared with GPIO\_15 and CONFIG\_2) could be used as an additional PWM driver port to control a third external LED.

- ACCESS.bus address is selected by the CONFIG\_1 and CONFIG\_2 inputs. These pins may also be used as GPIO pins after reset initialization has occurred. If extra GPIO pins are not needed, CONFIG\_1 and CONFIG\_2 may be tied directly to V<sub>CC</sub> and GND.

- Crystal pins XTAL\_IN and XTAL\_OUT may be used to connect to an external 32.768 kHz crystal or receive an external 32.768 kHz clock input for running the PWM peripheral. By default, the PWM is clocked by an on-chip clock source.

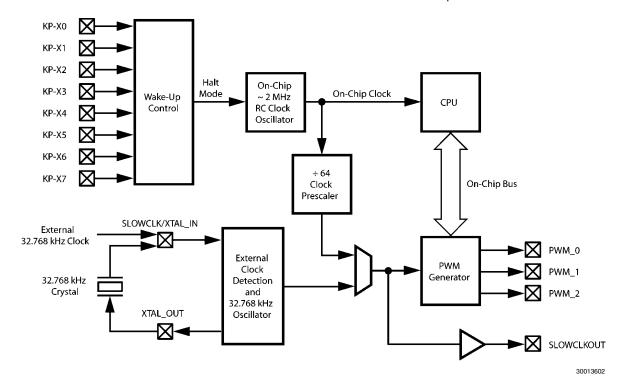

#### 9.0 Clocks

- System Clock (mclk) The system clock is in the range of about 21 MHz (± 7%) typical. This clock is used to drive the I<sup>2</sup>C compatible serial ACCESS bus and is the input clock for other function blocks.

- Processing and Command Execution Clock (t<sub>C</sub>) The internal processing is based on a 2 MHz clock. This clock is derived from the System Clock.

- Internal PWM Clock The internal PWM clock is a fixed scaled down clock (÷ 64) of the Processing and Command

- Execution Clock. This clock is close to 32 kHz which is in a good range to source the PWM function block as an alternative to an external clock source.

- External 32.768 kHz Clock driven into the SLOWCLK input. May be used internally as the timebase for the PWM and driven on the SLOWCLKOUT output.

- External 32.768 kHz Crystal connected across the XTAL\_IN and XTAL\_OUT pins (XTAL\_IN is an alternate function of the SLOWCLK pin). May be used internally as the timebase for the PWM and driven on the SLOWCLKOUT output.

**FIGURE 2. Clock Architecture**

#### 9.1 INTERNAL EXECUTION CYCLE

The Processing - and Command - execution clock is about 2 MHz. This clock is stopped in Halt mode, which only occurs under control of the LM8322. However, the host can set the period of inactivity which causes the device to enter Halt mode.

Exit from Halt mode can be triggered by any of these events:

- · Occurrence of a key-press or key-release event.

- A Start condition driven by the host on the ACCESS.bus interface.

- Assertion of the RESET input.

After reset, the default timebase for the PWM outputs is the internal execution clock divided by 64.

#### 9.2 BUFFERED CLOCK

The timebase for the PWM comes from any of three sources:

- Prescaled internal Execution clock.

- External 32.768 kHz clock received on the SLOWCLK input.

- On-chip oscillator with an external crystal connected across XTAL\_IN and XTAL\_OUT.

Any of these sources may be buffered and driven on the SLOWCLKOUT output. The clock buffer is enabled with the WRITE\_CLOCK command.

If XTAL\_IN is not used it must be terminated to  $\ensuremath{\text{V}_{\text{CC}}}$  or GND.

#### 9.3 CLOCK CONFIGURATION

Table 2 shows the clock configurations available by loading the clock configuration register with the WRITE\_CLOCK com-

mand. The WRITE\_CLOCK command must be issued only once during system initialization. This command is used to override the default settings.

#### **TABLE 2. Clock Configuration Register**

| 7 | 6          | 5 | 4 | 3         | 2 | 1   | 0   |

|---|------------|---|---|-----------|---|-----|-----|

| 0 | SLOWCLKOUT | 0 | 0 | SLOWCLKEN | 0 | RCF | PWM |

| Bit        | Value | Description                                                                                   |

|------------|-------|-----------------------------------------------------------------------------------------------|

| SLOWCLKOUT | 0     | Disable SLOWCLKOUT buffer.                                                                    |

| SLOWCLROOT | 1     | Enable SLOWCLKOUT buffer.                                                                     |

|            | 0     | External 32.768 kHz crystal is installed between the XTAL_IN and XTAL_OUT pins.               |

| SLOWCLKEN  | 1     | External 32.768 kHz clock is received on the SLOWCLK pin, or no 32.768 kHz clock is required. |

|            | 00    | On-chip RC clock divided by 64 drives the PWM and clock buffer.                               |

| BCPWM      | 01    | Reserved.                                                                                     |

| RCPWW      | 10    | Reserved.                                                                                     |

|            | 11    | External 32.768 kHz clock or crystal drives the PWM and clock buffer.                         |

The SLOWCLKOUT signal is an alternate function of the pin used for the KP-Y8 scanning output and the GPIO\_03 port. If

the SLOWCLKOUT function is enabled, these other functions of the pin are unavailable.

## 10.0 Reset

The LM8322 may be reset by either an external reset, RE-SET command, or an internally generated power-on reset (POR) signal. The RESET input must not be allowed to float. If the external RESET input is not used, it must be connected to VCC, either directly or through a pull-up resistor.

#### **10.1 EXTERNAL RESET**

The device enters a reset state immediately when the  $\overline{\text{RE-SET}}$  input is driven low.  $\overline{\text{RESET}}$  must be held low for a minimum of 700 ns to guarantee a valid reset. If  $\overline{\text{RESET}}$  is asserted at power-on, it must be held low until  $V_{CC}$  rises above the minimum operating voltage (1.62V). If an RC circuit is used to drive  $\overline{\text{RESET}}$ , it must have a time constant 5 times (5x) greater than the  $V_{CC}$  rise time to this level.

When RESET goes low, the I/O ports are initialized immediately, any observed delay being only propagation delay.

When the RESET pin goes high, the LM8322 comes out of the reset state within about 1400 ns.

#### 10.2 POWER-ON RESET (POR)

The POR circuit is always enabled. When  $V_{\rm CC}$  rises above the POR threshold voltage VPOR (about 1.2–1.5V), an on-chip reset signal is asserted. The  $V_{\rm CC}$  rise time must be greater than 20 µs and less than 10 ms, otherwise the on-chip reset signal may deassert before  $V_{\rm CC}$  reaches the minimum operating voltage. While  $V_{\rm CC}$  is below VPOR, the LM8322 is held in reset and a timer clocked by the on-chip RC clock is preset with 0xFF (256 clock cycles). When  $V_{\rm CC}$  reaches a value greater than VPOR, the timer starts counting down. When it underflows, the on-chip reset signal is deasserted and the LM8322 begins operation.

#### **10.3 PIN CONFIGURATION AFTER RESET**

Table 2 shows the pin configuration after reset.

**TABLE 3. Pin Configuration After Reset**

| Pins     | After Reset          | After LM8322 Initialization                                                   |  |  |

|----------|----------------------|-------------------------------------------------------------------------------|--|--|

| KP-X00   |                      |                                                                               |  |  |

| KP-X01   | High-impedance mode. | Input mode with an on-chip pullup enabled.                                    |  |  |

| KP-X02   |                      |                                                                               |  |  |

| KP-X03   |                      |                                                                               |  |  |

| KP-X04   |                      |                                                                               |  |  |

| KP-X05   | High-impedance mode. | High-impedance mode, until host configures them as keypad inputs or GPIO.     |  |  |

| KP-X06   |                      | of dr lo.                                                                     |  |  |

| KP-X07   |                      |                                                                               |  |  |

| KP-Y00   |                      |                                                                               |  |  |

| KP-Y01   | High-impedance mode. | Active drive low.                                                             |  |  |

| KP-Y02   |                      |                                                                               |  |  |

| KP-Y03   |                      |                                                                               |  |  |

| KP-Y04   |                      |                                                                               |  |  |

| KP-Y05   |                      |                                                                               |  |  |

| KP-Y06   |                      | Ligh importance mode with heat configurate them as leaves of substitution     |  |  |

| KP-Y07   | High-impedance mode. | High-impedance mode, until host configures them as keypad outp or GPIO.       |  |  |

| KP-Y08   |                      | of dr io.                                                                     |  |  |

| KP-Y09   |                      |                                                                               |  |  |

| KP-Y10   |                      |                                                                               |  |  |

| KP-Y11   |                      |                                                                               |  |  |

| CONFIG_1 | High-impedance mode. | The ACCESS.bus slave address must be selected with external                   |  |  |

| CONFIG_2 | High-impedance mode. | pullup or pulldown resistors or direct connections to $V_{\text{CC}}$ or GND. |  |  |

| ĪRQ      | High-impedance mode. | Active drive low.                                                             |  |  |

| PWM_0    |                      |                                                                               |  |  |

| PWM_1    | High-impedance mode. | High-impedance mode.                                                          |  |  |

| PWM_2    |                      |                                                                               |  |  |

| ACB_SDA  | Open drain made      | Open drain mode                                                               |  |  |

| ACB_SCL  | Open-drain mode.     | Open-drain mode.                                                              |  |  |

| XTAL_IN  | High-impedance mode. | High-impedance mode. Terminate to V <sub>CC</sub> or GND if not used.         |  |  |

| XTAL_OUT | Weak pullup device.  | Weak pullup device.                                                           |  |  |

| RESET    | High-impedance mode. | High-impedance mode.                                                          |  |  |

#### **10.4 DEVICE CONFIGURATION AFTER RESET**

After the LM8322 has completed its reset initialization, it will have the following internal configuration:

- PWM Clock the PWM clock source is the on-chip clock divided by 64. This remains in effect until changed by a host command.

- **Keypad Size** 3 × 3.

- Digital Multiplexers disabled.

- **IRQ** enabled, active low.

- NOINIT Bit set.

- **Debounce Time** 3 scan cycles (about 12 milliseconds).

- Active Time 500 milliseconds.

#### **10.5 CONFIGURATION INPUTS**

The states sampled from the CONFIG\_1 and CONFIG\_2 inputs during reset select the ACCESS.bus address used by the LM8322, as shown in *Table 4*. The address occupies the high seven bits of the first byte of a bus transaction, with the LSB (shown as X below) indicating the direction of transfer.

**TABLE 4. Bus Address Selection**

| CONFIG_1 | CONFIG_2 | Bus Address |

|----------|----------|-------------|

| 0        | 0        | 1000 010X   |

| 0        | 1        | 1000 011X   |

| 1        | 0        | 1000 100X   |

| 1        | 1        | 1000 101X   |

When these pins are used as GPIO ports, the design must ensure that they have the desired states during reset. For example, a 100-kohm resistor to ground can impose a logic 0 during reset without interfering with normal operation as a GPIO port.

#### **10.6 INITIALIZATION**

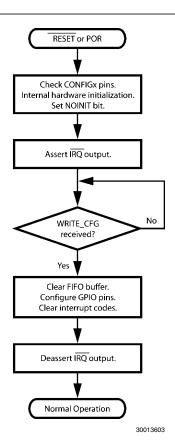

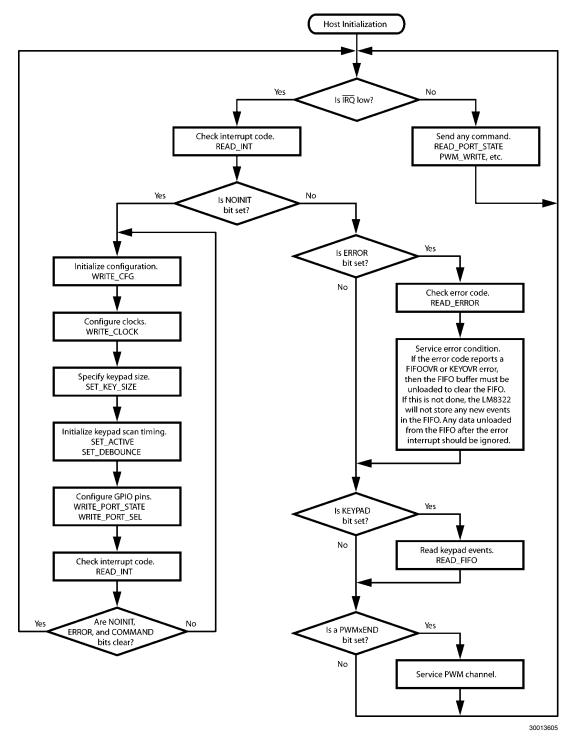

The LM8322 waits for a WRITE\_CFG command from the host. During this time,  $\overline{\text{IRQ}}$  is asserted to request service from the host. *Figure 3* describes the behavior of the LM8322 following reset.

FIGURE 3. LM8322 Initialization Behavior

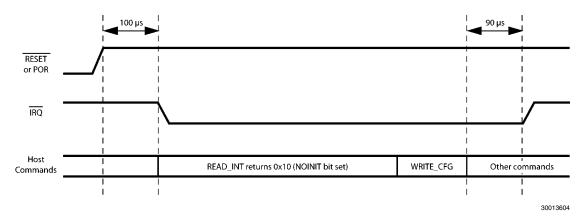

Figure 4 shows the timing of IRQ relative to a RESET or POR event and the WRITE\_CFG command. 100 μs after a RESET or POR event, IRQ is asserted and any READ\_INT command will return an interrupt code with the NOINIT bit set. 90 μs after a WRITE\_CFG command is received, IRQ is deasserted.

FIGURE 4. IRQ Reset Timing

After sending the WRITE\_CFG command, the host must send a series of commands to configure the LM8322, as shown in *Figure 5* (see left hand side).

This Flow - diagram illustrates also the basic host communication steps which the host must execute upon an  $\overline{\text{IRQ}}$  re-

quest received from the LM8322 during operation. Such requests will be made from the LM8322 as a result of key pressed events, the detection of an error, the termination of a PWM cycle and others.

FIGURE 5. Host-Side LM8322 Initialization

12

#### 10.7 INITIALIZATION EXAMPLE

In the following example, the LM8322 is configured as:

- Keypad matrix configuration is 8 x 4.

- GPIO\_03 through GPIO\_07 are available to use as GPIO pins.

- GPIO\_03 is an output driven low.

- GPIO\_4 and GPIO\_5 are outputs driven high.

- GPIO\_06 and GPIO\_07 are inputs with weak pulldowns.

- GPIO\_14 and GPIO\_15 are inputs with weak pullups.

- The PWM clock source is the internal execution clock divided by 64 (about 32 kHz).

Most of these settings can be verified by executing commands such as READ\_CONF, READ\_PORT\_SEL, READ\_CLOCK, etc.

ALL GPIO pin states can be read using the READ\_PORT\_STATE command, without regard to whether the pin is an input or an output.

An open-drain signal can be created by alternating between input mode and driving the output low.

All GPIO s can sink and source 16 mA when configured as an output.

| Command          | Encoding | Parameter 1 | Parameter 2 | Description                                                                                                                                                               |

|------------------|----------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRITE_CFG        | 0x81     | 0x40        |             | Selects 36-pin package and disables the two digital multiplexers.                                                                                                         |

| WRITE_CLK        | 0x93     | 0x08        |             | SLOWCLKOUT disabled, no external 32.768 kHz clock required, PWM clock source is internal.                                                                                 |

| SET_KEY_SIZE     | 0x90     | 0x84        |             | Selects a keypad matrix size of 8 × 4.                                                                                                                                    |

| SET_ACTIVE       | 0x8B     | 0x4B        |             | Sets the active time to about 300 milliseconds (75 $\times$ 4 milliseconds).                                                                                              |

| SET_DEBOUNCE     | 0x8F     | 0x03        |             | Sets the key debouncing time to about 12 milliseconds $(3 \times 4 \text{ ms})$ . This is actually the default and would not have to be performed.                        |

| WRITE_PORT_SEL   | 0x85     | 0x00        | 0x38        | Configure GPIO_03, GPIO_04, and GPIO_05 as outputs. Configure GPIO_06, GPIO_07, GPIO_14, and GPIO_15 as inputs.                                                           |

| WRITE_PULL_DOWN  | 0x84     | 0x00        | 0x3F        | Set the direction for the pullup/pulldown devices on GPIO_06 and GPIO_07 to pulldown. Set the direction for the pullup/pulldown devices on GPIO_14 and GPIO_15 to pullup. |

| WRITE_PORT_STATE | 0x86     | 0xC0        | 0xF0        | Set GPIO_04 and GPIO_05 to drive high. Enable the pullups on GPIO_06, GPIO_07, GPIO_14, and GPIO_15.                                                                      |

#### 11.0 Halt Mode

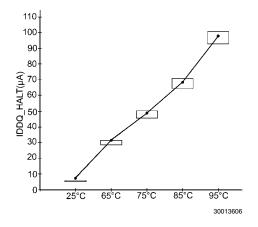

The fully static architecture of the LM8322 allows stopping the internal RC clock in Halt mode, which reduces power consumption to the minimum level. *Figure 6* shows the current in Halt mode at the maximum  $V_{CC}$  (1.98V) from 25°C to +85°C.

FIGURE 6. Halt Current vs. Temperature at 1.98V

Halt mode is entered when no key-press event, key-release event, or ACCESS.bus activity is detected for a certain period of time (by default, 500 milliseconds). The mechanism for entering Halt mode is always enabled in hardware, but the host can program the period of inactivity which triggers entry into Halt mode.

#### 11.1 ACCESS.bus ACTIVITY

When the LM8322 is in Halt mode, any activity on the ACCESS.bus interface will cause the LM8322 to exit from Halt mode. However, the LM8322 will not be able to acknowledge the first bus cycle immediately following wake-up from Halt mode. It will respond with a negative acknowledgement, and the host should then repeat the cycle.

The LM8322 will be prevented from entering Halt mode if it shares the bus with peripherals that are continuously active. For lowest power consumption, the LM8322 should only share the bus with peripherals that require little or no bus activity after system initialization.

# 12.0 Keypad Interface

#### 12.1 EVENT CODE ASSIGNMENT

After power-on reset and host initialization, the LM8322 starts scanning the keypad. It stays active for a default time of about 500 ms after the last key is released, after which it enters Halt

mode to minimize power consumption (typically <5  $\mu$ A standby current).

Table 5 lists the codes assigned to the matrix positions encoded by the hardware. Key-press events are assigned the codes listed in *Table 5*, but with the MSB set. When a key is released, the MSB of the code is clear.

**TABLE 5. Keypad Matrix Code Assignments**

|       | KP-Y0 | KP-Y1 | KP-Y2 | KP-Y3 | KP-Y4 | KP-Y5 | KP-Y6 | KP-Y7 | KP-Y8 | KP-Y9 | KP-Y10 | KP-Y11 | SF Keys |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------|

| KP-X0 | 0x01  | 0x02  | 0x03  | 0x04  | 0x05  | 0x06  | 0x07  | 80x0  | 0x09  | 0x0A  | 0x0B   | 0x0C   | 0x0F    |

| KP-X1 | 0x11  | 0x12  | 0x13  | 0x14  | 0x15  | 0x16  | 0x17  | 0x18  | 0x19  | 0x1A  | 0x1B   | 0x1C   | 0x1F    |

| KP-X2 | 0x21  | 0x22  | 0x23  | 0x24  | 0x25  | 0x26  | 0x27  | 0x28  | 0x29  | 0x2A  | 0x2B   | 0x2C   | 0x2F    |

| KP-X3 | 0x31  | 0x32  | 0x33  | 0x34  | 0x35  | 0x36  | 0x37  | 0x38  | 0x39  | 0x3A  | 0x3B   | 0x3C   | 0x3F    |

| KP-X4 | 0x41  | 0x42  | 0x43  | 0x44  | 0x45  | 0x46  | 0x47  | 0x48  | 0x49  | 0x4A  | 0x4B   | 0x4C   | 0x4F    |

| KP-X5 | 0x51  | 0x52  | 0x53  | 0x54  | 0x55  | 0x56  | 0x57  | 0x58  | 0x59  | 0x5A  | 0x5B   | 0x5C   | 0x5F    |

| KP-X6 | 0x61  | 0x62  | 0x63  | 0x64  | 0x65  | 0x66  | 0x67  | 0x68  | 0x69  | 0x6A  | 0x6B   | 0x6C   | 0x6F    |

| KP-X7 | 0x71  | 0x72  | 0x73  | 0x74  | 0x75  | 0x76  | 0x77  | 0x78  | 0x79  | 0x7A  | 0x7B   | 0x7C   | 0x7F    |

The codes are loaded into the FIFO buffer in the order in which they occurred. *Table 6* shows an example sequence of

events, and *Figure 7* shows the resulting sequence of event codes loaded into the FIFO buffer.

**TABLE 6. Example Sequence of Events**

| Event Number | Event Code | Event on Input | Driven Output | Description                    |

|--------------|------------|----------------|---------------|--------------------------------|

| 1            | 0xC5       | KP-X4          | KP-Y4         | Key is pressed                 |

| 2            | 0xB2       | KP-X3          | KP-Y1         | Key is pressed                 |

| 3            | 0x45       | KP-X4          | KP-Y4         | Key is released                |

| 4            | 0x32       | KP-X3          | KP-Y1         | Key is released                |

| 5            | 0x81       | KP-X0          | KP-Y0         | Key is pressed                 |

| 6            | 0x5F       | KP-X5          | n.a.          | SF Key is released             |

| 7            | 0x01       | KP-X0          | KP-Y0         | Key is released                |

| 8            | 0x00       | n.a.           | n.a.          | Indicates end of stored events |

FIGURE 7. Example Event Codes Loaded in FIFO Buffer

#### 12.2 KEYPAD SCAN CYCLES

The LM8322 starts new scan cycles at fixed time intervals of about 4 milliseconds. If a change in the state of the keypad is detected, the keypad is rescanned after a debounce delay. When the state change has been reliably captured, it is encoded and written to the FIFO buffer.

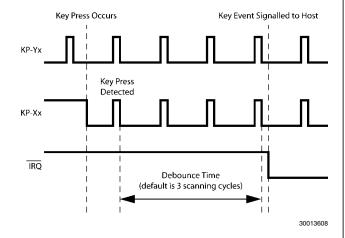

Figure 8 shows the relationship between a KP-Yx output and a KP-Xx input over multiple scan cycles during a key press event. Between scan cycles, the KP-Yx outputs that are specified by the SET\_KEY\_SIZE command (0x90) for keypad scanning are driven low.

FIGURE 8. Keypad Scan Cycles

During a scan cycle, only one KP-Yx output pin will be driven low at any time, while the others are driven high or undriven. At the time scale used in *Figure 8*, the low phase of a KP-Yx output during a scan cycle is not visible. The KP-Xx input pins are pulled high by weak pullups.

There are capacitive loads on the KP-Xx inputs and KP-Yx outputs due to protection circuits, wiring, etc. The LM8322 inserts delays to allow complete charging or discharging of these loads before sampling the input levels on the KP-Xx inputs. The maximum parasitic load capacitance on the KP-Xx inputs is 5 nF.

After detecting a key-press or key-release event, the debounce time specified by the SET\_DEBOUNCE command (0x8F) sets the minimum time for confirming the event before the  $\overline{\mbox{IRQ}}$  output is asserted.

If more than two keys are pressed simultaneously, the pattern of key closures may be ambiguous, in which case the the interrupt code indicates an error and the  $\overline{\text{IRQ}}$  output is asserted (if enabled).

The SF keys connect KP-Xx inputs directly to ground. There can be up to eight SF-keys. If any of these keys are pressed, other keys that use the same KP-Xx pin are ignored.

#### 12.2.1 Timing Parameters

Two timing parameters affect scanning of the keypad:

- Debounce Time minimum delay between detecting a keypad event and confirming the event before asserting IRQ. The default debounce time is 3 scan cycles (about 12 milliseconds), but the host can set values in the range 1–255 cycles (4–1020 milliseconds).

- Active Time period without detecting a state change in the keypad that triggers entry into Halt mode, during which keypad scanning is suspended. The default active time is 500 milliseconds, but the host can set it values in the range 4–1020 milliseconds. The active time must be greater than the debounce time.

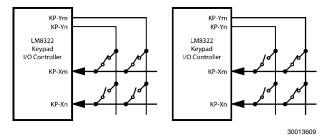

#### 12.2.2 Multiple Key Pressings

If more than two keys are pressed at the same time, the LM8322 stores all key pressed and released events in the FIFO buffer in the sequence in which they were decoded.

For multiple key pressings the following circumstances have to be respected:

- A multiple key-press event is given if two or more keypress events are reported but no corresponding keyrelease event.

- With the activity time set between the minimum and maximum time (4 msec to 1 second) it is not safe to detect

- two simultaneous key pressings in one input row (see Figure 9 on the left hand side.)

- If all key pressings (two or more) are located in different input rows (see Figure 9 on the right hand side) then the key pressed events will be correctly found in the FIFO buffer without any restriction.

FIGURE 9. Simultaneous Keys Pressed

In order to securely detect and store the key codes of simultaneous key pressings in the same input row the following precautions must be taken from the host side:

"As soon as the host device has detected a key pressed event the host must send the SET\_ACTIVE Command with the parameter set to "00". This will prevent the LM8322 from entering HALT mode. If all keyboard events are resolved (no remaining key pressed status in the LM8322 anymore) then the host must send the SET\_ACTIVE Command again with the parameter setting the desired duration for the active time. This will enable the LM8322 to enter low power HALT mode once the activity time has passed without detecting any events.

- Once one or more key (pressed and/or released) events have been read from the host with the help of the READ FIFO command there are two conditions cleaning the FIFO buffer contents:

- A second execution of the READ FIFO Command or,

- A new key event detected from the LM8322.

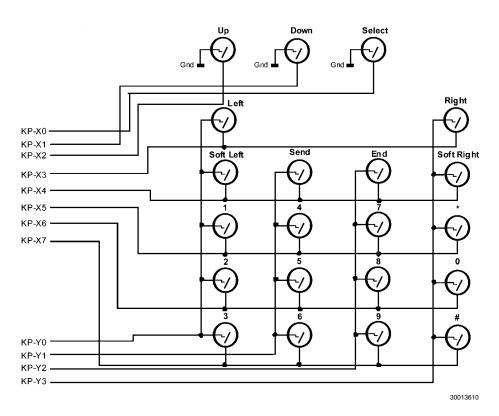

#### 12.3 EXAMPLE KEYPAD CONFIGURATION

Figure 10 shows an  $8\times4$  keypad matrix. This configuration occupies all scanning inputs (KP-X0 through KP-X7) and four scanning outputs (KP-Y0 through KP-Y3). The remaining scanning outputs KP-Y4 through KP-Y11 are available for use as GPIO pins.

FIGURE 10. Keypad Interface Example

In the example above, three keys (Up, Down, and Select) are connected as SF keys (connected directly to ground). Although they could have shared the KP-Xx inputs used with the scanned keys, the advantage of placing them on their own KP-Xx inputs is that it allows scanning the keypad while an SF key is pressed. If an SF key shares a KP-Xx input with any scanned keys, pressing the SF key prevents the LM8322 from reading the scanned keys.

The SET\_KEY\_SIZE command includes a data byte that specifies the keypad size. The upper 4 bits of the data byte specify the number of KP-Xx inputs, and the lower 4 bits specify the number of KP-Yx outputs. The minimum number of inputs and outputs is 3. Therefore, the minimum keypad configuration supports  $3\times 3+3$  SF keys (total of 12 keys). The maximum number of KP-Xx inputs is 8, and the maximum number of KP-Yx pins is 12. All KP-Xx and KP-Yx pins not used for the keyboard interface can be used for general-purpose I/O.

For the example shown in *Figure 10*, the SET\_KEY\_SIZE command would specify 8 KP-Xx inputs and 4 KP-Yx outputs.

# 13.0 General-Purpose I/O Ports

Any unused KP-Xx and KP-Yx pins may be used as general-purpose I/O (GPIO) port pins. The WRITE\_PORT\_SEL (0x85) command selects the port direction, in which a clear bit in the parameter to the command selects the input direction and a set bit selects the output direction.

The WRITE\_PORT\_STATE (0x86) command selects either the port level when configured as output (by the WRITE\_PORT\_SEL command) or when configured as an input selects between a high-impedance input or an input with a pullup or pulldown device. The selection between pullup or pulldown devices is controlled by the parameter bytes to the WRITE\_PULL\_DOWN (0x84) command. Clear bits in the parameter bytes select pullup devices, while set bits select pulldown devices.

*Table 7* shows the GPIO port configurations selected by the bits in the WRITE\_PORT\_SEL, WRITE\_PORT\_STATE, and WRITE\_PULL\_DOWN command parameters.

| WRITE_PORT_SEL | WRITE_PORT_STATE | WRITE_PULL_DOWN | Description                |

|----------------|------------------|-----------------|----------------------------|

| 0              | 0                | Х               | High-Impedance Input       |

| 0              | 1                | 0               | Input with Pullup Device   |

| 0              | 1                | 1               | Input with Pulldown Device |

| 1              | 0                | Х               | Output, Drive Low          |

**TABLE 7. GPIO Port Control Bits**

Any pins used as GPIO ports must be configured after the peripheral configuration has been initialized with the WRITE\_CFG command (0x81) and the keypad configuration

has been initialized with the SET\_KEY\_SIZE command (0x90). The default keypad configuration after reset is a  $3\times3$

Output, Drive High

keyboard matrix. The default GPIO configuration is an input with the pullup disabled.

#### 13.1 USING THE CONFIG\_X PINS FOR GPIO

The CONFIG\_1 and CONFIG\_2 pins are available for use as GPIO pins after power-on or reset. However, stable states must be provided on these pins during power-on or reset to select the ACCESS.bus (I<sup>2</sup>C) bus address.

External pullup or pulldown resistors can be used to pull either CONFIG\_x pin low, while retaining the ability to drive it to another state when used as a GPIO pin.

CONFIG\_2 has two alternate functions, in addition to GPIO. It can be configured as a multiplexer output using the

WRITE\_CFG command (0x81), in which case it will not be available as a GPIO pin. It can also be configured as a PWM output, which also would override its use as a GPIO pin.

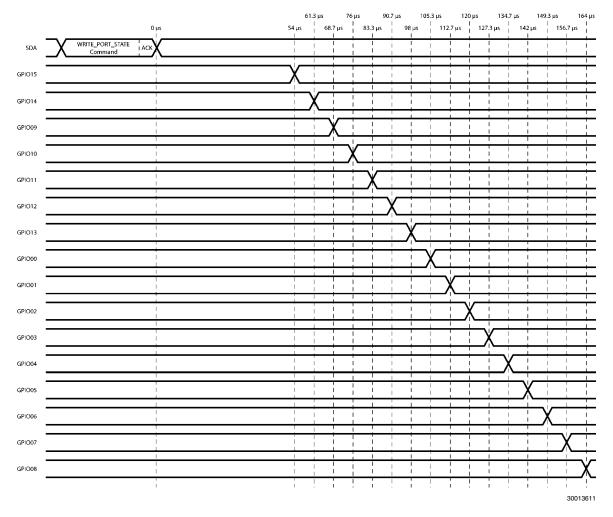

#### 13.2 GPIO TIMING

When a WRITE\_PORT\_STATE command (0x86) is received, the GPIO outputs do not change to their new states immediately or simultaneously. The first one changes 54  $\mu$ s after the command is acknowledged, and the others change at intervals of 7.3  $\mu$ s, as shown in *Figure 11*.

FIGURE 11. GPIO Port State Change Timing

# 14.0 PWM Output Generation

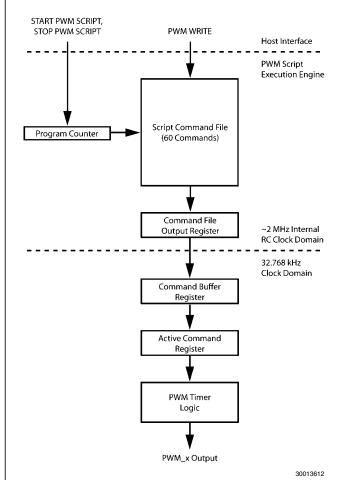

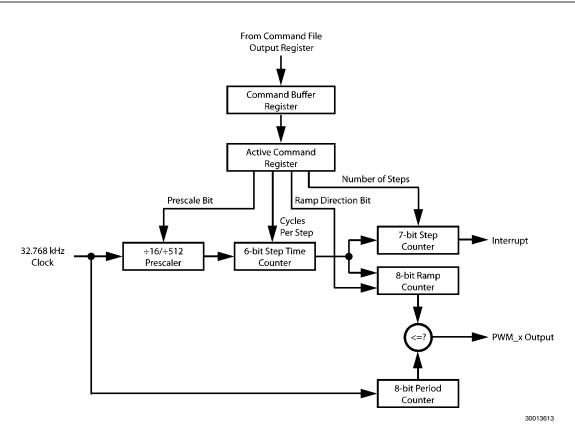

Three pulse-width modulated (PWM) outputs are provided with advanced capabilities for ramp-up and ramp-down of the PWM duty cycle and execution of simple to complex command sequences. These capabilities are supported by three independent script-execution engines capable of autonomous operation after setup and launch by the host. Figure 12 shows the architecture of a script-execution engine.

FIGURE 12. PWM Script Execution Engine

The host has three commands for interfacing to the script execution engine. The following commands are always associated with one particular PWM channel:

PWM\_WRITE — load one word into the script command file at a specified address.

- PWM\_START start execution of the script.

- PWM\_STOP stop execution of the script.

Please note: The PWM\_STOP command might not take immediate effect if the current command being executed is a command with long execution time. If a PWM\_STOP command is sent when the PWM engine is running a long RAMP command, the PWM will only stop after the RAMP is completed.

The script commands have their own fixed-length 16-bit format and encoding unrelated to the variable-length, byte-based format used for host commands. A script command is sent by the host to the LM8322 as a parameter to the PWM\_WRITE command. Another parameter to the PWM\_WRITE command specifies an address in the script command file for receiving the command.

#### **14.1 COMMAND QUEUE**

After the host issues a PWM\_START command, script commands are read from the script command file into a command queue which consists of a command file output register, command buffer, and active command register. This allows one command to be active while another command is queued in the command buffer, which allows seamless back-to-back command execution.

A command loaded into the command file output register is synchronized to the 32.768 kHz clock and stored in the command buffer. If no command is currently active, the command passes through to the active command register. In this case, another command can be read from the script command file, which is queued in the command buffer. On completion of the currently active command, the contents of the command buffer are transferred to the active command register, and the command buffer may then receive a new command.

The host does not have direct access to any of the registers in the command queue. The operations which read script commands from the script command file occur automatically after the host issues the PWM START command.

Script execution stops when the host sends a PWM\_STOP command or when the script engine executes an END command with the Reset bit set to 1. Executing an END command with the Reset bit set to "1" or the reception of a PWM\_STOP command asserts  $\overline{\text{IRQ}}$  to the host.

#### 14.2 PWM TIMER OPERATION

The timers implement a fixed 256-cycle period with a programmable duty cycle and programmable ramp-up/ramp-down of the duty cycle. *Figure 13* shows the architecture of a PWM timer.

FIGURE 13. PWM Timer

The period counter is a free running 8-bit up-counter which starts counting when the script command file issues the first RAMP command. An END command stops the period counter.

The duty cycle of the PWM output is controlled by the ramp counter. If the PWM period counter is active, the PWM output signal is asserted while the period counter has a value less than or equal to the value of the ramp counter.

The ramp counter can increment or decrement at a rate controlled by the prescaler and step time counter. The prescaler selects a factor of 16 or 512 for dividing down the frequency

of the 32.768 kHz clock. The ramp counter saturates at either 0x00 or 0xFF depending on the ramp direction.

The number of increment or decrement steps is specified by the INCREMENT field of the RAMP command, which is loaded into the step counter. Even if the ramp counter hits its saturation value, the requested number of steps will be performed. An option enables assertion of the  $\overline{\mbox{IRQ}}$  output to the host after the last step is performed.

#### 14.3 PWM SCRIPT COMMANDS

Table 8 summarizes the script commands.

**TABLE 8. PWM Script Commands**

| Command         | 15 | 14           | 13 | 12 | 11      | 10   | 9   | 8 | 7    | 6           | 5 | 4    | 3    | 2  | 1 | 0 |  |  |  |

|-----------------|----|--------------|----|----|---------|------|-----|---|------|-------------|---|------|------|----|---|---|--|--|--|

| RAMP            | 0  | PRES<br>CALE |    |    | STEPTIM | 1E   |     |   | SIGN |             |   | INCI | REME | NT |   |   |  |  |  |

| SET_PWM         | 0  | 1            |    |    | 0       |      |     |   |      | PWMVALUE    |   |      |      |    |   |   |  |  |  |

| GO_TO_<br>START |    |              |    |    |         |      |     | 0 |      |             |   |      |      |    |   |   |  |  |  |

| BRANCH          | 1  | 0            | 1  |    | LOC     | PCO  | UNT |   |      | 0 ADDRESS   |   |      |      |    |   |   |  |  |  |

| END             | 1  | 1            | 0  | 0  | RESET   |      |     |   |      | 0           |   |      |      |    |   |   |  |  |  |

| TRIGGER         | 1  | 1            | 1  |    | WAIT    | TRIG | GER |   |      | SENDTRIGGER |   |      |      |    |   | 0 |  |  |  |

#### 14.4 RAMP COMMAND

The RAMP command generates a duty-cycle ramp starting from the current value. At each step, the ramp counter is incremented or decremented by one, unless it has reached its its saturation value (0xFF for increment, or 0x00 for decrement). The time for one step is controlled by the PRESCALE bit and STEPTIME field. The minimum time for one step is 0.49 milliseconds. and the maximum time is about 1 second,

which supports both very fast and very slow ramps. The IN-CREMENT field specifies the number of steps to be executed by the command. The maximum value is 126, which corresponds to half of full scale.

There are two special cases in the instruction encoding. If all bits and fields are 0, it is interpreted as the GO TO START command. If the STEPTIME field is 0 but any other bit or field is non-zero, it is interpreted as the SET\_PWM command.

| 15 | 14       | 13 | 12 | 11   | 10   | 9 | 8 | 7    | 6 | 5 | 4   | 3     | 2  | 1 | 0 |

|----|----------|----|----|------|------|---|---|------|---|---|-----|-------|----|---|---|

| 0  | PRESCALE |    |    | STEF | TIME | : |   | SIGN |   |   | INC | CREME | NT |   |   |

| Bit or Field | Value | Description                                  |

|--------------|-------|----------------------------------------------|

| PRESCALE     | 0     | Divide the 32.768 kHz clock by 16            |

| FRESUALE     | 1     | Divide the 32.768 kHz clock by 512           |

| STEPTIME     | 1–63  | Number of prescaled clock cycles per step    |

| SIGN         | 0     | Increment ramp counter                       |

| SIGN         | 1     | Decrement ramp counter                       |

| INCREMENT    | 1–126 | Number of steps executed by this instruction |

#### 14.5 SET\_PWM COMMAND

The SET\_PWM command loads the ramp counter from the 8-bit DUTYCYCLE field in the instruction.

**Please note:** Only 0x00 and 0xFF are valid values for the duty cycle in SET\_PWM command. Other values can be estab-

lished by initializing the duty cycle to either 100% or 0% followed by a RAMP command.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|-------|------|---|---|---|

| 0  | 1  | 0  | 0  | 0  | 0  | 0 | 0 |   |   |   | DUTYC | YCLE |   |   |   |

| Bit or Field | Value | Description         |

|--------------|-------|---------------------|

| DUTYCYCLE    | 0     | Duty cycle is 0%.   |

| DOTTOTOLE    | 255   | Duty cycle is 100%. |

#### 14.6 GO\_TO\_START COMMAND

The GO\_TO\_START command jumps to the first command in the script command file.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    |    |    |    |    |    |   | 0 |   |   |   |   |   |   |   |   |

#### 14.7 BRANCH COMMAND

The BRANCH command jumps to the specified command in the script command file, with the option of looping for a specified number of repetitions. Nested loops are not allowed.

| 15 | 14 | 13 | 12 | 11 | 10   | 9     | 8 | 7 | 6 | 5 | 4 | 3   | 2    | 1 | 0 |

|----|----|----|----|----|------|-------|---|---|---|---|---|-----|------|---|---|

| 1  | 0  | 1  |    |    | LOOP | COUNT |   |   | 0 |   |   | ADD | RESS |   |   |

| Field     | Value | Description                                                                                                            |

|-----------|-------|------------------------------------------------------------------------------------------------------------------------|

| LOOPCOUNT | 0     | Loop until a STOP PWM SCRIPT command is issued by the host.                                                            |

| LOOPCOONT | 1–63  | Number of repetitions to perform, biased by -1. The range is 0–62 repetitions.                                         |

| ADDRESS   | 0–59  | Branch destination address in the script command file. If this field is greater than 59, no looping will be performed. |

#### 14.8 END COMMAND

The END command terminates script execution and asserts an interrupt to the host if the RESET bit is set to "1" or "0". If the END command is executed with the RESET bit set to "1", the PWM output will be disabled. If the RESET bit is "0" when executing the END command, the PWM channel remains active with the fixed duty cycle it was last set to.

**Please note:** If a PWM channel is waiting for the trigger (last executed command was "TRIGGER") and the script execution is halted then the "END" command can't be executed because the previous command is still pending. This is an exception - in this case the  $\overline{\mbox{IRQ}}$  signal will not be asserted.

| 15 | 14 | 13 | 12 | 11    | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|-------|----|---|---|---|---|---|---|---|---|---|---|

| 1  | 1  | 0  | 0  | RESET |    |   | - |   |   | 0 |   |   |   |   |   |

| Bit       | Value | Description                                                |  |  |  |

|-----------|-------|------------------------------------------------------------|--|--|--|

| RESET 0 1 |       | PWM_x output is active when script execution terminates.   |  |  |  |

|           |       | PWM_x output is Tristate when script execution terminates. |  |  |  |

#### 14.9 TRIGGER COMMAND

Triggers are used to synchronize operations between PWM channels. A TRIGGER command that sends a trigger takes sixteen 32.768 kHz clock cycles, and a command that waits for a trigger takes at least sixteen 32.768 kHz clock cycles.

A TRIGGER command that waits for a trigger (or triggers) will stall script execution until the trigger conditions are satisfied.

Then, it will clear the trigger(s) and continue to the next command.

When a trigger is sent, it is stored by the receiving channel and can only be cleared when the receiving channel executes a TRIGGER command that waits for the trigger.

| 15 | 14 | 13 | 12 | 11          | 10 | 9 | 8 | 7 | 6 | 5 | 4     | 3      | 2 | 1 | 0 |

|----|----|----|----|-------------|----|---|---|---|---|---|-------|--------|---|---|---|

| 1  | 1  | 1  |    | WAITTRIGGER |    |   |   |   |   | S | ENDTF | RIGGER | 3 |   | 0 |

| Field       | Value  | Description                     |  |  |

|-------------|--------|---------------------------------|--|--|

|             | 0001xx | Wait for trigger from channel 2 |  |  |

| WAITTRIGGER | 000xx1 | Wait for trigger from channel 0 |  |  |

| WAITINIGGEN | 000x1x | Wait for trigger from channel 1 |  |  |

|             | 000xx1 | Send trigger to channel 0       |  |  |

| SENDTRIGGER | 000x1x | Send trigger to channel 1       |  |  |

|             | 0001xx | Send trigger to channel 2       |  |  |

#### 14.10 PWM SCRIPT EXAMPLE

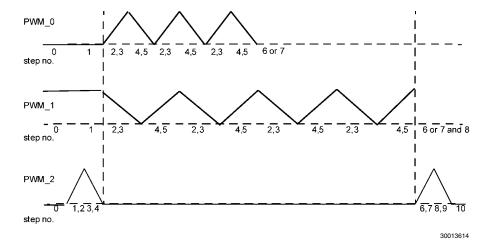

This example shows a complex ramping sequence that uses triggers for synchronization. Three scripts implement the example. *Figure 14* shows the PWM outputs for this example.

FIGURE 14. PWM Outputs

# 14.10.1 PWM Channel 0 Script

| Script<br>Command<br>Address | PWM_WRITE<br>Parameter 1 | PWM_WRITE<br>Parameter 2 | PWM_WRITE<br>Parameter 3 | Script<br>Command | Description                             |  |  |

|------------------------------|--------------------------|--------------------------|--------------------------|-------------------|-----------------------------------------|--|--|

| 0x00                         | 0x01                     | 0x40                     | 0x00                     | SET_PWM           | Initialize channel for 0% duty cycle    |  |  |

| 0x01                         | 0x05                     | 0xE2                     | 0x00                     | TRIGGER           | Wait for trigger from channel 2         |  |  |

| 0x02                         | 0x09                     | 0x07                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x03                         | 0x0D                     | 0x07                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x04                         | 0x11                     | 0x07                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0x05                         | 0x15                     | 0x07                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0x06                         | 0x19                     | 0xA1                     | 0x82                     | BRANCH            | Loop 2 times starting at address 0x02   |  |  |

| 0x07                         | 0x1D                     | 0xC8                     | 0x00                     | END               | Terminate script and assert IRQ to host |  |  |

# 14.10.2 PWM Channel 1 Script

| Script<br>Command<br>Address | PWM_WRITE<br>Parameter 1 | PWM_WRITE<br>Parameter 2 | PWM_WRITE<br>Parameter 3 | Script<br>Command | Description                             |

|------------------------------|--------------------------|--------------------------|--------------------------|-------------------|-----------------------------------------|

| 0x00                         | 0x02                     | 0x40                     | 0xFF                     | SET_PWM           | Initialize channel for 100% duty cycle  |

| 0x01                         | 0x06                     | 0xE2                     | 0x00                     | TRIGGER           | Wait for trigger from channel 2         |

| 0x02                         | 0x0A                     | 0x0F                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |

| 0x03                         | 0x0E                     | 0x0F                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |

| 0x04                         | 0x12                     | 0x0F                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |

| 0x05                         | 0x16                     | 0x0F                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |

| 0x06                         | 0x1A                     | 0xA2                     | 0x02                     | BRANCH            | Loop 3 times starting at address 0x02   |

| 0x07                         | 0x1E                     | 0xE0                     | 0x08                     | TRIGGER           | Send trigger to channel 2               |

| 0x08                         | 0x22                     | 0xC8                     | 0x00                     | END               | Terminate script and assert IRQ to host |

## 14.10.3 PWM Channel 2 Script

| Script<br>Command<br>Address | PWM_WRITE<br>Parameter 1 | PWM_WRITE<br>Parameter 2 | PWM_WRITE<br>Parameter 3 | Script<br>Command | Description                             |  |  |

|------------------------------|--------------------------|--------------------------|--------------------------|-------------------|-----------------------------------------|--|--|

| 0x00                         | 0x03                     | 0x40                     | 0x00                     | SET_PWM           | Initialize channel for 0% duty cycle    |  |  |

| 0x01                         | 0x07                     | 0x03                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x02                         | 0x0B                     | 0x03                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x03                         | 0x0F                     | 0x03                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0x04                         | 0x13                     | 0x03                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0.405                        | 0x17                     | 0xE1                     | 0x06                     | TRIGGER           | Send triggers to channels 0 and 1,      |  |  |

| 0x05                         | UX17                     | UXET                     | 0000                     | INIGGEN           | wait for trigger from channel 1         |  |  |

| 0x06                         | 0x1B                     | 0x03                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x07                         | 0x1F                     | 0x03                     | 0x7E                     | RAMP              | Ramp up by 126 steps                    |  |  |

| 0x08                         | 0x23                     | 0x03                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0x09                         | 0x27                     | 0x03                     | 0xFE                     | RAMP              | Ramp down by 126 steps                  |  |  |

| 0x0A                         | 0x2B                     | 0xC8                     | 0x00                     | END               | Terminate script and assert IRQ to host |  |  |

#### 14.11 SELECTABLE SCRIPT EXAMPLE

Multiple scripts can be placed in a single buffer. The script which is executed is selected by the address in the parameter to the PWM\_START command (0x96).

| Script<br>Command<br>Address | PWM_WRITE<br>Parameter 1                             | PWM_WRITE<br>Parameter 2 | PWM_WRITE<br>Parameter 3 | Script<br>Command | Description                                           |

|------------------------------|------------------------------------------------------|--------------------------|--------------------------|-------------------|-------------------------------------------------------|

| 0x00                         |                                                      | 0x01                     | 0x40                     | 0x00              | Set PWM_0 to 0% duty cycle                            |

| 0x01                         | Script 1                                             | 0x05                     | 0x0F                     | 0x33              | Ramp up 51 steps                                      |

| 0x02                         |                                                      | 0x09                     | 0xC0                     | 0x00              | Keep channel at 20% duty cycle                        |

| 0x03                         |                                                      | 0x0D                     | 0x40                     | 0xFF              | Set PWM_0 to 100% duty cycle                          |

| 0x04                         | Script 2                                             | 0x11                     | 0x0F                     | 0xD5              | Ramp down 85 steps                                    |

| 0x05                         |                                                      | 0x15                     | 0xC0                     | 0x00              | Keep channel at 66.6% duty cycle                      |

| 0x06                         |                                                      | 0x19                     | 0x40                     | 0x00              | Set PWM_0 to 0% duty cycle                            |

| 0x07                         |                                                      | 0x1D                     | 0x07                     | 0x7E              | Ramp up 126 steps                                     |

| 0x08                         | Cominst O                                            | 0x21                     | 0x07                     | 0x7E              | Ramp up 126 steps                                     |

| 0x09                         | Script 3                                             | 0x25                     | 0x07                     | 0xFE              | Ramp down 126 steps                                   |

| 0x0A                         |                                                      | 0x29                     | 0x07                     | 0xFE              | Ramp down 126 steps                                   |

| 0x0B                         |                                                      | 0x2D                     | 0xA5                     | 0x07              | Loop ten times to script address 0x07                 |

| 0x0C                         | Script 4                                             | 0x31                     | 0xC8                     | 0x00              | Switch PWM_0 off (script 3 automatically enters here) |

| 0x0D                         |                                                      | 0x35                     | 0x40                     | 0x00              | Set PWM_0 to 0% duty cycle                            |

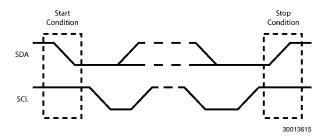

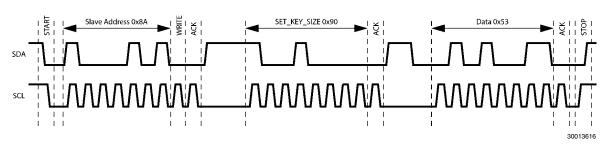

| 0x0E                         | Script 5                                             | 0x39                     | 0x07                     | 0x25              | Ramp up 37 steps                                      |