**Features**

## 1.8A Step-Down Regulator with Differential Remote Sense in 2mm x 2mm WLP

### **General Description**

The MAX8649 high-efficiency DC-to-DC step-down switching regulator delivers up to 1.8A of output current. The device operates from a 2.5V to 5.5V input voltage range, making it future proof for next-generation battery technologies. The output voltage is I<sup>2</sup>C programmable from 0.75V to 1.38V. Fully differential remote sense ensures precise DC regulation at the load. Total output error is less than 2% over load, line, and temperature.

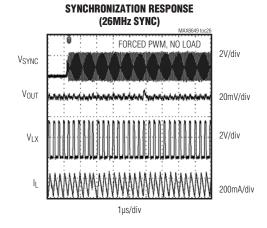

The MAX8649 operates at a 3.25MHz fixed frequency. The high operating frequency minimizes the size of external components. The switching frequency of the converter can be synchronized to the master clock of the application. When synchronizing to an external clock, the MAX8649 measures the frequency of the external clock to ensure that the clock is stable before changing the switching frequency to the external clock frequency.

An on-board DAC allows adjustment of the output voltage in 10mV steps. The output voltage can be programmed directly through the I<sup>2</sup>C interface, or by preloading a set of on-board registers and using the two VID logic signals to select the appropriate register. Other features include internal soft-start control circuitry to reduce inrush current, output overvoltage, overcurrent, and overtemperature protection.

### **Applications**

Cell Phones and Smartphones PDAs and MP3 Players

#### ♦ 1.8A Guaranteed Output Current

- ◆ I<sup>2</sup>C Programmable V<sub>OUT</sub> (750mV to 1.38V in 10mV Steps)

- ♦ Operates from 2.5V to 5.5V Input Supply

- ♦ On-Chip FET and Synchronous Rectifier

- ♦ Fixed 3.25MHz PWM Switching Frequency

- ♦ Synchronizes to 13MHz, 19.2MHz, or 26MHz System Clock when Available

- ♦ Small 1.0µH Inductor

- ♦ Initial Accuracy 0.5% at 1.25V Output

- ♦ 2% Output Accuracy Over Load, Line, and Temperature

- ♦ Power-Save Mode Increases Light Load Efficiency

- ♦ Overvoltage and Overcurrent Protection

- **♦ Thermal Shutdown Protection**

- ♦ 400kHz I<sup>2</sup>C Interface

- ♦ < 1µA Shutdown Current

</p>

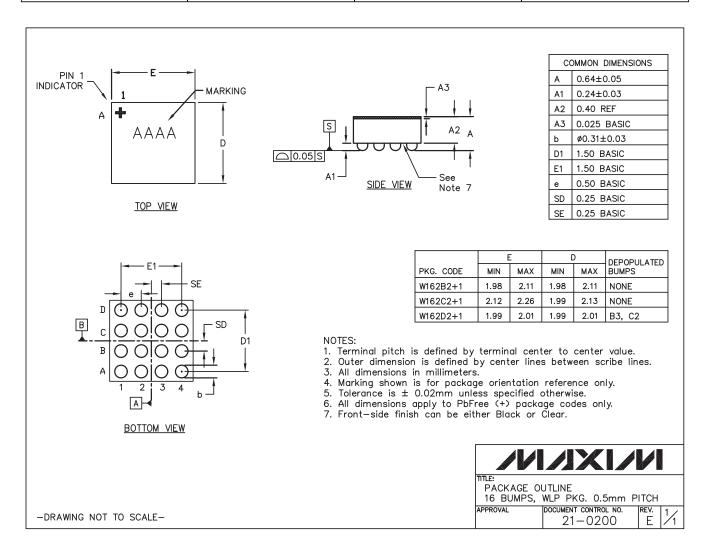

- ♦ 16-Bump, 2mm x 2mm WLP Package

### Ordering Information

| PART         | TEMP RANGE     | PIN-PACKAGE                  |

|--------------|----------------|------------------------------|

| MAX8649EWE+T | -40°C to +85°C | 16 Bump WLP<br>(0.5mm pitch) |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

### Pin Configuration

#### TOP VIEW (BUMPS ON BOTTOM VID1 AGND АЗ A1 A2 A4 SNS-FΝ LX В1 B2 ВЗ В4 PGND PGND SNS VID0 C1 C2 C3 C4 SDA SCL SYNC $V_{DD} \\$ D1 D3 D2 D4 WLP 0.5mm PITCH

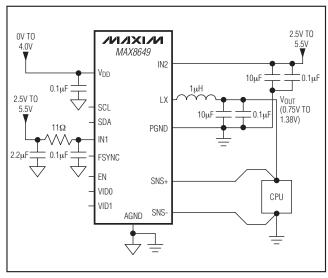

## Typical Operating Circuit

Maxim Integrated Products

1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN1, IN2 to AGND0.3V to +6.0V                              |

|------------------------------------------------------------|

| V <sub>DD</sub> to AGND0.3V to +4.0V                       |

|                                                            |

| LX, SNS+, VID0, VID1, EN to AGND0.3V to $(V_{IN1} + 0.3V)$ |

| SCL, SDA, SYNC to AGND0.3V to (V <sub>DD</sub> + 0.3V)     |

| PGND, SNS- to AGND0.3V to +0.3V                            |

| RMS LX Current                                             |

|                                                            |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )      |

| 16-Bump WLP 0.5mm Pitch                                    |

| (derate 13mW/°C above +70°C) 1040mW                        |

| Operating Temperature Range            | 40°C to +85°C                       |

|----------------------------------------|-------------------------------------|

| Junction to Ambient Thermal Resistance | e (θ <sub>JA</sub> ) (Note 1)76°C/W |

| Junction Temperature                   | +150°C                              |

| Storage Temperature Range              | 65°C to +150°C                      |

| Bump Temperature (soldering, reflow)   | +260°C                              |

|                                        |                                     |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN1} = V_{IN2} = 3.6V, V_{AGND} = V_{PGND} = 0V, V_{DD} = 1.8V, T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                | CONDITIONS                                                                                                  | 3                      | MIN                   | TYP   | MAX                 | UNITS |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------|---------------------|-------|--|

| IN1, IN2 Operating Range                                 |                                                                                                             |                        | 2.5                   |       | 5.5                 | V     |  |

| V <sub>DD</sub> Operating Range                          |                                                                                                             |                        | 1.8                   |       | 3.6                 | V     |  |

| V <sub>DD</sub> Undervoltage Lockout<br>(UVLO) Threshold | V <sub>DD</sub> falling                                                                                     |                        | 0.54                  | 0.865 | 1.35                | ٧     |  |

| V <sub>DD</sub> UVLO Hysteresis                          |                                                                                                             |                        |                       | 50    |                     | mV    |  |

| IN_ Undervoltage Lockout (UVLO) Threshold                | V <sub>IN</sub> falling                                                                                     |                        | 2.10                  | 2.15  | 2.20                | V     |  |

| IN_ UVLO Hysteresis                                      |                                                                                                             |                        |                       | 70    |                     | mV    |  |

| V <sub>DD</sub> Shutdown Supply Current                  | $V_{IN1} = V_{IN2} = 5.5V$ ,<br>$EN = V_{DD} = AGND$                                                        | $T_A = +25^{\circ}C$   |                       | 0.01  | 1                   | μΑ    |  |

| VDD Shataown Supply Carrent                              |                                                                                                             | T <sub>A</sub> = +85°C |                       | 0.01  |                     |       |  |

| IN1, IN2 Shutdown Supply                                 | $V_{IN1} = V_{IN2} = 5.5V,$                                                                                 | $T_A = +25^{\circ}C$   |                       | 0.25  | 1                   | - μΑ  |  |

| Current                                                  | $EN = V_{DD} = AGND$                                                                                        | $T_A = +85^{\circ}C$   |                       | 0.25  |                     |       |  |

| IN1, IN2 Standby Supply Current                          | V <sub>IN1</sub> = V <sub>IN2</sub> = 5.5V, SCL = SDA = V <sub>DD</sub> , EN = AGND, I <sup>2</sup> C ready | T <sub>A</sub> = +25°C |                       | 0.35  | 1                   | μΑ    |  |

| INT, INZ Standby Supply Current                          |                                                                                                             | T <sub>A</sub> = +85°C |                       | 0.35  |                     |       |  |

| V <sub>DD</sub> Standby Supply Current                   | $V_{IN1} = V_{IN2} = V_{DD} = 3.6V$ ,                                                                       | T <sub>A</sub> = +25°C |                       | 0.02  | 1                   | μΑ    |  |

| VDD Standby Supply Current                               | $SCL = SDA = V_{DD}$ , $EN = AGND$ , $I^2C$ ready                                                           | T <sub>A</sub> = +85°C |                       | 0.02  |                     |       |  |

| LOGIC INTERFACE                                          |                                                                                                             |                        |                       |       |                     |       |  |

| Logic Input High Voltage (VIH)                           | $V_{IN1} = V_{IN2} = 2.5V \text{ to } 5.5V,$                                                                | EN, VID0, VID1         | 1.4                   |       |                     | V     |  |

| Logic input High Voltage (VIH)                           | $V_{DD} = 1.8V \text{ to } 3.6V$                                                                            | SYNC, SCL, SDA         | 0.7 x V <sub>DD</sub> |       |                     | V     |  |

| Lagia lagust Lagus Valtaga (V.)                          | $V_{IN1} = V_{IN2} = 2.5V \text{ to } 5.5V,$                                                                | EN, VID0, VID1         |                       |       | 0.4                 | V     |  |

| Logic Input Low Voltage (V <sub>IL</sub> )               | $V_{DD} = 1.8V \text{ to } 3.6V$                                                                            | SYNC, SCL, SDA         |                       |       | $0.3 \times V_{DD}$ | v     |  |

| SDA, SCL, SYNC Logic Input                               | $V_{IL} = 0V \text{ or } V_{IH} = 3.6V,$                                                                    | $T_A = +25^{\circ}C$   | -1                    | 0.01  | +1                  |       |  |

| Current                                                  | EN = AGND                                                                                                   | $T_A = +85^{\circ}C$   |                       | 0.01  |                     | μA    |  |

! \_\_\_\_\_\_NIXI/N

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = 3.6V, V_{AGND} = V_{PGND} = 0V, V_{DD} = 1.8V, T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                            | CONDITIONS                                                                         | MIN   | TYP   | MAX   | UNITS |

|------------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VID0, VID1, EN Logic Input<br>Pulldown Resistor      | Controlled by I <sup>2</sup> C command:<br>VID0_PD = 1<br>VID1_PD = 1<br>EN_PD = 1 | 200   | 320   | 450   | kΩ    |

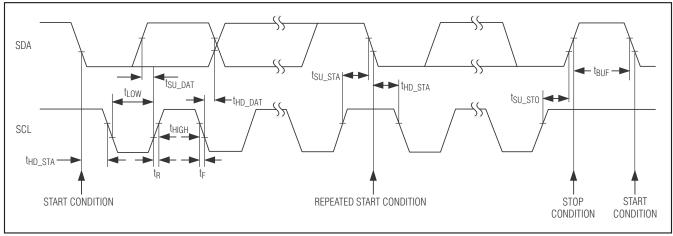

| I <sup>2</sup> C INTERFACE                           |                                                                                    | •     |       |       |       |

| SDA Output Low Voltage                               | I <sub>SDA</sub> = 3mA                                                             |       | 0.03  | 0.4   | V     |

| I <sup>2</sup> C Clock Frequency                     |                                                                                    |       |       | 400   | kHz   |

| Bus-Free Time Between START and STOP                 | tBUF                                                                               | 1.3   |       |       | μs    |

| Hold Time Repeated START<br>Condition                | thd_STA                                                                            | 0.6   | 0.1   |       | μs    |

| SCL Low Period                                       | t <sub>LOW</sub>                                                                   | 1.3   | 0.2   |       | μs    |

| SCL High Period                                      | thigh                                                                              | 0.6   | 0.2   |       | μs    |

| Setup Time Repeated START Condition                  | tsu_sta                                                                            | 0.6   | 0.1   |       | μs    |

| SDA Hold Time                                        | thd_dat                                                                            | 0     | -0.01 |       | μs    |

| SDA Setup Time                                       | tsu_dat                                                                            | 0.1   | 0.05  |       | μs    |

| Setup Time for STOP Condition                        | tsu_sto                                                                            | 0.6   | 0.1   |       | μs    |

| STEP-DOWN DC-DC REGULATO                             | DR .                                                                               |       |       |       |       |

| IN1 + IN2                                            | OPERATION_MODE_ = 0, V <sub>OUT</sub> = 1.27V, no switching                        |       | 54    | 70    | μΑ    |

| Supply Current                                       | OPERATION_MODE_ = 1, V <sub>OUT</sub> = 1.27V, f <sub>SW</sub> = 3.25MHz           |       | 9     |       | mA    |

| Minimum Output Capacitance<br>Required for Stability | $V_{OUT} = 0.75V \text{ to } 1.38V,$ $I_{OUT} = 0 \text{ to } 1.8A$                |       | 10    |       | μF    |

| OUT Voltage Range                                    | 10mV steps                                                                         | 0.750 |       | 1.380 | V     |

| Output Overvoltage Protection                        | Rising, 50mV hysteresis (typ)                                                      | 1.65  | 1.8   | 1.9   | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = 3.6V, V_{AGND} = V_{PGND} = 0V, V_{DD} = 1.8V, T_{A} = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{A} = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                  | CONDIT                                                                      | TIONS                                 | MIN   | TYP                | MAX  | UNITS  |

|--------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------|-------|--------------------|------|--------|

|                                            | No load, V <sub>IN</sub> = 2.5V to 5.5V, V<br>OPERATION_MODE_ = 1           | OUT = 1.27V                           | -0.5  |                    | +0.5 |        |

| OUT Voltage Accuracy                       | I <sub>OUT</sub> = no load, V <sub>IN</sub> _ = 2.5V to OPERATION_MODE_ = 1 | $5.5V$ , $V_{OUT} = 0.75V$ ,          | -1.0  |                    | +1.0 | %      |

|                                            | I <sub>OUT</sub> = no load, V <sub>IN</sub> _ = 2.5V to OPERATION_MODE_ = 1 | $5.5V, V_{OUT} = 1.38V,$              | -0.5  |                    | +0.5 |        |

| Load Regulation                            | R <sub>L</sub> is the resistance from LX to                                 | SNS+ (output)                         |       | R <sub>L</sub> /25 |      | V/A    |

|                                            | RAMP[2:0] = 000                                                             |                                       |       | 32.50              |      |        |

|                                            | RAMP[2:0] = 001                                                             |                                       |       | 16.25              |      |        |

|                                            | RAMP[2:0] = 010                                                             |                                       |       | 8.125              |      |        |

| RAMP Timer                                 | RAMP[2:0] = 011                                                             |                                       |       | 4.063              |      | mV/µs  |

| HAMP Timer                                 | RAMP[2:0] = 100                                                             |                                       |       | 2.031              |      | ΠΙV/μS |

|                                            | RAMP[2:0] = 101                                                             |                                       |       | 1.016              |      |        |

|                                            | RAMP[2:0] = 110                                                             |                                       | 0.508 |                    |      |        |

|                                            | RAMP[2:0] = 111                                                             | 0.254                                 |       |                    |      |        |

| Peak Current Limit<br>(p-Channel MOSFET)   | PWM and hysteretic mode                                                     | PWM and hysteretic mode               |       |                    |      | А      |

| Valley Current Limit<br>(n-Channel MOSFET) | Hysteretic mode                                                             |                                       | 1.8   | 2.4                | 3.0  | А      |

| Negative Current Limit (n-Channel MOSFET)  | PWM mode                                                                    |                                       | 2.0   | 2.5                | 3.0  | А      |

| n-Channel Zero-Crossing<br>Threshold       |                                                                             |                                       |       | 50                 | 0.16 | mA     |

| LX pFET On-Resistance                      | IN2 to LX, I <sub>LX</sub> = -200mA                                         |                                       |       | 0.08               | 0.16 | Ω      |

| LX nFET On-Resistance                      | OPERATION_MODE = 0<br>LX to PGND, I <sub>LX</sub> = 200mA                   |                                       |       | 0.06               | 0.12 | Ω      |

| LVIl                                       | V 5 5V - 20V                                                                | T <sub>A</sub> = +25°C                | -1    | 0.03               | +1   |        |

| LX Leakage                                 | $V_{LX} = 5.5V \text{ or } 0V$                                              | T <sub>A</sub> = +85°C                |       | 0.05               |      | μΑ     |

|                                            | Internal oscillator, PWM                                                    |                                       | 2.82  | 3.25               | 3.56 |        |

|                                            | Internal oscillator, power-save mode before entering PWM mode               |                                       | 2.43  | 3.25               | 4.06 |        |

| Operating Frequency                        | 13MHz option                                                                | 13MHz option                          |       |                    |      | MHz    |

|                                            | 19.2MHz option                                                              | · · · · · · · · · · · · · · · · · · · |       |                    |      |        |

|                                            | 26MHz option                                                                | ·                                     |       |                    |      |        |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN1} = V_{IN2} = 3.6V, V_{AGND} = V_{PGND} = 0V, V_{DD} = 1.8V, T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are at } T_{A} = +25^{\circ}C.) \text{ (Note 2)}$

| PARAMETER                                 | CONDITIONS                                                             | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|------------------------------------------------------------------------|------|------|------|-------|

| Minimum Duty Cycle                        | Forced PWM mode only, minimum duty cycle in (OPERATION_MODE_ = 1) = 0% |      |      | 16   | %     |

| Maximum Duty Cycle                        |                                                                        | 60   |      |      | %     |

| Minimum On- and Off-Time                  |                                                                        | 30   | 40   | 50   | ns    |

| OUT Discharge Resistance                  | During shutdown or UVLO, from SNS+ to PGND                             |      | 650  |      | Ω     |

| SNS+, SNS- Input Impedance                |                                                                        | 400  | 600  | 850  | kΩ    |

| Time Delay from PWM to Power-Save Mode    | Time required for error amplifier to stabilize before switching mode   |      | 70   |      | μs    |

| Time Delay from Power-Save<br>Mode to PWM | Time required for error amplifier to stabilize before switching mode   |      | 140  |      | μs    |

| SYNCHRONIZATION (SYNC)                    | ·                                                                      | *    |      |      |       |

|                                           | SYNC = 00 default                                                      | 18.9 | 26.0 | 38.0 |       |

| SYNC Capture Range                        | SYNC = 1X default                                                      | 14.2 | 19.2 | 28.5 | MHz   |

|                                           | SYNC = 01 default                                                      | 9.5  | 13.0 | 19.0 |       |

| SYNC Pulse Width                          |                                                                        |      | 13   |      | ns    |

| PROTECTION CIRCUITS                       |                                                                        |      |      |      |       |

| Thermal-Shutdown Hysteresis               |                                                                        |      | 20   |      | °C    |

| Thermal Shutdown                          |                                                                        |      | +160 |      | °C    |

**Note 2:** All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

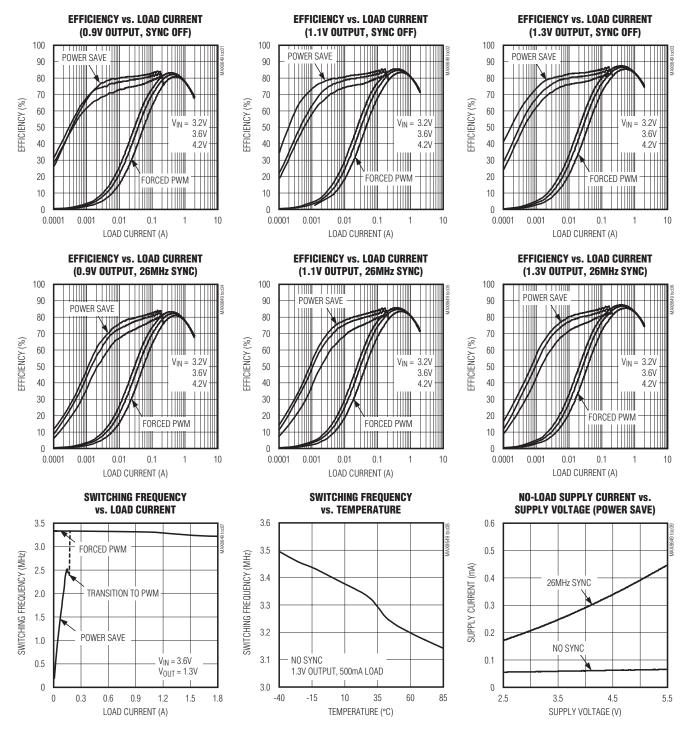

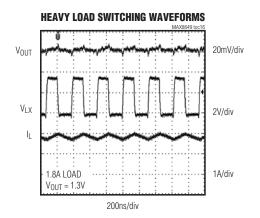

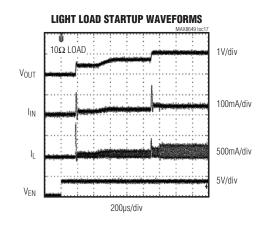

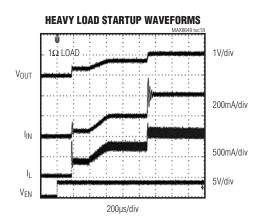

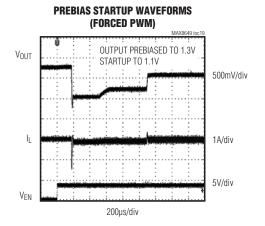

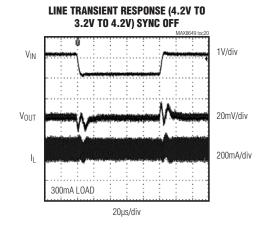

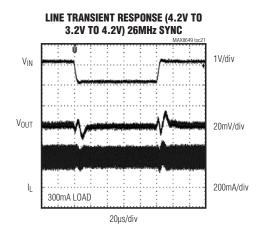

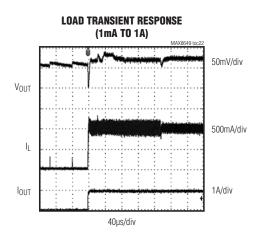

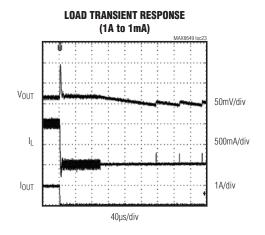

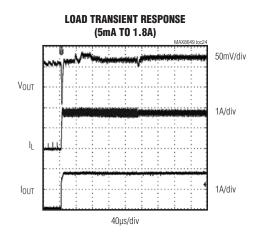

### Typical Operating Characteristics

(Typical Operating Circuit,  $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.1V$ ,  $V_{DD} = 1.8V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

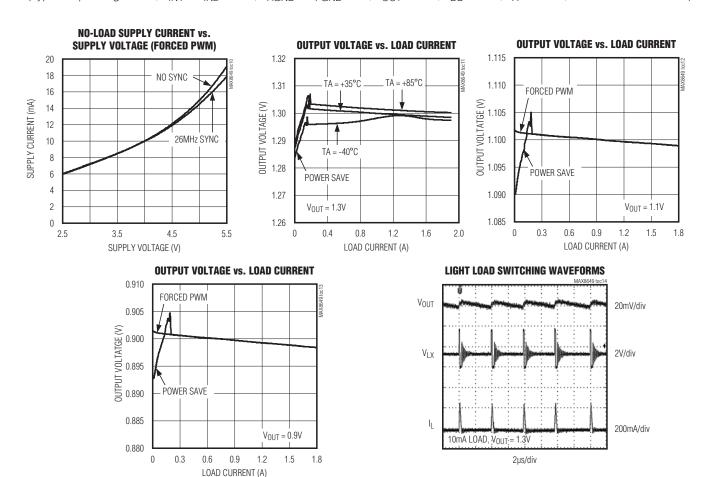

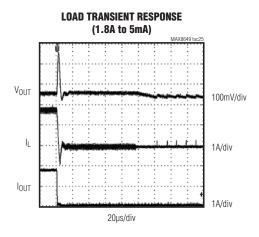

### Typical Operating Characteristics (continued)

(Typical Operating Circuit, V<sub>IN1</sub> = V<sub>IN2</sub> = 3.6V, V<sub>AGND</sub> = V<sub>PGND</sub> = 0V, V<sub>OUT</sub> = 1.1V, V<sub>DD</sub> = 1.8V, T<sub>A</sub> = +25°C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(Typical Operating Circuit,  $V_{IN1} = V_{IN2} = 3.6V$ ,  $V_{AGND} = V_{PGND} = 0V$ ,  $V_{OUT} = 1.1V$ ,  $V_{DD} = 1.8V$ ,  $V_{AB} = +25^{\circ}C$ , unless otherwise noted.)

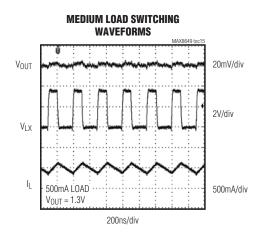

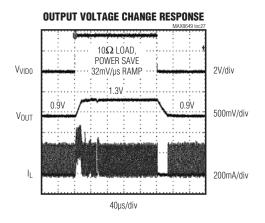

**Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Bump Description**

| ВИМР   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1     | IN1             | Analog Supply Voltage Input. The input voltage range is 2.5V to 5.5V. Place an $11\Omega$ resistor between IN1 and the input supply. Bypass the input supply with a 2.2 $\mu$ F ceramic capacitor as close as possible to the $11\Omega$ resistor. Bypass IN1 to the 2.2 $\mu$ F capacitor ground plane terminal with a 0.1 $\mu$ F ceramic capacitor as close as possible to the IC. Connect IN1 and IN2 to the same power source. |

| A2     | AGND            | Analog Ground. Connect AGND to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                |

| A3     | VID1            | Voltage ID Control Input. The logic states of VID0 and VID1 select the register that sets the output voltage.                                                                                                                                                                                                                                                                                                                       |

| A4     | IN2             | Power-Supply Voltage Input. The input voltage range is from 2.5V to 5.5V. IN2 powers the internal p-channel and n-channel MOSFETs. Bypass IN2 to PGND with 10µF and 0.1µF ceramic capacitors as close as possible to the IC. Connect IN1 and IN2 to the same power source.                                                                                                                                                          |

| B1     | SNS+            | Output Voltage Remote Sense, Positive Input. Connect SNS+ directly to the output at the load.                                                                                                                                                                                                                                                                                                                                       |

| B2     | EN              | Logic Enable Input. Drive EN high to enable the DC-DC step-down regulator, or low to place in shutdown mode. In shutdown mode, this logic input has an internal pulldown resistor to AGND.                                                                                                                                                                                                                                          |

| B3, B4 | LX              | Inductor Connection. LX is connected to the drains of the internal p-channel and n-channel MOSFETs. LX is high impedance during shutdown.                                                                                                                                                                                                                                                                                           |

| C1     | SNS-            | Output Voltage Remote Sense, Negative Input. Connect to a quiet ground directly at the load.                                                                                                                                                                                                                                                                                                                                        |

| C2     | VID0            | Voltage ID Control Input. The logic states of VID0 and VID1 select the register that sets the output voltage.                                                                                                                                                                                                                                                                                                                       |

| C3, C4 | PGND            | Power Ground. Connect both PGND bumps to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                      |

| D1     | V <sub>DD</sub> | Logic Input Supply Voltage. Connect $V_{DD}$ to the logic supply driving SDA, SCL, and SYNC. Bypass $V_{DD}$ to AGND with a 0.1µF ceramic capacitor. When $V_{DD}$ drops below the UVLO threshold, the I <sup>2</sup> C registers are reset, but the EN control is still active in this mode.                                                                                                                                       |

| D2     | SDA             | I <sup>2</sup> C Data Input. Data is read on the rising edge of SCL and data is clocked out on the falling edge of SCL.                                                                                                                                                                                                                                                                                                             |

| D3     | SCL             | I <sup>2</sup> C Clock Input                                                                                                                                                                                                                                                                                                                                                                                                        |

| D4     | SYNC            | External Clock Synchronization Input. Connect SYNC to a 13MHz, 19.2MHz, or 26MHz system clock. The DC-DC regulator can be forced to synchronize to this external clock depending on I <sup>2</sup> C setting. See Table 8. SYNC does not have an internal pulldown. Connect SYNC to AGND if not used.                                                                                                                               |

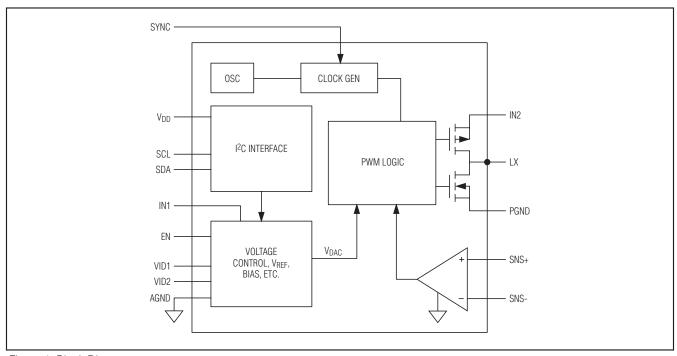

Figure 1. Block Diagram

## **Detailed Description**

The MAX8649 high-efficiency, 3.25MHz step-down switching regulator delivers up to 1.8A of output current. The device operates from a 2.5V to 5.5V input voltage range, and the output voltage is I<sup>2</sup>C programmable from 0.75V to 1.38V in 10mV increments. Fully differential remote sense ensures precise DC regulation at the load. Total output error is less than 2% over load, line, and temperature.

#### **Dynamic Voltage Scaling**

The output voltage is dynamically adjusted by use of the VID0 and VID1 logic inputs, allowing selection between four predefined operation modes/voltage configurations. For each of the different output modes, the following parameters are programmable:

- Output voltage from 0.75V to 1.38V in 10mV steps

- Mode of operation: Forced PWM or power save

- Enable/disable of synchronization of switching frequency to external clock source

The relation between the VID0/VID1 and operation mode is given by Table 1.

The VID\_ inputs have internal pulldown resistors. These pulldown resistors can be disabled through the CONTROL register after the MAX8649 is enabled, achieving lowest possible quiescent current. When EN is low, the CONTROL register is reset to default, enabling the pulldown resistors (see Table 7).

Table 1. VID0 and VID1 Configuration

| VID1 | VID0 | MODE  | I <sup>2</sup> C REGISTER | DEFAULT<br>SWITHCING<br>MODE | DEFAULT<br>SYNCHRONIZATION | DEFAULT<br>OUTPUT<br>VOLTAGE (V) |

|------|------|-------|---------------------------|------------------------------|----------------------------|----------------------------------|

| 0    | 0    | MODE0 | Table 3                   | FORCED PWM                   | OFF                        | 1.27                             |

| 0    | 1    | MODE1 | Table 4                   | POWER SAVE                   | OFF                        | 1.05                             |

| 1    | 0    | MODE2 | Table 5                   | FORCED PWM                   | OFF                        | 1.23                             |

| 1    | 1    | MODE3 | Table 6                   | FORCED PWM                   | OFF                        | 1.05                             |

#### **Enable**

The MAX8649 DC-DC step-down regulator is enabled/disabled using the EN logic input. The EN input is able to handle input voltages up to  $V_{\rm IN1}$ , ensuring that the EN logic input can be controlled by a wide variety of signals/supplies.

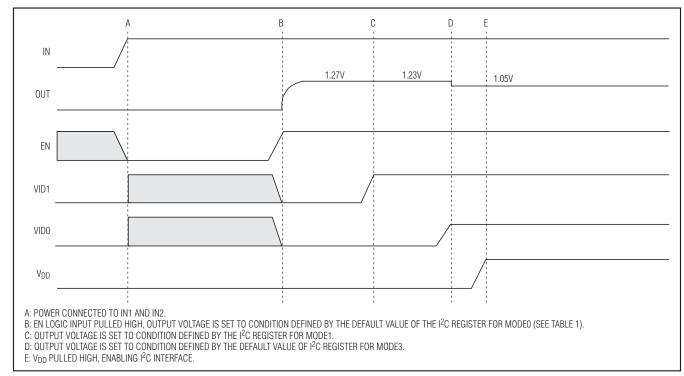

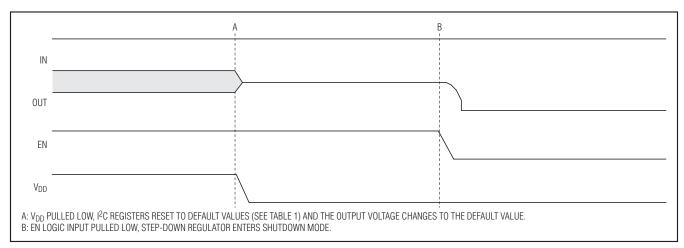

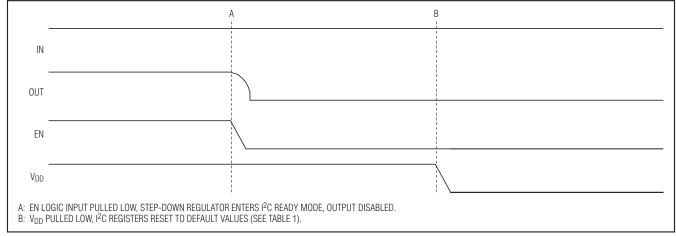

The EN input has an internal pulldown resistor that ensures EN is discharged during off conditions. This pulldown resistor can be disabled through the CONTROL register (see Table 7) once the MAX8649 is enabled, achieving lowest possible quiescent current. When EN is low, the CONTROL register is reset to default, enabling the pulldown resistors on EN, VIDO, and VID1. See Figures 2 and 3 for detailed information on power-up and power-down sequencing and operation mode changes.

#### **DC-DC Regulator Operating Modes**

The MAX8649 operates in one of four modes determined by the state of the VID\_ inputs (see Table 1). At power-up, the MAX8649 is default set to operate in power-save operation for MODE1 and forced-PWM mode for MODE0, MODE2, and MODE3. For each of the operation modes, MODE0 to MODE3, the MAX8649 DC-DC step-down regulator can be set to operate in either power-save mode or forced-PWM mode. This is

done by writing to the MODE\_ registers (see Table 3 to Table 6). The mode of operation can be changed at any time.

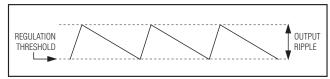

In power-save mode, the MAX8649 PWM switching frequency depends on the load current. For medium to high load condition, the MAX8649 operates in fixedfrequency PWM mode. For light load conditions, the MAX8649 operates in hysteretic mode. The proprietary hysteretic PWM control scheme ensures high efficiency, fast switching, and fast transient response. This control scheme is simple: when the output voltage is below the regulation threshold, the error comparator begins a switching cycle by turning on the high-side switch. This switch remains on until the minimum ontime expires and the output voltage is above the regulation threshold plus hysteresis or the inductor current is above the current-limit threshold. Once off, the highside switch remains off until the minimum off-time expires and the output voltage falls again below the regulation threshold. During the off period, the lowside synchronous rectifier turns on and remains on until either the high-side switch turns on again or the inductor current approaches zero. The internal synchronous rectifier eliminates the need for an external Schottky diode.

Figure 2. Power-Up Sequence

12 \_\_\_\_\_\_\_/N/XI/M

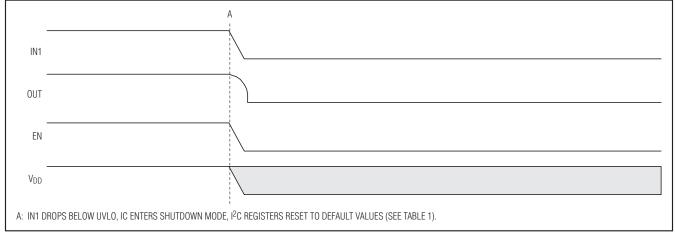

Figure 3a. Shutdown by Pulling V<sub>DD</sub> Low Before EN

Figure 3b. Shutdown by Pulling EN Low Before V<sub>DD</sub>

Figure 3c. Shutdown Due to IN1 Undervoltage Lockout

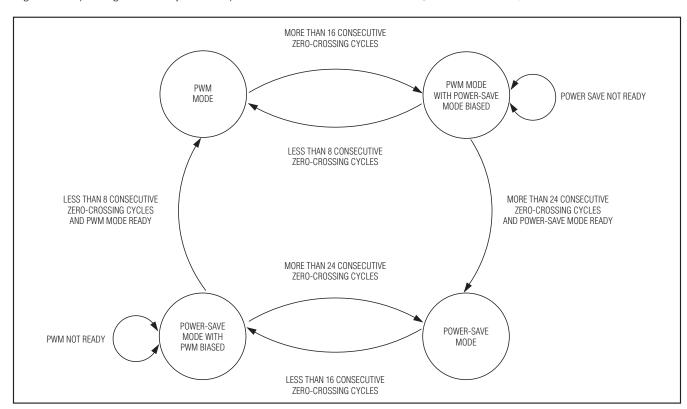

The transition between PWM and hysteretic operation is based on the number of consecutive zero-crossing cycles. When more than 16 consecutive zero-crossing cycles are detected, the DC-DC step-down converter enables the bias for hysteretic operation. Once correctly biased and the number of consecutive zero-crossing cycles exceeds 24, the DC-DC step-down converter begins hysteretic operation.

During hysteretic operation, there is a silent DC offset due to the use of valley regulation. See Figure 4.

When operating in power-save mode and the load current is increased so that the number of consecutive zero-crossing cycles is less than 16, the PWM mode is biased. Once fully biased and the number of zero-crossing cycles drops below 8, the DC-DC converter then begins PWM operation. Since there is a delay between the increase in load current and the

Figure 4. Output Regulation in Hysteretic Operation

DC-DC converter starting PWM, the converter supports full current on the output during hysteretic operation. See Figure 5 for a detailed state diagram.

Power-save operation offers improved efficiency at light loads by changing to hysteretic mode, reducing the switching frequency depending on the load condition. With moderate to heavy loading, the regulator switches at a fixed switching frequency as it does in forced-PWM mode. In power-save mode, the transition from hysteretic mode to fixed-frequency switching occurs at the load current specified in the following equation:

$$I_{OUT} = \frac{V_{IN} - V_{OUT}}{2 \times L} \times \frac{V_{OUT}}{V_{IN} \times f_{OSC}}$$

In forced-PWM mode, the regulator operates with a constant (3.25MHz or synchronized to external clock source) switching frequency regardless of output load.

Forced-PWM mode is ideal for low-noise systems because switching harmonics occur at multiples of the constant switching frequency and are easily filtered. However, light-load power consumption in forced-PWM mode is higher than that of power-save mode.

Figure 5. Mode Change for DC-DC Step-Down Converter

14 \_\_\_\_\_\_\_ /I/XI/M

#### Soft-Start

The MAX8649 includes internal soft-start circuitry that eliminates inrush current at startup, reducing transients on the input source (see the *Typical Operating Characteristics*). Soft-start is particularly useful for high-impedance input sources, such as Li+ and alkaline cells. When enabling the MAX8649 into a prebiased output, the MAX8649 performs a complete soft-start cycle.

#### **Synchronous Rectification**

An internal n-channel synchronous rectifier eliminates the need for an external Schottky diode and improves efficiency. The synchronous rectifier turns on during the second half of each switching cycle (off-time). During this time, the voltage across the inductor is reversed, and the inductor current ramps down. In PWM mode, the synchronous rectifier turns off at the end of the switching cycle. In power-save mode, the synchronous rectifier turns off when the inductor current falls below 50mA (typ) or at the end of the switching cycle, whichever occurs first.

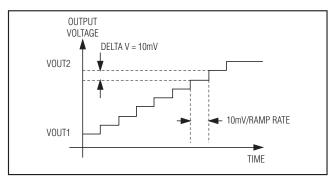

#### Ramp-Rate Control

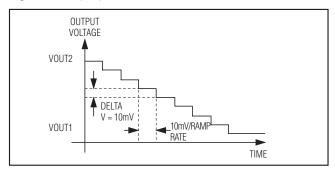

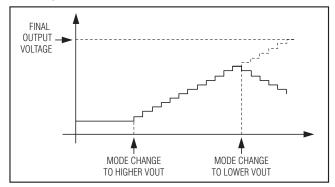

The MAX8649 output voltage has an actively controlled variable ramp rate, set with the  $I^2C$  interface (see Figures 6, 7, and 8). The value set in the RAMP register controls the output voltage ramp rate. The RAMP\_DOWN bit controls the active ramp-down

Figure 6. Ramp-Up Function

Figure 7. Ramp-Down Function

behavior in power-save mode. When the regulator is set for power-save mode and the RAMP\_DOWN bit is cleared, the ramp-down is not actively controlled, and the regulator output voltage ramps down at the rate determined by the output capacitance and the external load. Small loads result in an output-voltage decay that is slower than that specified by RAMP; large loads result in an output-voltage decay that is no faster than that specified by RAMP When the RAMP\_DOWN bit is set in power-save mode, the zero-cross comparator is disabled during the ramp-down condition. Active ramp-down functionality is inherent in forced-PWM operation.

Calculate the maximum and minimum values for the ramp rate as follows:

$$t_{RAMP\_MIN} = \frac{V_{OUT\_LSB}}{t_{CLK\_MAX}} \times \frac{1}{2^{RAMP\_CODE}}$$

$$t_{RAMP\_MAX} = \frac{V_{OUT\_LSB}}{t_{CLK\_MIN}} \times \frac{1}{2^{RAMP\_CODE}}$$

where:

$$\begin{aligned} &V_{OUT\_LSB} = 10 mV \\ &t_{CLK\_MAX} = \frac{1}{f_{SW\_MIN}} \\ &t_{CLK\_MIN} = \frac{1}{f_{SW\_MAX}} \end{aligned}$$

$f_{SW} = 3.25 MHz \pm 10\%$  for PWM operation  $f_{SW} = 3.25 MHz \pm 25\%$  for hysteretic operation

$$f_{SW} = \frac{f_{SYNC}}{n}$$

fsync = frequency of external clock n = 4 for 13MHz, 6 for 19.2MHz, and 8 for 26MHz RAMP\_CODE = value of the RAMP[2:0] register (see Table 9)

Figure 8. Mode Change Before Final Value is Reached

Figure 9. I<sup>2</sup>C Bit Transfer

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the MAX8649. When internal thermal sensors detect a die temperature in excess of +160°C (typ), the DC-DC step-down regulator is shut down, allowing the IC to cool. The DC-DC step-down regulator is turned on again after the junction cools by 20°C (typ), resulting in a pulsed output during continuous thermal-overload conditions.

During thermal overload, the I<sup>2</sup>C interface remains active and all register values are maintained.

#### I<sup>2</sup>C Interface

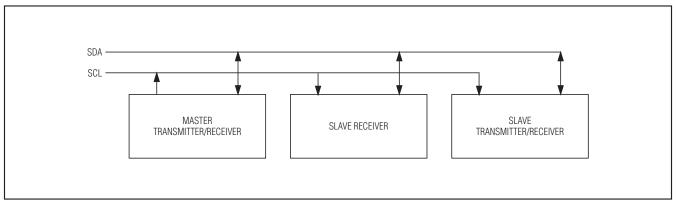

An I<sup>2</sup>C-compatible, 2-wire serial interface controls the step-down converter output voltage, ramp rate, operating mode, and synchronization. The serial bus consists of a bidirectional serial-data line (SDA) and a serial-clock input (SCL). The master initiates data transfer on the bus and generates SCL to permit data transfer.

$I^2C$  is an open-drain bus. SDA and SCL require pullup resistors (500 $\Omega$  or greater). Optional (24 $\Omega$ ) in series with SDA and SCL protect the device inputs from high-voltage spikes on the bus lines. Series resistors also minimize crosstalk and undershoot on bus signals.

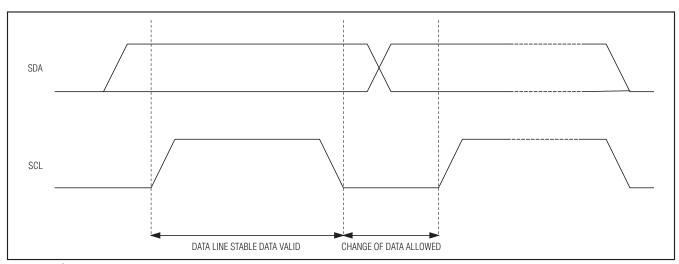

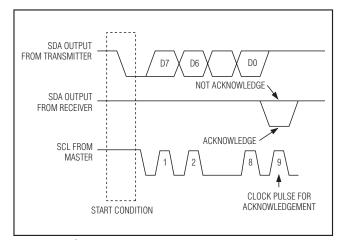

#### Bit Transfer

One data bit is transferred during each SCL clock cycle. The data on SDA must remain stable during the high period of the SCL clock pulse (see Figure 9). Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section for more information).

Each transmit sequence is framed by a START (S) condition and a STOP (P) condition. Each data packet is 9 bits long; 8 bits of data followed by the acknowledge bit. The MAX8649 supports data transfer rates with SCL frequencies up to 400kHz.

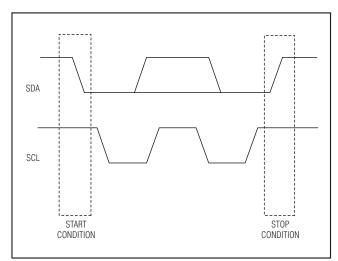

#### START and STOP Conditions

When the serial interface is inactive, SDA and SCL idle high. A master device initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA, while SCL is high (Figure 10).

Figure 10. I<sup>2</sup>C START and STOP Conditions

16 \_\_\_\_\_\_\_ /V|/X|/V|

Figure 11. I<sup>2</sup>C Master/Slave Configuration

A START condition from the master signals the beginning of a transmission to the MAX8649. The master terminates transmission by issuing a not acknowledge followed by a STOP condition (see the *Acknowledge* section for more information). The STOP condition frees the bus. To issue a series of commands to the slave, the master can issue REPEATED START (Sr) commands instead of a STOP command to maintain control of the bus. In general, a REPEATED START command is functionally equivalent to a regular START command.

When a STOP condition or incorrect address is detected, the MAX8649 internally disconnects SCL from the serial interface until the next START condition, minimizing digital noise and feedthrough.

#### System Configuration

A device on the I<sup>2</sup>C bus that generates a message is called a transmitter and a device that receives the message is a receiver. The device that controls the message is the master and the devices that are controlled by the master are called slaves. See Figure 11.

#### Acknowledge

The number of data bytes between the START and STOP conditions for the transmitter and receiver are unlimited. Each 8-bit byte is followed by an acknowledge bit. The acknowledge bit is a high-level signal put on SDA by the transmitter during which time the master generates an extra acknowledge-related clock pulse. A slave receiver that is addressed must generate an acknowledge after each byte it receives. Also, a master receiver must generate an acknowledge after each byte it receives that has been clocked out of the slave transmitter. See Figure 12.

Figure 12. I<sup>2</sup>C Acknowledge

The device that acknowledges must pull down the DATA line during the acknowledge clock pulse, so that the DATA line is stable low during the high period of the acknowledge clock pulse (setup and hold times must also be met). A master receiver must signal an end of data to the transmitter by not generating an acknowledge on the last byte that has been clocked out of the slave. In this case, the transmitter must leave SDA high to enable the master to generate a STOP condition.

#### Register Reset

The I<sup>2</sup>C resisters reset back to their default values when the voltage at either IN1 or V<sub>DD</sub> drops below the corresponding UVLO threshold (see the *Electrical Characteristics* table).

Figure 13. Update Output Operation

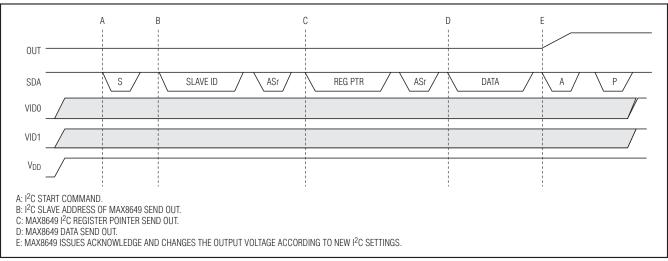

#### **Update of Output Operation Mode**

If updating the output voltage or Operation Mode register for the mode that the MAX8649 is currently operating in, the output voltage/operation mode is updated at the same time the MAX8649 sends the acknowledge for the I<sup>2</sup>C data byte (see Figure 13).

#### Slave Address

A bus master initiates communication with a slave device (MAX8649) by issuing a START condition followed by the slave address. The slave address byte consists of 7 address bits (1100 000x) and a read/write bit (R/ $\overline{\rm W}$ ). After receiving the proper address, the MAX8649 issues an acknowledge by pulling SDA low during the ninth clock cycle.

Other slave addresses can be assigned. Contact the factory for details.

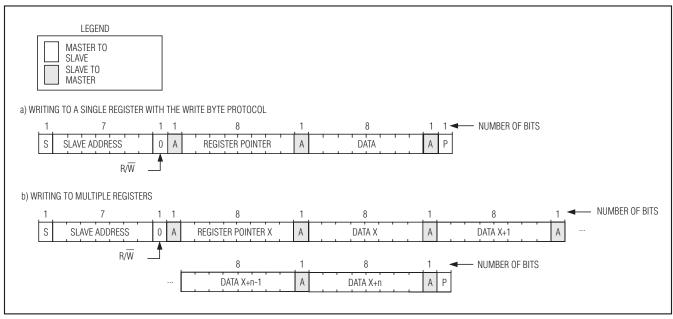

#### Write Operations

The MAX8649 recognizes the write byte protocol as defined in the SMBus specification and shown in Figures 14a and 14b. The write byte protocol allows the I<sup>2</sup>C master device to send 1 byte of data to the slave device. The write byte protocol requires a register pointer address for the subsequent write. The MAX8649 acknowledges any register pointer even though only a subset of those registers actually exists in the device. The write byte protocol is as follows:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a data byte.

- 7) The slave acknowledges the data byte.

- 8) The slave updates with the new data.

- 9) The master sends a STOP condition.

In addition to the write-byte protocol, the MAX8649 can write to multiple registers as shown in Figure 14b. This protocol allows the I<sup>2</sup>C master device to address the slave only once and then send data to a sequential block of registers starting at the specified register pointer.

Use the following procedure to write to a sequential block of registers:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends the 8-bit register pointer of the first register to write.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a data byte.

- 7) The slave acknowledges the data byte.

- 8) The slave updates with the new data.

- 9) Steps 6 to 8 are repeated for as many registers in the block, with the register pointer automatically incremented each time.

- 10) The master sends a STOP condition.

18 \_\_\_\_\_\_\_/W/JXI/M

Figures 14a and 14b. Writing to the MAX8649

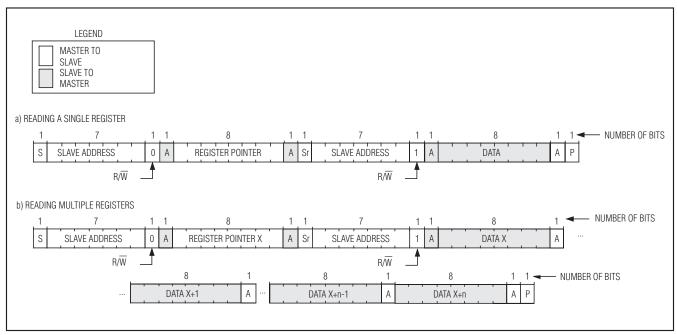

#### Read Operations

The method for reading a single register (byte) is shown in Figure 15a. To read a single register:

- 1) The master sends a start command.

- 2) The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a repeated START (S) condition.

- 7) The master sends the 7-bit slave address followed by a read bit.

- 8) The slave asserts an acknowledge by pulling SDA low.

- 9) The slave sends the 8-bit data (contents of the register).

- 10) The master asserts a not acknowledge by keeping SDA high.

- 11) The master sends a STOP (P) condition.

In addition, the MAX8649 can read a block of multiple sequential registers as shown in Figure 15b. Use the following procedure to read a sequential block of registers:

- 1) The master sends a start command.

- The master sends the 7-bit slave address followed by a write bit.

- 3) The addressed slave asserts an acknowledge by pulling SDA low.

- 4) The master sends an 8-bit register pointer of the first register in the block.

- 5) The slave acknowledges the register pointer.

- 6) The master sends a repeated START condition.

- 7) The master sends the 7-bit slave address followed by a read bit.

- 8) The slave asserts an acknowledge by pulling SDA low.

- 9) The slave sends the 8-bit data (contents of the register).

- 10) The master asserts an acknowledge by pulling SDA low when there is more data to read, or a not acknowledge by keeping SDA high when all data has been read.

- 11) Steps 9 and 10 are repeated for as many registers in the block, with the register pointer automatically incremented each time.

- 12) The master sends a STOP condition.

Figures 15a and 15b. Reading from the MAX8649

Figure 16. I<sup>2</sup>C Timing Diagram

Table 2. I<sup>2</sup>C Register Map

| POINTER | REGISTER | POR  | BIT7         | BIT6               | BIT5                            | BIT4           | BIT3 | BIT2 | BIT1 E   | BITO |

|---------|----------|------|--------------|--------------------|---------------------------------|----------------|------|------|----------|------|

| 0x00    | MODE0    | 0xB4 | OPER<br>MODE | SYNC<br>MODE       |                                 | OUT MODE0[5:0] |      |      |          |      |

| 0x01    | MODE1    | 0x1E | OPER<br>MODE | ()    M() )=1 5·() |                                 |                |      |      |          |      |

| 0x02    | MODE2    | 0xB0 | OPER<br>MODE | SYNC<br>MODE       | - I ()[I] M()[)[2]5:()[         |                |      |      |          |      |

| 0x03    | MODE3    | 0x9E | OPER<br>MODE | SYNC<br>MODE       |                                 | OUT MODE3[5:0] |      |      |          |      |

| 0x04    | CONTROL  | 0xE0 | EN_PD        | VID0_PD            | VID1_PD                         | _              | _    | _    | _        | _    |

| 0x05    | SYNC     | 0x00 | SYNC         | [1:0]              | _                               |                |      | _    | _        |      |

| 0x06    | RAMP     | 0x01 |              | RAMP[2:0]          | FORCE_HYS FORCE_OSC — RAMP_DOWN |                |      | _    |          |      |

| 0x08    | CHIP_ID1 | 0x20 |              | DIE T              | TYPE[7:4] DIE TYPE[3:0]         |                |      |      |          |      |

| 0x09    | CHIP_ID2 | 0x0E |              | DAS                | SH[3:0]                         |                |      | MASK | REV[3:0] |      |

### Table 3. I<sup>2</sup>C Register: MODE0

This register contains output voltage and operation mode control for MODE0, VID0 = GND, VID1 = GND.

| REGISTER NAME    | MODE0                                  |

|------------------|----------------------------------------|

| Address          | 0x00h                                  |

| Reset Value      | 0xB4h                                  |

| Туре             | Read/write                             |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| BIT      | NAME             | DESCRIPTION                                                                                                                                                                                                                                         | DEFAULT<br>VALUE |

|----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | OPERATION_MODE0  | DC-DC Step-Down Converter Operation Mode for MODE0  0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.  1 = DC-DC converter operates in forced-PWM mode. | 1                |

| В6       | SYNC_MODE0       | Disable/Enable Synchronization to External Clock  0 = DC-DC converter ignores the external SYNC input regardless of operation mode.  1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       |                  | Output Voltage Selection for MODE0                                                                                                                                                                                                                  |                  |

| B4       |                  | 000000 = 0.75V<br>000001 = 0.76V                                                                                                                                                                                                                    |                  |

| В3       |                  | 110011 = 1.26V                                                                                                                                                                                                                                      | 110100           |

| B2       | OUT_ MODE0 [5:0] | 110100 = 1.27V                                                                                                                                                                                                                                      | 110100           |

| B1       | 1                | 110101 = 1.28V<br>111110 = 1.37V                                                                                                                                                                                                                    |                  |

| B0 (LSB) | 1                | 111111 = 1.38V                                                                                                                                                                                                                                      |                  |

## Table 4. I<sup>2</sup>C Register: MODE1

This register contains output voltage and operation mode control for MODE1, VID1 = GND, VID0 = VDD.

| REGISTER NAME    | MODE1                                  |

|------------------|----------------------------------------|

| Address          | 0x01h                                  |

| Reset Value      | 0x1Eh                                  |

| Туре             | Read/write                             |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| ВІТ      | NAME            | DESCRIPTION                                                                                                                                                                                                                                         | DEFAULT<br>VALUE |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | OPERATION_MODE1 | DC-DC Step-Down Converter Operation Mode for MODE1  0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.  1 = DC-DC converter operates in forced-PWM mode. | 0                |

| В6       | SYNC_MODE1      | Disable/Enable Synchronization to External Clock  0 = DC-DC converter ignores the external SYNC input regardless of operation mode.  1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       |                 | Output Voltage Selection for MODE1                                                                                                                                                                                                                  |                  |

| B4       |                 | 000000 = 0.75V<br>000001 = 0.76V                                                                                                                                                                                                                    |                  |

| В3       | OUT MODE (E.O.) | 011101 = 1.04V                                                                                                                                                                                                                                      | 011110           |

| B2       | OUT_MODE1[5:0]  | 011110 = 1.05V                                                                                                                                                                                                                                      | 011110           |

| B1       |                 | 011111 = 1.06V<br>111110 = 1.37V                                                                                                                                                                                                                    |                  |

| B0 (LSB) |                 | 111111 = 1.38V                                                                                                                                                                                                                                      |                  |

### Table 5. I<sup>2</sup>C Register: MODE2

This register contains output voltage and operation mode control for MODE2, VID1 = V<sub>DD</sub>, VID0 = GND.

| REGISTER NAME    | MODE2                                  |

|------------------|----------------------------------------|

| Address          | 0x02h                                  |

| Reset Value      | 0xB0h                                  |

| Туре             | Read/write                             |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| ВІТ      | NAME            | DESCRIPTION                                                                                                                                                                                                                                         | DEFAULT<br>VALUE |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | OPERATION_MODE2 | DC-DC Step-Down Converter Operation Mode for MODE2  0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.  1 = DC-DC converter operates in forced-PWM mode. | 1                |

| В6       | SYNC_MODE2      | Disable/Enable Synchronization to External Clock  0 = DC-DC converter ignores the external SYNC input regardless of operation mode.  1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       |                 | Output Voltage Selection for MODE2                                                                                                                                                                                                                  |                  |

| B4       |                 | 000000 = 0.75V<br>000001 = 0.76V                                                                                                                                                                                                                    |                  |

| В3       | OUT MODESIE O   | 101110 = 1.21V                                                                                                                                                                                                                                      | 110000           |

| B2       | OUT_MODE2[5:0]  | 101111 = 1.22V                                                                                                                                                                                                                                      | 110000           |

| B1       |                 | 110000 = 1.23V<br>111110 = 1.37V                                                                                                                                                                                                                    |                  |

| B0 (LSB) |                 | 111111 = 1.38V                                                                                                                                                                                                                                      |                  |

### Table 6. I<sup>2</sup>C Register: MODE3

This register contains output voltage and operation mode control for MODE3, VID1 =  $V_{DD}$ , VID0 =  $V_{DD}$ .

| REGISTER NAME    | MODE3                                  |

|------------------|----------------------------------------|

| Address          | 0x03h                                  |

| Reset Value      | 0x9Eh                                  |

| Type             | Read/write                             |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| ВІТ      | NAME            | DESCRIPTION                                                                                                                                                                                                                                         | DEFAULT<br>VALUE |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | OPERATION_MODE3 | DC-DC Step-Down Converter Operation Mode for MODE3  0 = DC-DC converter automatically changes between hysteretic mode for light load conditions and PWM mode for medium to heavy load conditions.  1 = DC-DC converter operates in forced-PWM mode. | 1                |

| В6       | SYNC_MODE3      | Disable/Enable Synchronization to External Clock  0 = DC-DC converter ignores the external SYNC input regardless of operation mode.  1 = DC-DC converter synchronizes to external SYNC input when available.                                        | 0                |

| B5       |                 | Output Voltage Selection for MODE3                                                                                                                                                                                                                  |                  |

| B4       |                 | 000000 = 0.75V<br>000001 = 0.76V                                                                                                                                                                                                                    |                  |

| В3       | OUT MODE3[5:0]  | 011101 = 1.04V                                                                                                                                                                                                                                      | 011110           |

| B2       | OU1_WODE3[5.0]  | 011110 = 1.05V                                                                                                                                                                                                                                      | 011110           |

| B1       |                 | 011111 = 1.06V<br>111110 = 1.37V                                                                                                                                                                                                                    |                  |

| B0 (LSB) |                 | 111111 = 1.38V                                                                                                                                                                                                                                      |                  |

### Table 7. I<sup>2</sup>C Register: CONTROL

This register enables or disables pulldown resistors.

| REGISTER NAME    | CONTROL                                                |

|------------------|--------------------------------------------------------|

| Address          | 0x04h                                                  |

| Reset Value      | 0xE0h                                                  |

| Туре             | Read/write                                             |

| Special Features | Reset upon V <sub>DD</sub> , IN1 UVLO or EN pulled low |

| ВІТ      | NAME    | DESCRIPTION                                                                       | DEFAULT<br>VALUE |

|----------|---------|-----------------------------------------------------------------------------------|------------------|

| B7 (MSB) | EN_PD   | 0 = Pulldown on EN input is disabled.<br>1 = Pulldown on EN input is enabled.     | 1                |

| B6       | VID0_PD | 0 = Pulldown on VID0 input is disabled.<br>1 = Pulldown on VID0 input is enabled. | 1                |

| B5       | VID1_PD | 0 = Pulldown on VID1 input is disabled.<br>1 = Pulldown on VID1 input is enabled. | 1                |

| B4       | _       | Reserved for future use.                                                          | 0                |

| В3       | _       | Reserved for future use.                                                          | 0                |

| B2       | _       | Reserved for future use.                                                          | 0                |

| B1       | _       | Reserved for future use.                                                          | 0                |

| B0 (LSB) | _       | Reserved for future use.                                                          | 0                |

## Table 8. I<sup>2</sup>C Register: SYNC

This register specifies the clock frequency of external clock source.

| REGISTER NAME    | SYNC                                   |

|------------------|----------------------------------------|

| Address          | 0x05h                                  |

| Reset Value      | 0x00h                                  |

| Type             | Read                                   |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| BIT      | NAME      | DESCRIPTION                                                                              | DEFAULT<br>VALUE |

|----------|-----------|------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) | CVNC[1:0] | Sets Clock Frequency of External Clock Present on SYNC Input<br>00 = 26MHz<br>01 = 13MHz | 00               |

| В6       | SYNC[1:0] | 10 = 13MHz<br>10 = 19.2MHz<br>11 = 19.2MHz                                               | 00               |

| B5       | _         | Reserved for future use.                                                                 | 0                |

| B4       | _         | Reserved for future use.                                                                 | 0                |

| B3       | _         | Reserved for future use.                                                                 | 0                |

| B2       | _         | Reserved for future use.                                                                 | 0                |

| B1       | _         | Reserved for future use.                                                                 | 0                |

| B0 (LSB) | _         | Reserved for future use.                                                                 | 0                |

### Table 9. I<sup>2</sup>C Register: RAMP

This register controls of ramp-up/down function.

| REGISTER NAME    | RAMP                                   |

|------------------|----------------------------------------|

| Address          | 0x06h                                  |

| Reset Value      | 0x01h                                  |

| Туре             | Read                                   |

| Special Features | Reset upon V <sub>DD</sub> or IN1 UVLO |

| ВІТ      | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                       | DEFAULT<br>VALUE |

|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| B7 (MSB) |           | Control the RAMP Timing $000 = 32\text{mV}/\mu\text{s}$ $001 = 16\text{mV}/\mu\text{s}$                                                                                                                                                                                                                           |                  |

| B6       | RAMP[2:0] | 010 = 8mV/μs<br>011 = 4mV/μs<br>100 = 2mV/μs                                                                                                                                                                                                                                                                      | 000              |

| B5       |           | 101 = $1mV/\mu s$<br>110 = $0.5mV/\mu s$<br>111 = $0.25mV/\mu s$                                                                                                                                                                                                                                                  |                  |

| B4       | FORCE_HYS | Only Valid When Converter is Operating in OPERATION_MODE 0  0 = Automatically change between power-save mode and PWM mode, depending on load current.  1 = Converter always operates in power-save mode regardless of load current as long as OPERATION_MODE = 0. If OPERATION_MODE = 1, this setting is ignored. | 0                |

| ВЗ       | FORCE_OSC | Force Oscillator While Running in Hysteretic Mode  0 = Internal oscillator is disabled in power save when operating in hysteretic mode.  1 = Internal oscillator is enabled in power save even when operating in hysteretic mode.                                                                                 | 0                |

| B2       | _         | Reserved for future use.                                                                                                                                                                                                                                                                                          | 0                |

| B1       | RAMP_DOWN | Active Ramp-Down Control for Power-Save Mode  0 = Active ramp disabled for power-save mode.  1 = During ramp-down, the error crossing detector is disabled allowing negative current to flow thought the nMOS device.                                                                                             | 0                |

| B0 (LSB) | _         | Reserve for future use.                                                                                                                                                                                                                                                                                           | 1                |

## Table 10. I<sup>2</sup>C Register: CHIP\_ID1

This register contains the die type number (20).

| REGISTER NAME    | CHIP_ID1 |

|------------------|----------|

| Address          | 0x08h    |

| Reset Value      | 0x20h    |

| Туре             | Read     |

| Special Features |          |

| BIT      | NAME          | DESCRIPTION       | DEFAULT<br>VALUE |

|----------|---------------|-------------------|------------------|

| B7 (MSB) |               |                   |                  |

| B6       | DIE_TYPE[7:4] | BCD character (2) | 0010             |

| B5       |               |                   |                  |

| B4       |               |                   |                  |

| B3       |               |                   |                  |

| B2       | DIE TYDEIO OI | BCD character (0) | 0000             |

| B1       | DIE_TYPE[3:0] |                   |                  |

| B0 (LSB) |               |                   |                  |

## Table 11. I<sup>2</sup>C Register: CHIP\_ID2\*

This register contains the die type dash number and mask revision level.

| REGISTER NAME    | CHIP_ID2 |

|------------------|----------|

| Address          | 0x09h    |

| Reset Value      | 0x0Eh    |

| Туре             | Read     |

| Special Features | _        |

| BIT      | NAME     | DESCRIPTION     | DEFAULT<br>VALUE |

|----------|----------|-----------------|------------------|

| B7 (MSB) | DASH     | BCD character 0 |                  |

| В6       |          |                 | 0000             |

| B5       |          |                 | 0000             |

| B4       |          |                 |                  |

| B3       | MACK DEV |                 |                  |

| B2       |          | BCD character E | 1110             |

| B1       | MASK_REV |                 | 1110             |

| B0 (LSB) |          |                 |                  |

<sup>\*</sup>See Revision History for CHIP\_ID2 history.

### **Applications Information**

#### **Inductor Selection**

Calculate the inductor value (LIDEAL) using the following formula:

$$L_{IDEAL} = \frac{4 \times V_{IN} \times D \times (1-D)}{I_{OUT(MAX)} \times f_{OSC}}$$

This sets the peak-to-peak inductor current ripple to 1/4 the maximum output current. The oscillator frequency, fosc, is 3.25MHz, and the duty cycle, D, is:

$$D = \frac{V_{OUT}}{V_{IN}}$$

Given Lideal, the peak-to-peak inductor ripple current is 0.25 x Iout(Max). The peak inductor current is 1.125 x Iout(Max). Make sure that the saturation current of the inductor exceeds the peak inductor current, and the rated maximum DC inductor current exceeds the maximum output current Iout(Max). Inductance values smaller than Lideal can be used to reduce inductor size; however, if much smaller values are used, peak inductor current rises and a larger output capacitance may be required to suppress output ripple. Larger inductance values than Lideal can be used to obtain higher output current, but typically require a physically larger inductor size. See Table 12 for recommended inductors.

**Table 12. Recommended Inductors**

| MANUFACTURER   | SERIES                    | INDUCTANCE<br>(µH)                | DC RESISTANCE<br>(Ω typ)                  | CURRENT RATING (mA)                  | DIMENSIONS<br>L x W x H (mm) |