## Product Preview

# Low Voltage Synchronous Buck Controller

The NCP1589A/B is a low cost PWM controller designed to operate from a 5 V or 12 V supply. This device is capable of producing an output voltage as low as 0.8 V. This device is capable of converting voltage from as low as 2.5 V. This 10-pin device provides an optimal level of integration to reduce size and cost of the power supply. Features include a 1.5 A gate driver design and an internally set 300 kHz or 600 kHz oscillator. In addition to the 1.5 A gate drive capability, other efficiency enhancing features of the gate driver include adaptive non-overlap circuitry. The NCP1589A/B also incorporates an externally compensated error amplifier. Protection features include programmable short circuit protection and undervoltage lockout (UVLO).

#### **Features**

- V<sub>CC</sub> Range from 4.5 V to 13.2 V

- 300 kHz and 600 kHz Internal Oscillator

- Boost Pin Operates to 30 V

- Voltage Mode PWM Control

- Precision 0.8 V Internal Reference

- Adjustable Output Voltage

- Internal 1.5 A Gate Drivers

- 80% Max Duty Cycle

- Input Under Voltage Lockout

- Programmable Current Limit

- This is a Pb-Free Device

#### **Applications**

- Graphics Cards

- Desktop Computers

- Servers / Networking

- DSP & FPGA Power Supply

- DC-DC Regulator Modules

#### ON Semiconductor®

http://onsemi.com

#### **MARKING DIAGRAMS**

DFN10 CASE 485C

1589x = Specific Device Code

x = A or B

= Assembly Location

L = Wafer Lot Y = Year W = Work Week ■ Pb-Free Device

(Note: Microdot may be in either location)

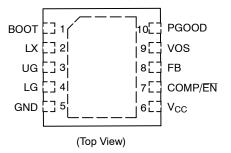

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Device        | Package            | Shipping <sup>†</sup> |

|---------------|--------------------|-----------------------|

| NCP1589AMNTWG |                    |                       |

| NCP1589BMNTWG | DFN10<br>(Pb-Free) | 3000 /                |

| NCP1589AMNTXG |                    | Tape & Reel           |

| NCP1589BMNTXG |                    |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

This document contains information on a product under development. ON Semiconductor reserves the right to change or discontinue this product without notice.

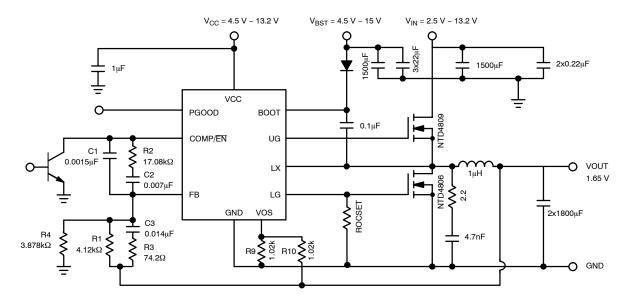

**Figure 1. Typical Application Diagram**

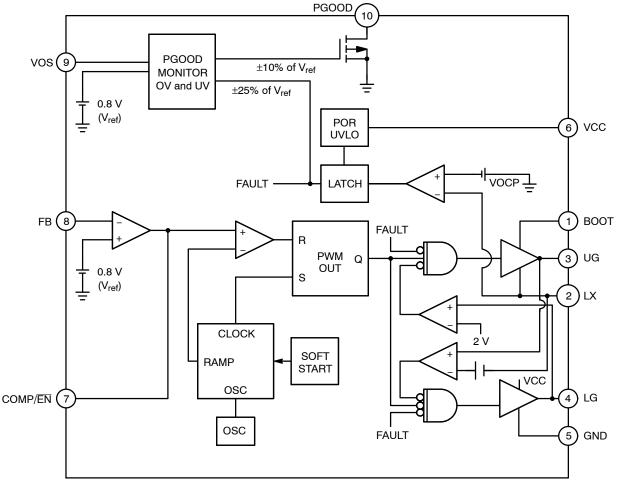

Figure 2. Detailed Block Diagram

#### **PIN FUNCTION DESCRIPTION**

| Pin No. | Symbol  | Description                                                                                                                                                                                                                                                                                                                                                       |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | воот    | Supply rail for the floating top gate driver. To form a boost circuit, use an external diode to bring the desired input voltage to this pin (cathode connected to BOOT pin). Connect a capacitor ( $C_{BOOT}$ ) between this pin and the LX pin. Typical values for $C_{BOOT}$ range from 0.1 $\mu$ F to 1 $\mu$ F. Ensure that $C_{BOOT}$ is placed near the IC. |

| 2       | LX      | Switch node pin. This is the reference for the floating top gate driver. Connect this pin to the source of the top MOSFET.                                                                                                                                                                                                                                        |

| 3       | UG      | Top gate MOSFET driver pin. Connect this pin to the gate of the top N-channel MOSFET.                                                                                                                                                                                                                                                                             |

| 4       | LG      | Bottom gate MOSFET driver pin. Connect this pin to the gate of the bottom N-channel MOSFET.                                                                                                                                                                                                                                                                       |

| 5       | GND     | IC ground reference. All control circuits are referenced to this pin.                                                                                                                                                                                                                                                                                             |

| 6       | VCC     | Supply rail for the internal circuitry. Operating supply range is 4.5 V to 13.2 V. Decouple with a 1 $\mu$ F capacitor to GND. Ensure that this decoupling capacitor is placed near the IC.                                                                                                                                                                       |

| 7       | COMP/EN | Compensation Pin. This is the output of the error amplifier (EA) and the non-inverting input of the PWM comparator. Use this pin in conjunction with the FB pin to compensate the voltage-control feedback loop. Pull this pin low for disable.                                                                                                                   |

| 8       | FB      | This pin is the inverting input to the error amplifier. Use this pin in conjunction with the COMP pin to compensate the voltage–control feedback loop. Connect this pin to the output resistor divider (if used) or directly to V <sub>out</sub> .                                                                                                                |

| 9       | VOS     | Voltage Offset Sense                                                                                                                                                                                                                                                                                                                                              |

| 10      | PGOOD   | Power Good output. Pulled Low if VOS is ±10% of 0.8 V V <sub>ref</sub> .                                                                                                                                                                                                                                                                                          |

#### **ABSOLUTE MAXIMUM RATINGS**

| Pin Name                                 | Symbol  | V <sub>MAX</sub>                                 | V <sub>MIN</sub>                   |

|------------------------------------------|---------|--------------------------------------------------|------------------------------------|

| Main Supply Voltage Input                | VCC     | 15 V                                             | -0.3 V                             |

| Bootstrap Supply Voltage Input           | ВООТ    | 35 V wrt/GND<br>40 V < 100 ns<br>15 V wrt/LX     | -0.3 V<br>-0.3 V<br>-0.3 V         |

| Switching Node (Bootstrap Supply Return) | LX      | 35 V<br>40 V for < 100 ns                        | −5 V<br>−10 V for < 200 ns         |

| High-Side Driver Output (Top Gate)       | UG      | 30 V wrt/GND<br>15 V wrt/LX<br>40 V for < 100 ns | -0.3 V wrt/LX<br>-2 V for < 200 ns |

| Low-Side Driver Output (Bottom Gate)     | LG      | V <sub>CC</sub> + 0.3 V                          | −0.3 V<br>−5 V for < 200 ns        |

| Feedback, VOS                            | FB, VOS | 5.0 V                                            | -0.3 V                             |

| COMP/EN                                  | COMP/EN | 3.6 V                                            | -0.3 V                             |

| PGOOD                                    | PGOOD   | 7 V                                              | -0.3 V                             |

#### **MAXIMUM RATINGS**

| Rating                                  | Symbol           | Value       | Unit |

|-----------------------------------------|------------------|-------------|------|

| Thermal Resistance, Junction-to-Ambient | $R_{	hetaJA}$    | 165         | °C/W |

| Thermal Resistance, Junction-to-Case    | $R_{	heta JC}$   | 45          | °C/W |

| Operating Junction Temperature Range    | TJ               | 0 to 150    | °C   |

| Operating Ambient Temperature Range     | T <sub>A</sub>   | 0 to 70     | °C   |

| Storage Temperature Range               | T <sub>stg</sub> | -55 to +150 | °C   |

| Moisture Sensitivity Level              | MSL              | 1           | -    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

This device is ÉSD sensitive. Use standard ESD precautions when handling.

$\textbf{ELECTRICAL CHARACTERISTICS} \ (0^{\circ}\text{C} < T_{A} < 70^{\circ}\text{C}; \ 4.5 \ \text{V} < [BST-PHASE] < 13.2 \ \text{V}, \ 4.5 \ \text{V} < BST < 30 \ \text{V}, \ 0 \ \text{V} < PHASE < 21 \ \text{V}, \ C_{TG} = C_{BG} = 1.0 \ \text{nF}, \ \text{for min/max values unless otherwise noted.}$

| Characteristic                               | Conditions                                                            | Min        | Тур  | Max    | Unit |

|----------------------------------------------|-----------------------------------------------------------------------|------------|------|--------|------|

| Input Voltage Range                          |                                                                       | 4.5        |      | 13.2   | V    |

| Boost Voltage Range                          | 13.2 V wrt LX                                                         | 4.5        |      | 30     | V    |

| Supply Current                               | •                                                                     | -          |      | -      | •    |

| Quiescent Supply Current (NCP1589A)          | V <sub>FB</sub> = 1.0 V, No Switching, V <sub>CC</sub> = 13.2 V       | 1.0        |      | 8.0    | mA   |

| Boost Quiescent Current                      | V <sub>FB</sub> = 1.0 V, No Switching                                 | 0.1        |      | 100    | μΑ   |

| Undervoltage Lockout                         |                                                                       |            |      |        |      |

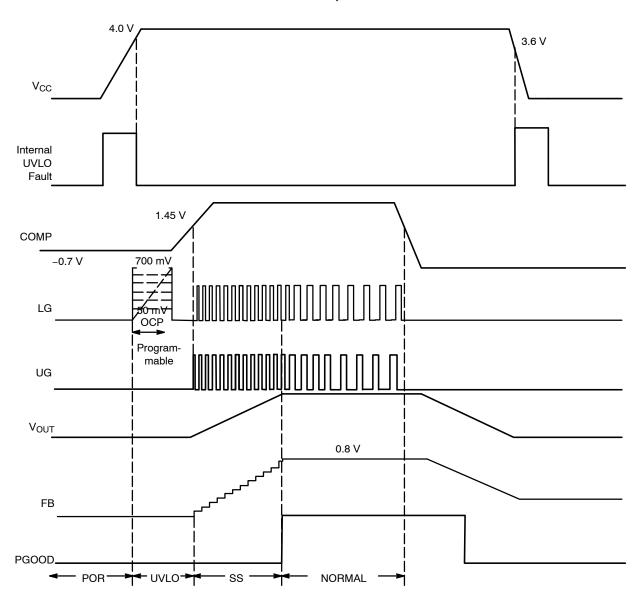

| UVLO Threshold                               | V <sub>CC</sub> Rising                                                | 3.8        | 4.0  | 4.2    | V    |

| UVLO Threshold                               | V <sub>CC</sub> Falling                                               | 3.4        | 3.6  | 3.8    | V    |

| UVLO Hysteresis                              | V <sub>CC</sub> Rising or V <sub>CC</sub> Falling                     |            | 0.4  |        | V    |

| Switching Regulator                          |                                                                       |            |      |        |      |

| VFB Feedback Voltage                         | (FB Tied to Comp. Measure FB Pin.)                                    | 0.7936     | 0.8  | 0.8064 | V    |

| Oscillator Frequency (NCP1589A)              |                                                                       | 270        | 300  | 330    | kHz  |

| Oscillator Frequency (NCP1589B)              |                                                                       | TBD        | 600  | TBD    | kHz  |

| Ramp-Amplitude Voltage                       |                                                                       |            | 1.1  |        | V    |

| Minimum Duty Cycle                           |                                                                       |            | 0    |        | %    |

| Maximum Duty Cycle                           |                                                                       | 70         | 75   | 80     | %    |

| LG Minimum on Time                           |                                                                       |            | 500  |        | ns   |

| Error Amplifier                              | •                                                                     |            |      |        |      |

| Open Loop DC Gain (Note 1)                   |                                                                       | 70         | 80   |        | dB   |

| Output Source Current<br>Output Sink Current | $V_{fb} < 0.8 \text{ V} $ $V_{fb} > 0.8 \text{ V}$                    | 2.0<br>2.0 |      |        | mA   |

| Input Offset Voltage (Note 1)                |                                                                       | -2.0       | 0    | 2.0    | mV   |

| Input Bias Current                           |                                                                       |            | 0.1  | 1.0    | μΑ   |

| Unity Gain Bandwidth (Note 1)                |                                                                       | 15         |      |        | Mhz  |

| Disable Threshold                            |                                                                       | 0.6        | 0.8  |        | V    |

| Output Source Current During Disable         |                                                                       |            | 10   | 40     | μΑ   |

| Gate Drivers                                 | •                                                                     |            |      |        |      |

| Upper Gate Source                            | V <sub>CC</sub> = 5 V, VUG – VLX = 2.5 V                              | 1.5        |      |        | Α    |

| Upper Gate Sink                              |                                                                       |            | 1.4  |        | Ω    |

| Lower Gate Source                            |                                                                       | 1.5        |      |        | Α    |

| Lower Gate Sink                              | V <sub>CC</sub> = 12 V                                                |            | 1.0  |        | Ω    |

| UG Falling to LG Rising Delay                | V <sub>CC</sub> = 12 V, UG–LX < 2.0 V, LG > 2.0 V                     | 12.4       | 18   |        | ns   |

| LG Falling to UG Rising Delay                | V <sub>CC</sub> = 12 V, LG < 2.0 V, UG > 2.0 V                        | 12.4       | 18   |        | ns   |

| Soft-Start                                   | •                                                                     |            |      |        |      |

| Soft-Start time                              |                                                                       | 3.0        |      | 7.0    | ms   |

| Power Good                                   | •                                                                     |            |      |        |      |

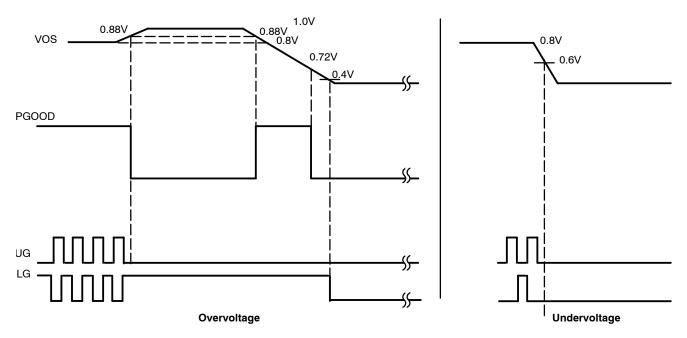

| Output Voltage                               | Logic Low, Sinking 4 mA                                               |            |      | 0.4    | V    |

| OVP Threshold to PGOOD Output Low            | Ramp VOS from 0.7 to 1.2.<br>Monitor when PGOOD goes Low              |            | 0.88 | 1.0    | V    |

| OVP Threshold to Part Disable                | Ramp VOS from 0.8 to 1.2.<br>Monitor when outputs disable             |            | 1.0  | 1.2    | V    |

| UVP Threshold to PGOOD Output Low            | Ramp VOS from 800 mV to 500 mV.<br>Monitor when PGOOD goes Low        | 0.65       | 0.72 |        | V    |

| UVP Threshold to Part Disable                | Ramp VOS from 800 mV to 500 mV.<br>Monitor when utputs stop switching | 0.5        | 0.6  |        | V    |

| Overcurrent Protection                       |                                                                       | •          |      |        |      |

| OC Current Source (Note 1)                   | Sourced from LG pin, before SS                                        | 9.0        | 10   | 11     | μΑ   |

<sup>1.</sup> Guaranteed by design but not tested in production.

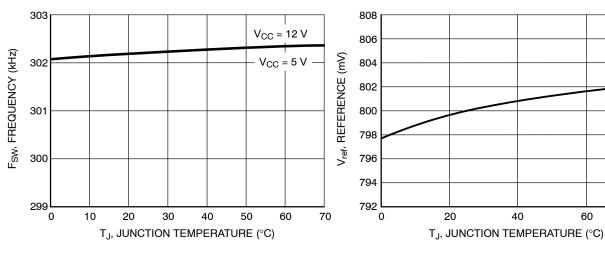

#### **TYPICAL CHARACTERISTICS**

Figure 3. Oscillator Frequency (F<sub>SW</sub>) vs. **Temperature**

Figure 4. Reference Voltage (V<sub>ref</sub>) vs. **Temperature**

40

60

80

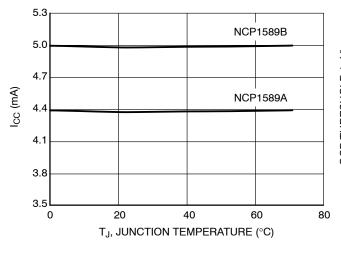

Figure 5. I<sub>CC</sub> vs. Temperature

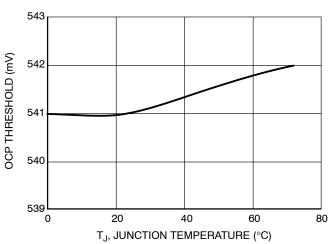

Figure 6. OCP Threshold at 55k vs. Temperature

#### **APPLICATIONS INFORMATION**

#### **Over Current Protection (OCP)**

The NCP1589A/B monitors the voltage drop across the low side mosfet and uses this information to determine if there is excessive output current. The voltage across the low side mosfet is measured from the LX pin, and is referenced to ground. The over current measurement is timed to occur at the end of the low side mosfet conduction period, just before the bottom mosfet is turned off.

If the voltage drop across the bottom mosfet exceeds the over current protection threshold, then an internal counter is incremented. If the voltage drop does not exceed the over current protection threshold, then the internal counter is reset. The NCP1589A/B will latch the over current protection fault condition only if the over current protection threshold is exceeded for four consecutive cycles.

When the NCP1589A/B latches an over current protection fault, both the high side and low side mosfets are turned off. To reset the over current protection fault, the power to the VCC pin must be cycled.

The over current threshold voltage can be externally, by varying the value of the ROCSET resistor. The ROCSET resistor is a resistor connected between the LG pin (low side mosfet gate) and ground.

During startup, after the VCC and BOOT pins reach the under voltage lock out threshold, the NCP1589A/B will source 10  $\mu A$  of current out of the LG pin. This current will flow through the ROCSET resistor and produce a voltage that is sampled and then used as the over current protection threshold voltage. For example, if ROCSET is set to  $10~k\Omega$ , the  $10~\mu A$  of current will yield a 100~mV threshold, and if the voltage drop across the low side mosfet exceeds 100~mV at the end of its conduction period, then an over current event will be detected.

If the ROCSET resistor is not present, then the over current protection threshold will max out at 640 mV. The valid range for ROCSET is 5 k $\Omega$  to 55 k $\Omega$  which yields a threshold voltage range of 50 mV to 550 mV.

#### **Internal Soft-Start**

To prevent excess inrush current during startup, the NCP1589A/B uses a calibrated current source with an internal soft start capacitor to ramp the reference voltage from 0 to 800 mV over a period of 4 ms. The softstart ramp generator will reset if the input power supply voltages reach

the under voltage lockout threshold, or if the NCP1589A/B is disabled by having the COMP pin pulled low.

#### Startup into a Precharged Load

During a startup and soft start sequence the NCP1589A will detect a residual charge on the output capacitors and not forcefully discharge the capacitors before beginning the softstart sequence, instead, the softstart ramping of the output will begin at the voltage level of the residual charge. For example, if the NCP1589A/B is configured to provide a regulated output voltage of 2.5 V, the normal softstart sequence will ramp the output voltage from 0 to 2.5 V in 4.2 ms; however if the output capcitors already have a 1.2 V charge on them, the NCP1589A/B will not discharge the capacitors, instead the softstart sequence will begin at 1.2 V and then ramp the output to 2.5 V.

#### **Power Good**

The PGOOD pin is an open drain active high output pin that signals the condition of the VOS (Voltage Output Sense) pin. PGOOD is pulled low during soft start cycle, and if there is a latched over current, over voltage, or under voltage fault. If the voltage on the VOS pin is within  $\pm 10\%$  of Vref (800 mV) then the PGOOD pin will not be pulled low. The PGOOD pin does not have an internal pull-up resistor.

#### **Overvoltage Protection**

If the voltage on the VOS pin exceeds the over voltage threshold the NCP1589A/B will latch an over voltage fault. During an over voltage fault the UG pin will be pulled low, and the LG pin will be high while the until the voltage on the VOS pin goes below  $V_{ref}/2$  (400 mV). The NCP1589A will continue drive the LG pin, LG will go high if VOS exceeds 1 V and then go low when VOS goes below 400 mV. The power to the NCP1589 must be cycled to reset the over voltage protection fault.

#### **Under Voltage Protection**

If the voltage on the VOS pin falls below the under voltage threshold after the soft start cycle completes, then the NCP1589A/B will latch an under voltage fault. During an under voltage fault, both the UG and LG pins will be pulled low. The power to the NCP1589 must be cycled to reset the under voltage protection fault.

Figure 7. Typical Startup Sequence

**Figure 8. Typical Power Good Function**

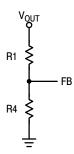

#### **Feedback and Compensation**

The NCP1589A/B allows the output voltage to be adjusted from 0.8~V to 5.0~V via an external resistor divider network. The controller will try to maintain 0.8~V at feedback pin. Thus, if a resistor divider circuit was placed across the feedback pin to  $V_{OUT}$ , the controller will regulate the output voltage proportional to the resistor divider network in order to maintain 0.8~V at the FB pin. The same formula applies to the VOS pin and the controller will maintain 0.8~V at the VOS pin.

Figure 9.

The relationship between the resistor divider network above and the output voltage is shown in the following equation:

$$R_4 = R_1 \times \left( \frac{V_{REF}}{V_{OUT} - V_{REF}} \right)$$

The same formula can be applied to the feedback resistors at VOS.

$$R_9 = R_{10} \times \left( \frac{V_{REF}}{V_{OUT} - V_{REF}} \right)$$

#### **Design Example**

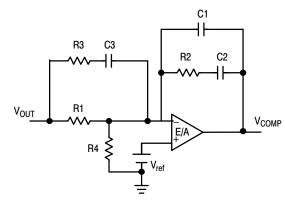

# Voltage Mode Control Loop with TYPE III Compensation

#### **Converter Parameters:**

Input Voltage: V<sub>IN</sub> = 5 V Output Voltage: V<sub>OUT</sub> = 1.65 V Switching Frequency: 300 kHz

Total Output Capacitance:  $C_{OUT} = 3600 \mu F$

Total ESR: ESR =  $6 \text{ m}\Omega$ Output Inductance:  $L_{OUT}$ : 1  $\mu H$ Ramp Amplitude:  $V_{RAMP} = 1.1 \text{ V}$

Figure 10.

a.. Set a target for the close loop bandwidth at 1/6<sup>th</sup> of the switching frequency.

$$F_{cross\ over} := 50\ kHz$$

b.. Output Filter Double Pole Frequency

$$\mathsf{F}_{\mathsf{lc}} := \frac{1}{2 \cdot \pi \cdot \sqrt{\mathsf{L}_{\mathsf{OUT}} \cdot \mathsf{C}_{\mathsf{OUT}}}}$$

$F_{lc} = 2.653 \, kHz$

c.. ESR Zero Frequency:

$$\mathsf{F}_{\mathsf{ESR}} := \frac{1}{2 \cdot \pi \cdot \mathsf{C}_{\mathsf{OUT}} \cdot \mathsf{C}_{\mathsf{ESR}}}$$

$F_{FSR} = 7.368 \text{ kHz}$

Step 1: Set a value for R1 between 2  $k\Omega$  and 5  $k\Omega$

$R1 := 4.12 k\Omega$

Step 2: Pick compensation DC gain (R2/R1) for desired close loop bandwidth.

$$V_{RAMP} := 1.1 V$$

$$R2 := R1 \cdot \left(\frac{V_{RAMP}}{V_{IN}}\right) \cdot \left(\frac{F_{cross\_over}}{F_{Ic}}\right)$$

$R2\,=\,17.085~k\Omega$

Step 3: Place 1st zero at half the output filter double pole frequency.

$$C2 := \frac{2 \cdot \sqrt{L_{OUT} \cdot C_{OUT}}}{R2}$$

$$C2 = 7.024 \times 10^{-3} \, \mu F$$

Step 4: Place 1st pole at ESR zero frequency.

$$C1 := \frac{C2}{C2 \cdot R2 \cdot 2 \cdot \pi \cdot F_{FSR} - 1}$$

$$C1 = 1.542 \times 10^{-3} \, \mu F$$

Step 5: Place 2<sup>nd</sup> zero at the output filter double pole frequency.

$$R3 := \frac{R1}{\frac{F_{SW}}{2 \cdot F_{IC}} - 1}$$

$$R3 = 74.169 \Omega$$

Step 6: Place 2<sup>nd</sup> pole at half the switching frequency.

$$C3 := \frac{1}{\left(\pi \cdot R3 \cdot F_{SW}\right)}$$

$$C3 = 0.014 \mu F$$

Step 7: R4 is sized to maintain the feedback voltage to  $V_{ref} = 0.8 \text{ V}$ .

$$R4 := \frac{V_{REF} \cdot R1}{V_{OUT} - V_{REF}}$$

$$R4 = 3.878 \, k\Omega$$

#### The Component values for Type III Compensation are:

$R1 = 4.12 \text{ k}\Omega$

$R2 = 17.085 \text{ k}\Omega$

$R3 = 74.169 \Omega$

$R4 = 3.878 \text{ k}\Omega$

$C1 = 0.0015 \mu F$

$C2 = 0.007 \,\mu\text{F}$

$C3 = 0.014 \,\mu\text{F}$

NOTE: Recommend to change values to industry standard component values.

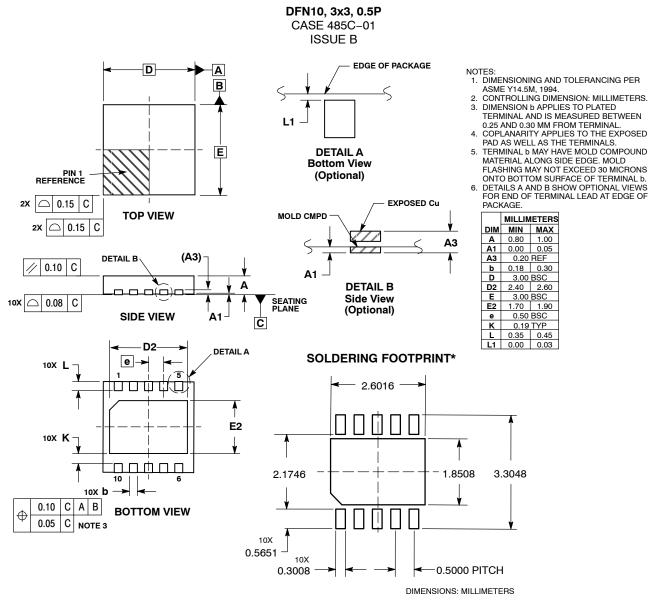

#### PACKAGE DIMENSIONS

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and 📖 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

N. American Technical Support: 800-282-9855 Toll Free

Japan Customer Focus Center Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative