# Monolithic 1A Step-Down Regulator

The EL7536 is a synchronous, integrated FET 1A step-down regulator with internal compensation. It operates with an input voltage range from 2.5V to 5.5V, which accommodates supplies of 3.3V, 5V, or a Li-lon battery source. The output can be externally set from 0.8V to  $V_{\mbox{\footnotesize{IN}}}$  with a resistive divider.

The EL7536 features PWM mode control. The operating frequency is typically 1.4MHz. Additional features include a 100ms Power-On-Reset output, <1µA shut-down current, short-circuit protection, and over-temperature protection.

The EL7536 is available in the 10 Ld MSOP package, making the entire converter occupy less than  $0.15 \text{in}^2$  of PCB area with components on one side only. Both packages are specified for operation over the full -40°C to +85°C temperature range.

# Ordering Information

| PART NUMBER<br>(BRAND)  | PART<br>MARKING | TAPE & REEL | PACKAGE                 | PKG.<br>DWG.# |

|-------------------------|-----------------|-------------|-------------------------|---------------|

| EL7536IY                | BDAAA           | -           | 10 Ld MSOP              | MDP0043       |

| EL7536IY-T7             | BDAAA           | 7"          | 10 Ld MSOP              | MDP0043       |

| EL7536IY-T13            | BDAAA           | 13"         | 10 Ld MSOP              | MDP0043       |

| EL7536IYZ<br>(Note)     | BFAAA           | -           | 10 Ld MSOP<br>(Pb-free) | MDP0043       |

| EL7536IYZ-T7<br>(Note)  | BFAAA           | 7"          | 10 Ld MSOP<br>(Pb-free) | MDP0043       |

| EL7536IYZ-T13<br>(Note) | BFAAA           | 13"         | 10 Ld MSOP<br>(Pb-free) | MDP0043       |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

#### **Pinout**

| EL7536 (10 LD MSOP | ) |

|--------------------|---|

| TOP VIEW           |   |

| 1 | SGND | FB  | 10 |

|---|------|-----|----|

| 2 | PGND | vo  | 9  |

| 3 | LX   | POR | 8  |

| 4 | VIN  | EN  | 7  |

| 5 | VDD  | RSI | 6  |

#### **Features**

- Less than 0.15in<sup>2</sup> (0.97cm<sup>2</sup>) footprint for the complete 1A converter

- · Components on one side of PCB

- Max height 1.1mm MSOP10

- 100ms Power-On-Reset output (POR)

- · Internally-compensated voltage mode controller

- Up to 94% efficiency

- <1µA shut-down current</li>

- Overcurrent and over-temperature protection

- Pb-free plus anneal available (RoHS compliant)

# **Applications**

- · PDA and pocket PC computers

- · Bar code readers

- · Cellular phones

- · Portable test equipment

- · Li-Ion battery powered devices

- · Small form factor (SFP) modules

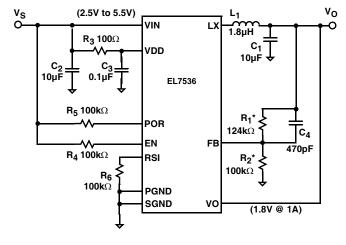

# Typical Application Diagram

EL7536 TOP VIEW

$^* V_0 = 0.8V * (1 + R_1 / R_2)$

## **Absolute Maximum Ratings** (T<sub>A</sub> = 25°C)

| V <sub>IN</sub> , V <sub>DD</sub> , POR to SGND0.3V to +6.5V | Operating Ambient Temperature |

|--------------------------------------------------------------|-------------------------------|

| LX to PGND0.3V to (V <sub>IN</sub> + +0.3V)                  | Storage Temperature           |

| RSI, EN, $V_O$ , FB to SGND0.3V to $(V_{IN} + +0.3V)$        | Junction Temperature          |

| PGND to SGND0.3V to +0.3V                                    |                               |

| Peak Output Current 1.2A                                     |                               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typ values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# $\textbf{Electrical Specifications} \hspace{0.5cm} V_{DD} = V_{IN} = V_{EN} = 3.3 \text{V}, \hspace{0.5cm} \text{C1} = \text{C2} = 10 \mu\text{F}, \hspace{0.5cm} \text{L} = 1.8 \mu\text{H}, \hspace{0.5cm} V_{O} = 1.8 \text{V}, \hspace{0.5cm} \text{unless otherwise specified}. \hspace{0.5cm} \text{C1} = \text{C2} = 10 \mu\text{F}, \hspace{0.5cm} \text{L} = 1.8 \mu\text{H}, \hspace{0.5cm} \text{V}_{O} = 1.8 \text{V}, \hspace{0.5cm} \text{unless otherwise specified}. \hspace{0.5cm} \text{C2} = 10 \mu\text{F}, \hspace{0.5cm} \text{C3} = 1.8 \mu\text{H}, \hspace{0.5cm} \text{C4} = 1.8 \mu\text{H}, \hspace$

| PARAMETER                            | DESCRIPTION                                   | CONDITIONS                                       | MIN      | TYP | MAX  | UNIT |

|--------------------------------------|-----------------------------------------------|--------------------------------------------------|----------|-----|------|------|

| DC CHARACTE                          | RISTICS                                       |                                                  | 1        | '   | '    |      |

| $V_{FB}$                             | Feedback Input Voltage                        |                                                  | 790      | 800 | 810  | mV   |

| I <sub>FB</sub>                      | Feedback Input Current                        |                                                  |          |     | 250  | nA   |

| $V_{IN}, V_{DD}$                     | Input Voltage                                 |                                                  | 2.5      |     | 5.5  | V    |

| V <sub>IN,OFF</sub>                  | Minimum Voltage for Shutdown                  | V <sub>IN</sub> falling                          | 2        |     | 2.2  | V    |

| V <sub>IN,ON</sub>                   | Maximum Voltage for Startup                   | V <sub>IN</sub> rising                           | 2.2      |     | 2.4  | V    |

| I <sub>DD</sub>                      | Supply Current                                | PWM, $V_{IN} = V_{DD} = 5V$                      |          | 400 | 500  | μΑ   |

|                                      |                                               | EN = 0, V <sub>IN</sub> = V <sub>DD</sub> = 5V   |          | 0.1 | 1    | μΑ   |

| R <sub>DS(ON)-PMOS</sub>             | PMOS FET Resistance                           | V <sub>DD</sub> = 5V, wafer test only            |          | 70  | 100  | mΩ   |

| R <sub>DS(ON)-NMOS</sub>             | NMOS FET Resistance                           | V <sub>DD</sub> = 5V, wafer test only            |          | 45  | 75   | mΩ   |

| I <sub>LMAX</sub>                    | Current Limit                                 |                                                  |          | 1.5 |      | Α    |

| T <sub>OT,OFF</sub>                  | Over-temperature Threshold                    | T rising                                         |          | 145 |      | °C   |

| T <sub>OT,ON</sub>                   | Over-temperature Hysteresis                   | T falling                                        |          | 130 |      | °C   |

| I <sub>EN</sub> , I <sub>RSI</sub>   | EN, RSI Current                               | V <sub>EN</sub> , V <sub>RSI</sub> = 0V and 3.3V | -1       |     | 1    | V    |

| V <sub>EN1</sub> , V <sub>RSI1</sub> | EN, RSI Rising Threshold                      | V <sub>DD</sub> = 3.3V                           |          |     | 2.4  | V    |

| V <sub>EN2</sub> , V <sub>RSI2</sub> | EN, RSI Falling Threshold                     | V <sub>DD</sub> = 3.3V                           | 0.8      |     |      | V    |

| V <sub>POR</sub>                     | Minimum V <sub>FB</sub> for POR, WRT Targeted | V <sub>FB</sub> rising                           |          |     | 95   | %    |

|                                      | V <sub>FB</sub> Value                         | V <sub>FB</sub> falling                          | 86       |     |      | %    |

| V <sub>OLPOR</sub>                   | POR Voltage Drop                              | I <sub>SINK</sub> = 5mA                          |          | 35  | 70   | mV   |

| AC CHARACTE                          | RISTICS                                       |                                                  | <u>.</u> |     |      |      |

| F <sub>PWM</sub>                     | PWM Switching Frequency                       |                                                  | 1.4      | 1.5 | 1.75 | MHz  |

| t <sub>RSI</sub>                     | Minimum RSI Pulse Width                       | Guaranteed by design                             |          | 25  | 50   | ns   |

| t <sub>SS</sub>                      | Soft-start Time                               |                                                  |          | 650 |      | μs   |

| t <sub>POR</sub>                     | Power On Reset Delay Time                     |                                                  | 80       | 100 | 120  | ms   |

intersil FN7396.8 July 13, 2006

# Pin Descriptions

| PIN NUMBER | PIN NAME | PIN FUNCTION                                                                                                          |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------|

| 1          | SGND     | Negative supply for the controller stage                                                                              |

| 2          | PGND     | Negative supply for the power stage                                                                                   |

| 3          | LX       | Inductor drive pin; high current digital output with average voltage equal to the regulator output voltage            |

| 4          | VIN      | Positive supply for the power stage                                                                                   |

| 5          | VDD      | Power supply for the controller stage                                                                                 |

| 6          | RSI      | Resets POR timer                                                                                                      |

| 7          | EN       | Enable                                                                                                                |

| 8          | POR      | Power on reset open drain output                                                                                      |

| 9          | VO       | Output voltage sense                                                                                                  |

| 10         | FB       | Voltage feedback input; connected to an external resistor divider between V <sub>O</sub> and SGND for variable output |

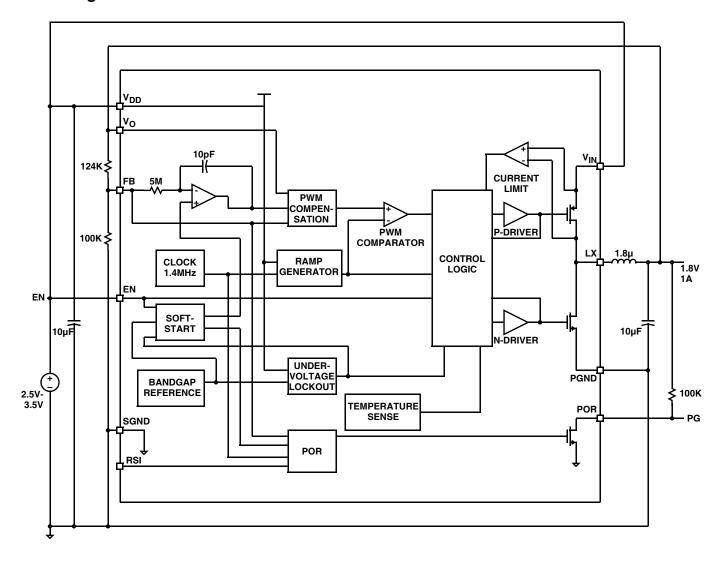

# **Block Diagram**

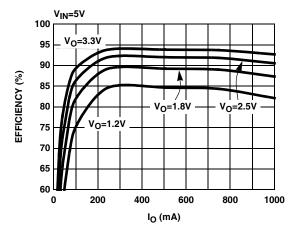

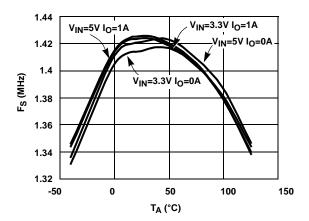

## Performance Curves and Waveforms

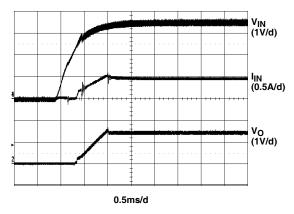

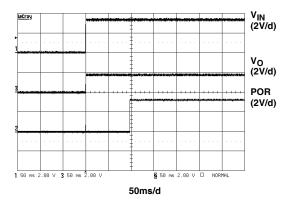

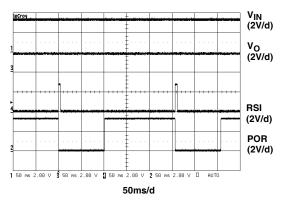

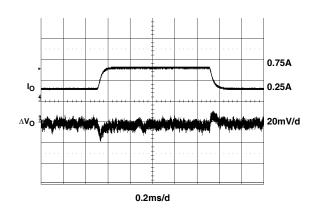

All waveforms are taken at  $V_{IN} = 3.3V$ ,  $V_O = 1.8V$ ,  $I_O = 1A$  with component values shown on page 1 at room ambient temperature, unless otherwise noted.

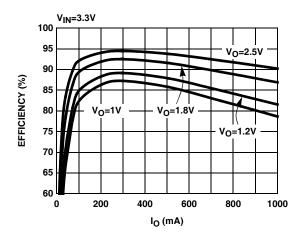

FIGURE 1. EFFICIENCY

FIGURE 3. F<sub>S</sub> vs JUNCTION TEMPERATURE

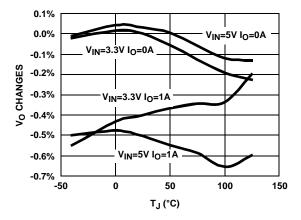

FIGURE 5. LOAD/LINE REGULATIONS vs JUNCTION TEMPERATURE

FIGURE 2. EFFICIENCY

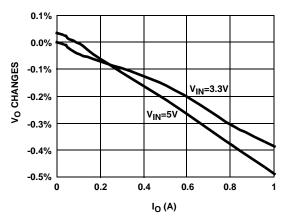

FIGURE 4. LOAD REGULATIONS

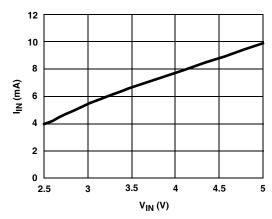

FIGURE 6. NO LOAD INPUT CURRENT

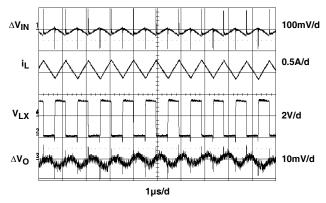

# Performance Curves and Waveforms (Continued)

All waveforms are taken at  $V_{IN} = 3.3V$ ,  $V_O = 1.8V$ ,  $I_O = 1A$  with component values shown on page 1 at room ambient temperature, unless otherwise noted.

FIGURE 7. START-UP 1

FIGURE 8. START-UP 2

FIGURE 9. POR FUNCTION

FIGURE 10. TRANSIENT RESPONSE

FIGURE 11. STEADY-STATE

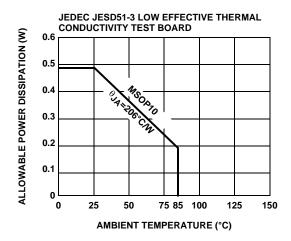

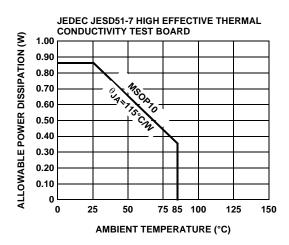

## Performance Curves and Waveforms (Continued)

All waveforms are taken at  $V_{IN} = 3.3V$ ,  $V_O = 1.8V$ ,  $I_O = 1A$  with component values shown on page 1 at room ambient temperature, unless otherwise noted.

FIGURE 12. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE

FIGURE 13. PACKAGE POWER DISSIPATION vs AMBIENT TEMPERATURE

## Applications Information

#### **Product Description**

The EL7536 is a synchronous, integrated FET 1A step-down regulator which operates from an input of 2.5V to 6V. The output voltage is user-adjustable with a pair of external resistors.

The internally-compensated controller makes it possible to use only two ceramic capacitors and one inductor to form a complete, very small footprint 1A DC:DC converter.

#### Start-Up and Shut-Down

When the EN pin is tied to  $V_{IN}$ , and  $V_{IN}$  reaches approximately 2.4V, the regulator begins to switch. The output voltage is gradually increased to ensure proper soft-start operation.

When the EN pin is connected to a logic low, the EL7536 is in the shut-down mode. All the control circuitry and both MOSFETs are off, and  $V_{OUT}$  falls to zero. In this mode, the total input current is less than 1 $\mu$ A.

When the EN reaches logic HI, the regulator repeats the start-up procedure, including the soft-start function.

#### **PWM Operation**

In the PWM mode, the P channel MOSFET and N channel MOSFET always operate complementary. When the PMOSFET is on and the NMOSFET off, the inductor current increases linearly. The input energy is transferred to the output and also stored in the inductor. When the P channel MOSFET is off and the N channel MOSFET on, the inductor current decreases linearly, and energy is transferred from the inductor to the output. Hence, the average current through the inductor is the output current. Since the inductor and the output capacitor act as a low pass filter, the duty cycle ratio is approximately equal to  $V_{\mbox{\scriptsize O}}$  divided by  $V_{\mbox{\scriptsize IN}}$ .

The output LC filter has a second order effect. To maintain the stability of the converter, the overall controller must be compensated. This is done with the fixed internally compensated error amplifier and the PWM compensator. Because the compensations are fixed, the values of input and output capacitors are 10µF to 22µF ceramic. The inductor is nominally 1.8µH, but 1.5µA to 2.2µH can be used.

#### 100% Duty Ratio Operation

EL7536 utilizes CMOS power FET's as the internal synchronous power switches. The upper switch is a PMOS and lower switch a NMOS. This not only saves a boot capacitor, it also allows 100% turn-on of the upper PFET switch, achieving  $V_O$  close to  $V_{IN}$ . The maximum achievable  $V_O$  is,

$$V_O = V_{IN} - (R_I + R_{DSON1}) \times I_O$$

Where RL is the DC resistance on the inductor and R<sub>DSON1</sub> the PFET on-resistance, nominal  $70m\Omega$  at room temperature with tempco of  $0.2m\Omega/^{\circ}C$ .

As the input voltage drops gradually close or even below the preset  $V_{\rm O}$ , the converter gets into 100% duty ratio. At this condition, the upper PFET needs some minimum turn-off time if it is turned off. This off-time is related to input/output conditions. This makes the duty ratio appears randomly and increases the output ripple somewhat until the 100% duty ratio is reached. Larger output capacitor could reduce the random-looking ripple. Users need to verify if this condition has adverse effect on overall circuit if close to 100% duty ratio is expected.

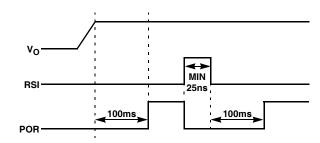

#### RSI/POR Function

When powering up, the open-collector Power-On-Reset output holds low for about 100ms after  $V_O$  reaches the preset voltage. When the active-HI reset signal RSI is issued, POR goes to low immediately and holds for the same period of time after RSI comes back to LOW. The output voltage is unaffected. (Please refer to the timing diagram). When the function is not used, connect RSI to ground and leave open the pull-up resister  $R_4$  at POR pin.

The POR output also serves as a 100ms delayed Power Good signal when the pull-up resister  $R_4$  is installed. The RSI pin needs to be directly (or indirectly through a resister  $R_6$ ) connected to Ground for this to function properly.

FIGURE 14. RSI & POR TIMING DIAGRAM

### **Output Voltage Selection**

Users can set the output voltage of the converter with a resister divider, which can be chosen based on the following formula:

$$V_O = 0.8 \times \left(1 + \frac{R_2}{R_1}\right)$$

#### **Component Selection**

Because of the fixed internal compensation, the component choice is relatively narrow. We recommend  $10\mu F$  to  $22\mu F$  multi-layer ceramic capacitors with X5R or X7R rating for both the input and output capacitors, and  $1.5\mu H$  to  $2.2\mu H$  inductance for the inductor.

<u>intersil</u>

At extreme conditions ( $V_{IN}$  < 3V,  $I_O$  > 0.7A, and junction temperature higher than 75°C), input cap  $C_1$  is recommended to be 22 $\mu$ F. Otherwise, if any of the above 3 conditions is not true,  $C_1$  can remain as low as 10 $\mu$ F.

The RMS current present at the input capacitor is decided by the following formula:

$$I_{INRMS} = \frac{\sqrt{V_O \times (V_{IN} - V_O)}}{V_{IN}} \times I_O$$

This is about half of the output current  $I_O$  for all the  $V_O$ . This input capacitor must be able to handle this current.

The inductor peak-to-peak ripple current is given as:

$$\Delta I_{IL} = \frac{(V_{IN} - V_{O}) \times V_{O}}{L \times V_{IN} \times f_{S}}$$

- · L is the inductance

- fs the switching frequency (nominally 1.4MHz)

The inductor must be able to handle  $I_{\rm O}$  for the RMS load current, and to assure that the inductor is reliable, it must handle the 1.5A surge current that can occur during a current limit condition.

In addition to decoupling capacitors and inductor value, it is important to properly size the phase-lead capacitor  $C_4$  (Refer to the Typical Application Diagram). The phase-lead capacitor creates additional phase margin in the control loop by generating a zero and a pole in the transfer function. As a general rule of thumb,  $C_4$  should be sized to start the phase-lead at a frequency of ~2.5kHz. The zero will always appear at lower frequency than the pole and follow the equation below:

$$f_Z = \frac{1}{2\pi R_2 C_4}$$

Over a normal range of  $R_2$  (~10-100k),  $C_4$  will range from ~470-4700pF. The pole frequency cannot be set once the zero frequency is chosen as it is dictated by the ratio of  $R_1$  and  $R_2$ , which is solely determined by the desired output set point. The equation below shows the pole frequency relationship:

$$f_P = \frac{1}{2\pi (R_1 \big| \big| R_2) C_4}$$

## **Current Limit and Short-Circuit Protection**

The current limit is set at about 1.5A for the PMOS. When a short-circuit occurs in the load, the preset current limit restricts the amount of current available to the output, which causes the output voltage to drop below the preset voltage. In the meantime, the excessive current heats up the regulator until it reaches the thermal shut-down point.

#### Thermal Shut-Down

Once the junction reaches about 145°C, the regulator shuts down. Both the P channel and the N channel MOSFETs turn off. The output voltage will drop to zero. With the output MOSFETs turned off, the regulator will soon cool down. Once the junction temperature drops to about 130°C, the regulator will restart again in the same manner as EN pin connects to logic HI.

#### Thermal Performance

The EL7536 is in a fused-lead MSOP10 package. Compared with regular MSOP10 package, the fused-lead package provides lower thermal resistance. The  $\theta_{JA}$  is 100°C/W on a 4-layer board and 125°C/W on 2-layer board. Maximizing the copper area around the pins will further improve the thermal performance.

#### Layout Considerations

The layout is very important for the converter to function properly. The following PC layout guidelines should be followed:

- Separate the Power Ground (1) and Signal Ground (1); connect them only at one point right at the pins

- Place the input capacitor as close to V<sub>IN</sub> and PGND pins as possible

- Make the following PC traces as small as possible:

- from L<sub>X</sub> pin to L

- from CO to PGND

- If used, connect the trace from the FB pin to R1 and R2 as close as possible

- Maximize the copper area around the PGND pin

- Place several via holes under the chip to additional ground plane to improve heat dissipation

The demo board is a good example of layout based on this outline. Please refer to the EL7536 Application Brief.

<u>intersil</u>

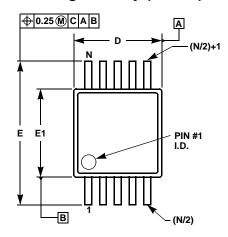

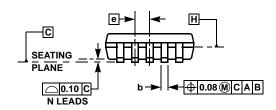

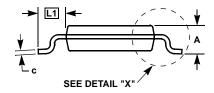

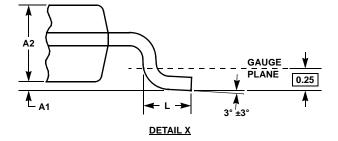

# Mini SO Package Family (MSOP)

# MDP0043 MINI SO PACKAGE FAMILY

| SYMBOL | MSOP8 | MSOP10 | TOLERANCE   | NOTES |

|--------|-------|--------|-------------|-------|

| А      | 1.10  | 1.10   | Max.        | -     |

| A1     | 0.10  | 0.10   | ±0.05       | -     |

| A2     | 0.86  | 0.86   | ±0.09       | -     |

| b      | 0.33  | 0.23   | +0.07/-0.08 | -     |

| С      | 0.18  | 0.18   | ±0.05       | -     |

| D      | 3.00  | 3.00   | ±0.10       | 1, 3  |

| Е      | 4.90  | 4.90   | ±0.15       | -     |

| E1     | 3.00  | 3.00   | ±0.10       | 2, 3  |

| е      | 0.65  | 0.50   | Basic       | -     |

| L      | 0.55  | 0.55   | ±0.15       | -     |

| L1     | 0.95  | 0.95   | Basic       | -     |

| N      | 8     | 10     | Reference   | -     |

Rev. C 6/99

#### NOTES:

- Plastic or metal protrusions of 0.15mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25mm maximum per side are not included.

- 3. Dimensions "D" and "E1" are measured at Datum Plane "H".

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9000 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil