# LM3475

# **Hysteretic PFET Buck Controller**

# **General Description**

The LM3475 is a hysteretic P-FET buck controller designed to support a wide range of high efficiency applications in a very small SOT23-5 package. The hysteretic control scheme has several advantages, including simple system design with no external compensation, stable operation with a wide range of components, and extremely fast transient response. Hysteretic control also provides high efficiency operation, even at light loads. The PFET architecture allows for low component count as well as 100% duty cycle and ultralow dropout operation.

#### **Features**

- Easy to use control methodology

- 0.8V to V<sub>IN</sub> adjustable output range

- High Efficiency (90% typical)

- ±0.9% (±1.5% over temp) feedback voltage

- 100% duty cycle capable

- Maximum operating frequency up to 2MHz

- Internal Soft-Start

- Enable pin

- SOT23-5 package

# **Applications**

- TFT Monitor

- Auto PC

- Vehicle Security

- Navigation Systems

- Notebook Standby Supply

- Battery Powered Portable Applications

- Distributed Power Systems

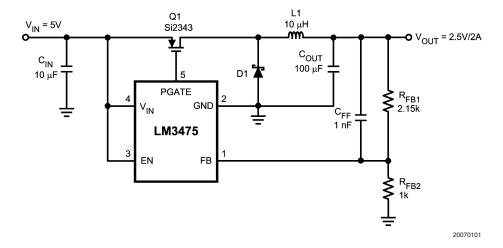

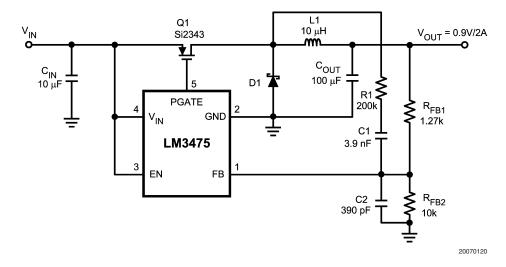

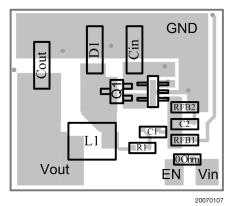

# **Typical Application Circuit**

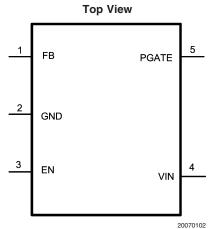

# **Connection Diagram**

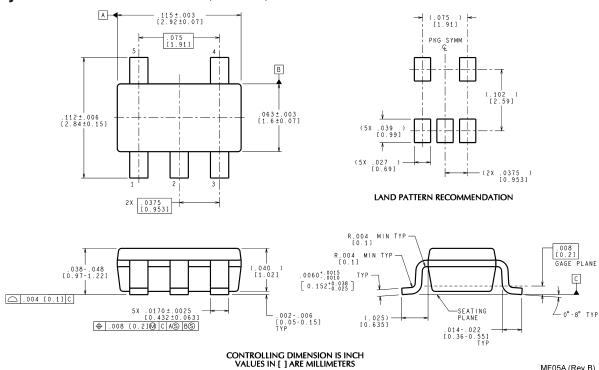

5 Lead Plastic SOT23-5 NS package Number MF05A

# **Package Marking and Ordering Information**

| Order Number | Package Type | Package Marking | Supplied As:                |

|--------------|--------------|-----------------|-----------------------------|

| LM3475MF     | SOT23-5      | S65B            | 1000 units on Tape and Reel |

| LM3475MFX    | SOT23-5      | S65B            | 3000 units on Tape and Reel |

# **Pin Description**

| Pin Name | Pin Number | Description                                                      |  |

|----------|------------|------------------------------------------------------------------|--|

| FB       | 1          | Feedback input. Connect to a resistor divider between the output |  |

|          |            | and GND.                                                         |  |

| GND      | 2          | Ground.                                                          |  |

| EN       | 3          | Enable. Pull this pin above 1.5V (typical) for normal operation. |  |

|          |            | When EN is low, the device enters shutdown mode.                 |  |

| VIN      | 4          | Power supply input.                                              |  |

| PGATE    | 5          | Gate drive output for the external PFET.                         |  |

215°C

220°C

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-0.3V to 16V  $V_{IN}$ **PGATE** -0.3V to 16V FΒ -0.3V to 5V ΕN -0.3V to 16V Storage Temperature -65°C to 150°C

Power Dissipation (Note 2) **ESD Susceptibilty**

Human Body Model (Note 3)

Lead Temperature Vapor Phase (60 sec.) Infared (15 sec.)

# **Operating Ratings** (Note 1)

Supply Voltage 2.7V to 10V

**Operating Junction**

Temperature -40°C to +125°C

### **Electrical Characteristics**

Specifications in Standard type face are for  $T_J = 25^{\circ}C$ , and in **bold type face** apply over the full **Operating Temperature** Range ( $T_J = -40$ °C to +125°C). Unless otherwise specified,  $V_{IN} = EN = 5.0V$ . Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis.

440mW

2.5kV

| Symbol                          | Parameter                           | Conditions                                  | Min   | Тур   | Max   | Unit |  |

|---------------------------------|-------------------------------------|---------------------------------------------|-------|-------|-------|------|--|

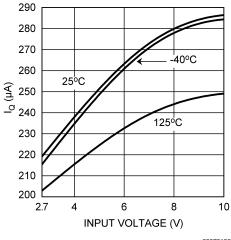

| I <sub>Q</sub>                  | Quiescent Current                   | EN = V <sub>IN</sub> (PGATE<br>Open)        | 170   | 260   | 320   | μΑ   |  |

|                                 |                                     | EN = 0V                                     | 4     | 7     | 10    |      |  |

| $V_{FB}$                        | Feedback Voltage                    |                                             | 0.788 | 0.8   | 0.812 | V    |  |

| $\%\Delta V_{FB}/\Delta V_{IN}$ | Feedback Voltage<br>Line Regulation | 2.7V < V <sub>IN</sub> < 10V                |       | 0.01  |       | %/V  |  |

| V <sub>HYST</sub>               | Comparator                          | 2.7V < V <sub>IN</sub> < 10V                |       | 21    | 28    | mV   |  |

|                                 | Hysteresis                          | -40°C to +125°C                             | 21    |       | 32    |      |  |

| I <sub>FB</sub>                 | FB Bias Current                     |                                             |       | 50    | 600   | nA   |  |

| Vth <sub>EN</sub>               | Enable Threshold<br>Voltage         | Increasing                                  | 1.2   | 1.5   | 1.8   | V    |  |

|                                 | Hysteresis                          |                                             |       | 365   |       | mV   |  |

| I <sub>EN</sub>                 | Enable Leakage<br>Current           | EN = 10V                                    |       | .025  | 1     | μΑ   |  |

| R <sub>PGATE</sub>              | Driver Resistance                   | Source<br>I <sub>SOURCE</sub> = 100mA       |       | 2.8   |       | Ω    |  |

|                                 | Driver Resistance                   | Sink<br>I <sub>Sink</sub> = 100mA           |       | 1.8   |       |      |  |

| I <sub>PGATE</sub>              | Driver Output Current               | Source $V_{PGATE} = 3.5V$ $C_{PGATE} = 1nF$ |       | 0.475 |       | A    |  |

|                                 | Driver Output Current               | Sink $V_{PGATE} = 3.5V$ $C_{PGATE} = 1nF$   |       | 1.0   |       |      |  |

| T <sub>SS</sub>                 | Soft-Start Time                     | 2.7V < V <sub>IN</sub> < 10V<br>(EN Rising) |       | 4     |       | ms   |  |

| T <sub>ONMIN</sub>              | Minimum On-Time                     | PGATE Open                                  |       | 180   |       | ns   |  |

| V <sub>UVD</sub>                | Under Voltage<br>Detection          | Measured at the FB<br>Pin                   | 0.487 | 0.56  | 0.613 | V    |  |

| Note 1: Abstractional Note 2: The the ambient P <sub>D_MAX</sub> = ( | rical Charact solute maximum ratings a al, but device parameter se maximum allowable power temperature, T <sub>A</sub> . The material T <sub>J_MAX</sub> - T <sub>A</sub> )/ $\theta$ <sub>JA</sub> . The material buman body model is a | re limits beyond which d<br>pecifications may not be<br>ver dissipation is a function<br>eximum allowable power<br>eximum power dissipation | lamage to the device<br>e guaranteed. For gu<br>on of the maximum ju<br>dissipation at any an<br>n of 0.44W is determ | aranteed specification unction temperature, T mbient temperature is ined using $T_A = 25^{\circ}C$ | as and test conditions $f_{J_MAX}$ , the junction-to calculated using:<br>$f_{J_MAX}$ , $f_{J_MAX}$ , $f_{J_MAX}$ , and $f_{J_MAX}$ = 225°C/W, and | s, see the Electrical (<br>o-ambient thermal res | Characteristics. |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------|

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

|                                                                      |                                                                                                                                                                                                                                          |                                                                                                                                             |                                                                                                                       |                                                                                                    |                                                                                                                                                    |                                                  |                  |

# $\begin{tabular}{ll} \textbf{Typical Performance Characteristics} & \textbf{Unless specified otherwise, all curves taken at $V_{IN}=5$V,} \\ V_{OUT}=2.5V, \ L=10 \ \mu\text{H}, \ C_{OUT}=100 \ \mu\text{F}, \ ESR=100 m\Omega, \ \text{and } T_A=25^{\circ}\text{C}. \\ \end{tabular}$

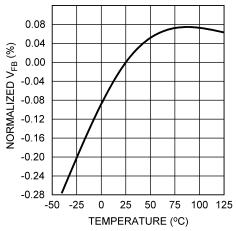

# Feedback Voltage vs Temperature

20070123

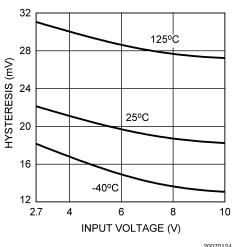

#### Hysteresis Voltage vs Input Voltage

Hysteresis Voltage vs Temperature

2007012

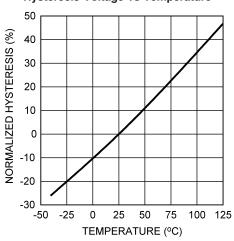

### **Efficiency vs Load Current**

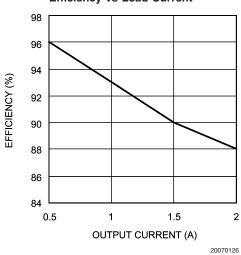

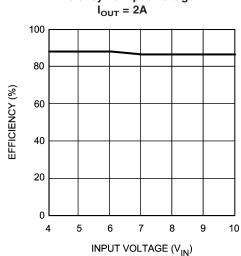

# Efficiency vs Input Voltage

20070127

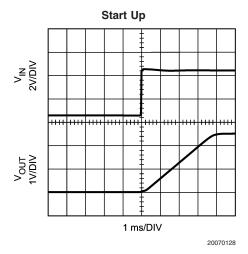

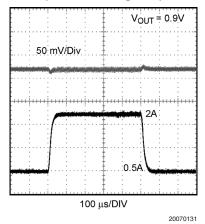

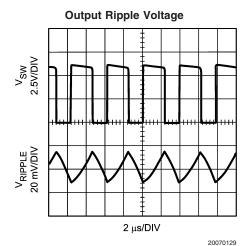

**Typical Performance Characteristics** Unless specified otherwise, all curves taken at  $V_{IN}$  = 5V,  $V_{OUT}$  = 2.5V, L = 10  $\mu$ H,  $C_{OUT}$  = 100  $\mu$ F, ESR = 100 $m\Omega$ , and  $T_A$  = 25°C. (Continued)

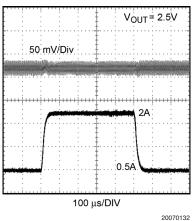

Load Transient Response with External Ramp (Circuit from Figure 3)

Load Transient Response (Typical Application Circuit from *Figure 5*)

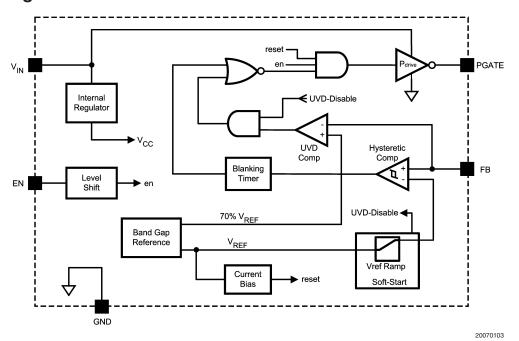

### **Block Diagram**

# **Operation Description**

#### **OVERVIEW**

The LM3475 is a buck (step-down) DC-DC controller that uses a hysteretic control architecture, which results in Pulse Frequency Modulated (PFM) regulation. The hysteretic control scheme does not utilize an internal oscillator. Switching frequency depends on external components and operating conditions. Operating frequency decreases at light loads, resulting in excellent efficiency compared to PWM architectures. Because switching is directly controlled by the output conditions, hysteretic control provides exceptional load transient response.

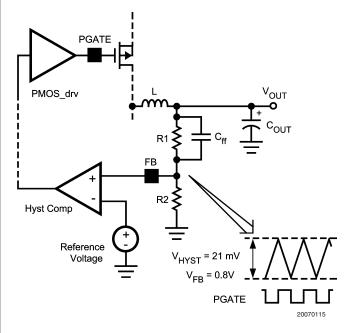

#### HYSTERETIC CONTROL CIRCUIT

The LM3475 uses a comparator-based voltage control loop. The voltage on the feedback pin is compared to a 0.8V reference with 21mV of hysteresis. When the FB input to the comparator falls below the reference voltage, the output of the comparator goes low. This results in the driver output, PGATE, pulling the gate of the PFET low and turning on the PFET.

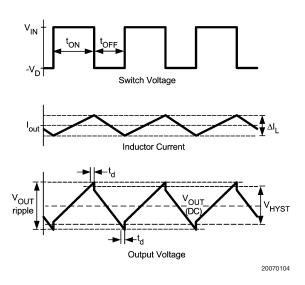

With the PFET on, the input supply charges  $C_{\text{OUT}}$  and supplies current to the load through the PFET and the inductor. Current through the inductor ramps up linearly, and the output voltage increases. As the FB voltage reaches the upper threshold (reference voltage plus hysteresis) the output of the comparator goes high, and the PGATE turns the PFET off. When the PFET turns off, the catch diode turns on, and the current through the inductor ramps down. As the output voltage falls below the reference voltage, the cycle repeats. The resulting output, inductor current, and switch node waveforms are shown in *Figure 1*.

**FIGURE 1. Hysteretic Waveforms**

The LM3475 operates in discontinuous conduction mode at light load current and continuous conduction mode at heavy load current. In discontinuous conduction mode, current through the inductor starts at zero and ramps up to the peak, then ramps down to zero. The next cycle starts when the FB voltage reaches the reference voltage. Until then, the inductor current remains zero. Operating frequency is low, as are switching losses. In continuous conduction mode, current always flows through the inductor and never ramps down to zero.

#### **SOFT-START**

The LM3475 includes an internal soft-start function to protect components from excessive inrush current and output voltage overshoot. As  $V_{\rm IN}$  rises above 2.7V (typical), the internal bias circuitry becomes active. When EN goes high, the

# **Operation Description** (Continued)

device enters soft-start. During soft-start, the reference voltage is ramped up to the nominal value of 0.8V in approximately 4ms. Duty cycle and output voltage will increase as the reference voltage is ramped up.

#### UNDER VOLTAGE DETECTION

When the output voltage falls below 70% (typical) of the normal voltage, as measured at the FB pin, the device turns off PFET and restarts a new soft-start cycle. In short circuit, the PFET is always on, and the converter is effectively a resistor divider from input to output to ground. Whether the part restarts depends on the power path resistance and the short circuit resistance. This feature should not be considered as overcurrent protection or output short circuit protection.

#### **PGATE**

During switching, the PGATE pin swings from  $V_{IN}$  (off) to ground (on). As input voltage increases, the time it takes to slew the gate of the PFET on and off also increases. Also, as the PFET gate voltage approaches  $V_{IN}$ , the PGATE current driving capability decreases. This can cause a significant additional delay in turning the switch off when using a PFET with a low threshold voltage. These two effects will increase power dissipation and reduce efficiency. Therefore, a PFET with relatively high threshold voltage and low gate capacitance is recommended.

#### MINIMUM ON/OFF TIME

To ensure accurate comparator switching, the LM3475 imposes a blanking time after each comparator state change. This blanking time is 180ns typically. Immediately after the comparator goes high or low, it will be held in that state for the duration of the blanking time. This helps keep the hysteretic comparator from improperly responding to switching noise spikes (See Reducing Switching Noise) and ESL spikes (See Output Capacitor Selection) at the output.

At very low or very high duty cycle operation, maximum frequency will be limited by the blanking time. The maximum operating frequency can be determined by the following equations:

$$F_{MAX} = D / ton_{min}$$

$F_{MAX} = (1-D) / toff_{min}$

Where D is the duty cycle, defined as  $V_{OUT}/V_{IN}$ , and ton<sub>min</sub> and toff<sub>min</sub> is the sum of the blanking time, the propagation delay time and the PFET delay time (see *Figure 1*).

#### **ENABLE PIN (EN)**

The LM3475 provides a shutdown function via the EN pin to disable the device. The device is active when the EN pin is pulled above 1.5V (typ) and in shutdown mode when EN is below 1.135V (typ). In shutdown mode, total quiescent current is less than  $10\mu A$ . The EN pin can be directly connected to  $V_{\text{IN}}$  for always-on operation.

### **Design Information**

#### **SETTING OUTPUT VOLTAGE**

The output voltage is programmed using a resistor divider between V<sub>OUT</sub> and GND as shown in *Figure 2*. The feedback resistors can be calculated as follows:

$$V_{OUT} = \frac{R_1 + R_2}{R_2} \times V_{FB}$$

Where Vfb is 0.8V typically.

The feedback resistor ratio,  $\alpha = (R1+R2) / R2$ , will also be used below to calculate output ripple and operating frequency.

FIGURE 2. Hysteretic Window

# SETTING OPERATING FREQUENCY AND OUTPUT RIPPLE

Although hysteretic control is a simple control scheme, the operating frequency and other performance characteristics depend on external conditions and components. If the inductance, output capacitance, ESR,  $V_{\rm IN}$ , or  $C_{\rm ff}$  is changed, there will be a change in the operating frequency and possibly output ripple. Therefore, care must be taken to select components which will provide the desired operating range. The best approach is to determine what operating frequency is desirable in the application and then begin with the selection of the inductor and output capacitor ESR. The design process usually involves a few iterations to select appropriate standard values that will result in the desired frequency and ripple.

Without the feedforward capacitor ( $C_{\rm ff}$ ), the operating frequency (F) can be approximately calculated using the formula:

$$F = \frac{V_{OUT}}{V_{IN}} \times \frac{(V_{IN} - V_{OUT}) \times ESR}{(V_{HYST} \times \alpha \times L) + (V_{IN} \times delay \times ESR)}$$

Where delay is the sum of the LM3475 propagation delay time and the PFET delay time. The propagation delay is 90ns typically.

Minimum output ripple voltage can be determined using the following equation:

$$V_{OUT\ PP} = V_{HYST} (R1 + R2) / R2$$

#### **USING A FEED-FORWARD CAPACITOR**

The operating frequency and output ripple voltage can also be significantly influenced using a speed up capacitor, Cff, as shown in Figure 2. Cff is connected in parallel with the high side feedback resistor, R1. The output ripple causes a current to be sourced or sunk through this capacitor. This current is essentially a square wave. Since the input to the feedback pin (FB) is a high impedance node, the bulk of the current flows through R2. This superimposes a square wave ripple voltage on the FB node. The end result is a reduction in output ripple and an increase in operating frequency. When adding  $C_{ff}$ , calculate the formula above with  $\alpha$ = 1. The value of Cff depends on the desired operating frequency and the value of R2. A good starting point is 1nF ceramic at 100kHz decreasing linearly with increased operating frequency. Also note that as the output voltage is programmed below 1.6V, the effect of C<sub>ff</sub> will decrease significantly.

#### INDUCTOR SELECTION

The most important parameters for the inductor are the inductance and the current rating. The LM3475 operates over a wide frequency range and can use a wide range of inductance values. Minimum inductance can be calculated using the following equation:

$$L = \frac{V_{IN} - V_{SD} - V_{OUT}}{\Delta I} \times \frac{D}{F}$$

Where D is the duty cycle, defined as  $V_{OUT}/V_{IN}$ , and  $\Delta I$  is the allowable inductor ripple current.

Maximum allowable inductor ripple current should be calculated as a function of output current ( $I_{OUT}$ ) as shown below:

$$\Delta I_{\text{max}} = I_{\text{OUT}} \times 0.3$$

The inductor must also be rated to handle the peak current ( $I_{PK}$ ) and RMS current given by:

$$I_{PK} = (I_{OUT} + \Delta I/2) \times 1.1$$

$$I_{RMS} = \sqrt{I_{OUT}^2 + \frac{\Delta I^2}{3}}$$

The inductance value and the resulting ripple is one of the key parameters controlling operating frequency.

#### **OUTPUT CAPACITOR SELECTION**

Once the desired operating frequency and inductance value are selected, ESR must be selected based on the equation in the Setting Operating Frequency and Output Ripple. This process may involve a few iterations to select standard ESR and inductance values.

In general, the ESR of the output capacitor and the inductor ripple current create the output ripple of the regulator. However, the comparator hysteresis sets the first order value of this ripple. Therefore, as ESR and ripple current vary, operating frequency must also vary to keep the output ripple

# **Design Information** (Continued)

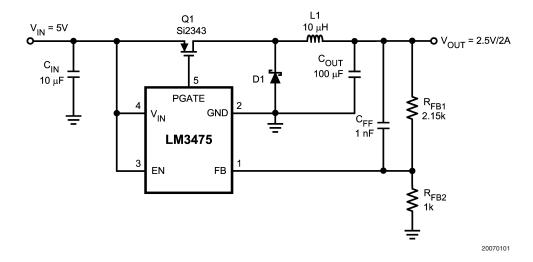

voltage regulated. The hysteretic control topology is well suited to using ceramic output capacitors. However, ceramic capacitors have a very low ESR, resulting in a 90° phase shift of the output voltage ripple. This results in low operating frequency and increased output ripple. To fix this problem a low value resistor could be added in series with the ceramic output capacitor. Although counter intuitive, this combination of a ceramic capacitor and external series resistance provide highly accurate control over the output voltage ripple. Another method is to add an external ramp at the FB pin as shown in *Figure 3*. By proper selection of R1 and C2, the FB pin sees faster voltage change than the output ripple can cause. As a result, the switching frequency is higher while the output ripple becomes lower. The switching frequency is approximately:

$$F = \frac{V_{IN}}{2\pi \times R_1 \times C_2 \times V_{HYS}}$$

Other types of capacitor, such as Sanyo POSCAP, OS-CON, and Nichicon 'NA' series are also recommended and may be used without additional series resistance. For all practical purposes, any type of output capacitor may be used with proper circuit verification.

Capacitors with high ESL (equivalent series inductance) values should not be used. As shown in *Figure 1*, the output ripple voltage contains a small step at both the high and low peaks. This step is caused by and is directly proportional to the output capacitor's ESL. A large ESL, such as in an electrolytic capacitor, can create a step large enough to cause abnormal switching behavior.

#### INPUT CAPACITOR SELECTION

A bypass capacitor is required between  $V_{\rm IN}$  and ground. It must be placed near the source of the external PFET. The input capacitor prevents large voltage transients at the input and provides the instantaneous current when the PFET turns on. The important parameters for the input capacitor are the voltage rating and the RMS current rating. Follow the manufacturer's recommended voltage de-rating. RMS current and power dissipation (PD) can be calculated with the equations below:

$$I_{RMS\_CIN} = \frac{I_{OUT}}{V_{IN}} \sqrt{V_{OUT} x (V_{IN} - V_{OUT})}$$

FIGURE 3. External Ramp

### **DIODE SELECTION**

The catch diode provides the current path to the load during the PFET off time. Therefore, the current rating of the diode must be higher than the average current through the diode, which be calculated as shown:

$$I_{D\_AVE} = I_{OUT} x (1 - D)$$

The peak voltage across the catch diode is approximately equal to the input voltage. Therefore, the diode's peak reverse voltage rating should be greater than 1.3 times the input voltage.

A Schottky diode is recommended, since a low forward voltage drop will improve efficiency.

For high temperature applications, diode leakage current may become significant and require a higher reverse voltage rating to achieve acceptable performance.

### P-CHANNEL MOSFET SELECTION

The PFET switch should be selected based on the maximum Drain-Source voltage (VDS), Drain current rating (ID), maximum Gate-Source voltage (VGS), on resistance (RDSON), and Gate capacitance. The voltage across the PFET when it is turned off is equal to the sum of the input voltage and the diode forward voltage. The VDS must be selected to provide some margin beyond the sum of the input voltage and Vd. Since the current flowing through the PFET is equal to the current through the inductor, ID must be rated higher than the maximum IPK. During switching, PGATE swings the PFET's gate from VIN to ground. Therefore, A PFET must be selected with a maximum VGS larger than VIN. To insure that the PFET turns on completely and quickly, refer to the PGATE section.

### **Design Information** (Continued)

The power loss in the PFET consists of switching losses and conducting losses. Although switching losses are difficult to precisely calculate, the equation below can be used to estimate total power dissipation. Increasing  $R_{\rm DSON}$  will increase power losses and degrade efficiency. Note that switching losses will also increase with lower gate threshold voltages.

$PD_{switch} = R_{DSON}x (I_{OUT})^2 x D + F x I_{OUT}x V_{IN}x (t_{on} + t_{off})/2$ where:

ton = FET turn on time

$t_{off} = FET turn off time$

A value of 10ns to 50ns is typical for ton and toff. Note that the  $R_{\rm DSON}$  has a positive temperature coefficient. At 100°C, the  $R_{\rm DSON}$  may be as much as 150% higher than the value at 25°C.

The Gate capacitance of the PFET has a direct impact on both PFET transition time and the power dissipation in the LM3475. Most of the power dissipated in the LM3475 is used to drive the PFET switch. This power can be calculated as follows:

The amount of average gate driver current required during switching (I $_{\rm G}$ ) is:

$$I_G = Q_g \times F$$

And the total power dissipated in the device is:

$$I_aV_{IN} + I_GV_{IN}$$

Where  $I_{\rm q}$  is typically 260 $\mu$ A as shown in the Electrical Characteristics table. As gate capacitance increases, operating frequency may need to be reduced, or additional heat sinking may be required to lower the power dissipation in the device.

In general, keeping the gate capacitance below 2000pF is recommended to keep transition times (switching losses), and power losses low.

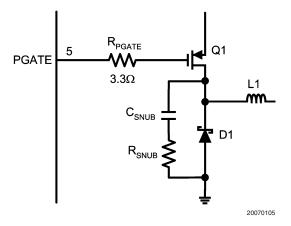

#### REDUCING SWITCHING NOISE

Although the LM3475 employs internal noise suppression circuitry, external noise may continue to be excessive. There are several methods available to reduce noise and EMI.

MOSFETs are very fast switching devices. The fast increase in PFET current coupled with parasitic trace inductance can create unwanted noise spikes at both the switch node and at  $V_{\rm IN}$ . Switching noise will increase with load current and input voltage. This noise can also propagate through the ground plane, sometimes causing unpredictable device performance. Slowing the rise and fall times of the PFET can be very effective in reducing this noise. Referring to *Figure 4*, the PFET can be slowed down by placing a small  $(1\Omega-10\Omega)$

resistor in series with PGATE. However, this resistor will increase the switching losses in the PFET and will lower efficiency. Therefore it should be kept as small as possible and only used when necessary. Another method to reduce switching noise (other than good PCB layout, see Layout section) is to use a small RC filter or snubber. The snubber should be placed in parallel with the catch diode, connected close to the drain of the PFET, as shown in Figure 4. Again, the snubber should be kept as small as possible to limit its impact on system efficiency. A typical range is a  $10\Omega\text{-}100\Omega$  resistor and a 470pF to 2.2nF ceramic capacitor.

FIGURE 4. PGATE Resistor and Snubber

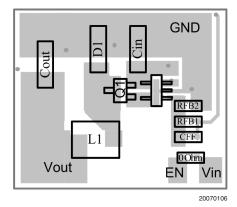

### Layout

PC board layout is very important in all switching regulator designs. Poor layout can cause EMI problems, excess switching noise and poor operation.

As shown in *Figure 6* and *Figure 7*, place the ground of the input capacitor as close as possible to the anode of the diode. This path also carries a large AC current. The switch node, the node connecting the diode cathode, inductor, and PFET drain, should be kept as small as possible. This node is one of the main sources for radiated EMI.

The feedback pin is a high impedance node and is therefore sensitive to noise. Be sure to keep all feedback traces away from the inductor and the switch node, which are sources of noise. Also, the resistor divider should be placed close to the FB pin. The gate pin of the external PFET should be located close to the PGATE pin.

Using a large, continuous ground plane is also recommended, particularly in higher current applications.

# Layout (Continued)

FIGURE 5.

### **Bill of Materials**

| Designator       | Description       | Part Number      | Vendor                |

|------------------|-------------------|------------------|-----------------------|

| C <sub>IN</sub>  | 10μF, 16V, X5R    | EMK325BJ106MN    | TAIYO YUDEN           |

| C <sub>OUT</sub> | 100μF, 6V, Ta     | TPSY107M006R0100 | AVX                   |

| C <sub>FF</sub>  | 1nF, 25V, X7R     | VJ1206Y102KXXA   | Vishay                |

| D1               | Schottky, 20V, 2A | CMSH2-20L        | Central Semiconductor |

| L1               | 10μH, 3.1A        | CDRH103R100      | Sumida                |

| Q1               | 30V, 2.5A         | Si2343           | Vishay                |

| R <sub>FB2</sub> | 1kΩ, 0805, 1%     | CRW08051001F     | Vishay                |

| R <sub>FB1</sub> | 2.15kΩ, 0805, 1%  | CRCW08052151F    | Vishay                |

FIGURE 6. Top Layer (Standard Board) (2:1 Scale)

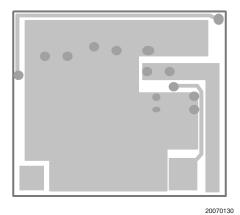

# Layout (Continued)

FIGURE 7. Top Layer (with External Ramp) (2:1 Scale)

FIGURE 8. Bottom Layer (2:1 Scale)

### Physical Dimensions inches (millimeters) unless otherwise noted

5 Lead Plastic SOT23-5 NS package Number MF05A

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

**National Semiconductor Americas Customer** Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com **National Semiconductor** Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

MF05A (Rev B)