## STBB1XX

## 1 A, high efficiency single inductor dual mode buck-boost DC-DC converter

#### **Features**

- Buck-boost DC-DC converter

- Operating input voltage range from 2.0 V to 5.5

- 2% DC feedback voltage tolerance

- Synchronous rectification

- Shutdown function

- 1.5 MHz switching frequency

- Power save mode at light load

- Typical efficiency: > 94 %

- 1 A output current capability

- Shutdown current < 1 µA

- Available in DFN10 (3 x 3 mm)

#### **Applications**

- Single cell Li-lon and 3 cells alkaline, Ni-MH powered devices

- SD/MMC memory card supply

- Palmtop computers

- Cell phones

- Digital cameras

### **Description**

The STBB1 is a fixed frequency, high efficiency, buck-boost DC-DC converter able to provide output voltages ranging from 1.2 V to 5.5 V and input voltages from 2.0 V to 5.5 V. The device can operate with input voltages higher than, equal to, or lower than the output voltage making the product suitable for single lithium-lon, multicell alkaline or NiMH applications where the output voltage is within the battery voltage range. The

Table 1. Device summary

| Table 1. | Device Summary |         |                |

|----------|----------------|---------|----------------|

|          | Order code     | Marking | Output voltage |

|          | STBB1PUR       | BB1     | ADJ            |

DFN10 (3 x 3 mm)

integrated low-R<sub>DSon</sub> N-channel and P-channel MOSFET switches contribute to its high efficiency. The MODE pin allows selecting between auto mode and forced PWM mode thus taking benefit either of lower power consumption or best dynamic performance. The device includes also soft-start control, thermal shutdown and current limit. The STBB1 is packaged in DFN10 (3 x 3 mm).

September 2010 Doc ID 15474 Rev 5 1/21

Contents STBB1XX

## **Contents**

| 1  | Bloc  | k diagra          | am                                                   | 3      |  |  |  |  |

|----|-------|-------------------|------------------------------------------------------|--------|--|--|--|--|

| 2  | Abso  | olute ma          | aximum ratings                                       | 4      |  |  |  |  |

| 3  | Pin o | Pin configuration |                                                      |        |  |  |  |  |

| 4  | Турі  | cal appl          | lication                                             | 6      |  |  |  |  |

| 5  | Elec  | trical ch         | naracteristics                                       | 7      |  |  |  |  |

| 6  | Deta  | iled des          | scription                                            | 9      |  |  |  |  |

|    | 6.1   | Genera            | al description                                       | 9      |  |  |  |  |

|    | 6.2   | Dual m            | node operation                                       | 9      |  |  |  |  |

|    | 6.3   | Externa           | al synchronization                                   | 10     |  |  |  |  |

|    | 6.4   | Enable            | e pin                                                | 10     |  |  |  |  |

|    | 6.5   | Protect           | tion features                                        | 10     |  |  |  |  |

|    |       | 6.5.1             | Soft-start and short-circuit                         | 10     |  |  |  |  |

|    |       | 6.5.2             | Under-voltage lockout                                | 10     |  |  |  |  |

|    |       | 6.5.3             | Over-temperature protection                          | 10     |  |  |  |  |

| 7  | Турі  | cal perfo         | ormance characteristics                              | 11     |  |  |  |  |

| 8  | Арр   | lication          | information                                          | 13     |  |  |  |  |

|    | 8.1   | Progra            | mming the output voltage                             | 13     |  |  |  |  |

|    | 8.2   | Inducto           | or selection                                         | 13     |  |  |  |  |

|    | 8.3   | Input a           | and output capacitor selection                       | 14     |  |  |  |  |

| 9  | Reco  | ommend            | ded PCB layout                                       | 15     |  |  |  |  |

| 10 | Pack  | age me            | echanical data                                       | 16     |  |  |  |  |

| 11 | Diffe | erent out         | tput voltage versions of the STBB1 available on requ | est 19 |  |  |  |  |

| 12 | Revi  | sion his          | story                                                | 20     |  |  |  |  |

|    |       |                   |                                                      |        |  |  |  |  |

STBB1XX Block diagram

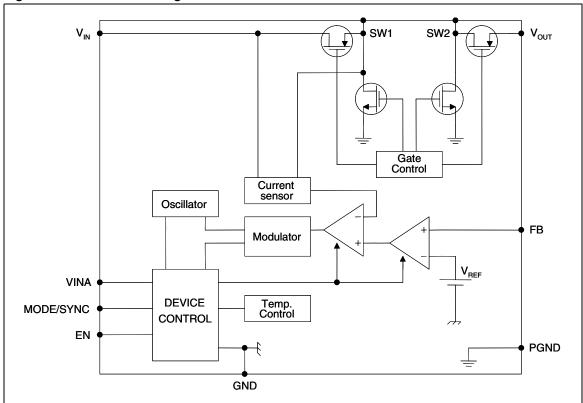

## 1 Block diagram

Figure 1. STBB1 block diagram

## 2 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol           | Parameter                            | Value         | Unit |

|------------------|--------------------------------------|---------------|------|

| VINA, VIN        | Input voltage                        | - 0.3 to 7    | V    |

| VOUT             | Output voltage                       | - 0.3 to 7    | V    |

| SW1, SW2         | DC voltage                           | - 0.3 to 7    | V    |

| FB               | DC voltage                           | - 0.3 to 1.5  | V    |

| MOD/SYNC, EN     | DC voltage                           | - 0.3 to 7    | V    |

| T <sub>J</sub>   | Maximum junction temperature         | 150           | °C   |

| T <sub>STG</sub> | Storage temperature range            | - 65 to + 150 | °C   |

| T <sub>JOP</sub> | Operating junction temperature range | - 40 to + 85  | °C   |

| ESD              | Human body model                     | 2             | kV   |

Note: Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

Table 3. Thermal data

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJC</sub> | Thermal resistance junction-case    | 2.96  | °C/W |

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 30.9  | °C/W |

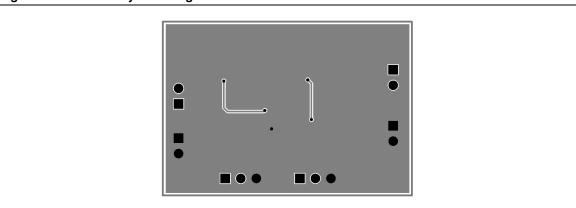

STBB1XX Pin configuration

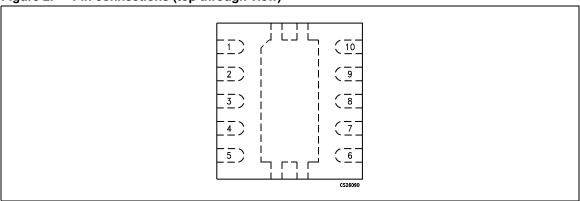

## 3 Pin configuration

Figure 2. Pin connections (top through view)

Table 4. Pin description

| Pin n° | Symbol         | Name and function                                                                                                                                                                                                                                                                                                                  |

|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VOUT           | Output voltage                                                                                                                                                                                                                                                                                                                     |

| 2      | SW2            | Switch pin - Internal switches are connected to this pin. Connect inductor between SW1 to SW2                                                                                                                                                                                                                                      |

| 3      | PGND           | Power ground                                                                                                                                                                                                                                                                                                                       |

| 4      | SW1            | Switch pin - Internal switches are connected to this pin. Connect inductor between SW1 and SW2                                                                                                                                                                                                                                     |

| 5      | VIN            | Power input voltage. Connect a ceramic bypass capacitor (10 μF minimum) between this pin and PGND                                                                                                                                                                                                                                  |

| 6      | EN             | Enable pin. Connect this pin to GND or a voltage lower than 0.4 V to shut down the IC. A voltage higher than 1.2 V is required to enable the IC.                                                                                                                                                                                   |

| 7      | MODE<br>(SYNC) | Operation mode selection.  If MODE pin is low, the STBB1 automatically switches between pulse skipping and fixed frequency PWM according to the load level.  If MODE pin is pulled high, the STBB1 works always in PWM mode.  When a square waveform is applied, this pin provides the clock signal for oscillator synchronization |

| 8      | VINA           | Supply voltage for control stage                                                                                                                                                                                                                                                                                                   |

| 9      | GND            | Signal ground                                                                                                                                                                                                                                                                                                                      |

| 10     | FB             | Feedback voltage                                                                                                                                                                                                                                                                                                                   |

|        | Exposed pad    | Power ground                                                                                                                                                                                                                                                                                                                       |

Typical application STBB1XX

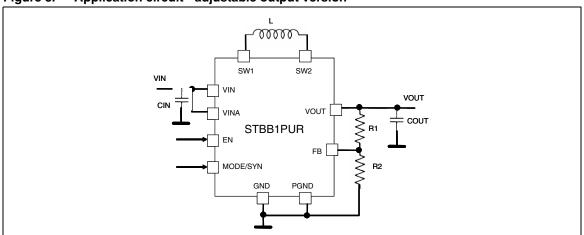

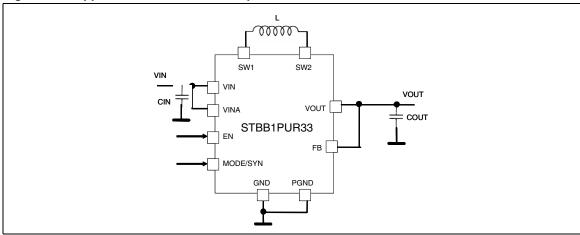

## 4 Typical application

Figure 3. Application circuit - adjustable output version

Figure 4. Application circuit - fixed output version

Table 5. List of external components (1)

| Component | Manufacturer | Part number                     | Value  | Size         |

|-----------|--------------|---------------------------------|--------|--------------|

| CIN       | Murata       | GRM188R60J106ME47D              | 10 μF  | 0603         |

| COUT      | Murata       | GRM188R60J106ME47D              | 10 μF  | 0603         |

| L         | TDK          | VLCF4020T-2R2N1R7               | 2.2 µH | 4 x 4 x 2 mm |

| R1        |              | 560 kΩ (V <sub>O</sub> = 3.3 V) | (2)    | 0402         |

| R2        |              | 100 kΩ                          | , ,    | 0402         |

Above listed components refer to typical application. Operation of the STBB1 is not limited to the choice of these external components.

$R1 = R2 \times (VOUT/VFB - 1)$

Suggested value for R2 is 100 k $\Omega$ . In order to reduce the quiescent current a maximum value of 500 k $\Omega$  is possible.

<sup>2.</sup> R1 and R2 are calculated according to the following formula:

## 5 Electrical characteristics

$V_{IN}$  =  $V_{INA}$  =  $V_{EN}$  = 3.6 V,  $C_{IN}$  = 10  $\mu\text{F},$   $C_{OUT}$  = 10  $\mu\text{F},$  L = 2.2  $\mu\text{H},$   $T_{J}$  = - 40 to 85°C (unless otherwise specified; typical values are referred to  $T_{A}$  = 25 °C).

Table 6. Electrical characteristics

| Symbol                 | Parameter                           | Test conditions                                                              | Min. | Тур. | Max. | Unit |  |

|------------------------|-------------------------------------|------------------------------------------------------------------------------|------|------|------|------|--|

| V <sub>IN</sub>        | Input voltage range                 |                                                                              | 2.0  |      | 5.5  | V    |  |

| V                      | Lindar valtaga laakaut thraahaid    | VINA rising                                                                  |      | 1.70 | 1.80 | V    |  |

| $V_{UVLO}$             | Under voltage lockout threshold     | VINA falling                                                                 | 1.50 | 1.60 |      | V    |  |

| V                      | Foodbook voltage                    |                                                                              | 485  | 500  | 515  | mV   |  |

| $V_{FB}$               | Feedback voltage                    | T <sub>J</sub> = 25°C                                                        | 490  | 500  | 510  | mV   |  |

| V <sub>OUT</sub>       | Output voltage range                |                                                                              | 1.2  |      | 5.5  | V    |  |

| Z <sub>FB</sub>        | FB input impedance                  |                                                                              |      | 10   |      | МΩ   |  |

| 1                      | No switching quiescent current      | FB = 0.7 V, V <sub>MODE</sub> = 0 V                                          |      | 160  | 250  | μA   |  |

| Ι <sub>Q</sub>         | (VIN+VINA) (see Figure 3, 4)        | FB = 0.7 V, V <sub>MODE</sub> = V <sub>IN</sub>                              |      | 600  | 750  | μΑ   |  |

| L                      | Operating quiescent current         | I <sub>OUT</sub> = 0 A, V <sub>OUT</sub> = 3.3 V,<br>V <sub>MODE</sub> = 0 V |      | 200  |      | μΑ   |  |

| lQ                     | (VIN+VINA)                          | $I_{OUT} = 0 A$ , $V_{OUT} = 3.3 V$ ,<br>$V_{MODE} = V_{IN}$                 |      | 3.4  | 5.0  | mA   |  |

| I <sub>QSHDN</sub>     | Shutdown quiescent current          | V <sub>EN</sub> = 0 V, V <sub>IN</sub> = 3.6 V                               |      | 0.1  | 1    | μΑ   |  |

|                        | Oscillator frequency                |                                                                              | 1300 | 1500 | 1750 |      |  |

| freq                   | Frequency range for synchronization |                                                                              | 1300 |      | 2000 | kHz  |  |

| V                      | Enable input logic low              | V <sub>IN</sub> = 2.2 V to 5.5 V                                             |      |      | 0.4  | V    |  |

| $V_{EN}$               | Enable input logic high             | V <sub>IN</sub> = 2.2 V to 5.5 V                                             | 1.2  |      |      | V    |  |

| I <sub>EN</sub>        | Enable pin current                  | V <sub>EN</sub> = 5.5 V                                                      |      | 0.01 | 1    | μΑ   |  |

| V                      | MODE/SYNC input logic low           | V <sub>IN</sub> = 2.2 V to 5.5 V                                             |      |      | 0.4  | V    |  |

| V <sub>MODE/SYNC</sub> | MODE/SYNC input logic high          | V <sub>IN</sub> = 2.2 V to 5.5 V                                             | 1.2  |      |      | V    |  |

| I <sub>MODE/SYNC</sub> | MODE/SYNC pin current               | V <sub>MODE/SYNC</sub> = 5.5 V                                               |      | 0.01 | 1    | μΑ   |  |

| %V <sub>OUT</sub>      | Line regulation                     | 2.2 V < V <sub>IN</sub> < 5.5 V; I <sub>OUT</sub> = 1 mA                     |      | 0.5  |      | %    |  |

| %V <sub>OUT</sub>      | Load regulation                     | 10 mA < I <sub>OUT</sub> < 1000 mA                                           |      | 1    |      | %    |  |

| I <sub>SWL</sub>       | Switch current limitation           | V <sub>IN</sub> = 3.3 V                                                      | 1.6  | 2.3  | 2.6  | Α    |  |

| I <sub>LKN</sub>       | NMOS leakage current                | V <sub>IN</sub> = 5.5 V                                                      |      | 0.01 | 1    | μΑ   |  |

| I <sub>LKP</sub>       | PMOS leakage current                |                                                                              |      | 0.01 | 1    | μΑ   |  |

| R <sub>DSon</sub> -N   | NMOS switch on resistance           |                                                                              |      | 0.13 | 0.35 | Ω    |  |

| R <sub>DSon</sub> -P   | PMOS switch on resistance           |                                                                              |      | 0.13 | 0.35 | Ω    |  |

Electrical characteristics STBB1XX

Table 6. Electrical characteristics (continued)

| Symbol            | Parameter                                                     | Test conditions                                                | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------------------------|----------------------------------------------------------------|------|------|------|------|

|                   |                                                               | $I_{OUT} = 10 \text{ mA}; V_{MODE} = 0$                        |      | 89   |      |      |

| ν                 | Efficiency, V <sub>IN</sub> = 3.6 V, V <sub>OUT</sub> = 3.3 V | I <sub>OUT</sub> = 10 mA; V <sub>MODE</sub> = V <sub>IN</sub>  |      | 67   |      | %    |

|                   |                                                               | I <sub>OUT</sub> = 100 mA; V <sub>MODE</sub> = V <sub>IN</sub> |      | 94   |      |      |

| T <sub>SHDN</sub> | Thermal shutdown                                              |                                                                |      | 140  |      | °C   |

| T <sub>HYS</sub>  | Thermal shutdown hysteresis                                   |                                                                |      | 20   |      | °C   |

STBB1XX Detailed description

## 6 Detailed description

#### 6.1 General description

The STBB1 is a high efficiency dual mode buck-boost switch mode converter. Thanks to the 4 internal switches, 2 P-channel and 2 N-channel, and its unique control mechanisms it is able to deliver e well-regulated output voltage using a variable input voltage which can be higher than, equal to or lower than the desired output voltage. This solves most of the power supply problems that circuit designers face when dealing with battery powered equipment.

The controller uses an average current mode technique in order to obtain good stability in all possible conditions of input voltage, output voltage and output current. In addition, the peak inductor current is monitored to avoid saturation of the coil.

The STBB1 can work in two different modes: PWM mode or power save mode. In the first case the device operates with a fixed oscillator frequency in all line/load conditions. This is the suitable condition to obtain the maximum dynamic performances. In the second case the device operates in burst mode allowing a drastic reduction of power consumption.

Top-class line and load transients are achieved thanks to feed-forward technique and due to the innovative control method specifically designed to optimize the performances in the buck-boost region where input voltage is very close to the output voltage.

The STBB1 is self protected from short circuit and over-temperature.

Under-voltage lockout and soft-start guarantee proper operation during startup.

Input voltage and ground connections are split into power and signal pins. This allows reduction of internal disturbances when the 4 internal switches are working. The switch bridge is connected between the VIN and PGND pins while all logic blocks are connected between VINA and GND.

#### 6.2 Dual mode operation

The STBB1 works in PWM or in power save (PS) mode according to the different operating conditions.

If the MODE pin is pulled high the device works only in PWM mode even at light or no load. In this condition STBB1 provides the best dynamic performance.

If the MODE pin is logic low, the STBB1 operation changes according to the average input current handled by the device.

At low average current the STBB1 enters in PS mode allowing very low power consumption and thus obtaining very good efficiency event at light load. When the average current increases, the device automatically switches to PWM mode in order to deliver the power needed by the load.

In PS mode the STBB1 implements a burst mode operation. If the output voltage increases above its nominal value the device stops switching. As soon the V<sub>OUT</sub> falls below the nominal value the device starts switching again with a programmed average current higher than the one needed by the load. *Figure 8* in *Section 7* shows PS mode operation areas vs. output current in typical application conditions.

Detailed description STBB1XX

#### 6.3 External synchronization

The STBB1 implements external synchronization pin. If and external clock signal is applied to the MODE (SYN) pin with a frequency between 1.35 MHz and 2.0 MHz and with proper low/high levels, the device automatically goes in PWM mode and the external clock is used as switching oscillator.

#### 6.4 Enable pin

The device operates when EN pin is set high. If EN pin is set low the device stops switching, all the internal blocks are turned off. In this condition the current drawn from VIN/VINA is below 1  $\mu$ A in the whole temperature range. In addition the internal switches are in off state so the load is electrically disconnected from the input, this avoids unwanted current leakage from the input to the load.

#### 6.5 Protection features

The STBB1 implements different types of protection features.

#### 6.5.1 Soft-start and short-circuit

After the EN pin is pulled high, or after a suitable voltage is applied to VIN, VINA and EN the device initiates the startup phase. The average current limit is set to 400 mA at the beginning and is gradually increased while tracking the output voltage increase. As soon the output voltage reaches 1.0 V the average current limit is set to its nominal value.

This method allows for a current limit proportional to the output voltage. If there is a short in the  $V_{OLT}$  pin, the output current will not exceed 400 mA.

This process is not handled by a timer so the device is also able to start up even with large capacitive loads.

#### 6.5.2 Under-voltage lockout

The under voltage lockout function prevents improper operation of STBB1 when the input voltage is not high enough. When the input voltage is below the VUVLO threshold the device is in shutdown mode. The hysteresis of 100 mV prevents unstable operation when the input voltage is close to the UVLO threshold.

#### 6.5.3 Over-temperature protection

An internal temperature sensor continuously monitors the IC junction temperature. If the IC temperature exceeds 140 °C typically the device stops operating. As soon as the temperature falls below 120 °C typically normal operation is restored.

11/21

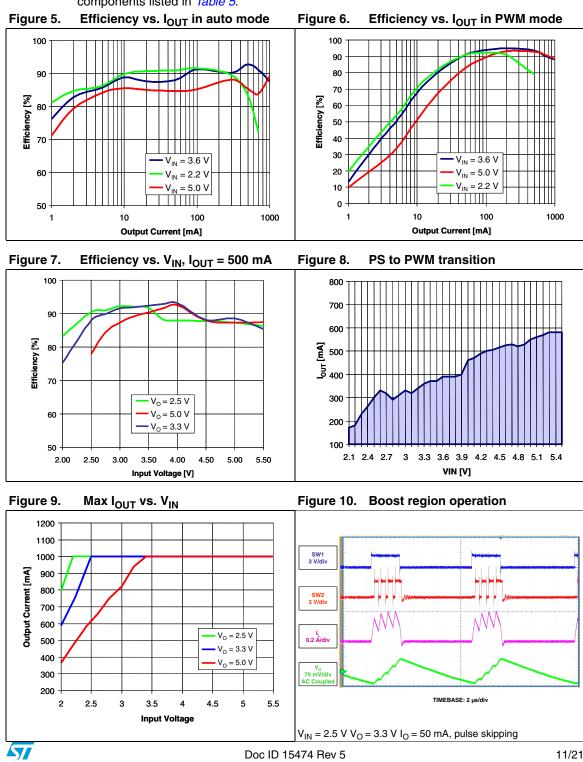

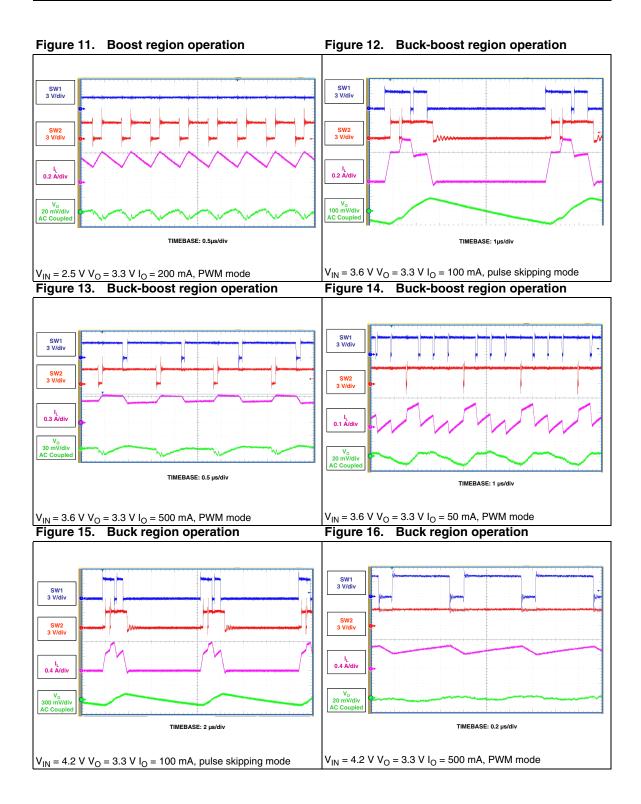

#### 7 Typical performance characteristics

$L = 2.2 \mu H$ ,  $V_O = 3.3 V$ , all measurements done with circuit shown in *Figure 3* and external components listed in Table 5.

## 8 Application information

#### 8.1 Programming the output voltage

The STBB1 is available in two versions: fixed output voltage (STBB1PURXX) and adjustable output voltage (STBB1PUR).

In the first case the device integrates the resistor divider needed to set the correct output voltage. This allows the saving of 2 external components. The FB pin must be connected directly to  $V_{OUT}$ .

For the adjustable version, the resistor divider must be connected between  $V_{OUT}$  and GND and the middle point of the divider must be connected to FB as shown in *Figure 3*.

#### **Equation 1**

$$R1 = R2 \times \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

A suggested value for R2 is 100 k $\Omega$ . To reduce the power consumption a maximum value of 500 k $\Omega$  can be used.

#### 8.2 Inductor selection

The inductor is the key passive component for switching converters. With a buck-boost device, the inductor selection must take into consideration the boundary conditions in which the converter works, as buck at the maximum input voltage and as a boost at the minimum input voltage.

Two critical inductance values are then obtained according to the following formulas:

#### **Equation 2**

$$L_{MIN-BUCK} = \frac{VOUT \times (VIN_{MAX} - VOUT)}{VIN_{MAX} \times fs \times \Delta I_I}$$

#### **Equation 3**

$$L_{MIN-BOOST} = \frac{VIN_{MIN} \times (VOUT - VIN_{MIN})}{VOUT \times fs \times \Delta I_{I}}$$

where:

fs: minimum switching frequency

$\Delta I_L$  = the peak-to-peak inductor ripple current. As a rule of thumb, the peak-to-peak ripple can be set at 10 % - 20 % of the output current.

57

Doc ID 15474 Rev 5

13/21

The minimum inductor value for the application is the higher between *Equation 2* and *Equation 3*. In addition to the inductance value the maximum current the inductor can handle must be calculated in order to avoid saturation.

#### **Equation 4**

$$I_{PEAK-BUCK} = \left(I_{OUT} \ / \ \eta\right) + \frac{VOUT \times \left(VIN_{MAX} - VOUT\right)}{2 \times VIN_{MAX} \times fs \times L}$$

#### **Equation 5**

$$I_{PEAK-BOOST} = \frac{VOUT \times I_{OUT}}{\eta \times VIN_{MIN}} + \frac{VIN_{MIN} \times (VOUT - VIN_{MIN})}{2 \times VOUT \times fs \times L}$$

Where  $\eta$  is the estimated efficiency of STBB1. The maximum of the two values above must be considered when selecting the inductor.

#### 8.3 Input and output capacitor selection

It is recommended to use ceramic capacitors with low ESR as input and output capacitors in order to filter any disturbance present in the input line and to obtain stable operation. Minimum values of 10  $\mu$ F for both capacitors are needed to achieve good behavior of the device.

The input capacitor must be placed as close as possible to the device.

15/21

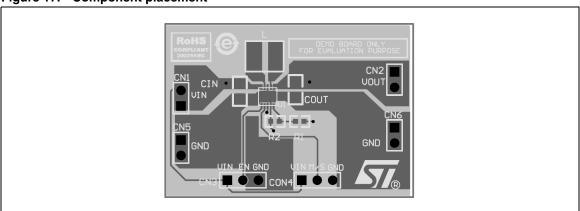

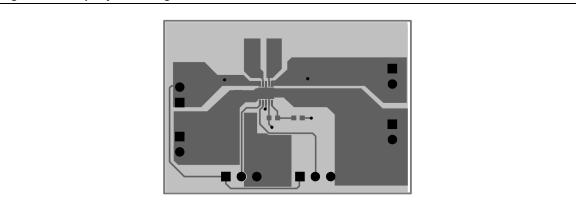

## 9 Recommended PCB layout

Figure 17. Component placement

Figure 18. Top layer routing

Figure 19. Bottom layer routing

Doc ID 15474 Rev 5

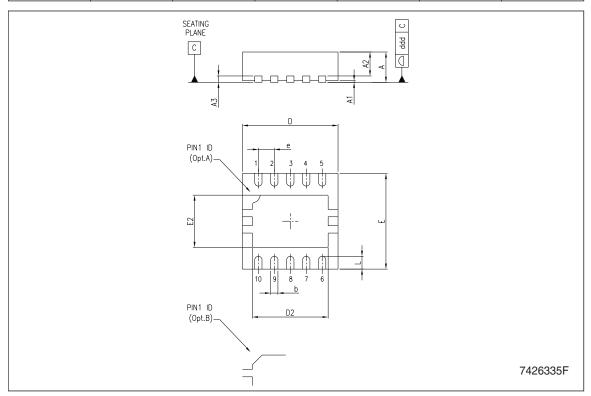

## 10 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

**577**

| DFN10 (3x3 mm) mechanical da |

|------------------------------|

|------------------------------|

| Dim  |      | mm.  |      |       | mils. |       |

|------|------|------|------|-------|-------|-------|

| Dim. | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| Α    | 0.80 | 0.90 | 1.00 | 31.5  | 35.4  | 39.4  |

| A1   |      | 0.02 | 0.05 |       | 0.8   | 2.0   |

| A2   | 0.55 | 0.65 | 0.80 | 21.7  | 25.6  | 31.5  |

| A3   |      | 0.20 |      |       | 7.9   |       |

| b    | 0.18 | 0.25 | 0.30 | 7.1   | 9.8   | 11.8  |

| D    | 2.85 | 3.00 | 3.15 | 112.2 | 118.1 | 124.0 |

| D2   | 2.20 |      |      | 86.6  |       |       |

| E    | 2.85 | 3.00 | 3.15 | 112.2 | 118.1 | 124.0 |

| E2   | 1.40 |      | 1.75 | 55.1  |       | 68.9  |

| е    |      | 0.50 |      |       | 19.7  |       |

| L    | 0.30 | 0.40 | 0.50 | 11.8  | 15.7  | 19.7  |

| ddd  |      |      | 0.08 |       |       | 3.1   |

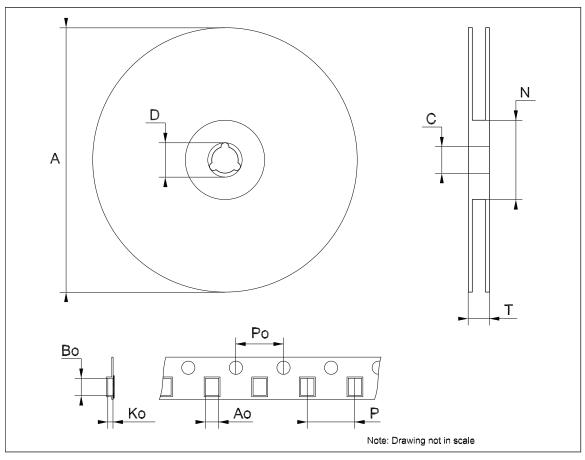

Doc ID 15474 Rev 5 17/21

| Dim.   | mm.  |      |      | inch. |       |       |

|--------|------|------|------|-------|-------|-------|

| Dilli. | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| А      |      |      | 180  |       |       | 7.087 |

| С      | 12.8 |      | 13.2 | 0.504 |       | 0.519 |

| D      | 20.2 |      |      | 0.795 |       |       |

| N      | 60   |      |      | 2.362 |       |       |

| Т      |      |      | 14.4 |       |       | 0.567 |

| Ao     |      | 3.3  |      |       | 0.130 |       |

| Во     |      | 3.3  |      |       | 0.130 |       |

| Ko     |      | 1.1  |      |       | 0.043 |       |

| Ро     |      | 4    |      |       | 0.157 |       |

| Р      |      | 8    |      |       | 0.315 |       |

# 11 Different output voltage versions of the STBB1 available on request

Table 7. Options available on request

| Order codes | Marking | Output voltages |

|-------------|---------|-----------------|

| STBB1PUR18  | BB1 18  | 1.8 V           |

| STBB1PUR25  | BB1 25  | 2.5 V           |

| STBB1PUR28  | BB1 28  | 2.8 V           |

| STBB1PUR33  | BB1 33  | 3.3 V           |

Revision history STBB1XX

## 12 Revision history

Table 8. Document revision history

| Date        | Revision | Changes                                                        |  |

|-------------|----------|----------------------------------------------------------------|--|

| 19-Mar-2009 | 1        | First release.                                                 |  |

| 25-Mar-2009 | 2        | Modified: Figure 5 and Figure 7 on page 11.                    |  |

| 01-Apr-2009 | 3        | Modified: Figure 3 and Figure 4 on page 6.                     |  |

| 15-Jul-2009 | 4        | Modified: Equation 4 and Equation 5 on page 14.                |  |

| 07-Sep-2010 | 5        | Modified: Table 7 on page 19, Figure 3 and Figure 4 on page 6. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 15474 Rev 5

21/21