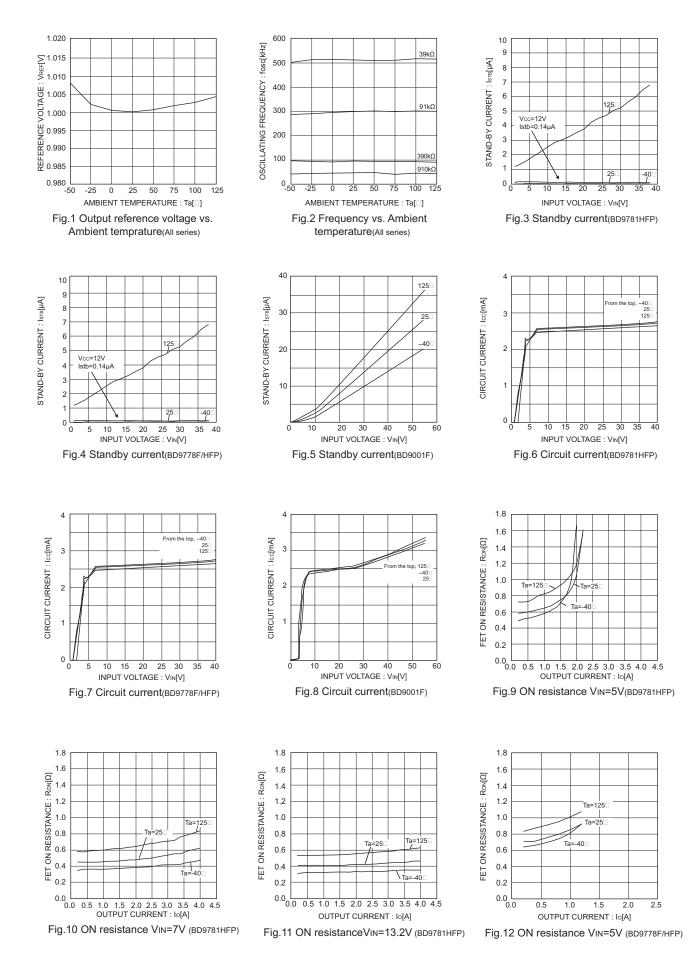

Single-chip built-in FET type Switching Regulator Series

# Flexible Step-down Switching Regulator BD9778F/HFP, BD9001F, BD9781HFP

# Overview

The flexible step-down switching regulator controller is a switching regulator controller designed with a high-withstand-voltage built-in POWER MOS FET, providing a free setting function of operating frequency with external resistor. This switching regulator controller features a wide input voltage range (7 V to 35 V or 7 V to 48 V) and operating temperature range (-40°C to +125°C or -40°C to +95°C). Furthermore, an external synchronization input pin (BD9781HFP) enables synchronous operation with external clock.

# Features

- 1) Minimal external components

- 2) Wide input voltage range: 7 V to 35 V (BD9778F/HFP and BD9781HFP), 7 V to 48 V (BD9001F)

- 3) Built-in P-ch POWER MOS FET

- 4) Output voltage setting enabled with external resistor: 1 to VIN

- 5) Reference voltage accuracy: ±2%

- 6) Wide operating temperature range: -40°C to +125°C (BD9778F/HFP and BD9781HFP),

- -40°C to +95°C (BD9001F)

- 8) Low dropout: 100% ON Duty cycle

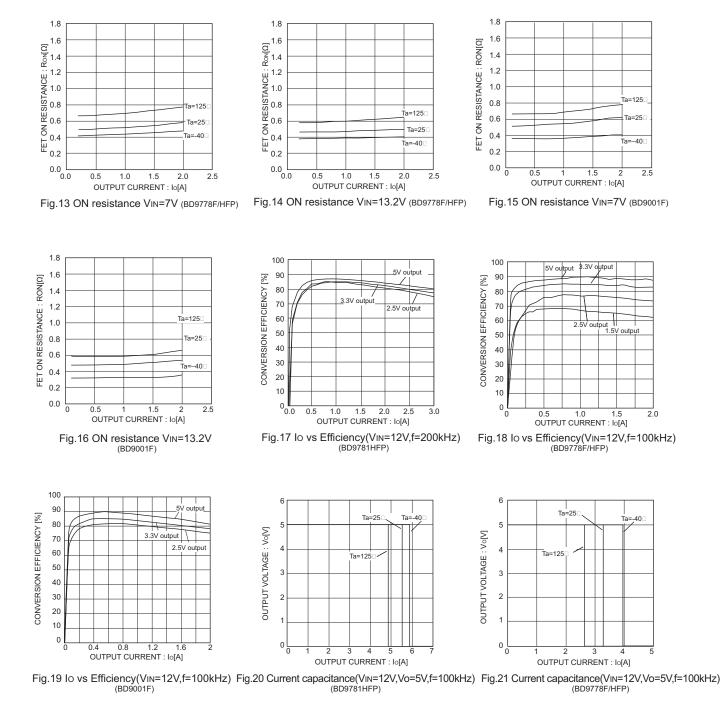

- 9) Standby mode supply current: 0 µA (Typ.) (BD9778F/HFP and BD9781HFP), 4 µA (Typ.) (BD9001F)

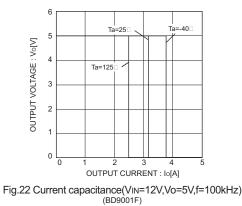

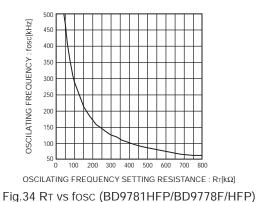

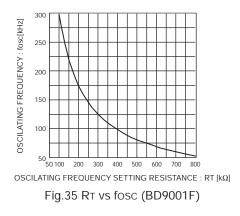

- 10) Oscillation frequency variable with external resistor: 50 to 300 kHz (BD9001F), 50 to 500 kHz (BD9778F/HFP and BD9781HFP)

- 11) External synchronization enabled (only on the BD9781HFP)

- 12) Soft start function : soft start time fixed to 5 ms (Typ.))

- 13) Built-in overcurrent protection circuit

- 14) Built-in thermal shutdown protection circuit

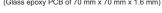

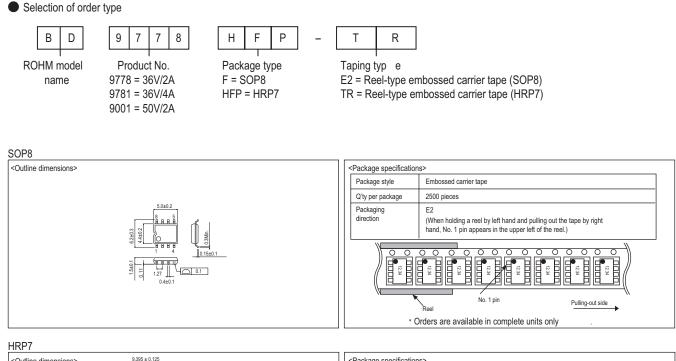

- 15) High power HRP7 package mounted (BD9778HFP and BD9781HFP) Compact SOP8 package mounted (BD9778F and BD9001F)

# Applications

All fields of industrial equipment, such as Flat TV , printer, DVD, car audio, car navigation, and communication such as ETC, AV, and OA.

# Product lineup

| Item                        | BD9778F/HFP    | BD9001F       | BD9781HFP      |

|-----------------------------|----------------|---------------|----------------|

| Output current              | 2A             | 2A            | 4A             |

| Input range                 | 7V ~ 35V       | 7V ~ 48V      | 7V ~ 35V       |

| Oscillation frequency range | 50 ~ 500kHz    | 50 ~ 300kHz   | 50 ~ 500kHz    |

| External synchronization    | Not provided   | Not provided  | Provided       |

| Standby function            | Provided       | Provided      | Provided       |

| Operating temperature       | −40°C ~ +125°C | −40°C ~ +95°C | –40°C ~ +125°C |

| Package                     | SOP8 / HRP7    | SOP8          | HRP7           |

# Absolute Maximum Ratings(Ta = 25°C)

| Param                     | eter                  | Symbol        | Limits            | Unit |

|---------------------------|-----------------------|---------------|-------------------|------|

| Power supply              | BD9778F/HFP,BD9781HFP | Vin           | 36                | V    |

| voltage                   | BD9001F               | VIIN          | 50                | v    |

| Output switch pin voltage | ge                    | Vsw           | VIN               | V    |

| Output owitch ourrept     | BD9778F/HFP, BD9001F  | Isw           | 2 *1              |      |

| Output switch current     | BD9781HFP             | ISVV          | 4 *1              | A    |

| EN/SYNC, EN pin voltage   |                       | VEN/SYNC, VEN | VIN               | V    |

| RT, FB, INV pin voltage   |                       | Vrt,Vfb,Vinv  | 7                 | v    |

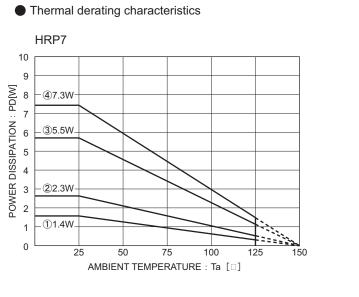

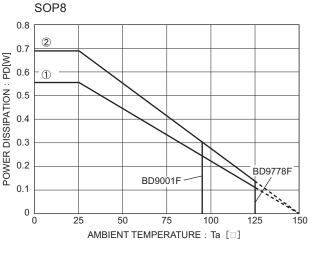

| Power dissipation         | HRP7                  | Pd            | 5.5 <sup>*2</sup> | W    |

|                           | SOP8                  |               | 0.69 *3           | vv   |

| Operating temperature     | BD9778F/HFP,BD9781HFP | т             | -40 ~ +125        | °O   |

| range                     | BD9001F               | Topr          | -40 ~ +95         | °C   |

| Storage temperature range |                       | Tstg          | -55 ~ +150        | °C   |

| Maximum junction temp     | perature              | Tjmax         | 150               | °C   |

\*1 Should not exceed P4-value.

\*2 Reduce by 44mW/∞C over 25∞C, when mounted on 2-layer PCB of 70 ¥ 70 ¥ 1.6 mm3.

(PCB incorporates thermal via. Copper foil area on the front side of PCB: 10.5 ¥ 10.5 mm2. Copper foil area on the reverse side of PCB: 70 ¥ 70 mm2)

\*3 Reduce by 5.52 mW/∞C over 25∞C, when mounted on 2-layer PCB of 70 ¥ 70 ¥ 1.6 mm3.

# Recommended operating range

| Parameter                            | BD9778F/HFP | BD9001F   | BD9781HFP | Unit |

|--------------------------------------|-------------|-----------|-----------|------|

| Operating power supply voltage       | 7 ~ 35      | 7 ~ 48    | 7 ~ 35    | V    |

| Output switch current                | ~ 2         | ~ 2       | ~ 4       | А    |

| Output voltage (ON Duty)             | 6 ~ 100     | 6 ~ 100   | 6 ~ 100   | %    |

| Oscillation frequency                | 50 ~ 500    | 50 ~ 300  | 50 ~ 500  | kHz  |

| Oscillation frequency set resistance | 40 ~ 800    | 100 ~ 800 | 39 ~ 800  | kΩ   |

#### Possible operating range

| Parameter                      | BD9778F/HFP | BD9001F | BD9781HFP | Unit |

|--------------------------------|-------------|---------|-----------|------|

| Operating power supply voltage | 5 ~ 35      | 7 ~ 48  | 5 ~ 35    | V    |

#### Electrical characteristics

◎ BD9778F/HFP (Unless otherwise specified, Ta = -40°C to +125°C, VIN =13.2 V, VEN = 5 V)

| Parameter                                          | Symbol        |      | Limits |      | Unit | Condition          |  |

|----------------------------------------------------|---------------|------|--------|------|------|--------------------|--|

| Parameter                                          | Symbol        | Min. | Тур.   | Max. | Unit | Condition          |  |

| Standby circuit current                            | ISTB          | _    | 0      | 10   | μA   | VEN=0V,Ta=25°C     |  |

| Circuit current                                    | lq            | —    | 3      | 4.2  | mA   | Io=0A              |  |

| [SW block]                                         |               |      |        |      |      |                    |  |

| POWER MOS FET ON resistance                        | Ron           | -    | 0.53   | 0.9  | Ω    | Isw=50mA           |  |

| Operating output current of overcurrent protection | IOLIMIT       | 2    | 4      | -    | A    | * Design assurance |  |

| Output leak current                                | IOLEAK        | _    | 0      | 30   | μA   | VIN=35V,VEN=0V     |  |

| [Error Amp block]                                  |               |      |        |      |      |                    |  |

| Reference voltage 1                                | VREF1         | 0.98 | 1.00   | 1.02 | V    | VFB=VINV,Ta=25°C   |  |

| Reference voltage 2                                | VREF2         | 0.96 | 1.00   | 1.04 | V    | VFB=VINV           |  |

| Reference voltage input regulation                 | $\Delta VREF$ | _    | 0.5    | _    | %    | VIN=5 ~ 35V        |  |

| Input bias current                                 | Ів            | -1   | -      | -    | μA   | VINV=1.1V          |  |

| Maximum FB voltage                                 | Vfbh          | 2.4  | 2.5    | -    | V    | VINV=0.5V          |  |

| Minimum FB voltage                                 | VFBL          | _    | 0.05   | 0.10 | V    | VINV=1.5V          |  |

| FB sink current                                    | IFBSINK       | -5.0 | -3.0   | -0.5 | mA   | VFB=1.5V,VINV=1.5V |  |

| FB source current                                  | IFBSOURCE     | 70   | 120    | 170  | μA   | VFB=1.5V,VINV=0.5V |  |

| Soft start time                                    | Tss           | -    | 5      | -    | mS   | * Design assurance |  |

| [Oscillator block]                                 |               |      |        |      |      |                    |  |

| Oscillation frequency                              | Fosc          | 82   | 102    | 122  | kHz  | R⊤=390kΩ           |  |

| Frequency input regulation                         | ∆Fosc         | -    | 1      | -    | %    | VIN=5 ~ 35V        |  |

| [Enable block]                                     |               |      |        |      |      |                    |  |

| Threshold voltage                                  | VEN           | 0.8  | 1.7    | 2.6  | V    |                    |  |

| Sink current                                       | IEN           | _    | 13     | 50   | μA   | Ven=5V             |  |

\* Not designed to be radiation-resistant.

$\odot$  BD9001F (Unless otherwise specified, Ta=-40°C ~ +95°C,VIN=13.2V, VEN=5V)

|                                                    |                   |      | Limits |      |      | 0 1111             |  |

|----------------------------------------------------|-------------------|------|--------|------|------|--------------------|--|

| Parameter                                          | Symbol            | Min. | Тур.   | Max. | Unit | Condition          |  |

| Standby circuit current                            | ISTB              | -    | 4      | 10   | μA   | VEN=0V,Ta=25°C     |  |

| Circuit current                                    | lq                | -    | 3      | 4.2  | mA   | Io=0A              |  |

| [SW block]                                         |                   |      |        |      |      |                    |  |

| POWER MOS FET ON resistance                        | Ron               | _    | 0.6    | 1.2  | Ω    | Isw=50mA           |  |

| Operating output current of overcurrent protection | IOLIMIT           | 2.5  | 4      | -    | Α    | * Design assurance |  |

| [Error Amp block]                                  |                   |      |        |      |      |                    |  |

| Reference voltage 1                                | VREF1             | 0.98 | 1.00   | 1.02 | V    | VFB=VINV,Ta=25°C   |  |

| Reference voltage 2                                | VREF2             | 0.96 | 1.00   | 1.04 | V    | VFB=VINV           |  |

| Reference voltage input regulation                 | $\Delta VREF$     | -    | 0.5    | -    | %    | VIN=7 ~ 48V        |  |

| Input bias current                                 | lв                | -1   | -      | 1    | μA   | VINV=1.1V          |  |

| Maximum FB voltage                                 | Vfbh              | 2.4  | 2.5    | -    | V    | VINV=0.5V          |  |

| Minimum FB voltage                                 | Vfbl              | _    | 0.05   | 0.10 | V    | VINV=1.5V          |  |

| FB sink current                                    | IFBSINK           | -5.0 | -3.0   | -0.5 | mA   | VFB=1.5V,VINV=1.5V |  |

| FB source current                                  | <b>I</b> FBSOURCE | 70   | 120    | 170  | μA   | VFB=1.5V,VINV=0.5V |  |

| Soft start time                                    | Tss               | -    | 5      | -    | ms   | * Design assurance |  |

| [Oscillator block]                                 |                   |      |        |      |      |                    |  |

| Oscillation frequency                              | Fosc              | 82   | 102    | 122  | kHz  | Rτ=390kΩ           |  |

| Frequency input regulation                         | ∆Fosc             | -    | 2      | -    | %    | VIN=7 ~ 48V        |  |

| [Enable block]                                     |                   |      |        |      |      |                    |  |

| Threshold voltage                                  | Ven               | 0.8  | 1.7    | 2.6  | V    |                    |  |

| Sink current                                       | IEN               | _    | 13     | 50   | μA   | VEN=5V             |  |

| * Not designed to be radiation-resistant.          |                   |      |        |      |      |                    |  |

\* Not designed to be radiation-resistant.

$\odot$  BD9781HFP (Unless otherwise specified, Ta=-40°C ~ +125°C,VIN=13.2V,VEN/SYNC=5V)

| Parameter                                          | Symbol        | Min. | Limits<br>Typ. | Max. | Unit | Condition            |

|----------------------------------------------------|---------------|------|----------------|------|------|----------------------|

| Standby circuit current                            | Іsтв          | _    | 0              | 10   | μA   | VEN/SYNC=0V,Ta=25°C  |

| Circuit current                                    | IQ            | _    | 3              | 8    | mΑ   | Io=0A                |

| [SW block]                                         |               |      |                |      |      |                      |

| POWER MOS FET ON resistance                        | Ron           | _    | 0.5            | 0.9  | Ω    | Isw=50mA             |

| Operating output current of overcurrent protection | IOLIMIT       | 4    | 8              | _    | Α    | * Design assurance   |

| Output leak current                                | IOLEAK        | _    | 0              | 30   | μA   | VIN=35V, VEN/SYNC=0V |

| [Error Amp block]                                  |               |      |                |      |      |                      |

| Reference voltage1                                 | VREF1         | 0.98 | 1.00           | 1.02 | V    | VFB=VINV,Ta=25℃      |

| Reference voltage2                                 | VREF2         | 0.97 | 1.00           | 1.03 | V    | VFB=VINV             |

| Reference voltage input regulation                 | $\Delta VREF$ | _    | 0.5            | _    | %    | VIN=5 ~ 35V          |

| Input bias current                                 | lв            | -1   | _              | _    | μA   | VINV=1.1V            |

| Maximum FB voltage                                 | Vfbh          | 2.4  | 2.5            | _    | V    | VINV=0.5V            |

| Minimum FB voltage                                 | Vfbl          | _    | 0.05           | 0.10 | V    | VINV=1.5V            |

| FB sink current                                    | IFBSINK       | -5.0 | -3.0           | -0.5 | mA   | VFB=1.5V,VINV=1.5V   |

| FB source current                                  | IFBSOURCE     | 70   | 120            | 170  | μA   | VFB=1.5V,VINV=0.5V   |

| Soft start time                                    | Tss           | _    | 5              | -    | mS   | * Design assurance   |

| [Oscillator block]                                 |               |      |                |      |      |                      |

| Oscillation frequency                              | Fosc          | 82   | 102            | 122  | kHz  | Rτ=390kΩ             |

| Frequency input regulation                         | ∆Fosc         | _    | 1              | _    | %    | VIN=5 ~ 35V          |

| [Enable/Synchronizing input block]                 |               |      |                |      |      |                      |

| Threshold voltage                                  | VEN/SYNC      | 0.8  | 1.7            | 2.6  | V    |                      |

| Sink current                                       | IEN/SYNC      | -    | 35             | 90   | μA   | VEN/SYNC=5V          |

| External synchronizing frequency                   | FSYNC         | -    | 150            | -    | kHz  | FEN/SYNC=150kHz      |

\* Not designed to be radiation-resistant.

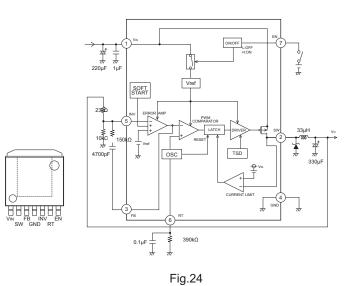

# (BD9778F)

# (BD9778HFP)

Fig.23

| No. | Pin name | Function                              |

|-----|----------|---------------------------------------|

| 1   | Vin      | Power supply input                    |

| 2   | SW       | Output                                |

| 3   | FB       | Error Amp output                      |

| 4   | INV      | Output voltage feedback               |

| 5   | EN       | Enable                                |

| 6   | RT       | Frequency setting resistor connection |

| 7   | GND      | Ground                                |

| 8   | PVIN     | Power system power supply input       |

| No. | Pin name | Function                              |

|-----|----------|---------------------------------------|

| 1   | Vin      | Power supply input                    |

| 2   | SW       | Output                                |

| 3   | FB       | Error Amp output                      |

| 4   | GND      | Ground                                |

| 5   | INV      | Output voltage feedback               |

| 6   | RT       | Frequency setting resistor connection |

| 7   | EN       | Enable                                |

| FIN | _        | Ground                                |

|     |          |                                       |

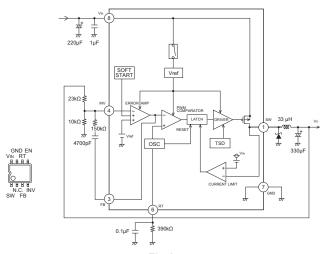

# (BD9001F)

| No. | Pin name | Function                              |  |

|-----|----------|---------------------------------------|--|

| 1   | SW       | Output                                |  |

| 2   | N.C.     | Non Connection                        |  |

| 3   | FB       | Error Amp Output                      |  |

| 4   | INV      | Output voltage feedback               |  |

| 5   | EN       | Enable                                |  |

| 6   | RT       | Frequency setting resistor connection |  |

| 7   | GND      | Ground                                |  |

| 8   | Vin      | Power supply input                    |  |

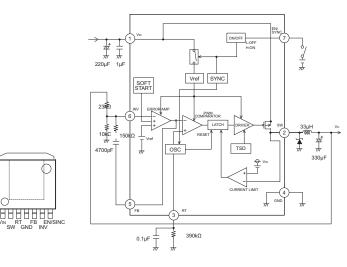

(BD9781HFP)

GND

6/16

| Fig. | 26 |

|------|----|

|------|----|

| . Pin | name  | Function                                |

|-------|-------|-----------------------------------------|

|       |       | 1 dileton                               |

|       | Vin   | Power supply input                      |

|       | SW    | Output                                  |

|       | RT    | Frequency setting resistor connection   |

| (     | GND   | Ground                                  |

|       | FB    | Error Amp output                        |

|       | INV   | Output voltage feedback                 |

| EN    | /SYNC | Enable/Synchronizing pulse input        |

| 1     | -     | Ground                                  |

|       | (     | SW<br>RT<br>GND<br>FB<br>INV<br>EN/SYNC |

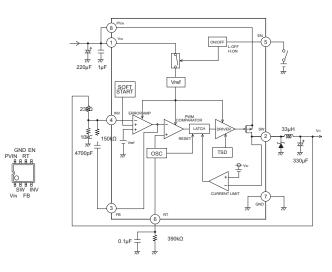

#### Description of operations

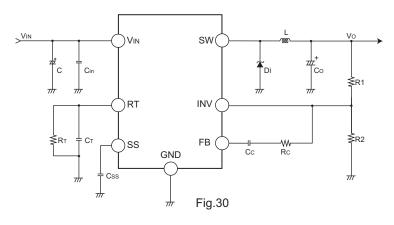

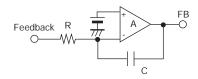

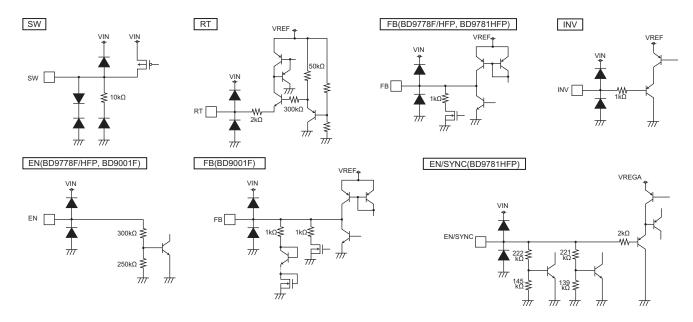

ERROR AMP

The ERROR AMP block is an error amplifier used to input the reference voltage (1 V typ.) and the INV pin voltage. The output FB pin controls the switching duty and output voltage Vo. These INV and FB pins are externally mounted to facilitate phase compensation. Inserting a capacitor and resistor between these pins enables adjustment of phase margin. (Refer to recommended examples on page 11.)

SOFT START

The SOFT START block provides a function to prevent the overshoot of the output voltage Vo through gradually increasing the normal rotation input of the error amplifier when power supply turns ON to gradually increase the switching Duty. The soft start time is set to 5 msec (Typ.).

#### ON/OFF(BD9778F/HFP,BD9781HFP)

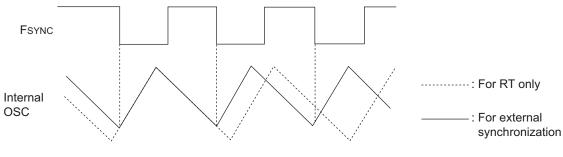

Setting the EN pin to 0.8 V or less makes it possible to shut down the circuit. Standby current is set to 0  $\mu$ A (Typ.). Furthermore, on the BD9781HFP, applying a pulse having a frequency higher than set oscillation frequency to the EN/SYNC pin allows for external synchronization (up to +50% of the set frequency).

PWM COMPARATOR

The PWM COMPARATOR block is a comparator to make comparison between the FB pin and internal triangular wave and output a switching pulse.

The switching pulse duty varies with the FB value and can be set in the range of 0 to 100%.

OSC(Oscillator)

The OSC block is a circuit to generate a triangular wave that is to be input in the PWM comparator. Connecting a resistor to the RT pin enables setting of oscillation frequency.

TSD(Thermal Shut Down)

In order to prevent thermal destruction/thermal runaway of this IC, the TSD block will turn OFF the output when the chip temperature reaches approximately 150°C or more. When the chip temperature falls to a specified level, the output will be reset. However, since the TSD is designed to protect the IC, the chip junction temperature should be provided with the thermal shutdown detection temperature of less than approximately 150°C.

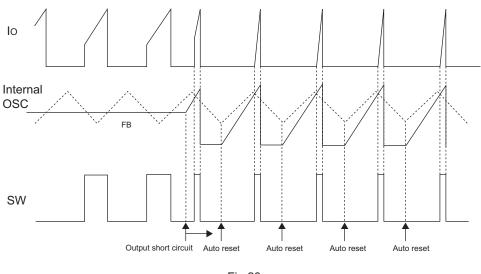

CURRENT LIMIT

While the output POWER P-ch MOS FET is ON, if the voltage between drain and source (ON resistance ¥ load current) exceeds the reference voltage internally set with the IC, this block will turn OFF the output to latch. The overcurrent protection detection values have been set as shown below:

BD9781HFP . . . 8A(Typ.) BD9001F,BD9778F/HFP . . . 4A(Typ.)

Furthermore, since this overcurrent protection is an automatically reset, after the output is turned OFF and latched, the latch will be reset with the RESET signal output by each oscillation frequency.

However, this protection circuit is only effective in preventing destruction from sudden accident. It does not support for the continuous operation of the protection circuit (e.g. if a load, which significantly exceeds the output current capacitance, is normally connected). Furthermore, since the overcurrent protection detection value has negative temperature characteristics, consider thermal design.

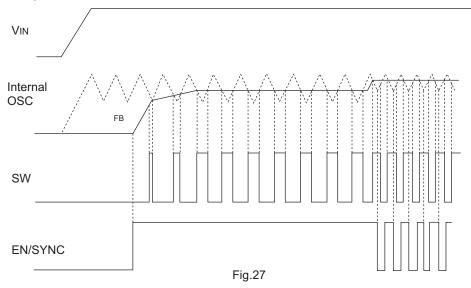

Timing chart (BD9781HFP)

- While in basic operation mode

- While in overcurrent protection mode

# External synchronizing function (BD9781HFP)

In order to activate the external synchronizing function, connect the frequency setting resistor to the RT pin and then input a synchronizing signal to the EN/SYNC pin. As the synchronizing signal, input a pulse wave higher than a frequency determined with the setting resistor (RT). On the BD9781HFP, design the frequency difference to be within 50%. Furthermore, set the pulse wave duty between 10% and 90%.

# Description of external components

| Design procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Calculation example                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Vo = Output voltage, Vin (Max.) = Maximum input voltage<br>lo (Max.) = Maximum load current, f = Oscillation frequency                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                      |

| <ol> <li>Setting or output voltage<br/>Output voltage can be obtained by the formula shown below.</li> <li>Vo=1 x (1+R1/R2)</li> </ol>                                                                                                                                                                                                                                                                                                                                                            | When Vo = 5 V and R2 = 10 k $\Omega$ ,                                                                               |

| Use the formula to select the R1 and R2.<br>Furthermore, set the R2 to 30 k $\Omega$ or less.<br>Select the current passing through the R1 and R2 to be small<br>enough for the output current.                                                                                                                                                                                                                                                                                                   | 5=1 x (1+R1/10kΩ)<br><u>R1=40kΩ</u>                                                                                  |

| <ol> <li>Selection of coil (L)</li> <li>The value of the coil can be obtained by the formula shown below:</li> </ol>                                                                                                                                                                                                                                                                                                                                                                              | When VIN = 13.2 V, Vo = 5 V, Io = 2 A, and f = 100 kHz,<br>L=(13.2–5) x 5/13.2 x 1/100k x 1/(2 x 0.3)<br>=51.8µH≒47µ |

| <ul> <li>L=(VIN-VO) x VO / (VIN x f x △IO)</li> <li>△IO: Output ripple current</li> <li>f = Operating frequency</li> <li>△IO should typically be approximately 20 to 30% of IO.</li> <li>If this coil is not set to the optimum value, normal (continuous)</li> <li>oscillation may not be achieved. Furthermore, set the value of</li> <li>the coil with an adequate margin so that the peak current passing</li> <li>through the coil will not exceed the rated current of the coil.</li> </ul> | <u>L=47µH</u>                                                                                                        |

| <ul> <li>3. Selection of output capacitor (Co)<br/>The output capacitor can be determined according to the<br/>output ripple voltage ΔVo (p-p) required.<br/>Obtain the required ESR value by the formula shown below<br/>and then select the capacitance.<br/>ΔIL=(VIN-VO) x VO/(L x f x VIN)<br/>ΔVpp=ΔIL x ESR+(ΔIL x VO)/(2 x Co x f x VIN)</li> </ul>                                                                                                                                        | VIN=13.2V, Vo=5V, L=100µH, f=100kHz<br>∆IL=(13.2-5) x 5/(100 x 10⋅6 x 100 x 10₃ x 13.2)<br>≒0.31<br>∆IL=0.31A        |

| Set the rating of the capacitor with an adequate margin to the output voltage. Also, set the maximum allowable ripple current with an adequate margin to $\Delta$ IL. Furthermore, the output rise time should be shorter than the soft start time. Select the output capacitor having a value smaller than that obtained by the formula shown below.<br>$\frac{3.5m \times (ILimit-Io(Max))}{CMax} = \frac{3.5m \times (ILimit-Io(Max))}{1000}$                                                  | When ILimit: 2 A, Io (Max) = 1 A, and Vo = 5V,<br>CMax=3.5m x (2-1)/5<br>=700μ                                       |

| Vo<br>ILimit:2A(BD9778F/HFP,BD9001F), 4A(BD9781HFP)<br>If this capacitance is not optimum, faulty startup may result.<br>(□3.5m is soft start time(min.))                                                                                                                                                                                                                                                                                                                                         | <u>C</u> Max=700μF                                                                                                   |

| Design procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Calculation example                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>4. Selection of diode</li> <li>Set diode rating with an adequate margin to the maximum load current. Also, make setting of the rated inverse voltage with an adequate margin to the maximum input voltage.</li> <li>A diode with a low forward voltage and short reverse recovery time will provide high efficiency.</li> </ul>                                                                                                                                                                                                                                           | When VIN = 36 V and Io = (max.) 2 A,<br>Select a diode of rated current of 2 A or more and rated<br>withstand voltage of 36 V or more. |

| <ul> <li>5. Selection of input capacitor         Two capacitors, ceramic capacitor CIN and bypass capacitor C, should be inserted between the VIN and GND.Be sure to insert a ceramic capacitor of 1 to 10 μF for the CThe capacitor C should have a low ESR and a significantly large ripple current. The ripple current IRMs can be obtained by the following formula:     </li> <li>IRMS=IO ×√VO × (Vin-VO)/Vin<sup>2</sup> </li> <li>Select capacitors that can accept this ripple current. If the capacitance of CIN and C is not optimum, the IC may malfunction.</li> </ul> | When VIN = 13.2 V, Vo = 5 V, and Io = 1 A,<br>IRMS=1 $\times \sqrt{5 \times (13.2-5)/(13.2)^2}$<br>=0.485<br><u>IRMS=0.485A</u>        |

| 6. Setting of oscillation frequency<br>Referring Fig. 34 and Fig. 35 on the following page, select R<br>for the oscillation frequency to be used. Furthermore,<br>in order to eliminate noises, be sure to connect ceramic<br>capacitors of 0.1 to 1.0 μF in parallel.                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |

| <ul> <li>8. Setting of phase compensation (Rc and Cc)<br/>The phase margin can be set through inserting a capacitor or<br/>a capacitor and resistor between the INV pin and the FB pin.<br/>Each set value varies with the output coil, capacitance,<br/>I/O voltage, and load. Therefore, set the phase compensation<br/>to the optimum value according to these conditions.<br/>(For details, refer to Application circuit on page 11.)<br/>If this setting is not optimum, output oscillation may result.</li> </ul>                                                            |                                                                                                                                        |

\* The set values listed above are all reference values. On the actual mounting of the IC, the characteristics may vary with the routing of wirings and the types of parts in use. In this connection, it is recommended to thoroughly verify these values on the actual system prior to use.

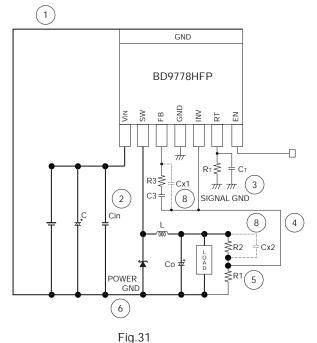

Directions for pattern layout of PCB

- ① Arrange the wirings shown by heavy lines as short as possible in a broad pattern.

- ② Locate the input ceramic capacitor Cin as close to the VIN-GND pin as possible.

- (3) Locate the RT and CT as close to the GND pin as possible.

- ④ Locate the R1 and R2 as close to the INV pin as possible, and provide the shortest wiring from the R1 and R2 to the INV pin.

- ⑤ Locate the R1 and R2 as far away from the L as possible.

- (6) Separate POWER GND(Schottky diode, I/O capacitor's GND) and SIGNAL GND(RT, CT's GND), so that SW noise don't have an effect on SIGNAL GND at all.

- ⑦ Design the POWER wire line as wide and short as possible.

- (8) Additional pattern for Cx1 and Cx2 expand compesation flexibility.

Fig.32 BD9001F reference layout pattern

※ As shown above, design the GND pattern as large area as possible within inner layer.

\* Gray zones indicate GND.

Scillation frequencys graph value is Typical value, oscillation frequency is necessary to consider ±20% as dispersion.

Phase compensation setting procedure

1. Application stability conditions

Fig.33 BD9781HFP reference layout pattern

The following section describes the stability conditions of the negative feedback system.

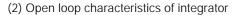

Since the DC/DC converter application is sampled according to the switching frequency, GBW (frequency at 0-dB gain) of the overall system should be set to 1/10 or less of the switching frequency. The following section summarizes the targeted characteristics of this application.

- At a 1 (0-dB) gain, the phase delay is 150° or less (i.e., the phase margin is 30° or more).

- The GBW for this occasion is 1/10 or less of the switching frequency.

Responsiveness is determined with restrictions on the GBW. To improve responsiveness, higher switching frequency should be provided.

Replace a secondary phase delay (-180<sup>-</sup>) with a secondary phase lead by inserting two phase leads, to ensure the stability through the phase compensation. Furthermore, the GBW (i.e., frequency at 0-dB gain) is determined according to phase compensation capacitance provided for the error amplifier. Consequently, in order to reduce the GBW, increase the capacitance value.

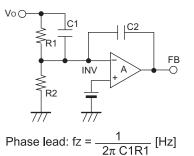

(1) Typical integrator (Low pass filter)

Since the error amplifier is provided with (1) or (2) phase compensation, the low pass filter is applied. In the case of the DC/DC converter application, the R becomes a parallel resistance of the feedback resistance.

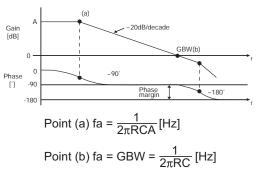

#### 2. For output capacitors having high ESR, such as electrolyte capacitor

For output capacitors that have high ESR (i.e., several  $\Omega$ ), the phase compensation setting procedure becomes comparatively simple. Since the DC/DC converter application has a LC resonant circuit attached to the output, a -180° phase-delay occurs in that area. If ESR component is present, however, a +90° phase-lead occurs to shift the phase delay to -90°. Since the phase delay should be set within 150°, it is a very effective method but tends to increase the ripple component of the output voltage.

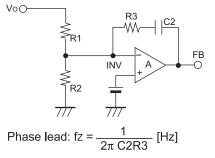

According to changes in phase characteristics, due to the ESR, only one phase lead should be inserted. For this phase lead, select either of the methods shows below:

(3) Insert feedback resistance in the C.

(4) Insert the R3 in integrator.

To cancel the LC resonance, the frequency to insert the phase lead should be set close to the LC resonant frequency. The settings above have are estimated. Consequently, the settings may be adjusted on the actual system. Furthermore, since these characteristics vary with the layout of PCB loading conditions, precise calculations should be made on the actual system.

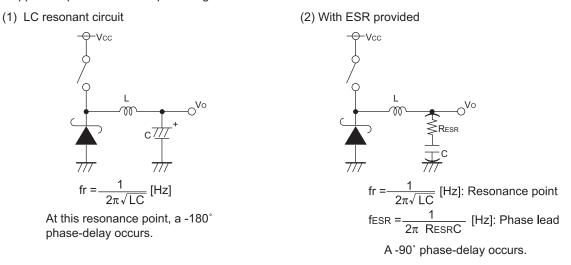

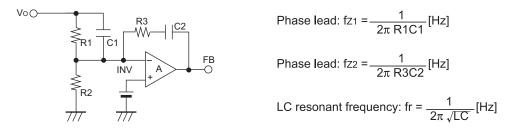

3. For output capacitors having low ESR, such as low impedance electrolyte capacitor or OS-CON

In order to use capacitors with low ESR (i.e., several tens of m $\Omega$ ), two phase-leads should be inserted so that a -180° phase-delay, due to LC resonance, will be compensated. The following section shows a typical phase compensation procedure.

(1) Phase compensation with secondary phase lead

To set phase lead frequency, insert both of the phase leads close to the LC resonant frequency. According to empirical rule, setting the phase lead frequency fz2 with R3 and C2 lower than the LC resonant frequency fr, and the phase lead frequency fz1 with the R1 and C1 higher than the LC resonant frequency fr, will provide stable application conditions.

To measure the open loop of DC/DC converter, use the gain phase analyzer or FRA to measure the frequency characteristics.

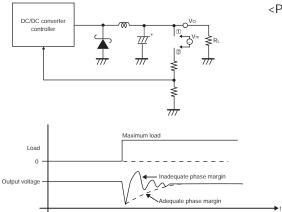

#### <Procedure>

- 1. Check to ensure output causes no oscillation at the maximum load in closed loop.

- Isolate (1) and (2) and insert Vm (with amplitude of approximately 100 mVpp).

- 3. Measure (probe) the oscillation of (1) to that of (2).

Furthermore, the phase margin can also be measured with the load responsiveness.

Measure variations in the output voltage when instantaneously changing the load from no load to the maximum load. Even though ringing phenomenon is caused, due to low phase margin, no ringing takes place. Phase margin is provided. However, no specific phase margin can be probed.

#### Heat loss

For thermal design, be sure to operate the IC within the following conditions.

- (Since the temperatures described hereunder are all guaranteed temperatures, take the margin into account.)

- 1. The ambient temperature Ta is to be 125°C or less.

- 2. The chip junction temperature Tj is to be 150°C or less.

The chip junction temperature Tj can be considered in the following two patterns:

| To obtain Tj from the IC surface<br>temperature Tc in the actual use state,<br>Tj = Tc+θj–c × W | To obtain Tj from the ambient temperature Ta Tj=Ta+ $\theta j\text{-}a\times W$               |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <reference value=""> 0j-c : HRP7 7°C/W</reference>                                              | <reference value=""> θj-a : HRP7 89.3°C/W Single piece of IC</reference>                      |

| SOP8 32.5°C/W                                                                                   | 54.3°C/W 2-layer PCB (Copper foil area on the front side<br>of PCB: 15 × 15 mm <sup>2</sup> ) |

|                                                                                                 | 22.7°C/W 2-layer PCB (Copper foil area on the front side<br>of PCB: 70 × 70 mm <sup>2</sup> ) |

|                                                                                                 | PCB size: $70 \times 70 \times 1.6$ mm <sup>3</sup> (PCB incorporates thermal via             |

|                                                                                                 | Copper foil area on the front side of PCB: $10.5 \times 10.5$ mm <sup>2</sup>                 |

|                                                                                                 | SOP8 222.2°C/W Single piece of IC                                                             |

|                                                                                                 | 181.8°C/W 1-layer PCB                                                                         |

|                                                                                                 | PCB size: $70 \times 70 \times 1.6 \text{ mm}^3$                                              |

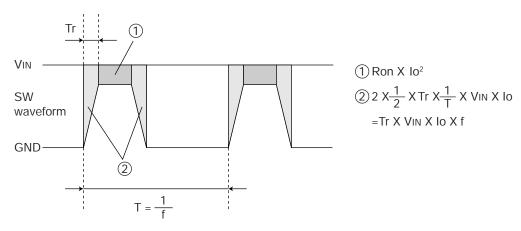

The heat loss W of the IC can be obtained by the formula shown below:

$$W=Ron \times Io^{2} \times \frac{Vo}{VIN} + VIN \times ICC + Tr \times VIN \times Io \times f$$

Ron: ON resistance of IC (refer to pages 4 and 5.) Io: Load current Vo: Output voltage VIN: Input voltage Icc: Circuit current (Refer to pages 2 and 3)

Tr: Switching rise/fall time (Approximately 40 nsec)

f : Oscillation frequency

Fig.36 Equivalent circuit

#### Cautions on use

1) Absolute maximum ratings

An excess in the absolute maximum ratings, such as supply voltage, temperature range of operating conditions, etc., can break down the devices, thus making impossible to identify breaking mode, such as a short circuit or an open circuit. If any over rated values will expect to exceed the absolute maximum ratings, consider adding circuit protection devices, such as fuses. Furthermore, don't turn on the IC with a fast rising edge of VIN. ( rise time << 10V / µsec )

2) GND potential

GND potential should maintain at the minimum ground voltage level. Furthermore, no terminals should be lower than the GND potential voltage including an electric transients.

3) Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

4) Inter-pin shorts and mounting errors

Use caution when positioning the IC for mounting on printed circuit boards. The IC may be damaged if there is any connection error or if positive and ground power supply terminals are reversed. The IC may also be damaged if pins are shorted together or are shorted to other circuits power lines.

5) Operation in strong electromagnetic field

Use caution when using the IC in the presence of a strong electromagnetic field as doing so may cause the IC to malfunction.

6) Inspection with set printed circuit board

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress. Always discharge capacitors after each process or step. Always turn the IC's power supply off before connecting it to, or removing it from a jig or fixture, during the inspection process. Ground the IC during assembly steps as an antistatic measure. Use similar precaution when transporting and storing the IC.

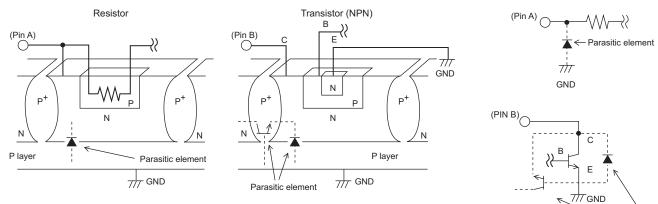

7) IC pin input (Fig. 37)

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements to keep them isolated. P-N junctions are formed at the intersection of these P layers with the N layers of other elements, creating a parasitic diode or transistor. For example, the relation between each potential is as follows:

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When Pin B > GND > Pin A, the P-N junction operates as a parasitic transistor. Parasitic diodes can occur inevitably in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Accordingly, methods by which parasitic diodes operate, such as applying a voltage that is lower than the GND (P substrate) voltage to an input pin, should not be used.

Parasitic element

#### 8. Ground wiring pattern

It is recommended to separate the large-current GND pattern from the small-signal GND pattern and establish a single ground at the reference point of the set PCB, so that resistance to the wiring pattern and voltage fluctuations due to a large current will cause no fluctuations in voltages of the small-signal GND. Prevent fluctuations in the GND wiring pattern of external parts.

#### 9. Temperature protection (thermal shut down) circuit

This IC has a built-in temperature protection circuit to prevent the thermal destruction of the IC. As described above, be sure to use this IC within the power dissipation range. Should a condition exceeding the power dissipation range continue, the chip temperature Tj will rise to activate the temperature protection circuit, thus turning OFF the output power element. Then, when the tip temperature Tj falls, the circuit will be automatically reset. Furthermore, if the temperature protection circuit is activated under the condition exceeding the absolute maximum ratings, do not attempt to use the temperature protection circuit for set design.

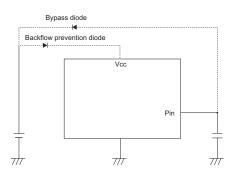

10. On the application shown below, if there is a mode in which VIN and each pin potential are inverted, for example, if the VIN is short-circuited to the Ground with external diode charged, internal circuits may be damaged. To avoid damage, it is recommended to insert a backflow prevention diode in the series with VIN or a bypass diode between each pin and VIN.

PCB size: 70 x 70 x 1.6 mm<sup>3</sup> (PCB incorporates thermal via.) Copper foil area on the front side of PCB: 10.5 x 10.5 mm

2 2-layer PCB (Copper foil area on the reverse side of PCB: 15 x 15 mm<sup>2</sup>)

① Single piece of IC 2 When mounted on ROHM standard PCB (Glass epoxy PCB of 70 mm x 70 mm x 1.6 mm)

Fig.40

#### Notes

- No technical content pages of this document may be reproduced in any form or transmitted by any means without prior permission of ROHM CO.,LTD.

- The contents described herein are subject to change without notice. The specifications for the

product described in this document are for reference only. Upon actual use, therefore, please request

that specifications to be separately delivered.

- Application circuit diagrams and circuit constants contained herein are shown as examples of standard use and operation. Please pay careful attention to the peripheral conditions when designing circuits and deciding upon circuit constants in the set.

- Any data, including, but not limited to application circuit diagrams information, described herein are intended only as illustrations of such devices and not as the specifications for such devices. ROHM CO.,LTD. disclaims any warranty that any use of such devices shall be free from infringement of any third party's intellectual property rights or other proprietary rights, and further, assumes no liability of whatsoever nature in the event of any such infringement, or arising from or connected with or related to the use of such devices.

- Upon the sale of any such devices, other than for buyer's right to use such devices itself, resell or

otherwise dispose of the same, no express or implied right or license to practice or commercially

exploit any intellectual property rights or other proprietary rights owned or controlled by

- ROHM CO., LTD. is granted to any such buyer.

- Products listed in this document are no antiradiation design.

The products listed in this document are designed to be used with ordinary electronic equipment or devices (such as audio visual equipment, office-automation equipment, communications devices, electrical appliances and electronic toys).

Should you intend to use these products with equipment or devices which require an extremely high level of reliability and the malfunction of which would directly endanger human life (such as medical instruments, transportation equipment, aerospace machinery, nuclear-reactor controllers, fuel controllers and other safety devices), please be sure to consult with our sales representative in advance.

It is our top priority to supply products with the utmost quality and reliability. However, there is always a chance of failure due to unexpected factors. Therefore, please take into account the derating characteristics and allow for sufficient safety features, such as extra margin, anti-flammability, and fail-safe measures when designing in order to prevent possible accidents that may result in bodily harm or fire caused by component failure. ROHM cannot be held responsible for any damages arising from the use of the products under conditions out of the range of the specifications or due to non-compliance with the NOTES specified in this catalog.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact your nearest sales office.

# **ROHM** Customer Support System

THE AMERICAS / EUROPE / ASIA / JAPAN

# www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2008 ROHM CO.,LTD. ROHM CO., LTD. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan TEL : +81-75-311-2121 FAX : +81-75-315-0172

Appendix1-Rev2.0

rohm