# FAN5232 Adjustable PWM Buck Controller for LCD PCs

## Features

- Three outputs: Adjustable Buck, 3.3V-Always, 5V-Always

- Adjustable synchronous switcher, 5V 80% Vin

- 1% internal reference precision

- Current mode with voltage feed-forward

- Precision current limit option

- Charge pump works at all loads

- No shoot-through current

- Independent shutdown pins for ACPI

- Power Good, input UVLO, output OV

- 5.6V to 24V input voltage range

# **Applications**

- LCD PCs

- Notebook PCs and PDAs

- Hand-held portable instruments

# Description

The FAN5232 is a high efficiency and high precision DC/DC controller for PCs. It has a synchronous switcher whose output can be adjusted from 5V up to 80% of Vin. It also has two linear regulators for standby, 3.3V and 5V. The PWM utilizes both input and output voltage feedback in a current-mode control, allowing for fast and stable loop response over a wide range of input and output variations. Synchronous switching provides best efficiency over a wide range of loads. Current sense based on MOSFET  $R_{DS,on}$  gives maximum efficiency, while also permitting use of an optional sense resistor for high precision.

The FAN5232 is available in a 14 pin TSSOP package.

# **Block Diagram**

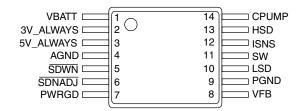

### **Pin Assignments**

### **Pin Description**

| Pin Number | Pin Name  | Pin Function Description                                                                                                                     |

|------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VBATT     | Battery Voltage. Battery voltage sensor.                                                                                                     |

| 2          | 3V_ALWAYS | <b>3.3V-ALWAYS Linear Regulator.</b> Total load current on pins 2 and 3 together must not exceed 50mA.                                       |

| 3          | 5V_ALWAYS | <b>5V-ALWAYS Linear Regulator.</b> Total load current on pins 2 and 3 together must not exceed 50mA.                                         |

| 4          | AGND      | Analog Ground.                                                                                                                               |

| 5          | SDWN      | IC Shutdown. Puts entire chip into shutdown. OFF=0. ON=1.                                                                                    |

| 6          | SDNADJ    | Shutdown and Softstart for the Switcher. OFF=0. ON=1.                                                                                        |

| 7          | PWRGD     | <b>Switcher Output OK.</b> An open collector output that will be low if the switcher output is out of spec.                                  |

| 8          | VFBSW     | Voltage Feedback for the Switcher.                                                                                                           |

| 9          | PGND      | <b>Ground for the Switcher.</b> Connect by the shortest possible path to the source of the low side MOSFET.                                  |

| 10         | LSD       | <b>Low Side FET Driver for the Switcher.</b> Connect this pin through a resistor to the gate of an N-channel MOSFET.                         |

| 11         | SW        | High Side FET Source and Low Side FET Drain Switching Node.                                                                                  |

| 12         | ISNS      | <b>Current Feedback for the Switcher.</b> Connect by the shortest possible path to a resistor connected to the drain of the low side MOSFET. |

| 13         | HSD       | <b>High Side FET Driver for the Switcher.</b> Connect this pin through a resistor to the gate of an N-channel MOSFET.                        |

| 14         | CPUMP     | <b>Charge Pump for the Switcher.</b> Generates gate drive voltage for the high-side MOSFET.                                                  |

# Absolute Maximum Ratings<sup>1</sup>

| Parameter                                            | Conditions | Min. | Тур.      | Max. | Units        |

|------------------------------------------------------|------------|------|-----------|------|--------------|

| VBATT Pin                                            |            | -0.3 |           | 29   | V            |

| PHASE, IFB, SDWN Pins                                |            | -5   |           | 29   | V            |

| CPUMP, HSD Pins                                      |            | -0.3 |           | 34   | V            |

| All Other Pins                                       |            | -0.3 |           | 6.5  | V            |

| Thermal Resistance, $\theta_{J-A}$<br>$\theta_{J-C}$ |            |      | 100<br>32 |      | °C/W<br>°C/W |

| Junction Temperature                                 |            |      |           | 150  | °C           |

| Storage Temperature                                  |            | -65  |           | 150  | °C           |

| Lead Temperature, Soldering 10 sec.                  |            |      |           | 300  | °C           |

Note:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

# **Recommended Operating Conditions**

| Parameter           | Conditions | Min. | Тур. | Max. | Units |

|---------------------|------------|------|------|------|-------|

| VBATT Voltage       |            | 5.6  |      | 24   | V     |

| Ambient Temperature |            | -20  |      | 85   | °C    |

## **Electrical Specifications**

( $V_{BATT}$  = 16V,  $T_A$  = -20 to 85°C, circuit of Figure 1, unless otherwise specified.)

| Parameter                                              | Conditions                                                  | Min.  | Тур. | Max.  | Units           |  |

|--------------------------------------------------------|-------------------------------------------------------------|-------|------|-------|-----------------|--|

| Supply                                                 |                                                             |       |      |       |                 |  |

| V <sub>CC</sub> Input Quiescent Current                | H/LSD Open                                                  |       |      | 1.4   | mA              |  |

|                                                        | Stand-by                                                    |       |      | 60    | μA              |  |

|                                                        | Shut-down                                                   |       |      | 10    | μA              |  |

| V <sub>CC</sub> Input UVLO Threshold                   | Rising                                                      | 4.3   | 4.5  | 5.1   | V               |  |

|                                                        | Falling                                                     | 4.0   | 4.3  | 4.7   | 1               |  |

| Switcher                                               |                                                             |       |      |       |                 |  |

| Output Voltage Precision, VFB                          | $0.1 \le I \le 5.5A, 7.2 \le VBATT \le 24V$                 | 4.900 | 5    | 5.100 | V               |  |

|                                                        | $I \le 100 \text{mA}, 5.6 \le \text{VBATT} \le 24 \text{V}$ | 4.900 | 5    | 5.100 |                 |  |

| Oscillator Frequency, f <sub>OSC</sub>                 |                                                             | 255   | 300  | 345   | KHz             |  |

| Gate Drive On-Resistance for all Sources and HSD Sinks |                                                             |       | 6    | 12    | Ω               |  |

| Gate Drive On Resistance for LSD Sink                  |                                                             |       | 1.5  | 8     | Ω               |  |

| HSD On Output, V <sub>CPUMP</sub> -V <sub>GS</sub>     | I = 10μA                                                    |       |      | 100   | mV              |  |

| HSD Off Output, V <sub>GS</sub>                        | I = -10μA                                                   |       |      | 100   | mV              |  |

| LSD On Output, V <sub>5V-Always</sub> -V <sub>GS</sub> | I = 10μA                                                    |       |      | 100   | mV              |  |

| LSD Off Output, V <sub>GS</sub>                        | I = -10μA                                                   |       |      | 100   | mV              |  |

| Ramp Amplitude, pk-pk                                  |                                                             |       | 2    |       | V               |  |

| Ramp Offset                                            |                                                             |       | 0.5  |       | V               |  |

| Ramp Gain from VBATT                                   |                                                             |       | 125  |       | mV/V            |  |

| Error Amplifier GBW                                    |                                                             |       | 3    |       | MHz             |  |

| Current Limit Threshold                                | R3 = 1KΩ                                                    | 135   | 150  | 165   | mV              |  |

| Over Voltage Threshold                                 | 2µs delay                                                   | 110   | 115  | 120   | %V <sub>O</sub> |  |

| Under Voltage Threshold                                | 2µs delay                                                   | 70    | 75   | 80    | %V <sub>O</sub> |  |

| Max Duty Cycle                                         |                                                             | 80    |      |       | %               |  |

| Min HSD On-time                                        |                                                             |       | 200  |       | nsec            |  |

| VFBSW, ISNS Input Leakage<br>Current                   |                                                             |       | 100  | 200   | nA              |  |

| SDN/SS Full On Voltage Min.                            |                                                             | 4.2   |      |       | V               |  |

| SDN/SS Full Off Voltage Max.                           |                                                             |       |      | 800   | mV              |  |

| 5V and 3.3V Always                                     | · · · · · · · · · · · · · · · · · · ·                       |       |      | 1     |                 |  |

| Linear Regulator Accuracy                              | $5.6V \le VBATT \le 22V$ ,<br>$0 \le ILOAD \le 50mA$        | -3.3  |      | 2     | %               |  |

| Rated Output Current                                   | I <sub>3.3</sub> + I <sub>5</sub>                           |       |      | 50    | mA              |  |

| Overcurrent Limit                                      | 2µs delay                                                   | 100   |      | 180   | mA              |  |

| Undervoltage Threshold                                 | 2µs delay                                                   | 70    | 75   | 80    | %               |  |

REV. 1.1.1 10/7/02

### Electrical Specifications (Continued)

$(V_{BATT} = 16V, T_A = -20 \text{ to } 85^{\circ}C, \text{ circuit of Figure 1, unless otherwise specified.})$

| Parameter                           | Conditions                   | Min. | Тур. | Max. | Units           |

|-------------------------------------|------------------------------|------|------|------|-----------------|

| <b>Control and Signal Functions</b> |                              |      |      | •    | •               |

| Control Logic Low                   |                              |      |      | 600  | mV              |

| Control Logic High                  |                              | 2    |      |      | V               |

| Softstart Current                   |                              | 3    | 5    | 7    | μA              |

| Over-temperature Shutdown           |                              |      | 150  |      | °C              |

| Over-temperature Hysteresis         |                              |      | 25   |      | °C              |

| PWRGD Threshold                     |                              | -14  | -12  | -9   | %V <sub>O</sub> |

| PWRGD Saturation Voltage            | I <sub>sink</sub> = 4mA      |      |      | 400  | mV              |

| PWRGD Leakage Current               | $V_{CC} = 5.5V$              |      |      | 1    | μA              |

| PWRGD Pulse Width for Trip          | $Low \to High, High \to Low$ | 5    |      | 10   | µsec            |

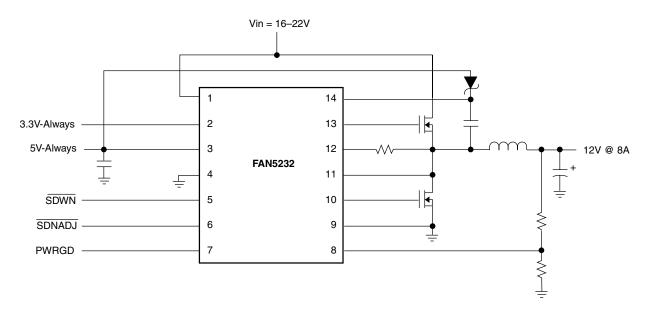

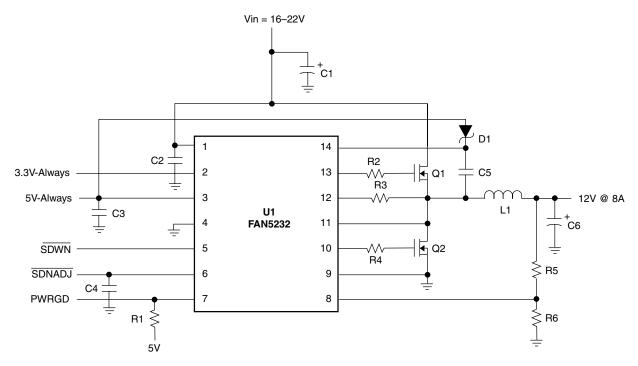

# **Application Circuit**

Downloaded from Elcodis.com electronic components distributor

| Reference | Manufacturer, Part #    | Quantity | Description                                      | Comments                        |

|-----------|-------------------------|----------|--------------------------------------------------|---------------------------------|

| C1        | SANYO<br>25SV47M        | 1        | 47μF, 25V                                        | OSCON, I <sub>rms</sub> = 3.5A  |

| C2-5      | Any                     | 4        | 100nF, 50V                                       | Ceramic                         |

| C6        | AVX<br>TPSE227M016#0100 | 1        | 220µF, 16V                                       | Tantalum, ESR=100m $\Omega$     |

| R1        | Any                     | 1        | 10KΩ, 1%                                         |                                 |

| R2, R4    | Any                     | 2        | 4.7Ω, 1%                                         |                                 |

| R3, R5    | Any                     | 2        | 1KΩ, 1%                                          |                                 |

| R6        | Any                     | 1        | 715Ω, 1%                                         |                                 |

| D1        | Fairchild<br>MBR0540L   | 1        | 500mA, 40V Schottky                              |                                 |

| L1        | Coiltronics<br>UP2B-1R5 | 1        | 1.5µH, 8.3A                                      | R < 8mΩ                         |

| Q1        | Fairchild<br>FDS6690A   | 1        | 30V N-channel MOSFET                             | $R = 20m\Omega @ V_{GS} = 4.5V$ |

| Q2        | Fairchild<br>FDS6680S   | 1        | 30V N-channel MOSFET<br>with Integrated Schottky | $R = 17m\Omega @ V_{GS} = 4.5V$ |

| U1        | Fairchild FAN5232       | 1        | Controller                                       |                                 |

Table 1. RC5232 Application Bill of Materials

### **Application Information**

#### Overview

The FAN5232 is a high efficiency and high precision DC/DC controller for LCD PCs and portable applications. It provides a switcher controller capable of generating a voltage between 5V to 80% of Vin, and a 5V and a 3.3V linear regulator for standby applications. The controller has a power good output and an enable/soft start to permit proper system sequencing.

#### Initialization

The FAN5232 automatically initializes upon receipt of input power. The Power-on Reset (POR) function continually monitors the input supply voltage on the  $V_{CC}$  pin and initiates soft start operation after the input supply voltage exceeds 4.5V. Should this voltage drop below 4.0V, POR disables the chip.

#### Soft Start

When soft start is initiated by POR, and if the SDWN pin is not held low, the voltage on the SDNADJ pin begins ramping up, with the rate of rise set by the external capacitor on the pin. Below 700mV, the output is off. Between 700mV and 1.6V, the output is allowed to linearly ramp up. Above 1.6V, the output is fully enabled, and regulates.

#### Shutdown

There are two separate shutdown pins to provide output power control –  $\overline{\text{SDWN}}$ , and  $\overline{\text{SDNADJ}}$ . Taking the  $\overline{\text{SDNADJ}}$ pin low will disable the switcher output and reset the output's internal latches for short circuit, under-voltage and over-voltage. Taking the  $\overline{\text{SDWN}}$  pin low puts the entire chip in shutdown. Each of the SDN pins has an internal pull-up.

### Switcher Architecture

#### Overview

The switcher output of the FAN5232 is generated from the unregulated input (battery) voltage using a synchronous buck converter. Both high-side and low-side MOSFETs are N-channel.

The converter has pins for current sensing using the low-side MOSFET  $R_{DS,on}$ ; a pin for voltage-sense feedback; a pin that enables the converter and permits soft-start; a power good pin; and a pin for generating the boost voltage to drive the high-side MOSFET.

#### Loop Compensation

The switcher regulator control loop of the FAN5232 is current-mode with voltage feed-forward. It uses voltage feed-forward to guarantee loop rejection of input voltage variation: the ramp amplitude is varied as a function of the input voltage. Compensation of the control loop is done entirely internally using current-mode compensation. This scheme allows the bandwidth and phase margin to be almost independent of output capacitance and capacitors' ESR. Use of a current sense resistor other than the recommended  $1K\Omega$ may affect the converter's stability.

#### **Current Sensing**

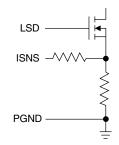

Current sensing is done by measuring the voltage across the low side MOSFET 50nsec after it is turned on. This value is then held for current feedback and over-current limit. The gain is set by an external resistor from the drain to the ISNS pin, which is normally set to be  $1K\Omega$ .

#### **Current Limit**

The converter senses the voltage across its low-side MOSFET to determine when to enter current limit. If output current in excess of the current limit threshold is measured, the converter enters pulse skip mode with  $I_{out}$  equal to the over-current (OC) limit. If this situation persists for 8 clock cycles then the regulator is latched off (HSD and LSD off). This is the likely scenario in case of a "soft" short. If the short is "hard", it will instantly trigger the under-voltage protection, which again will latch the regulator off (HSD and LSD off) after a 2µsec delay.

Selection of a current-limit set resistor must include the tolerance of the current-limit trip point, the MOSFET resistance and temperature coefficient, and the ripple current, in addition to the maximum output current.

**Example**: Maximum DC output current on the 12V is 8A, the MOSFET  $R_{DS,on}$  is  $17m\Omega$ , and the inductor is  $4.7\mu$ H at a current of 8A. Because of the low  $R_{DS,on}$ , the low-side MOSFET will have a maximum temperature (ambient + self-heating) of only 75°C, at which its  $R_{DS,on}$  increases to 24m $\Omega$ .

Peak current is DC output current plus peak ripple current:

$$I_{pk} \approx I_{DC} + \frac{TV_O \bullet (V_{in} - V_o)}{2 \bullet L \bullet V_{in}}$$

$$= 8A + \frac{4\mu s \bullet 12V \bullet (19V - 12V)}{2 \bullet 4.7\mu H \bullet 12V} = 11A$$

where T is the maximum period,  $V_O$  is output voltage,  $V_{in}$  is input voltage, and L is the inductance. This current generates a voltage on the low-side MOSFET of 11A • 24m $\Omega$  = 254mV. The current limit threshold is typically 150mV (worst-case 135mV) with R2 = 1K $\Omega$ , and so this value must be decreased to (135/254) • 1K $\Omega$  = 531 $\Omega$ .

#### **Precision Current Limit**

Precision current limiting can be achieved by placing a discrete sense resistor between the source of the low-side MOSFET and ground. Sensing is then accomplished with the  $1K\Omega$  resistor between the sense resistor and the IFBSW pin, as shown in Figure 2. In this case, current limit accuracy is set by the tolerance of the IC,  $\pm 10\%$ .

**Figure 2. Precision Current Sensing**

#### Softstart

Softstart of the switcher is accomplished by means of an external capacitor between pins **SDNADJ** and ground.

#### **Overvoltage Protection (Soft Crowbar)**

When the output voltage of the switcher exceeds approximately 115% of nominal, it enters into over-voltage (OV) protection, with the goal of protecting the load from damage. During operation, severe load dump or a short of an upper MOSFET can cause the output voltage to increase significantly over normal operation range. When the output exceeds the over-voltage threshold of 115%, the over-voltage comparator forces the lower gate driver high and turns the lower MOSFET on. This will pull down the output voltage and eventually may blow the battery fuse. As soon as output voltage drops below the threshold, the OVP comparator is disengaged.

This OVP scheme provides a soft crowbar function (bangbang control followed by blow of the fuse), which helps to tackle severe load transients and does not invert the output voltage when activated – common problem for OVP schemes with a latch. The prevention of the output inversion saves the use of a Schottky diode across the load.

#### **Undervoltage Protection**

When the output voltage of the switcher falls below 75% of nominal value, after a 2usec delay it goes into under-voltage protection. In under-voltage protection, the high and low side MOSFETs are turned off. Once under-voltage protection is triggered, it remains on until power is recycled.

#### 5V/3.3V-ALWAYS Operation

The 5V-ALWAYS supply is generated from the on-chip linear regulator off the input supply voltage. The 3.3V-ALWAYS is generated from a linear regulator attached internally to the 5V-ALWAYS.

The purpose of these two supplies -whose combined current is specified to never exceed 50mA- is to provide power to the system micro-controller (8051 class) as well as a few other ICs needing a stand-by power. The micro-controller as well as the other IC's discussed here are migrating from 5V to 3.3V power at different times and we expect that some "legacy" devices will continue to need 5V indefinitely.

#### 5V/3.3V-ALWAYS Protections

The two internal linear regulators are current limit and undervoltage protected. Once protection is triggered **all** outputs go off until power is recycled.

#### **ALWAYS mode of Operation**

If it is desired that the ALWAYS voltages are always ON then the  $\overline{\text{SDWN}}$  pin must be connected to V<sub>CC</sub> permanently. This way the ALWAYS regulator comes up as soon as there is power while the state of the switcher can be controlled via the  $\overline{\text{SDNADJ}}$  pin.

### **Component Selection**

#### Switcher MOSFET Selection

The application circuit shown in Figure 1 is designed to run with an input voltage operating range of 16–22V. This input range helps determine the selection of the MOSFETs for the switcher, since the high-side MOSFET can be on as much as  $(V_{out} / V_{in}) = 12V / 16V = 75\%$  of the time, and the low-side MOSFET as much as  $1 - (V_{out} / V_{in}) = 1 - (12V / 22V) = 45\%$  of the time.

The MOSFETs have maximum duty cycles greater than 45%. Thus, it is necessary to size both approximately the same.

#### **Switcher Schottky Selection**

In the application shown in Figure 1, the use of a SynchFET eliminates the need of a Schottky diode for the synchronous buck. If SynchFETs are not used, selection of a schottky is determined by the maximum current at which the converter operates. Select a diode whose instantaneous Vf is less than 0.75V at the maximum output current. The schottky dissipates no power, because it is on for only a very small portion of the switching cycle.

#### **Input Capacitor Selection**

Input capacitor selection is determined by ripple current rating by the formula:

$$I_{\rm rms} = I_{\rm out} \sqrt{DC - DC^2}$$

where I<sub>out</sub> is the output current of the converter, and DC is

the duty cycle,  $DC = V_{in} / V_{out}$ . Capacitor ripple current rating is a function of temperature and switching frequency, and so the manufacturer should be contacted to find out the ripple current rating at the expected operational temperature and frequency.

#### Soft Start Capacitor selection

The recommended value of the soft start capacitor is 100nF. This will result in roughly 20msec turn on time. The general formula is:

$$C_{SS} = \frac{(I_{SS} \bullet T_{SS})}{1.125V}$$

Where  $I_{SS}$  is the soft start current (5µA),  $T_{SS}$  is the soft start delay (i.e. 20msec).

### **Control and Signal Circuitry**

#### Power Good

Power Good is an open-collector signal, and is asserted when the outputs are greater than 88% of nominal for more than 2µsec. When PWRGD goes low it will stay low for at least 2µsec.

#### **Fault Handling**

The FAN5232 has a full suite of protection against faults. Consult Table 2 for an overview, and the individual sections for details.

#### **Table 2. Fault Handling**

| Fault<br>Condition | Switcher                 | 3V- and<br>5V-Always     |

|--------------------|--------------------------|--------------------------|

| OC Switcher        | Latch off                | No Change                |

| OC Always          | No Change                | Ramp Down<br>till UV     |

| UV Switcher        | Latch off after<br>2µsec | No Change                |

| UV Always          | No Change                | Latch off after<br>2µsec |

| UV V <sub>CC</sub> | Off                      | Off                      |

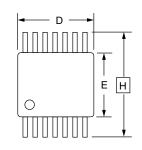

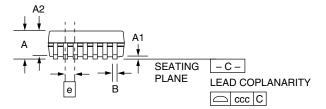

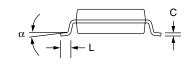

# **Mechanical Dimensions**

#### 14-Lead TSSOP

| Symbol | Inc  | hes  | Millimeters |            | Notes |

|--------|------|------|-------------|------------|-------|

| Symbol | Min. | Max. | Min.        | Max.       | Notes |

| А      | _    | .047 | _           | 1.20       |       |

| A1     | .002 | .006 | 0.05        | 0.15       |       |

| A2     | .031 | .041 | 0.80        | 1.05       |       |

| В      | .007 | .011 | 0.17        | 0.27       | 5     |

| С      | .004 | .008 | 0.09        | 0.20       | 5     |

| D      | .252 | .260 | 6.40        | 6.60       | 2, 4  |

| Н      | .252 | BSC  | 6.40 BSC    |            |       |

| E      | .169 | .177 | 4.30        | 4.50       |       |

| е      | .026 | BSC  | 0.65        | BSC        |       |

| L      | .018 | .030 | 0.45        | 0.75       | 3     |

| Ν      | 14   |      | 1           | 4          | 6     |

| α      | 0°   | 8°   | 0°          | <b>8</b> ° |       |

| ccc    | _    | .004 | _           | 0.10       |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- "D" and "E1" do not include mold flash. Mold flash or protrusions shall not exceed .010 inch (0.25mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. "B" & "C" dimensions include solder finish thickness.

- 6. Symbol "N" is the maximum number of terminals.

### **Ordering Information**

| Product Number | Package       |

|----------------|---------------|

| FAN5232MTC     | 14 Lead TSSOP |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com