Data Sheet May 15, 2006 FN9199.2

# Two-Phase Core Regulator for IMVP-6 Mobile CPUs

The ISL6262 is a two-phase buck converter regulator implementing Intel® IMVP-6 protocol, with embedded gate drivers. The two-phase buck converter uses two interleaved channels to effectively double the output voltage ripple frequency and thereby reduce output voltage ripple amplitude with fewer components, lower component cost, reduced power dissipation, and smaller real estate area.

The heart of the ISL6262 is  $R^3$  Technology<sup>TM</sup>, Intersil's Robust Ripple Regulator modulator. Compared with the traditional multiphase buck regulator, the  $R^3$  Technology<sup>TM</sup> has the fastest transient response. This is due to the  $R^3$  modulator commanding variable switching frequency during a load transient.

Intel Mobile Voltage Positioning (IMVP) is a smart voltage regulation technology, which effectively reduces power dissipation in Intel Pentium processors. To boost battery life, the ISL6262 supports DPRSLRVR (deeper sleep), DPRSTP# and PSI# functions and maximizes the efficiency via automatically enabling different phase operation modes. At heavy load operation of the active mode, the regulator commands the two phase continuous conduction mode (CCM) operation. While the PSI# is asserted at the medium load in the active mode, the ISL6262 smoothly disables one phase and operates in a one-phase CCM. When the CPU enters deeper sleep mode, the ISL6262 enables diode emulation to maximize the efficiency at the light load.

A 7-bit digital-to-analog converter (DAC) allows dynamic adjustment of the core output voltage from 0.300V to 1.500V. A 0.5% system accuracy of the core output voltage over temperature is achieved by the ISL6262.

A unity-gain differential amplifier is provided for remote CPU die sensing. This allows the voltage on the CPU die to be accurately measured and regulated per Intel IMVP-6 specifications. Current sensing can be realized using either lossless inductor DCR sensing or precision resistor sensing. A single NTC thermistor network thermally compensates the gain and the time constant of the DCR variations.

#### **Features**

- Precision Two-phase CORE Voltage Regulator

- 0.5% System Accuracy Over Temperature

- Enhanced load line accuracy

- Internal Gate Driver with 2A Driving Capability

- Dynamic Phase Adding/Dropping

- Microprocessor Voltage Identification Input

- 7-Bit VID Input

- 0.300V to 1.500V in 12.5mV Steps

- Support VID Change on-the-fly

- Multiple Current Sensing Schemes Supported

- Lossless Inductor DCR Current Sensing

- Precision Resistive Current Sensing

- Thermal Monitor

- User Programmable Switching Frequency

- · Differential Remote CPU Die Voltage Sensing

- · Static and Dynamic Current Sharing

- · Overvoltage, Undervoltage, and Overcurrent Protection

- Pb-Free Plus Anneal Available (RoHS Compliant)

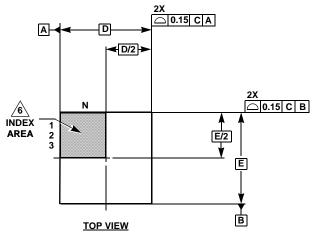

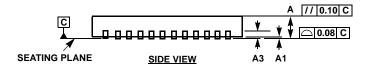

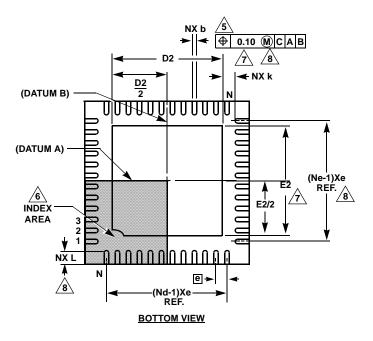

#### Ordering Information

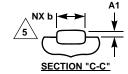

| PART<br>NUMBER         | PART<br>MARKING | TEMP.<br>(°C) | PACKAGE                    | PKG.<br>DWG. # |

|------------------------|-----------------|---------------|----------------------------|----------------|

| ISL6262CRZ<br>(Note)   | ISL6262CRZ      | -10 to 100    | 48 Ld 7x7 QFN<br>(Pb-free) | L48.7x7        |

| ISL6262CRZ-T<br>(Note) | ISL6262CRZ      | -10 to 100    | 48 Ld 7x7 QFN<br>(Pb-free) | L48.7x7        |

| ISL6262IRZ<br>(Note)   | ISL6262IRZ      | -40 to 100    | 48 Ld 7x7 QFN<br>(Pb-free) | L48.7x7        |

| ISL6262IRZ-T<br>(Note) | ISL6262IRZ      | -40 to 100    | 48 Ld 7x7 QFN<br>(Pb-free) | L48.7x7        |

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

## **Pinout**

### **Absolute Maximum Ratings**

| Supply Voltage, VDD               | -0.3 -+7V |

|-----------------------------------|-----------|

| Battery Voltage, VIN              | +25V      |

| Boot1,2 and UGATE1,2              | +30V      |

| ALL Other Pins0.3V to (VD         | D +0.3V)  |

| Open Drain Outputs, PGOOD, VR TT# | -0.3 -+7V |

#### **Thermal Information**

| Thermal Resistance (Typical)           | $\theta_{JA}$ °C/W | / θ <sub>JC</sub> °C/W |

|----------------------------------------|--------------------|------------------------|

| QFN Package (Notes 1, 2)               | 29                 | 4.5                    |

| Maximum Junction Temperature           |                    | 150°C                  |

| Maximum Storage Temperature Range      |                    | -65°C to 150°C         |

| Maximum Lead Temperature (Soldering 10 | )s)                | 300°C                  |

#### **Recommended Operating Conditions**

| Supply Voltage, VDD              | +5V ±5%        |

|----------------------------------|----------------|

| Battery Voltage, VIN             | +5V to 21V     |

| Ambient Temperature              | -10°C to 100°C |

| Junction Temperature             | -10°C to 125°C |

| Ambient Temperature, Industrial  | -40°C to 100°C |

| Junction Temperature, Industrial | -40°C to 125°C |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications**  $V_{DD} = 5V$ ,  $T_A = -40$ °C to 100°C, Unless Otherwise Specified.

| PARAMETER                         | SYMBOL                                          | TEST CONDITIONS                                                                      | MIN   | TYP  | MAX   | UNITS |

|-----------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------|-------|------|-------|-------|

| INPUT POWER SUPPLY                |                                                 |                                                                                      | 1     |      |       | -1    |

| +5V Supply Current                | I <sub>VDD</sub>                                | VR_ON = 3.3V                                                                         | -     | 3.1  | 3.6   | mA    |

|                                   |                                                 | VR_ON = 0V                                                                           | -     | -    | 1     | μA    |

| +3.3V Supply Current              | I <sub>3V3</sub>                                | No load on CLK_EN#                                                                   | -     | -    | 1     | μA    |

| Battery Supply Current at VIN pin | I <sub>VIN</sub>                                | VR_ON = 0V, VIN = 25V,                                                               | -     | -    | 1     | μA    |

| POR (Power-On Reset) Threshold    | POR <sub>r</sub>                                | V <sub>DD</sub> Rising                                                               | -     | 4.35 | 4.5   | V     |

|                                   | POR <sub>f</sub>                                | V <sub>DD</sub> Falling                                                              | 3.9   | 4.1  | -     | ٧     |

| SYSTEM AND REFERENCES             |                                                 |                                                                                      |       |      |       |       |

| System Accuracy                   | %Error<br>(V <sub>cc_core</sub> )               | No load, closed loop, active mode,<br>T <sub>A</sub> = 0°C to 100°C, VID = 0.75-1.5V | -0.5  | -    | 0.5   | %     |

|                                   | ISL6262CRZ                                      | VID = 0.5-0.7375V                                                                    | -8    | -    | 8     | mV    |

|                                   |                                                 | VID = 0.3-0.4875V                                                                    | -15   | -    | 15    | mV    |

|                                   | %Error<br>(V <sub>CC_Core</sub> )<br>ISL6262IRZ | $T_A = -40$ °C to 100°C, VID = 0.75-1.5V                                             | -0.8  | -    | 0.8   | %     |

|                                   |                                                 | VID = 0.5-0.7375V                                                                    | -10   | -    | 10    | mV    |

|                                   |                                                 | VID = 0.3-0.4875V                                                                    | -18   | -    | 18    | mV    |

| RBIAS Voltage                     | R <sub>RBIAS</sub>                              | $R_{RBIAS} = 147k\Omega$                                                             | 1.45  | 1.47 | 1.49  | V     |

| Boot Voltage                      | V <sub>BOOT</sub>                               |                                                                                      | 1.188 | 1.2  | 1.212 | ٧     |

| Maximum Output Voltage            | V <sub>CC_CORE</sub> (max)                      | VID = [0000000]                                                                      | -     | 1.5  | -     | V     |

|                                   | V <sub>CC_CORE</sub> (min)                      | VID = [1100000]                                                                      | -     | 0.3  | -     | V     |

| VID Off State                     |                                                 | VID = [1111111]                                                                      | -     | 0    | -     | V     |

| CHANNEL FREQUENCY                 | I                                               | '                                                                                    | L     |      |       |       |

| Nominal Channel Frequency         | f <sub>SW</sub>                                 | $R_{FSET}$ = 3.9kΩ, 2 channel operation, $V_{comp}$ = 2V                             | -     | 300  | -     | kHz   |

| Adjustment Range                  |                                                 |                                                                                      | 200   | -    | 500   | kHz   |

**Electrical Specifications**  $V_{DD} = 5V$ ,  $T_A = -40$ °C to 100°C, Unless Otherwise Specified. **(Continued)**

| PARAMETER                        | SYMBOL                          | TEST CONDITIONS                                                            | MIN  | TYP  | MAX      | UNITS |

|----------------------------------|---------------------------------|----------------------------------------------------------------------------|------|------|----------|-------|

| AMPLIFIERS                       |                                 |                                                                            |      |      |          |       |

| Droop Amplifier Offset           |                                 |                                                                            | -0.3 | -    | 0.3      | mV    |

| Error Amp DC Gain                | A <sub>V0</sub>                 |                                                                            | -    | 90   | -        | dB    |

| Error Amp Gain-Bandwidth Product | GBW                             | C <sub>L</sub> = 20pF                                                      | -    | 18   | -        | MHz   |

| Error Amp Slew Rate              | SR                              | C <sub>L</sub> = 20pF                                                      | -    | 5    | -        | V/µs  |

| FB Input Current                 | I <sub>IN(FB)</sub>             |                                                                            | -    | 10   | 150      | nA    |

| ISEN                             | -                               |                                                                            |      | l    | l        |       |

| Imbalance Voltage                |                                 |                                                                            | -    | -    | 1        | mV    |

| Input Bias Current               |                                 |                                                                            | -    | 20   | -        | nA    |

| SOFT-START CURRENT               | ļ.                              | +                                                                          |      | ļ    | ļ        | -     |

| Soft-Start Current               | I <sub>SS</sub>                 |                                                                            | -47  | -41  | -35      | μA    |

| Soft Geyserville Current         | I <sub>GV</sub>                 | SOFT - REF >100mV                                                          | ±170 | ±200 | ±230     | μA    |

| Soft Deeper Sleep Entry Current  | I <sub>C4</sub>                 | DPRSLPVR = 3.3V                                                            | -47  | -41  | -35      | μA    |

| Soft Deeper Sleep Exit Current   | I <sub>C4EA</sub>               | DPRSLPVR = 3.3V                                                            | 35   | 41   | 47       | μA    |

| Soft Deeper Sleep Exit Current   | I <sub>C4EB</sub>               | DPRSLPVR = 0V                                                              | 170  | 200  | 230      | μA    |

| GATE DRIVER DRIVING CAPABILIT    |                                 |                                                                            |      |      |          |       |

| UGATE Source Resistance          | R <sub>SRC(UGATE)</sub>         | 500mA Source Current                                                       | -    | 1    | 1.5      | Ω     |

| UGATE Source Current             | I <sub>SRC(UGATE)</sub>         | Vugate_phase = 2.5V                                                        | -    | 2    | -        | А     |

| UGATE Sink Resistance            | R <sub>SNK(UGATE)</sub>         | 500mA Sink Current                                                         | -    | 1    | 1.5      | Ω     |

| UGATE Sink Current               | I <sub>SNK(UGATE)</sub>         | V <sub>UGATE_PHASE</sub> = 2.5V                                            | -    | 2    | -        | Α     |

| LGATE Source Resistance          | R <sub>SRC(LGATE)</sub>         | 500mA Source Current                                                       | -    | 1    | 1.5      | Ω     |

| LGATE Source Current             | I <sub>SRC(LGATE)</sub>         | V <sub>LGATE</sub> = 2.5V                                                  | -    | 2    | -        | Α     |

| LGATE Sink Resistance            | R <sub>SNK(LGATE)</sub>         | 500mA Sink Current                                                         | -    | 0.5  | 0.9      | Ω     |

| LGATE Sink Current               | I <sub>SNK(LGATE)</sub>         | V <sub>LGATE</sub> = 2.5V                                                  | -    | 4    | -        | А     |

| UGATE to PHASE Resistance        | R <sub>p(UGATE)</sub>           |                                                                            | -    | 1.1  | -        | kΩ    |

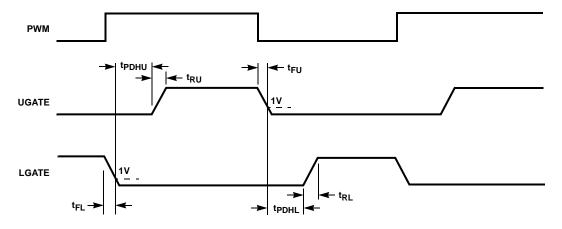

| GATE DRIVER SWITCHING TIMING     |                                 | agram)                                                                     |      |      |          |       |

| UGATE Turn-On Propagation Delay  | t <sub>PDHU</sub><br>ISL6262CRZ | T <sub>A</sub> = -10°C to 100°C<br>PV <sub>CC</sub> = 5V, Outputs Unloaded | 20   | 30   | 44       | ns    |

|                                  | t <sub>PDHU</sub><br>ISL6262IRZ | PV <sub>CC</sub> = 5V, Outputs Unloaded                                    | 18   | 30   | 44       | ns    |

| LGATE Turn-On Propagation Delay  | t <sub>PDHL</sub><br>ISL6262CRZ | T <sub>A</sub> = -10°C to 100°C<br>PV <sub>CC</sub> = 5V, Outputs Unloaded | 7    | 15   | 30       | ns    |

|                                  | t <sub>PDHL</sub><br>ISL6262IRZ | PV <sub>CC</sub> = 5V, Outputs Unloaded                                    | 5    | 15   | 30       | ns    |

| BOOTSTRAP DIODE                  | l                               | 1                                                                          |      | II.  | I        | -1    |

| Forward Voltage                  |                                 | V <sub>DDP</sub> = 5V, Forward Bias Current = 2mA                          | 0.43 | 0.58 | 0.72     | V     |

| Leakage                          |                                 | V <sub>R</sub> = 16V                                                       | -    | -    | 1        | μA    |

| POWER GOOD and PROTECTION        | MONITOR                         | 1                                                                          |      | 1    | <u> </u> |       |

| PGOOD Low Voltage                | V <sub>OL</sub>                 | I <sub>PGOOD</sub> = 4mA                                                   | -    | 0.11 | 0.4      | V     |

|                                  |                                 |                                                                            |      |      |          |       |

# **Electrical Specifications** V<sub>DD</sub> = 5V, T<sub>A</sub> = -40°C to 100°C, Unless Otherwise Specified. **(Continued)**

| PARAMETER SYMBOL TE                            |                                | TEST CONDITIONS                                              | MIN   | TYP  | MAX   | UNITS |

|------------------------------------------------|--------------------------------|--------------------------------------------------------------|-------|------|-------|-------|

| PGOOD Delay                                    | t <sub>pgd</sub><br>ISL6262CRZ | T <sub>A</sub> = -10°C to 100°C<br>CLK_EN# Low to PGOOD High | 5.5   | 6.8  | 8.1   | ms    |

|                                                | t <sub>pgd</sub><br>ISL6262IRZ | CLK_EN# Low to PGOOD High                                    | 5.3   | 6.8  | 8.1   | ms    |

| Overvoltage Threshold                          | O <sub>VH</sub>                | V <sub>O</sub> rising above setpoint > 1ms                   | 160   | 200  | 240   | mV    |

| Severe Overvoltage Threshold                   | O <sub>VHS</sub>               | V <sub>O</sub> rising above setpoint > 0.5μs                 | 1.675 | 1.7  | 1.725 | V     |

| OCSET Reference Current                        |                                | I(Rbias) = 10μA                                              | 9.8   | 10   | 10.2  | μA    |

| OC Threshold Offset                            |                                | DROOP rising above OCSET > 120µs                             | -3.5  | -    | 3.5   | mV    |

| Current Imbalance Threshold                    |                                | Difference between ISEN1 and ISEN2 > 1ms                     | -     | 7.5  | -     | mV    |

| Undervoltage Threshold<br>(VDIFF-SOFT)         | UV <sub>f</sub>                | V <sub>O</sub> falling below setpoint for > 1ms              | -365  | -300 | -240  | mV    |

| LOGIC INPUTS                                   |                                |                                                              |       | I    | 11    |       |

| VR_ON, DPRSLPVR and PGD_IN Input Low           | V <sub>IL</sub>                |                                                              | -     | -    | 1     | V     |

| VR_ON, DPRSLPVR and PGD_IN Input High          | $V_{IH}$                       |                                                              | 2.3   | -    | -     | V     |

| Leakage Current of VR_ON and PGD_IN            | I <sub>IL</sub>                | Logic input is low                                           | -1    | 0    | -     | μA    |

|                                                | I <sub>IH</sub>                | Logic input is high at 3.3V                                  | -     | 0    | 1     | μA    |

| Leakage Current of DPRSLPVR                    | I <sub>IL_DPRSLP</sub>         | DPRSLPVR input is low                                        | -1    | 0    | -     | μA    |

|                                                | I <sub>IH_DPRSLP</sub>         | DPRSLPVR input is high at 3.3V                               | -     | 0.45 | 1     | μA    |

| DAC(VID0-VID6), PSI# and<br>DPRSTP# Input Low  | V <sub>IL</sub>                |                                                              | -     | -    | 0.3   | V     |

| DAC(VID0-VID6), PSI# and<br>DPRSTP# Input High | V <sub>IH</sub>                |                                                              | 0.7   | -    | -     | V     |

| Leakage Current of DAC(VID0-                   | I <sub>IL</sub>                | Logic input is low                                           | -1    | 0    | -     | μA    |

| VID6), PSI# and DPRSTP#                        | I <sub>IH</sub>                | Logic input is high at 1V                                    | -     | 0.45 | 1     | μA    |

| THERMAL MONITOR                                |                                |                                                              |       |      |       |       |

| NTC Source Current                             |                                | NTC = 1.3 V                                                  | 53    | 60   | 68    | μA    |

| Over-Temperature Threshold                     |                                | V(NTC) falling                                               | 1.165 | 1.18 | 1.205 | V     |

| VR_TT# Low Output Resistance                   | R <sub>TT</sub>                | I = 20mA                                                     | -     | 5    | 9     | Ω     |

| CLK_EN# OUTPUT LEVELS                          |                                |                                                              |       | 1    | 1     | 1     |

| CLK_EN# High Output Voltage                    | V <sub>OH</sub>                | 3V3 = 3.3V, I = -4mA                                         | 2.9   | 3.1  | -     | V     |

| CLK_EN# Low Output Voltage                     | V <sub>OL</sub>                | I <sub>CLK</sub> EN# = 4mA                                   | -     | 0.18 | 0.4   | V     |

### ISL6262 Gate Driver Timing Diagram

## Functional Pin Description

**PGOOD -** Power good open-drain output. Will be pulled up externally by a  $680\Omega$  resistor to VCCP or  $1.9k\Omega$  to 3.3V.

**PSI#** - Low load current indicator input. When asserted low, indicates a reduced load-current condition, and product goes into single phase operation.

**PGD\_IN -** Digital Input. When asserted high, indicates VCCP and VCC\_MCH voltages are within regulation.

**RBIAS -** 147K resistor to VSS sets internal current reference.

$VR\_TT\#$  - Thermal overload output indicator with open-drain output. Over temperature pull-down resistance is  $10\Omega$ .

**NTC -** Thermistor input to VRTT# circuit and a 60µA current source is connected internally to this pin.

- **SOFT -** A capacitor from this pin to GND pin sets the maximum slew rate of the output voltage. The SOFT pin is the non-inverting input of the error amplifier.

- OCSET Overcurrent set input. A resistor from this pin to VO sets DROOP voltage limit for OC trip. A  $10\mu$ A current source is connected internally to this pin.

- **VW -** A resistor from this pin to COMP programs the switching frequency (exa.  $4.42k\Omega \cong 300kHz$ ).

- **COMP** This pin is the output of the error amplifier.

- **FB** This pin is the inverting input of error amplifier.

- **FB2** There is a switch between FB2 pin and the FB pin. The switch is closed in single-phase operation and is opened in two phase operation. The components connecting to FB2 is to adjust the compensation in single phase operation to achieve optimum performance.

- **VDIFF** This pin is the output of the differential amplifier.

- VSEN Remote core voltage sense input.

- RTN Remote core voltage sense return.

- **DROOP -** Output of the droop amplifier. The voltage level on this pin is the sum of Vo and the programmed droop voltage by the external resistors.

- **DFB** Inverting input to droop amplifier.

- **VO -** An input to the IC that reports the local output voltage.

- **VSUM -** This pin is connected to the summation junction of channel current sensing.

- **VIN** Battery supply voltage. It is used for input voltage feedforward to improve the input line transient performance.

- VSS Signal ground. Connect to local controller ground.

- VDD 5V control power supply.

- ISEN2 Individual current sharing sensing for channel 2.

- **ISEN1 -** Individual current sharing sensing for channel 1.

- **N/C** Not connected. Grounding this pin to signal ground in the practical layout.

- **BOOT2 -** This pin is the upper gate driver supply voltage for phase 2. An internal boot strap diode is connected to the PVCC pin.

- **UGATE2 -** Upper MOSFET gate signal for phase 2.

- **PHASE2 -** The phase node of phase 2. This pin should connect to the source of upper MOSFET.

- **PGND2** The return path of the lower gate driver for phase 2.

- LGATE2 Lower-side MOSFET gate signal for phase 2.

- **PVCC -** 5V power supply for gate drivers.

- LGATE1 Lower-side MOSFET gate signal for phase 1.

- **PGND1** The return path of the lower gate driver for phase 1.

- **PHASE1 -** The phase node of phase 1. This pin should connect to the source of upper MOSFET.

- **UGATE1 -** Upper MOSFET gate signal for phase 1.

- **BOOT1 -** This pin is the upper gate driver supply voltage for phase 1. An internal boot strap diode is connected to the PVCC pin.

- **VID0, VID1, VID2, VID3, VID4, VID5, VID6 -** VID input with VID0 is the least significant bit (LSB) and VID6 is the most significant bit (MSB).

- **VR\_ON -** Digital input enable. A high level logic signal on this pin enables the regulator.

- **DPRSLPVR** Deeper sleep enable signal. A high level logic indicates the micro-processor is in Deeper Sleep Mode and also indicates a slow C4 entry or exit rate with 41μA discharging or charging the SOFT cap.

- **DPRSTP# -** Deeper sleep slow wake up signal. A low level logic signal on this pin indicates the micro-processor is in deeper sleep mode.

- **CLK\_EN#** Digital output for system PLL clock. Goes active 10µs after PGD\_IN is active and Vcore is within 10% of Boot voltage.

- **3V3 -** 3.3V supply voltage for CLK\_EN#.

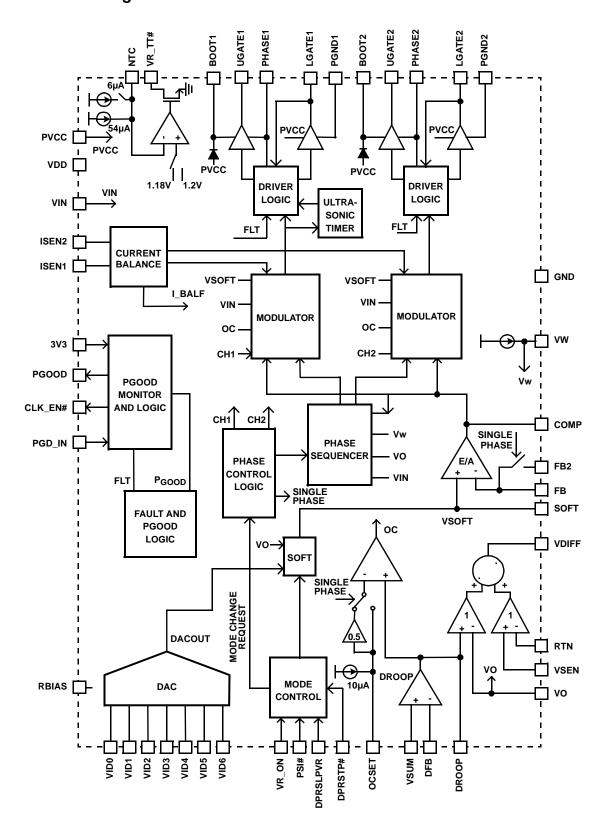

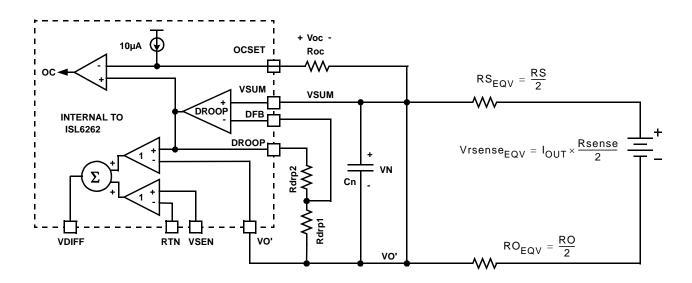

## Functional Block Diagram

FIGURE 1. SIMPLIFIED FUNCTION BLOCK DIAGRAM OF ISL6262

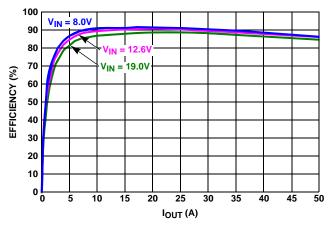

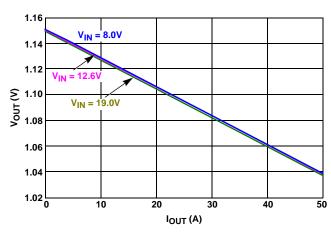

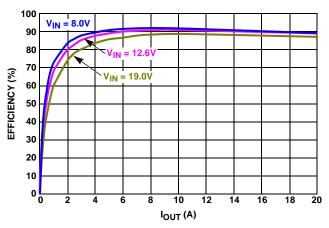

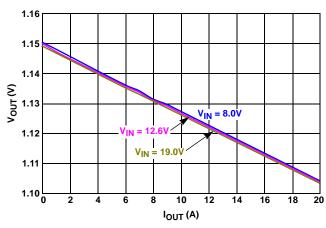

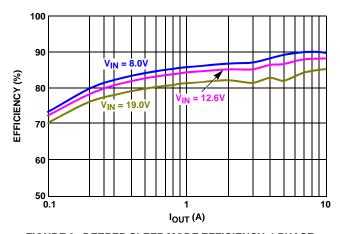

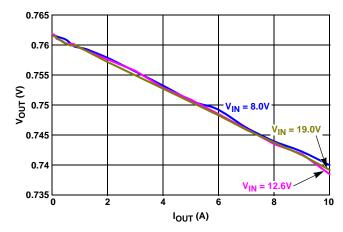

### Typical Performance Curves 300kHz, DCR Sense, 2xIRF7821/2xIRF7832 Per Phase

FIGURE 2. ACTIVE MODE EFFICIENCY, 2 PHASE, CCM, PSI# = HIGH, VID = 1.15V

FIGURE 3. ACTIVE MODE LOAD LINE, 2 PHASE, CCM, PSI# = HIGH, VID = 1.15V

FIGURE 4. ACTIVE MODE EFFICIENCY, 1 PHASE, CCM, PSI# = LOW, VID = 1.15V

FIGURE 5. ACTIVE MODE LOAD LINE, 1 PHASE, CCM, PSI# = LOW, VID = 1.15V

FIGURE 6. DEEPER SLEEP MODE EFFICIENCY, 1 PHASE, DCM MODE, VID = 0.7625V

FIGURE 7. DEEPER SLEEP MODE LOAD LINE, 1 PHASE, DCM MODE, VID = 0.7625V

### Typical Performance Curves 0.36µH Filter Inductor and 4 x 330µF Output SP Caps

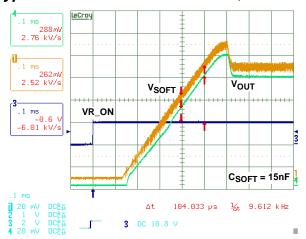

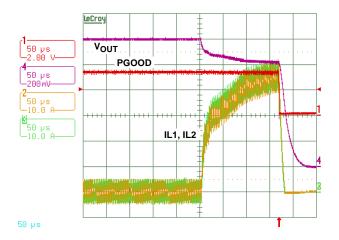

FIGURE 8. SOFT-START WAVEFORM SHOWING SLEW RATE OF 2.5mV/ $\mu$ s AT VID = 1V,  $I_{LOAD}$  = 10A

FIGURE 9. SOFT-START WAVEFORM SHOWING SLEW RATE OF 2.5mV/ $\mu$ s AT VID = 1.4375V,  $I_{LOAD}$  = 10A

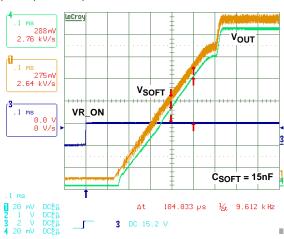

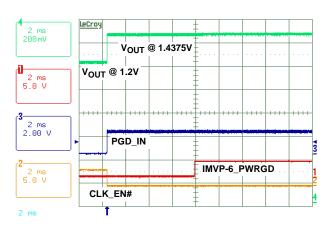

FIGURE 10. SOFT-START WAVEFORM SHOWING CLK\_EN# AND IMVP-6 PGOOD

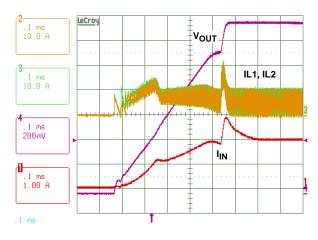

FIGURE 11. INRUSH CURRENT AT START-UP,  $V_{IN}$  = 8V,  $V_{ID}$  = 1.4375V,  $I_{LOAD}$  = 10A

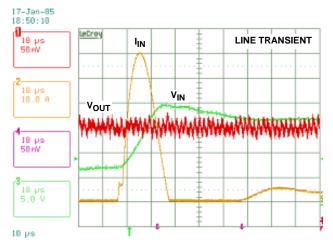

FIGURE 12. 8V-20V INPUT LINE TRANSIENT RESPONSE,  $C_{IN} = 240 \mu F \label{eq:cin}$

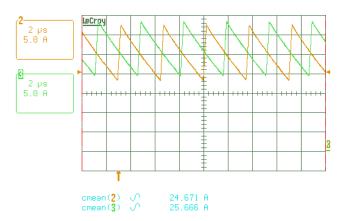

FIGURE 13. 2 PHASE CURRENT BALANCE, FULL LOAD = 50A

#### Typical Performance Curves 0.36µH Filter Inductor and 4 x 330µF Output SP Caps (Continued)

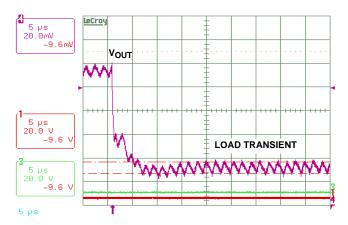

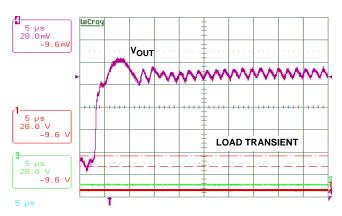

FIGURE 14. LOAD STEP-UP RESPONSE VIA CPU SOCKET MPGA479, 35A LOAD STEP @ 200A/μs, 2 PHASE CCM

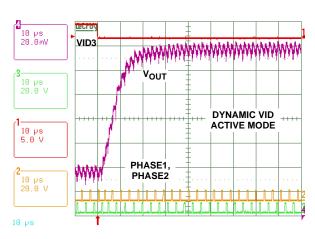

FIGURE 15. VID3 CHANGE OF 010X000 FROM 1.V TO 1.1V AT DPRSLPVR = 0, DPRSTP# = 1, PSI# = 1

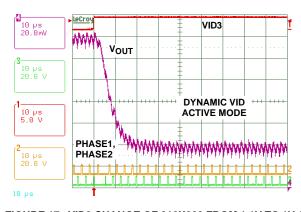

FIGURE 16. LOAD DUMP RESPONSE VIA CPU SOCKET MPGA479, 35A LOAD STEP @ 200A/µs, 2 PHASE CCM

FIGURE 17. VID3 CHANGE OF 010X000 FROM 1.1V TO 1V AT DPRSLPVR = 0, DPRSTP# = 1, PSI# = 1

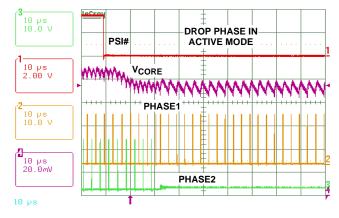

FIGURE 18. 2-CCM TO 1-CCM UPON PSI# ASSERTION WITH VID LSB CHANGE, AT DPRSLPVR = 0, DPRSTP# = 1,  $I_{LOAD}$  = 10A

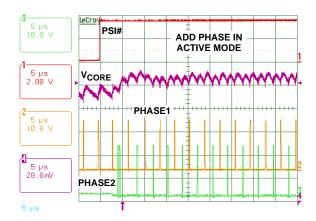

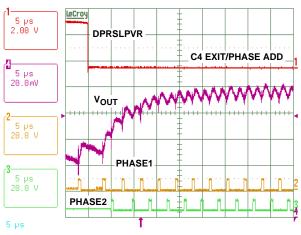

FIGURE 19. 1-CCM TO 2-CCM UPON PSI# DEASSERTION

WITH VID LSB CHANGE AT DPRSLPVR = 0,

DPRSTP# = 1

in<u>ter</u>sil

#### Typical Performance Curves 0.36µH Filter Inductor and 4 x 330µF Output SP Caps (Continued)

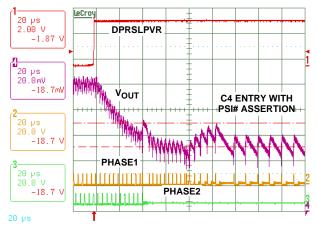

FIGURE 20. C4 ENTER WITH VID CHANGE 0011X00 FROM 1.2V TO 1.15V,  $I_{LOAD}$  = 2A, TRANSITION OF 2-CCM TO 1-DCM, PSI# TOGGLE FROM 1 TO 0 WITH DPRSLPVR FROM 0 TO 1

FIGURE 21. VID3 CHANGE OF 010X000 FROM 1.V TO 1.1V AT DPRSLPVR = 0, DPRSTP# = 1, PSI# = 1

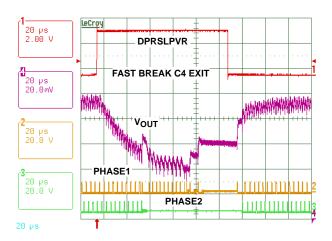

FIGURE 22. FAST BREAK C4 EXIT AT LOAD = 0.1A

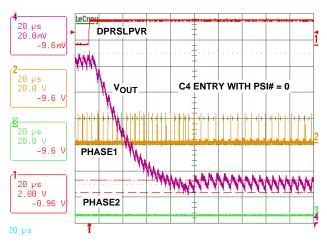

FIGURE 23. C4 ENTRY WITH VID CHANGE OF 011X011 FROM 0.8625V TO 0.7625V, I<sub>LOAD</sub> = 3A, 1-CCM TO 1-DCM

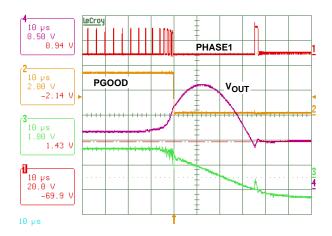

FIGURE 24. OVERCURRENT PROTECTION

FIGURE 25. 1.7V OVERVOLTAGE PROTECTION SHOWS

OUTPUT VOLTAGE PULLED LOW TO 0.9V AND

PWM THREE-STATE

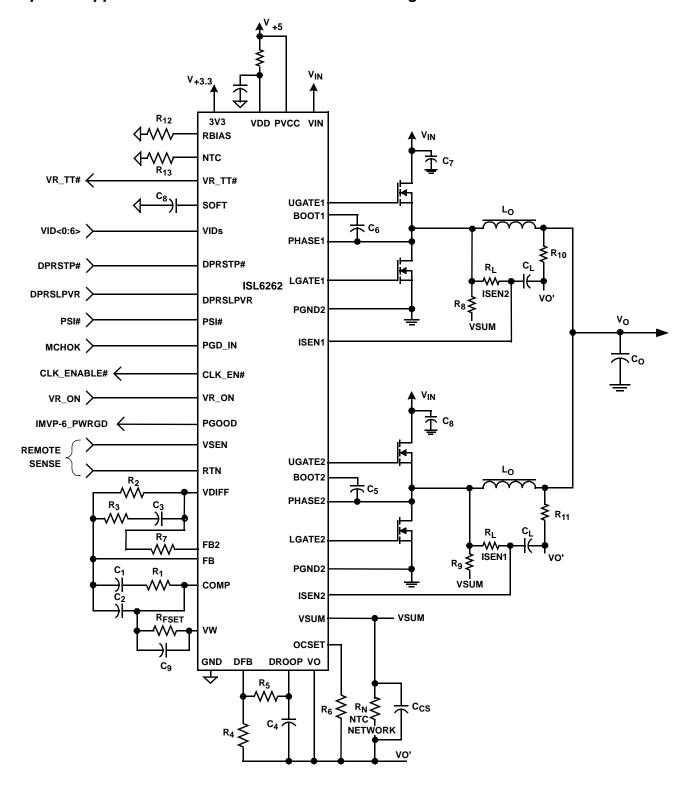

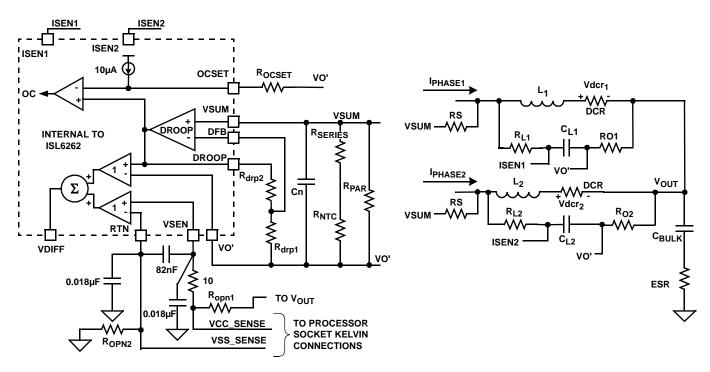

## Simplified Application Circuit for DCR Current Sensing

FIGURE 26. ISL6262 BASED TWO-PHASE BUCK CONVERTER WITH INDUCTOR DCR CURRENT SENSING

13

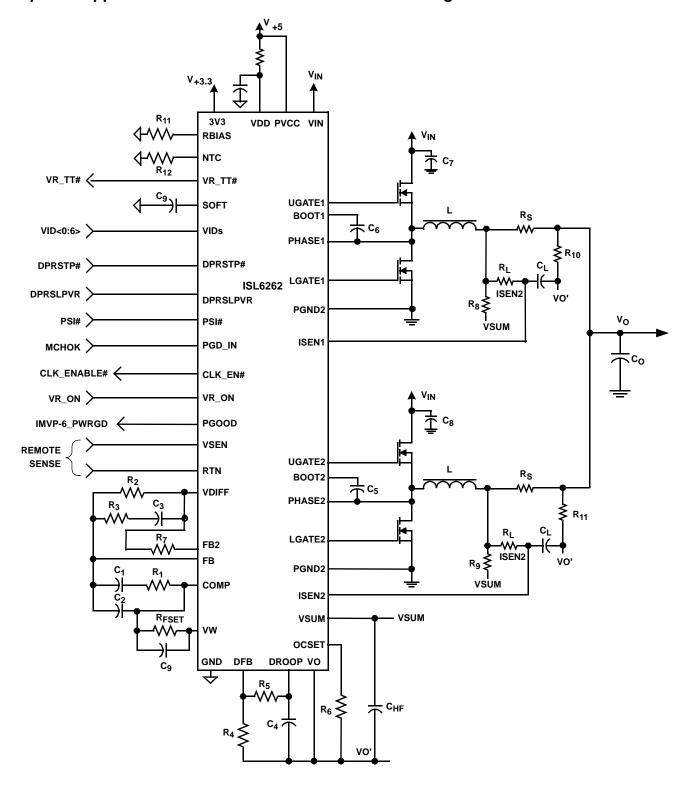

## Simplified Application Circuit for Resistive Current Sensing

FIGURE 27. ISL6262 BASED TWO-PHASE BUCK CONVERTER WITH RESISTIVE CURRENT SENSING

### Theory of Operation

The ISL6262 is a two-phase regulator implementing Intel® IMVP-6 protocol and includes embedded gate drivers for reduced system cost and board area. The regulator provides optimum steady-state and transient performance for microprocessor core applications up to 50A. System efficiency is enhanced by idling one phase at low-current and implementing automatic DCM-mode operation.

The heart of the ISL6262 is R³ Technology™, Intersil's Robust Ripple Regulator modulator. The R³ modulator combines the best features of fixed frequency PWM and hysteretic PWM while eliminating many of their shortcomings. The ISL6262 modulator internally synthesizes an analog of the inductor ripple current and uses hysteretic comparators on those signals to establish PWM pulse widths. Operating on these large-amplitude, noise-free synthesized signals allows the ISL6262 to achieve lower output ripple and lower phase jitter than either conventional hysteretic or fixed frequency PWM controllers. Unlike conventional hysteretic converters, the ISL6262 has an error amplifier that allows the controller to maintain a 0.5% voltage regulation accuracy throughout the VID range from 0.75V to 1.5V.

The hysteresis window voltage is relative to the error amplifier output such that load current transients results in increased switching frequency, which gives the R<sup>3</sup> regulator a faster response than conventional fixed frequency PWM controllers. Transient load current is inherently shared between active phases due to the use of a common hysteretic window voltage. Individual average phase voltages are monitored and controlled to equally share the static current among the active phases.

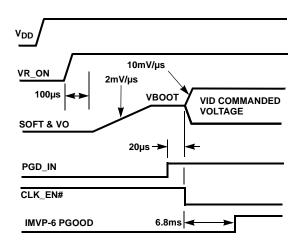

#### Start-Up Timing

With the controller's +5V VDD voltage above the POR threshold, the start-up sequence begins when VR ON exceeds the 3.3V logic HIGH threshold. Approximately 100µs later, SOFT and VOUT begin ramping to the boot voltage of 1.2V. At start-up, the regulator always operates in a 2-phase CCM mode, regardless of control signal assertion levels. During this internal, the SOFT cap is charged by 41µA current source. If the SOFT capacitor is selected to be 20nF, the SOFT ramp will be at 2mV/s for a soft-start time of 600µs. Once VOUT is within 10% of the boot voltage and PGD\_IN is HIGH for six PWM cycles (20µs for frequency = 300kHz), then CLK\_EN# is pulled LOW and the SOFT cap is charged/discharged by approximate 200µA. Therefore, VOUT slews at +10mV/s to the voltage set by the VID pins. Approximately 7ms later, PGOOD is asserted HIGH. Typical start-up timing is shown in Figure 28.

FIGURE 28. SOFT-START WAVEFORMS USING A 20nF SOFT CAPACITOR

#### PGD\_IN Latch

It should be noted that PGD\_IN going low will cause the converter to latch off. This state will be cleared when VR\_ON is toggled. This feature allows the converter to respond to other system voltage outages immediately.

#### Static Operation

After the start sequence, the output voltage will be regulated to the value set by the VID inputs per Table 1. The entire VID table is presented in the intel IMVP-6 specification. The ISL6262 will control the no-load output voltage to an accuracy of ±0.5% over the range of 0.75V to 1.5V.

TABLE 1. TRUNCATED VID TABLE FOR INTEL IMVP-6 SPECIFICATION

| VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOUT (V) |

|------|------|------|------|------|------|------|----------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1.5000   |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1.4875   |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.4375   |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1.2875   |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.15     |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0.8375   |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0.7625   |

| 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0.3000   |

| 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.0000   |

A fully-differential amplifier implements core voltage sensing for precise voltage control at the microprocessor die. The inputs to the amplifier are the VSEN and RTN pins.

As the load current increases from zero, the output voltage will droop from the VID table value by an amount proportional to current to achieve the IMVP-6 load line. The ISL6262 provides for current to be measured using either resistors in series with the channel inductors as shown in the application circuit of Figure 27, or using the intrinsic series

resistance of the inductors as shown in the application circuit of Figure 26. In both cases signals representing the inductor currents are summed at VSUM, which is the non-inverting input to the DROOP amplifier shown in the block diagram of Figure 1. The voltage at the DROOP pin minus the output voltage, VO´, is a high-bandwidth analog of the total inductor current. This voltage is used as an input to a differential amplifier to achieve the IMVP-6 load line, and also as the input to the overcurrent protection circuit.

When using inductor DCR current sensing, a single NTC element is used to compensate the positive temperature coefficient of the copper winding thus maintaining the load-line accuracy.

In addition to monitoring the total current (used for DROOP and overcurrent protection), the individual channel average currents are also monitored and used for balancing the load between channels. The IBAL circuit will adjust the channel pulse-widths up or down relative to the other channel to cause the voltages presented at the ISEN pins to be equal.

The ISL6262 controller can be configured for two-channel operation, with the channels operating 180 degrees apart. The channel PWM frequency is determined by the value of  $R_{\mbox{FSET}}$  connected to pin VW as shown in Figure 26 and Figure 27. Input and output ripple frequencies will be the channel PWM frequency multiplied by the number of active channels.

#### High Efficiency Operation Mode

The ISL6262 has several operating modes to optimize efficiency. The controller's operational modes are designed to work in conjunction with the Intel IMVP-6 control signals to maintain the optimal system configuration for all IMVP-6 conditions. These operating modes are established by the IMVP-6 control signal inputs such as PSI#, DPRSLPVR, and DPRSTP# as shown in Table 2. At high current levels, the system will operate with both phases fully active, responding rapidly to transients and deliver the maximum power to the load. At reduced load current levels, one of the phases may

be idled. This configuration will minimize switching losses, while still maintaining transient response capability. At the lowest current levels, the controller automatically configures the system to operate in single-phase automatic-DCM mode, thus achieving the highest possible efficiency. In this mode of operation, the lower FET will be configured to automatically detect and prevent discharge current flowing from the output capacitor through the inductors, and the switching frequency will be proportionately reduced, thus greatly reducing both conduction and switching losses.

Smooth mode transitions are facilitated by the R<sup>3</sup> Technology<sup>TM</sup>, which correctly maintains the internally synthesized ripple currents throughout mode transitions. The controller is thus able to deliver the appropriate current to the load throughout mode transitions. The controller contains embedded mode-transition algorithms which robustly maintain voltage-regulation for all control signal input sequences and durations.

Mode-transition sequences will often occur in concert with VID changes; therefore the timing of the mode transitions of ISL6262 has been carefully designed to work in concert with VID changes. For example, transitions into single-phase mode will be delayed until the VID induced voltage ramp is complete, to allow the associated output capacitor charging current is shared by both inductor paths. While in single-phase automatic-DCM mode, VID changes will initiate an immediate return to two-phase CCM mode. This ensures that both inductor paths share the output capacitor charging current and are fully active for the subsequent load current increases.

The controller contains internal counters which prevent spurious control signal glitches from resulting in unwanted mode transitions. Control signals of less than two switching periods do not result in phase-idling. Signals of less than 7 switching periods do not result in implementation of automatic-DCM mode.

TABLE 2. CONTROL SIGNAL TRUTH TABLES FOR OPERATION MODES OF ISL6262

|                 | DPRSLPVR | DPRSTP# | PSI# | PHASE OPERATION MODES   | EXPECTED CPU MODE |

|-----------------|----------|---------|------|-------------------------|-------------------|

| Intel IMVP-6    | 0        | 1       | 1    | 2-phase CCM             | active mode       |

| COMPLIANT LOGIC | 0        | 1       | 0    | 1-phase CCM             | active mode       |

|                 | 1        | 0       | 1    | 1-phase diode emulation | deeper sleep mode |

|                 | 1        | 0       | 0    | 1-phase diode emulation | deeper sleep mode |

| OTHER LOGIC     | 0        | 0       | 1    | 2-phase CCM             |                   |

| COMMANDS        | 0        | 0       | 0    | 1-phase CCM             |                   |

|                 | 1        | 1       | 1    | 2-phase CCM             |                   |

|                 | 1        | 1       | 0    | 1-phase CCM             |                   |

16

While transitioning to single-phase operation, the controller smoothly transitions current from the idling-phase to the active-phase, and detects the idling-phase zero-current condition. During transitions into automatic-DCM or forced-CCM mode, the timing is carefully adjusted to eliminate output voltage excursions. When a phase is added, the current balance between phases is quickly restored.

While PSI# is high, both phases are switching. If PSI# is asserted low and either DPRSTP# or DPRSLPVR are not asserted, the controller will transition to CCM operation with only phase 1 switching, and both FET's of phase 2 will be off. The controller will thus eliminate switching losses associated with the unneeded channel.

When PSI#, DPRSTP#, and DPRSLPVR are all asserted, the controller will transition to single-phase DCM mode. In this mode, both FET's associated with phase 2 will be off,

**DPRSLPVR'S EFFECT ON EXIT SLEW RATE**

and the ISL6262 will turn-off the lower FET of channel 1 whenever the channel 1 current decays to zero. As load is further reduced, the phase 1 channel switching frequency will decrease, thus maintaining high efficiency.

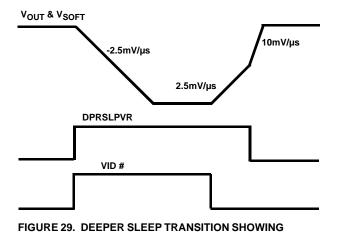

#### **Dynamic Operation**

Refer to Figure 29, the ISL6262 responds to changes in VID command voltage by slewing to new voltages with a dV/dt set by the SOFT capacitor and by the state of DPRSLPVR. With C<sub>SOFT</sub> = 15nF and DPRSLPVR HIGH, the output voltage will move at ±2.8mV/s for large changes in voltage. For DPRSLPVR LOW, the large signal dV/dt will be ±13mV/s. As the output voltage approaches the VID command value, the dV/dt moderates to prevent overshoot.

Keeping DPRSLPVR HIGH for voltage transitions into and out of Deeper Sleep will result in low dV/dt output voltage changes with resulting minimized audio noise. For fastest recovery from Deeper Sleep to Active mode, holding DPRSLPVR LOW will result in maximum dV/dt. Therefore, the ISL6262 is IMVP-6 compliant for DPRSTP# and DPRSLPVR logic.

Intersil's R<sup>3</sup> Technology™ has intrinsic voltage feedforward. As a result, high-speed input voltage steps do not result in significant output voltage perturbations. In response to load current step increases, the ISL6262 will transiently raise the switching frequency so that response time is decreased and current is shared by two channels.

#### **Protection**

The ISL6262 provides overcurrent, overvoltage, undervoltage protection and over-temperature protection as shown in Table 3.

**TABLE 3. FAULT-PROTECTION SUMMARY OF ISL6262**

|                                        | FAULT DURATION PRIOR<br>TO PROTECTION | PROTECTION ACTIONS                                                                                    | FAULT RESET                |

|----------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|

| Overcurrent fault                      | 120µs                                 | PWM1, PWM2 three-state,<br>PGOOD latched low                                                          | VR_ON toggle or VDD toggle |

| Way-Overcurrent fault                  | <2μs                                  | PWM1, PWM2 three-state,<br>PGOOD latched low                                                          | VR_ON toggle or VDD toggle |

| Overvoltage fault (1.7V)               | Immediately                           | Low-side FET on until Vcore<br><0.85V, then PWM three-state,<br>PGOOD latched low (OV-1.7V<br>always) | VDD toggle                 |

| Overvoltage fault (+200mV)             | 1ms                                   | PWM1, PWM2 three-state,<br>PGOOD latched low                                                          | VR_ON toggle or VDD toggle |

| Undervoltage fault<br>(-300mV)         | 1ms                                   | PWM1, PWM2 three-state,<br>PGOOD latched low                                                          | VR_ON toggle or VDD toggle |

| Unbalance fault<br>(7.5mV)             | 1ms                                   | PWM1, PWM2 three-state,<br>PGOOD latched low                                                          | VR_ON toggle or VDD toggle |

| Over-temperature<br>fault (NTC <1.18V) | Immediately                           | VR_TT# goes low                                                                                       | N/A                        |

Overcurrent protection is tied to the voltage droop which is determined by the resistors selected as described in the "Component Selection and Application" section. After the load-line is set, the OCSET resistor can be selected to detect overcurrent at any level of droop voltage. An overcurrent fault will occur when the load current exceeds the overcurrent setpoint voltage while the regulator is in a 2-phase mode. While the regulator is in a 1-phase mode of operation, the overcurrent setpoint is automatically reduced by half. For overcurrents less than twice the OCSET level, the over-load condition must exist for 120µs in order to trip the OC fault latch. This is shown in Figure 24.

For over-loads exceeding twice the set level, the PWM outputs will immediately shut off and PGOOD will go low to maximize protection due to hard shorts.

In addition, excessive phase unbalance, for example, due to gate driver failure, will be detected in two-phase operation and the controller will be shut-down after one millisecond's detection of the excessive phase current unbalance. The phase unbalance is detected by the voltage on the ISEN pins if the difference is greater than 7.5mV.

Undervoltage protection is independent of the overcurrent limit. If the output voltage is less than the VID set value by 300mV or more, a fault will latch after one millisecond in that condition. The PWM outputs will turn off and PGOOD will go low. Note that most practical core regulators will have the overcurrent set to trip before the -300mV undervoltage limit.

There are two levels of overvoltage protection and response. For output voltage exceeding the set value by +200mV for one millisecond, a fault is declared. All of the above faults have the same action taken: PGOOD is latched low and the upper and lower power FETs are turned off so that inductor current will decay through the FET body diodes. This condition can be reset by bringing VR\_ON low or by bringing VDD below 4V. When these inputs are returned to their high operating levels, a soft-start will occur.

Refer to Figure 25, the second level of overvoltage protection behaves differently. If the output exceeds 1.7V, an OV fault is immediately declared, PGOOD is latched low and the low-side FETs are turned on. The low-side FETs will remain on until the output voltage is pulled down below about 0.85V at which time all FETs are turned off. If the output again rises above 1.7V, the protection process is repeated. This offers the maximum amount of protection against a shorted high-side FET while preventing output ringing below ground. The 1.7V OV is not reset with VR\_ON, but requires that VDD be lowered to reset. The 1.7V OV detector is active at all times that the controller is enabled including after one of the other faults occurs so that the processor is protected against high-side FET leakage while the FETs are commanded off.

The ISL6262 has a thermal throttling feature. If the voltage on the NTC pin goes below the 1.18V over-temperature

threshold, the VR\_TT# pin is pulled low indicating the need for thermal throttling to the system oversight processor. No other action is taken within the ISL6262 in response to NTC pin voltage.

### **Component Selection and Application**

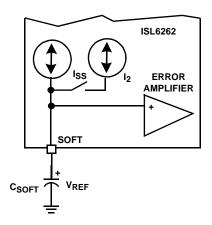

#### Soft-Start and Mode Change Slew Rates

The ISL6262 uses 2 slew rates for various modes of operation. The first is a slow slew rate, used to reduce inrush current during start-up. It is also used to reduce audible noise when entering or exiting Deeper Sleep Mode. A faster slew rate is used to exit out of Deeper Sleep and to enhance system performance by achieving active mode regulation more quickly. Note that the SOFT cap current is bidirectional. The current is flowing into the SOFT capacitor when the output voltage is commanded to rise, and out of the SOFT capacitor when the output voltage is commanded to fall.

Refer to Figure 30. The two slew rates are determined by commanding one of two current sources onto the SOFT pin. As can be seen in Figure 30, the SOFT pin has a capacitance to ground. Also, the SOFT pin is the input to the error amplifier and is, therefore, the commanded system voltage. Depending on the state of the system, i.e. Start-Up or Active mode, and the state of the DPRSLPVR pin, one of the two currents shown in Figure 30 will be used to charge or discharge this capacitor, thereby controlling the slew rate of the commanded voltage. These currents can be found under the SOFT-START CURRENT section of the Electrical Specification Table.

FIGURE 30. SOFT PIN CURRENT SOURCES FOR FAST AND SLOW SLEW RATES

The first current, labelled  $I_{SS}$ , is given in the Specification Table as 41µA. This current is used during soft-start. The second current,  $I_2$  sums with  $I_{SS}$  to get the larger of the two currents, labeled  $I_{GV}$  in the Electrical Specification Table. This total current is typically 200µA with a minimum of 175µA.

The IMVP-6 specification reveals the critical timing associated with regulating the output voltage. The symbol,

SLEWRATE, as given in the IMVP-6 specification will determine the choice of the SOFT capacitor,  $C_{SOFT}$ , by the following equation:

$$C_{SOFT} = \frac{I_{GV}}{SLEWRATE}$$

(EQ. 1)

Using a SLEWRATE of 10mV/ $\mu$ s, and the typical I $_{GV}$  value, given in the Electrical Specification Table of 200 $\mu$ A, C $_{SOFT}$  is

$$C_{SOFT} = 200 \mu A / (10 \text{mV} / 1 \mu \text{s})$$

(EQ. 2)

A choice of  $0.015\mu F$  would guarantee a SLEWRATE of  $10mV/\mu s$  is met for minimum  $I_{GV}$  value, given in the Electrical Specification Table. This choice of  $C_{SOFT}$  will then control the Start-Up slewrate as well. One should expect the output voltage to slew to the Boot value of 1.2V at a rate given by the following equation:

$$\frac{dV}{dt} = \frac{I_{SS}}{C_{SOFT}} = \frac{41 \mu A}{0.015 \mu F} = 2.8 \text{mV}/\mu \text{s}$$

(EQ. 3)

#### Selecting RBIAS

To properly bias the ISL6262, a reference current is established by placing a 147k $\Omega$ , 1% tolerance resistor from the RBIAS pin to ground. This will provide a highly accurate, 10 $\mu$ A current source from which OCSET reference current can be derived.

Care should be taken in layout that the resistor is placed very close to the RBIAS pin and that a good quality signal ground is connected to the opposite side of the RBIAS resistor. Do not connect any other components to this pin as this would negatively impact performance. Capacitance on this pin would create instabilities and should be avoided.

#### Start-Up Operation - CLK\_EN# and PGOOD

The ISL6262 provides a 3.3V logic output pin for CLK\_EN#. The 3V3 pin allows for a system 3.3V source to be connected to separated circuitry inside the ISL6262, solely devoted to the CLK\_EN# function. The output is a 3.3V CMOS signal with 4mA sourcing and sinking capability. This implementation removes the need for an external pull-up resistor on this pin, and due to the normal level of this signal being a low, removes the leakage path from the 3.3V supply to ground through the pull-up resistor. This reduces 3.3V supply current, that would occur under normal operation with a pull-up resistor, and prolongs battery life. The 3.3V supply should be decoupled to digital ground, not to analog ground for noise immunity.

As mentioned in the "Theory of Operation" section of this datasheet, CLK\_EN# is logic level high at start-up until 20µs after the system Vccp and Vcc\_mch supplies are within regulation, and the Vcc-core is in regulation at the Boot level. Approximately 20µs after these voltages are within regulation, as indicated by PGD\_IN going high, CLK\_EN# goes low, triggering an internal timer for the

19

IMVP-6\_PWRGD signal. This timer allows IMVP-6\_PWRGD to go high approximately 6.8ms after CLK\_EN# goes low.

#### Static Mode of Operation - Processor Die Sensing

Die sensing is the ability of the controller to regulate the core output voltage at a remotely sensed point. This allows the voltage regulator to compensate for various resistive drops in the power path and ensure that the voltage seen at the CPU die is the correct level independent of load current.

The VSEN and RTN pins of the ISL6262 are connected to Kelvin sense leads at the die of the processor through the processor socket. These signal names are Vcc\_sense and Vss\_sense respectively. This allows the voltage regulator to tightly control the processor voltage at the die, independent of layout inconsistencies and voltage drops. This Kelvin sense technique provides for extremely tight load line regulation.

These traces should be laid out as noise sensitive traces. For optimum load line regulation performance, the traces connecting these two pins to the Kelvin sense leads of the processor must be laid out away from rapidly rising voltage nodes, (switching nodes) and other noisy traces. To achieve optimum performance, place common mode and differential mode RC filters to analog ground on VSEN and RTN as shown in Figure 31. The filter resistors should be  $10\Omega$  so that they do not interact with the  $50k\Omega$  input resistance of the differential amplifier. The filter resistor may be inserted between Vcc\_sense and VSEN pin. Another option is to place to the filter resistor between Vcc\_sense and VSEN pin and between Vss\_sense and RTN pin. Whether to need these RC filter really depends on the actual board layout and noise environment.

Due to the fact that the voltage feedback to the switching regulator is sensed at the processor die, there exists the potential of an overvoltage due to an open circuited feedback signal, should the regulator be operated without the processor installed. Due to this fact, we recommend the use of the Ropn1 and Ropn2 connected to Vout and ground as shown in Figure 31. These resistors will provide voltage feedback in the event that the system is powered up without a processor installed. These resistors may typically range from 20 to  $100\Omega$ .

FIGURE 31. SIMPLIFIED SCHEMATIC FOR DROOP AND DIE SENSING WITH INDUCTOR DCR CURRENT SENSING

#### Setting the Switching Frequency - FSET

The R<sup>3</sup> modulator scheme is not a fixed frequency PWM architecture. The switching frequency can increase during the application of a load to improve transient performance.

It also varies slightly due changes in input and output voltage and output current, but this variation is normally less than 10% in continuous conduction mode.

Refer to Figure 26, the resistor connected between the VW and COMP pins of the ISL6262 adjusts the switching window, and therefore adjusts the switching frequency. The RFSET resistor that sets up the switching frequency of the converter operating in CCM can be determined using the following relationship, where  $R_{\mbox{\scriptsize FSET}}$  is in  $k\Omega$  and the switching period is in  $\mu s$ . Place a 47pF capacitor in parallel with the frequency set resistor for better noise immunity.

$$R_{\text{FSFT}}(k\Omega) \cong (\text{period}(\mu s) - 0.5) \bullet 1.56$$

(EQ. 4)

In discontinuous conduction mode (DCM), the ISL6262 runs in period stretching mode. The switching frequency is dependent on the load current level. In general, the lighter load, the slower switching frequency. Therefore, the switching loss is much reduced for the light load operation, which is important for conserving the battery power in the portable application.

#### Voltage Regulator Thermal Throttling

Intel® IMVP-6 technology supports thermal throttling of the processor to prevent catastrophic thermal damage to the voltage regulator. The ISL6262 features a thermal monitor

which senses the voltage change across an externally placed negative temperature coefficient (NTC) thermistor.

Proper selection and placement of the NTC thermistor allows for detection of a designated temperature rise by the system.

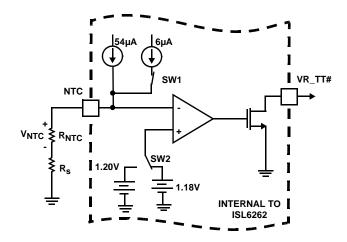

Figure 32 shows the thermal throttling feature with hysteresis. At low temperature, SW1 is on and SW2 connects to the 1.18V side. The total current going into NTC pin is 60µA. The voltage on NTC pin is higher than threshold voltage of 1.18V and the comparator output is low. VR\_TT# is pulling up high by the external resistor.

FIGURE 32. CIRCUITRY ASSOCIATED WITH THE THERMAL THROTTLING FEATURE IN ISL6262

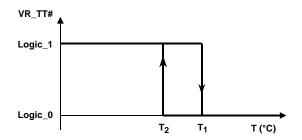

When temperature increases, the NTC resistor value on NTC pin decreases. Thus, the voltage on NTC pin decreases to a level lower than 1.18V. The comparator output changes polarity and turns SW1 off and connects SW2 to 1.20V. This pulls VR\_TT# low and sends the signal to start thermal throttle. There is a 6µA current reduction on NTC pin and 20mV voltage increase on threshold voltage of the comparator in this state. The VR\_TT# signal will be used to change the CPU operation and decrease the power consumption. When the temperature goes down, the NTC thermistor voltage will eventually go up. The NTC pin voltage increases to 1.20V, the comparator output will then be able to flip back. Such a temperature hysteresis feature of VR\_TT# is illustrated in Figure 33. T<sub>1</sub> represents the higher temperature point at which the VR\_TT# goes from low to high due to the system temperature rise. T<sub>2</sub> represents the lower temperature point at which the VR\_TT# goes high from low because the system temperature decreases to the normal level.

FIGURE 33. TEMPERATURE HYSTERESIS OF VR\_TT#

Usually, the NTC thermistor's resistance can be approximated by the following formula:

$$R_{NTC}(T) = R_{NTCTo} \cdot e^{b} \cdot \left(\frac{1}{T + 273} - \frac{1}{To + 273}\right)$$

(EQ. 5)

T is the temperature of the NTC thermistor and b is a parameter constant depending on the thermistor material.  $T_0$  is the reference temperature in which the approximation is derived. Most common temperature for  $T_0$  is 25°C. For example, there are commercial NTC thermistor products with b = 2750k, b = 2600k, b = 4500k or b = 4250k.

From the operation principle of the VR\_TT# circuit explained, the NTC resistor satisfies the following equation group.

$$R_{NTC}(T_1) + R_S = \frac{1.18 V}{60 \mu A} = 19.67 k\Omega$$

(EQ. 6)

$$R_{NTC}(T_2) + R_S = \frac{1.2V}{54 \text{ µA}} = 22.22 \text{k}\Omega$$

(EQ. 7)

From Equation 6 and Equation 7, the following can be derived,

$$R_{NTC}(T_2) - R_{NTC}(T_1) = 2.55k\Omega$$

(EQ. 8)

Using Equation 5 into Equation 8, the required nominal NTC resistor value can be obtained by:

$$R_{\text{NTCTo}} = \frac{2.55 \text{k}\Omega \bullet \text{e}}{b \bullet \left(\frac{1}{T_0 + 273}\right)} \\ e^{\frac{2.55 \text{k}\Omega \bullet \text{e}}{b \bullet \left(\frac{1}{T_2 + 273}\right)} b \bullet \left(\frac{1}{T_1 + 273}\right)}$$

(EQ. 9)

For some cases, the constant b is not accurate enough to approximate the NTC resistor value, the manufacturer provides the resistor ratio information at different temperature. The nominal NTC resistor value may be expressed in another way as follows:

$$R_{\text{NTCTo}} = \frac{2.55 \text{k}\Omega}{\Lambda - \Lambda R_{\text{NTC-T}_2} - R_{\text{NTC-T}_1}}$$

(EQ. 10)

where  $\overset{\Lambda}{R}_{NTC-T}$  is the normalized NTC resistance to its nominal value. Most datasheet of the NTC thermistor gives the normalized resistor value based on its value at 25°C.

Once the NTC thermistor resistor is determined, the series resistor can be derived by:

$$R_S = \frac{1.18V}{60\mu A} - R_{NTC}(T1) = 19.67k\Omega - R_{NTC_{-}T_{1}}$$

(EQ. 11)

Once  $R_{NTCTo}$  and  $R_{s}$  is designed, the actual NTC resistance at  $T_{2}$  and the actual  $T_{2}$  temperature can be found in:

$$R_{NTC_{-}T_{2}} = 2.55k\Omega + R_{NTC_{-}T_{1}}$$

(EQ. 12)

$$T_{2\_actual} = \frac{1}{\frac{1}{b} \ln \left( \frac{R_{NTC\_T_2}}{R_{NTC\_T_2}} \right) + 1/(273 + To)} - 273$$

(EQ. 13)

One example of using Equations 9, 10 and 11 to design a thermal throttling circuit with the temperature hysteresis  $100^{\circ}$ C to  $105^{\circ}$ C is illustrated as follows. Since  $T_1 = 105^{\circ}$ C and  $T_2 = 100^{\circ}$ C, if we use a Panasonic NTC with B = 4700, the Equation 9 gives the required NTC nominal resistance as

$$R_{NTC, To} = 396k\Omega$$

In fact, the datasheet gives the resistor ratio value at  $100^{\circ}$ C to  $105^{\circ}$ C, which is 0.03956 and 0.03322 respectively. The b value 4700K in Panasonic datasheet only covers to  $85^{\circ}$ C. Therefore, using Equation 10 is more accurate for  $100^{\circ}$ C design, the required NTC nominal resistance at  $25^{\circ}$ C is 402k $\Omega$ . The closest NTC resistor value from manufacturer is 470k $\Omega$ . So the series resistance is given by Equation 11 as follows

$$R_S = 19.67 k\Omega - R_{NTC \ 105^{\circ}C} = 19.67 k\Omega - 15.65 k\Omega = 4.067 k\Omega$$

Furthermore, the NTC resistance at T2 is given by Equation 12.

$$R_{NTC,T2} = 2.55k\Omega + R_{NTC,T1} = 18.16k\Omega$$

From the NTC datasheet, it can be concluded that the actual temperature  $T_2$  is about 97°C. If using the Equation 13,  $T_2$  is calculated to be 97.7°C. Check the NTC datasheet to decide

in<u>ter</u>sil

whether Equation 9 or Equation 10 can accurately represent the NTC resistor value at the designed temperature range.

Therefore, the NTC branch is designed to have a 470k NTC and 4.02k resistor in series. The part number of the NTC thermistor is ERTJ0EV474J. It is a 0402 package. The NTC thermistor should be placed in the spot which gives the best indication of the temperature of voltage regulator circuit. The actual hysteresis temperature is about 105°C and 97°C.

# Static Mode of Operation - Static Droop Using DCR Sensing

As previously mentioned, the ISL6262 has an internal differential amplifier which provides for very accurate voltage regulation at the die of the processor. The load line regulation is also accurate for both two-phase and single-phase operation. The process of selecting the components for the appropriate load line droop is explained here.

For DCR sensing, the process of compensation for DCR resistance variation to achieve the desired load line droop has several steps and is somewhat iterative.

The two-phase solution using DCR sensing is shown in Figure 31. There are two resistors connecting to the terminals of inductor of each phase. These are labeled RS and RO. These resistors are used to obtain the DC voltage drop across each inductor. Each inductor will have a certain level of DC current flowing through it, and this current when multiplied by the DCR of the inductor creates a small DC voltage drop across the inductor terminal. When this voltage is summed with the other channels DC voltages, the total DC load current can be derived.

RO is typically 1 to  $10\Omega$ . This resistor is used to tie the outputs of all channels together and thus create a summed average of the local CORE voltage output. RS is determined

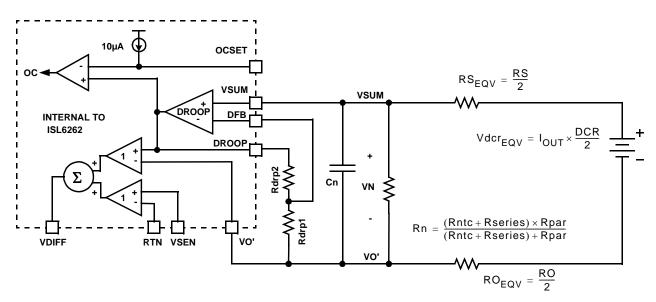

through an understanding of both the DC and transient load currents. This value will be covered in the next section. However, it is important to keep in mind that the output of each of these RS resistors are tied together to create the VSUM voltage node. With both the outputs of RO and RS tied together, the simplified model for the droop circuit can be derived. This is presented in Figure 34.

Figure 34 shows the simplified model of the droop circuitry. Essentially one resistor can replace the RO resistors of each phase and one RS resistor can replace the RS resistors of each phase. The total DCR drop due to load current can be replaced by a DC source, the value of which is given by:

$$V_{DCR\_EQU} = \frac{I_{OUT} \bullet DCR}{2}$$

(EQ. 14)

For the convenience of analysis, the NTC network comprised of Rntc, Rseries and Rpar, given in Figure 31, is labelled as a single resistor Rn in Figure 34.

The first step in droop load line compensation is to adjust Rn,  $RO_{EQV}$  and  $RS_{EQV}$  such that sufficient droop voltage exists even at light loads between the VSUM and VO' nodes. As a rule of thumb we start with the voltage drop across the Rn network, VN, to be 0.5-0.8 times  $V_{DCR\_EQU}$ . This ratio provides for a fairly reasonable amount of light load signal from which to arrive at droop.

The resultant NTC network resistor value is dependent on the temperature and given by

$$R_{n}(T) = \frac{(R_{series} + R_{ntc}) \bullet R_{par}}{R_{series} + R_{ntc} + R_{par}}$$

(EQ. 15)

For simplicity, the gain of Vn to the V<sub>dcr\_equ</sub> is defined by G1, also dependent on the temperature of the NTC thermistor.

FIGURE 34. EQUIVALENT MODEL FOR DROOP AND DIE SENSING USING DCR SENSING

$$G_1(T) \stackrel{\Delta}{=} \frac{R_n(T)}{R_n(T) + RS_{FQV}}$$

(EQ. 16)

$$DCR(T) = DCR_{25^{\circ}C} \bullet (1 + 0.00393*(T-25))$$

(EQ. 17)

Therefore, the output of the droop amplifier divided by the total load current can be expressed as follows.

$$R_{droop} = G_1(T) \bullet \frac{DCR_{25}}{2} \bullet (1 + 0.00393*(T-25)) \bullet k_{droopamp}$$

(EQ. 18)

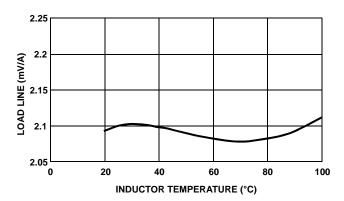

where  $R_{droop}$  is the realized load line slope and 0.00393 is the temperature coefficient of the copper. To achieve the droop value independent from the temperature of the inductor, it is equivalently expressed by the following.

$$G_1(T) \bullet (1 + 0.00393*(T-25)) \cong G_{1target}$$

(EQ. 19)

The non-inverting droop amplifier circuit has the gain  $K_{\text{droopamp}}$  expressed as:

$$k_{droopamp} \, = \, 1 + \frac{R_{drp2}}{R_{drp1}}$$

G<sub>1target</sub> is the desired gain of Vn over I<sub>OUT</sub> • DCR/2. Therefore, the temperature characteristics of gain of Vn is described by:

$$G_{1}(T) = \frac{G_{1target}}{(1 + 0.00393*(T-25))}$$

(EQ. 20)

For the  $G_{1target}=0.76$ , the Rntc =  $10k\Omega$  with b = 4300, Rseries =  $2610k\Omega$ , and Rpar =  $11k\Omega$ , RS<sub>EQV</sub> =  $1825\Omega$  generates a desired G1, close to the feature specified in Equation 20. The actual G1 at 25°C is 0.763. For different G1 and NTC thermistor preference, the design file to generate the proper value of Rntc, Rseries, Rpar, and RS<sub>EQV</sub> is provided by Intersil.

Then, the individual resistors from each phase to the VSUM node, labeled RS1 and RS2 in Figure 31, are then given by the following equation.

$$Rs = 2 \cdot RS_{EQV}$$

(EQ. 21)

So, Rs =  $3650\Omega$ . Once we know the attenuation of the RS and RN network, we can then determine the droop amplifier gain required to achieve the load line. Setting Rdrp1 =  $1k_1\%$ , then Rdrp2 is can be found using equation

$$Rdrp2 = \left(\frac{2 \cdot R_{droop}}{DCR \cdot G1(25^{\circ}C)} - 1\right) \cdot R_{drp1}$$

(EQ. 22)

Droop Impedance (Rdroop) = 0.0021 (V/A) as per the Intel IMVP-6 specification, DCR = 0.0008 $\Omega$  typical for a 0.36 $\mu$ H inductor, Rdrp1 = 1k $\Omega$  and the attenuation gain (G1) = 0.77, Rdrp2 is then given by

$$Rdrp2 = \left(\frac{2 \bullet R_{droop}}{0.0008 \bullet 0.763} - 1\right) \bullet 1k\Omega \approx 5.82k\Omega$$

Note, we choose to ignore the RO resistors because they do not add significant error.

These designed values in Rn network are very sensitive to layout and coupling factor of the NTC to the inductor. As only one NTC is required in this application, this NTC should be placed as close to the Channel 1 inductor as possible and PCB traces sensing the inductor voltage should be go directly to the inductor pads.

Once the board has been laid out, some adjustments may be required to adjust the full load droop voltage. This is fairly easy and can be accomplished by allowing the system to achieve thermal equilibrium at full load, and then adjusting Rdrp2 to obtain the appropriate load line slope.

To see whether the NTC has compensated the temperature change of the DCR, the user can apply full load current and wait for the thermal steady state and see how much the output voltage will deviate from the initial voltage reading. A good compensation can limit the drift to 2mV. If the output voltage is decreasing with temperature increase, that ratio between the NTC thermistor value and the rest of the resistor divider network has to be increased. The user should follow the evaluation board value and layout of NTC as much as possible to minimize engineering time.

The 2.1mV/A load line should be adjusted by Rdrp2 based on maximum current, not based on small current steps like 10A, as the droop gain might vary between each 10A steps. Basically, if the max current is 40A, the required droop voltage is 84mV. The user should have 40A load current on and look for 84mV droop. If the drop voltage is less than 84mV, for example, 80mV. The new value will be calculated by:

$$Rdrp2\_new = \frac{84mV}{80mV}(Rdrp1 + Rdrp2) - Rdrp1$$

For the best accuracy, the effective resistance on the DFB and VSUM pins should be identical so that the bias current of the droop amplifier does not cause an offset voltage. In the example above, the resistance on the DFB pin is Rdrp1 in parallel with Rdrop2, that is, 1K in parallel with 5.82K or 853 $\Omega$ . The resistance on the VSUM pin is Rn in parallel with RSEQV or 5.87K in parallel with 1.825K or 1392 $\Omega$ . The mismatch in the effective resistances is 1392 - 853 = 539 $\Omega$ . Do not let the mismatch get larger than  $600\Omega$ . To reduce the mismatch, multiply both Rdrp1 and Rdrp2 by the appropriate factor. The appropriate factor in the example is 1392/853 = 1.632. In summary, the predicted load line with the designed droop network parameters based on the Intersil design tool is shown in Figure 35.

FIGURE 35. LOAD LINE PERFORMANCE WITH NTC THERMAL COMPENSATION

# Dynamic Mode of Operation - Dynamic Droop Using DCR Sensing

Droop is very important for load transient performance. If the system is not compensated correctly, the output voltage could sag excessively upon load application and potentially create a system failure. The output voltage could also take a long period of time to settle to its final value. This could be problematic if a load dump were to occur during this time. This situation would cause the output voltage to rise above the no load setpoint of the converter and could potentially damage the CPU.

The L/DCR time constant of the inductor must be matched to the Rn\*Cn time constant as shown in the following equation:

$$\frac{L}{DCR} = \frac{R_n \bullet RS_{EQV}}{R_n + RS_{EQV}} \bullet C_n$$

(EQ. 23)

Solving for Cn we now have the following equation:

$$C_{n} = \frac{\frac{L}{DCR}}{\frac{R_{n} \cdot RS_{EQV}}{R_{n} + RS_{FQV}}}$$

(EQ. 24)

Note, RO was neglected. As long as the inductor time constant matches the Cn, Rn and Rs time constants as given above, the transient performance will be optimum. As in the static droop case, this process may require a slight adjustment to correct for layout inconsistencies. For the example of L =  $0.36\mu H$  with  $0.8m\Omega$  DCR, Cn is calculated below.

$$C_{n} = \frac{\frac{0.36 \mu H}{0.0008}}{\text{parallel}(5.87 \text{K}, 1.825 \text{K})} \approx 330 \text{nF} \tag{EQ. 25}$$

The value of this capacitor is selected to be 330nF. As the inductors tend to have 20% to 30% tolerances, this cap generally will be tuned on the board by examining the transient voltage. If the output voltage transient has an initial dip, lower than the voltage required by the load line, and slowly increases back to the steady state, the cap is too small and vice versa. It is better to have the cap value a little

24

bigger to cover the tolerance of the inductor to prevent the output voltage from going lower than the spec. This cap needs to be a high grade cap like X7R with low tolerance. There is another consideration in order to achieve better time constant match mentioned above. The NPO/COG (class-I) capacitors have only 5% tolerance and a very good thermal characteristics. But those caps are only available in small capacitance values. In order to use such capacitors, the resistors and thermistors surrounding the droop voltage sensing and droop amplifier has to be resized up to 10X to reduce the capacitance by 10X. But attention has to be paid in balancing the impedance of droop amplifier in this case.

## Dynamic Mode of Operation - Compensation Parameters

Considering the voltage regulator as a black box with a voltage source controlled by VID and a series impedance, in order to achieve the 2.1mV/A load line, the impedance needs to be  $2.1m\Omega$ . The compensation design has to target the output impedance of the converter to be  $2.1m\Omega$ . There is a mathematical calculation file available to the user. The power stage parameters such as L and Cs are needed as the input to calculate the compensation component values. Attention has to be paid to the input resistor to the FB pin. Too high of a resistor will cause an error to the output voltage regulation because of bias current flowing in the FB pin. It is better to keep this resistor below 3K when using this file.

# Static Mode of Operation - Current Balance Using DCR or Discrete Resistor Current Sensing

Current Balance is achieved in the ISL6262 through the matching of the voltages present on the ISEN pins. The ISL6262 adjusts the duty cycles of each phase to maintain equal potentials on the ISEN pins. RL and CL around each inductor, or around each discrete current resistor, are used to create a rather large time constant such that the ISEN voltages have minimal ripple voltage and represent the DC current flowing through each channel's inductor. For optimum performance, RL is chosen to be  $10 \text{k}\Omega$  and CL is selected to be  $0.22 \mu\text{F}$ . When discrete resistor sensing is used, a capacitor most likely needs to be placed in parallel with RL to properly compensate the current balance circuit.

ISL6262 uses RC filter to sense the average voltage on phase node and forces the average voltage on the phase node to be equal for current balance. Even though the ISL6262 forces the ISEN voltages to be almost equal, the inductor currents will not be exactly equal. Take DCR current sensing as example, two errors have to be added to find the total current imbalance. 1) Mismatch of DCR: If the DCR has a 5% tolerance then the resistors could mismatch by 10% worst case. If each phase is carrying 20A then the phase currents mismatch by 20A\*10% = 2A. 2) Mismatch of phase voltages/offset voltage of ISEN pins. The phase voltages are within 2mV of each other by current balance circuit. The error current that results is given by 2mV/DCR. If DCR =  $1m\Omega$  then the error is 2A.

In the above example, the two errors add to 4A. For the two phase DC/DC, the currents would be 22A in one phase and 18A in the other phase. In the above analysis, the current balance can be calculated with 2A/20A = 10%. This is the worst case calculation, for example, the actual tolerance of two 10% DCRs is 10%\*sqrt(2) = 7%.

There are provisions to correct the current imbalance due to layout or to purposely divert current to certain phase for better thermal management. Customer can put a resistor in parallel with the current sensing capacitor on the phase of interest in order to purposely increase the current in that phase.

In the case the pc board trace resistance from the inductor to the microprocessor are not the same on two phases, the current will not be balanced. On the phase that have too much trace resistance a resistor can be added in parallel with the ISEN capacitor that will correct for the poor layout.

An estimate of the value of the resistor is:

Rtweak = Risen \* Rdcr/(Rtrace-Rmin)

where Risen is the resistance from the phase node to the ISEN pin; usually  $10k\Omega$ . Rdcr is the DCR resistance of the inductor. Rtrace is the trace resistance from the inductor to the microprocessor on the phase that needs to be tweaked. It should be measured with a good microOhm meter. Rmin is the trace resistance from the inductor to the microprocessor on the phase with the least resistance.

For example, if the pc board trace on one phase is  $0.5m\Omega$ and on another trace is  $0.3m\Omega$ ; and if the DCR is  $1.2m\Omega$ ; then the tweaking resistor is

Rtweak =  $10k\Omega * 1.2/(0.5 - 0.3) = 60k\Omega$ .

When choosing current sense resistor, not only the tolerance of the resistance is important, but also the TCR. And its combined tolerance at a wide temperature range should be calculated.

#### Droop Using Discrete Resistor Sensing - Static/ Dynamic Mode of Operation

Figure 36 shows the equivalent circuit of a discrete current sense approach. Figure 27 shows a more detailed schematic of this approach. Droop is solved the same way as the DCR sensing approach with a few slight modifications.

First, there is no NTC required for thermal compensation, therefore, the Rn resistor network in the previous section is not required. Secondly, there is no time constant matching required, therefore, the Cn component is not matched to the L/DCR time constant. This component does indeed provide noise immunity and therefore is populated with a 39pF capacitor.

The RS values in the previous section, RS = 1.5k\_1% are sufficient for this approach.

25

Now, the input to the droop amplifier is essentially the Vrsense voltage. This voltage is given by the following equation:

$$Vrsense_{EQV} = \frac{R_{sense}}{2} \bullet I_{OUT}$$

(EQ. 26)

The gain of the droop amplifier, K<sub>droopamp</sub>, must be adjusted for the ratio of the Rsense to droop impedance, Rdroop. We use the following equation:

$$K_{droopamp} = \frac{R_{droop}}{R_{sense}} \bullet I_{OUT}$$