## **General Description**

## \_Features

- 1.8V Minimum Start-Up Voltage (MAX669)

- Wide Input Voltage Range (1.8V to 28V)

- Tiny 10-Pin µMAX Package

- ◆ Current-Mode PWM and Idle Mode<sup>™</sup> Operation

- Efficiency Over 90%

- Adjustable 100kHz to 500kHz Oscillator or SYNC Input

- ♦ 220µA Quiescent Current

- + Logic-Level Shutdown

- Soft-Start

Applications

Cellular Telephones Telecom Hardware LANs and Network Systems POS Systems

## **Ordering Information**

| PART      | TEMP RANGE     | PIN-PACKAGE |

|-----------|----------------|-------------|

| MAX668EUB | -40°C to +85°C | 10 µMAX     |

| MAX669EUB | -40°C to +85°C | 10 µMAX     |

Idle Mode is a trademark of Maxim Integrated Products.

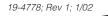

## **Pin Configuration**

The MAX668/MAX669 constant-frequency, pulse-width modulating (PWM), current-mode DC-DC controllers are designed for a wide range of DC-DC conversion applications including step-up, SEPIC, flyback, and isolated-output configurations. Power levels of 20W or more can be controlled with conversion efficiencies of over 90%. The 1.8V to 28V input voltage range supports a wide range of battery and AC-powered inputs. An advanced BiCMOS design features low operating current (220µA), adjustable operating frequency (100kHz to 500kHz), soft-start, and a SYNC input allowing the MAX668/MAX669 oscillator to be locked to an external clock.

DC-DC conversion efficiency is optimized with a low 100mV current-sense voltage as well as with Maxim's proprietary Idle Mode<sup>™</sup> control scheme. The controller operates in PWM mode at medium and heavy loads for lowest noise and optimum efficiency, then pulses only as needed (with reduced inductor current) to reduce operating current and maximize efficiency under light loads. A logic-level shutdown input is also included, reducing supply current to 3.5µA.

The MAX669, optimized for low input voltages with a guaranteed start-up voltage of 1.8V, requires bootstrapped operation (IC powered from boosted output). It supports output voltages up to 28V. The MAX668 operates with inputs as low as 3V and can be connected in either a bootstrapped or non-bootstrapped (IC powered from input supply or other source) configuration. When not bootstrapped, it has no restriction on output voltage. Both ICs are available in an extremely compact 10-pin  $\mu$ MAX package.

## **Typical Operating Circuit**

## M/X/M

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND    | 0.3V to +30V                      |

|---------------------------|-----------------------------------|

| PGND to GND               | ±0.3V                             |

| SYNC/SHDN to GND          | 0.3V to +30V                      |

| EXT, REF to GND           | 0.3V to (V <sub>LDO</sub> + 0.3V) |

| LDO, FREQ, FB, CS+ to GND | 0.3V to +6V                       |

| LDO Output Current        | 1mA to +20mA                      |

| REF Output Current        | 1mA to +1mA                       |

| LDO Short Circuit to GND  |                                   |

| REF Short Circuit to GND  | Continuous                        |

Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )

| 10-Pin µMAX (derate 5.6mW/°C above + | -70°C)444mW    |

|--------------------------------------|----------------|

| Operating Temperature Range          | 40°C to +85°C  |

| Junction Temperature                 | +150°C         |

| Storage Temperature Range            | 65°C to +150°C |

| Lead Temperature (soldering, 10sec)  | +300°C         |

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = LDO = 5V, R_{OSC} = 200k\Omega, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                            | (                                                                                                      | MIN                                               | TYP   | MAX   | UNITS |      |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------|-------|-------|------|

| PWM CONTROLLER                                       | K                                                                                                      |                                                   |       |       |       | 1    |

|                                                      | MAX668                                                                                                 |                                                   | 3     |       | 28    | V    |

| Input Voltage Range, V <sub>CC</sub>                 | Ditage Range, V <sub>CC</sub> MAX669                                                                   |                                                   |       |       | 28.0  | V    |

| Input Voltage Range with V <sub>CC</sub> Tied to LDO |                                                                                                        |                                                   | 2.7   |       | 5.5   | V    |

| FB Threshold                                         |                                                                                                        |                                                   | 1.225 | 1.250 | 1.275 | V    |

| FB Threshold Load Regulation                         |                                                                                                        | 3% per mV on CS+;<br>0 to 100mV for 0 to full     |       | 0.013 |       | %/mV |

| FB Threshold Line Regulation                         | Typically 0.012% per % duty factor on<br>EXT; EXT duty factor for a step-up is:<br>100% (1 – VIN/VOUT) |                                                   |       | 0.012 |       | %/%  |

| FB Input Current                                     | V <sub>FB</sub> = 1.30V                                                                                |                                                   |       | 1     | 20    | nA   |

| Current-Limit Threshold                              |                                                                                                        |                                                   | 85    | 100   | 115   | mV   |

| Idle Mode Current-Sense Threshold                    |                                                                                                        |                                                   | 5     | 15    | 25    | mV   |

| CS+ Input Current                                    | CS+ forced to GND                                                                                      |                                                   |       | 0.2   | 1     | μA   |

| V <sub>CC</sub> Supply Current (Note 1)              | $V_{FB} = 1.30V, V_{CC} = 3V \text{ to } 28V$                                                          |                                                   |       | 220   | 350   | μA   |

| Shutdown Supply Current (V <sub>CC</sub> )           | SYNC/SHDN = GND, V <sub>CC</sub> = 28V                                                                 |                                                   |       | 3.5   | 6     | μA   |

| REFERENCE AND LDO REGULATORS                         | u.                                                                                                     |                                                   | •     |       |       | 1    |

|                                                      | LDO load =                                                                                             | $5V \le V_{CC} \le 28V$<br>(includes LDO dropout) | 4.50  | 5.00  | 5.50  | V    |

| LDO Output Voltage                                   | $\infty$ to 400 $\Omega$                                                                               | $3V \le V_{CC} \le 28V$<br>(includes LDO dropout) | 2.65  |       | 5.50  | V    |

| Undervoltage Lockout Threshold                       | Sensed at LDO, falling edge,<br>hysteresis = 1%, MAX668 only                                           |                                                   | 2.40  | 2.50  | 2.60  | V    |

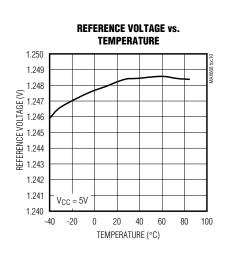

| REF Output Voltage                                   | No load, $C_{REF} = 0.22 \mu F$                                                                        |                                                   | 1.225 | 1.250 | 1.275 | V    |

| REF Load Regulation                                  | REF load = 0 to $50\mu$ A                                                                              |                                                   |       | -2    | -10   | mV   |

| REF Undervoltage Lockout Threshold                   | Rising edge, 1% hysteresis                                                                             |                                                   | 1.0   | 1.1   | 1.2   | V    |

| OSCILLATOR                                           |                                                                                                        |                                                   |       |       |       |      |

|                                                      | $R_{OSC} = 200k\Omega \pm 1\%$                                                                         |                                                   | 225   | 250   | 275   | kHz  |

| Oscillator Frequency                                 | $R_{OSC} = 100kG$                                                                                      | 425                                               | 500   | 575   |       |      |

|                                                      | $R_{OSC} = 500 k\Omega$                                                                                | 85                                                | 100   | 115   |       |      |

2

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = LDO = 5V, R_{OSC} = 200k\Omega, T_A = 0^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                | CONDITIONS                           | MIN     | TYP | MAX  | UNITS |  |

|------------------------------------------|--------------------------------------|---------|-----|------|-------|--|

|                                          | $R_{OSC} = 200k\Omega \pm 1\%$       | 87      | 90  | 93   |       |  |

| Maximum Duty Cycle                       | $R_{OSC} = 100k\Omega \pm 1\%$       |         | 90  | 94   | %     |  |

|                                          | $R_{OSC} = 500 k\Omega \pm 1\%$      | 86      | 90  | 94   |       |  |

| Minimum EXT Pulse Width                  |                                      |         | 290 |      | ns    |  |

| Minimum SYNC Input-Pulse Duty Cycle      |                                      |         | 20  | 45   | %     |  |

| Minimum SYNC Input Low Pulse Width       |                                      |         | 50  | 200  | ns    |  |

| SYNC Input Rise/Fall Time                | Not tested                           |         |     | 200  | ns    |  |

| SYNC Input Frequency Range               |                                      | 100     |     | 500  | kHz   |  |

| SYNC/SHDN Falling Edge to Shutdown Delay |                                      |         | 70  |      | μs    |  |

| CVNC/CLIDN Input Lligh Voltage           | $3V < V_{CC} < 28V$                  | 2.0     |     |      | V     |  |

| SYNC/SHDN Input High Voltage             | 1.8V < V <sub>CC</sub> < 3V (MAX669) | 1.5     |     |      | v     |  |

| SYNC/SHDN Input Low Voltage              | 3V < V <sub>CC</sub> < 28V           |         |     | 0.45 | V     |  |

| STIC/SHDN IIIput Low Voltage             | 1.8V < V <sub>CC</sub> < 3V (MAX669) |         |     | 0.30 |       |  |

|                                          | SYNC/SHDN = 5V                       | 0.5 3.0 |     |      |       |  |

| SYNC/SHDN Input Current                  | SYNC/SHDN = 28V                      |         | 1.5 | 6.5  | μA    |  |

| EXT Sink/Source Current                  | EXT forced to 2V                     |         | 1   |      | A     |  |

| EXT On-Resistance                        | EXT high or low                      |         | 2   | 5    | Ω     |  |

## **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = LDO = 5V, R_{OSC} = 200k\Omega, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                            | (                                             | MIN                                               | MAX    | UNITS |     |

|------------------------------------------------------|-----------------------------------------------|---------------------------------------------------|--------|-------|-----|

| PWM CONTROLLER                                       |                                               |                                                   |        |       |     |

| Input Voltage Pange Vee                              | MAX668                                        |                                                   | 3      | 28    | V   |

| Input Voltage Range, V <sub>CC</sub>                 | MAX669                                        |                                                   | 1.8 28 |       | - V |

| Input Voltage Range with $V_{\mbox{CC}}$ Tied to LDO |                                               |                                                   | 2.7    | 5.5   | V   |

| FB Threshold                                         |                                               |                                                   | 1.22   | 1.28  | V   |

| FB Input Current                                     | V <sub>FB</sub> = 1.30V                       |                                                   |        | 20    | nA  |

| Current-Limit Threshold                              |                                               |                                                   | 85     | 115   | mV  |

| Idle Mode Current-Sense Threshold                    |                                               |                                                   | 3      | 27    | mV  |

| CS+ Input Current                                    | CS+ forced to GND                             |                                                   |        | 1     | μA  |

| V <sub>CC</sub> Supply Current (Note 1)              | $V_{FB} = 1.30V, V_{CC} = 3V \text{ to } 28V$ |                                                   |        | 350   | μA  |

| Shutdown Supply Current (V <sub>CC</sub> )           | $SYNC/SHDN = GND, V_{CC} = 28V$               |                                                   |        | 6     | μA  |

| REFERENCE AND LDO REGULATORS                         |                                               |                                                   |        |       |     |

| LDO Output Voltage                                   | LDO load =                                    | $5V \le V_{CC} \le 28V$<br>(includes LDO dropout) | 4.50   | 5.50  | V   |

|                                                      | ∞ to 400Ω                                     | $3V \le V_{CC} \le 28V$<br>(includes LDO dropout) | 2.65   | 5.50  |     |

| LDO Undervoltage Lockout Threshold                   |                                               | O, falling edge,<br>%, MAX669 only                | 2.40   | 2.60  | V   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = LDO = 5V, R_{OSC} = 200k\Omega, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                           | CONDITIONS                           | MIN  | MAX  | UNITS |  |

|-------------------------------------|--------------------------------------|------|------|-------|--|

| REF Output Voltage                  | No load, $C_{REF} = 0.22 \mu F$      | 1.22 | 1.28 | V     |  |

| REF Load Regulation                 | REF load = 0 to $50\mu$ A            |      | -10  | mV    |  |

| REF Undervoltage Lockout Threshold  | Rising edge, 1% hysteresis           | 1.0  | 1.2  | V     |  |

| OSCILLATOR                          |                                      |      |      |       |  |

|                                     | $R_{OSC} = 200 k\Omega \pm 1\%$      | 222  | 278  |       |  |

| Oscillator Frequency                | $R_{OSC} = 100 k\Omega \pm 1\%$      | 425  | 575  | kHz   |  |

|                                     | $R_{OSC} = 500 k\Omega \pm 1\%$      | 85   | 115  |       |  |

|                                     | $R_{OSC} = 200 k\Omega \pm 1\%$      | 87   | 93   | -     |  |

| Maximum Duty Cycle                  | $R_{OSC} = 100 k\Omega \pm 1\%$      | 86   | 94   |       |  |

|                                     | $R_{OSC} = 500 k\Omega \pm 1\%$      | 86   | 94   |       |  |

| Minimum SYNC Input-Pulse Duty Cycle |                                      |      | 45   | %     |  |

| Minimum SYNC Input Low Pulse Width  |                                      |      | 200  | ns    |  |

| SYNC Input Rise/Fall Time           | Not tested                           |      | 200  | ns    |  |

| SYNC Input Frequency Range          |                                      | 100  | 500  | kHz   |  |

|                                     | $3V < V_{CC} < 28V$                  | 2.0  |      | V     |  |

| SYNC/SHDN Input High Voltage        | 1.8V < V <sub>CC</sub> < 3V (MAX669) | 1.5  |      | V     |  |

|                                     | $3V < V_{CC} < 28V$                  |      | 0.45 | V     |  |

| SYNC/SHDN Input Low Voltage         | 1.8V < V <sub>CC</sub> < 3V (MAX669) |      | 0.30 | v     |  |

|                                     | SYNC/SHDN = 5V                       |      | 3.0  |       |  |

| SYNC/SHDN Input Current             | SYNC/SHDN = 28V                      |      | 6.5  | μΑ    |  |

| EXT On-Resistance                   | EXT high or low                      |      | 5    | Ω     |  |

**Note 1:** This is the V<sub>CC</sub> current consumed when active but not switching. Does not include gate-drive current. **Note 2:** Limits at  $T_A = -40^{\circ}$ C are guaranteed by design.

4

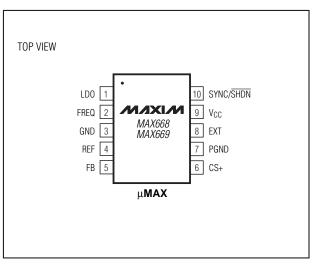

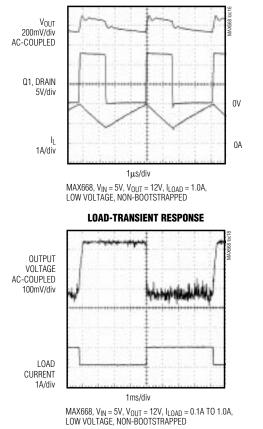

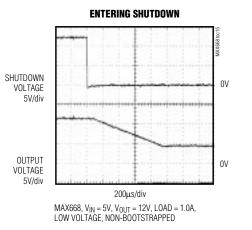

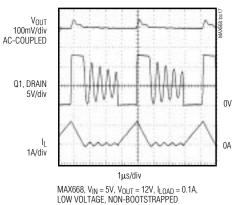

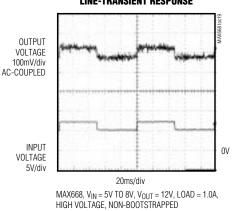

**Typical Operating Characteristics**

(Circuits of Figures 2, 3, 4, and 5;  $T_A = +25^{\circ}$ C; unless otherwise noted.)

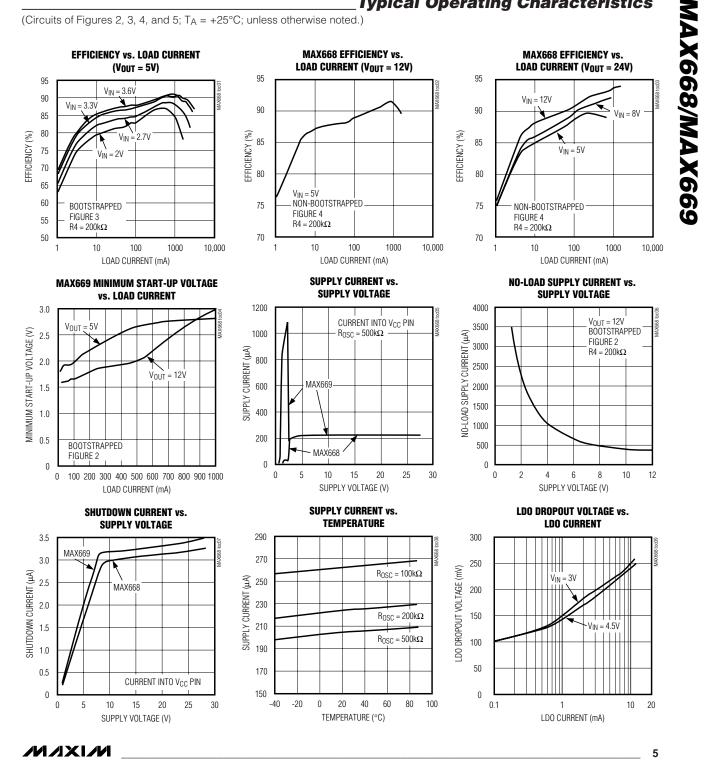

## Typical Operating Characteristics (continued)

(Circuits of Figures 2, 3, 4, and 5;  $T_A = +25^{\circ}C$ ; unless otherwise noted.)

M /X /M

## Typical Operating Characteristics (continued)

(Circuits of Figures 2, 3, 4, and 5;  $T_A = +25^{\circ}C$ ; unless otherwise noted.)

MAX668,  $V_{IN}$  = 5V,  $V_{OUT}$  = 12V, LOAD = 1.0A,  $R_{OSC}$  = 100k  $\Omega$ , LOW VOLTAGE, NON-BOOTSTRAPPED

**HEAVY-LOAD SWITCHING WAVEFORM**

LIGHT-LOAD SWITCHING WAVEFORM

LINE-TRANSIENT RESPONSE

**Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1   | LDO             | 5V On-Chip Regulator Output. This regulator powers all internal circuitry including the EXT gate driver.<br>Bypass LDO to GND with a 1µF or greater ceramic capacitor.                                                                                                                                                                                                                 |  |  |  |  |

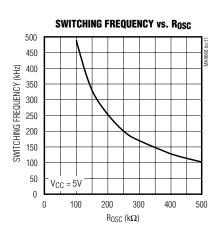

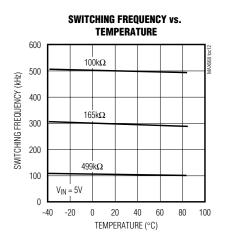

| 2   | FREQ            | Oscillator Frequency Set Input. A resistor from FREQ to GND sets the oscillator from 100kHz ( $R_{OSC} = 500k\Omega$ ) to 500kHz ( $R_{OSC} = 100k\Omega$ ). f <sub>OSC</sub> = 5 x 10 <sup>10</sup> / $R_{OSC}$ . R <sub>OSC</sub> is still required if an external clock is used at SYNC/SHDN (see the <i>SYNC/SHDN and FREQ Inputs</i> section).                                    |  |  |  |  |

| 3   | GND             | Analog Ground                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 4   | REF             | 1.25V Reference Output. REF can source 50µA. Bypass to GND with a 0.22µF ceramic capacitor.                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 5   | FB              | Feedback Input. The FB threshold is 1.25V.                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 6   | CS+             | Positive Current-Sense Input. Connect a current-sense resistor, R <sub>CS</sub> , between CS+ and PGND.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 7   | PGND            | Power Ground for EXT Gate Driver and Negative Current-Sense Input                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

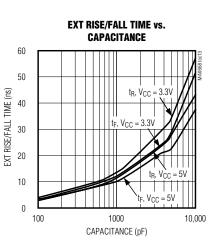

| 8   | EXT             | External MOSFET Gate-Driver Output. EXT swings from LDO to PGND.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 9   | V <sub>CC</sub> | Input Supply to On-Chip LDO Regulator. $V_{CC}$ accepts inputs up to 28V. Bypass to GND with a 0.1 $\mu F$ ceramic capacitor.                                                                                                                                                                                                                                                          |  |  |  |  |

| 10  | SYNC/<br>SHDN   | <ul> <li>Shutdown control and Synchronization Input. There are three operating modes:</li> <li>SYNC/SHDN low: DC-DC off.</li> <li>SYNC/SHDN high: DC-DC on with oscillator frequency set at FREQ by R<sub>OSC</sub>.</li> <li>SYNC/SHDN clocked: DC-DC on with operating frequency set by SYNC clock input. DC-DC conversion cycles initiate on rising edge of input clock.</li> </ul> |  |  |  |  |

## **Detailed Description**

The MAX668/MAX669 current-mode PWM controllers operate in a wide range of DC-DC conversion applications, including boost, SEPIC, flyback, and isolated output configurations. Optimum conversion efficiency is maintained over a wide range of loads by employing both PWM operation and Maxim's proprietary Idle Mode control to minimize operating current at light loads. Other features include shutdown, adjustable internal operating frequency or synchronization to an external clock, soft start, adjustable current limit, and a wide (1.8V to 28V) input range.

## MAX668 vs. MAX669 Differences

Differences between the MAX668 and MAX669 relate to their use in bootstrapped or non-bootstrapped circuits (Table 1). The MAX668 operates with inputs as low as 3V and can be connected in *either* a bootstrapped or non-bootstrapped (IC powered from input supply or other source) configuration. When not bootstrapped, the MAX668 has no restriction on output voltage. When bootstrapped, the output cannot exceed 28V.

The MAX669 is optimized for low input voltages (down to 1.8V) and *requires* bootstrapped operation (IC powered from  $V_{OUT}$ ) with output voltages no greater than

28V. Bootstrapping is required because the MAX669 does not have undervoltage lockout, but instead drives EXT with an open-loop, 50% duty-cycle start-up oscillator when LDO is below 2.5V. It switches to closed-loop operation only when LDO exceeds 2.5V. If a non-bootstrapped connection is used with the MAX669 and if V<sub>CC</sub> (the input voltage) remains below 2.7V, the output voltage will soar above the regulation point. Table 2 recommends the appropriate device for each biasing option.

## Table 1. MAX668/MAX669 Comparison

| FEATURE                        | MAX668                                                                                                                                              | MAX669                                                                                                                   |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> Input<br>Range | 3V to 28V                                                                                                                                           | 1.8V to 28V                                                                                                              |

| Operation                      | Bootstrapped or nonboot-<br>strapped. V <sub>CC</sub> can be con-<br>nected to input, output, or<br>other voltage source such as<br>a logic supply. | Must be boot-<br>strapped (V <sub>CC</sub><br>must be connect-<br>ed to boosted out-<br>put voltage, V <sub>OUT</sub> ). |

| UVLO                           | IC stops switching for LDO below 2.5V.                                                                                                              | No                                                                                                                       |

| Soft-Start                     | Yes                                                                                                                                                 | When LDO is above 2.5V                                                                                                   |

# MAX668/MAX669

# 1.8V to 28V Input, PWM Step-Up Controllers in µMAX

## **PWM Controller**

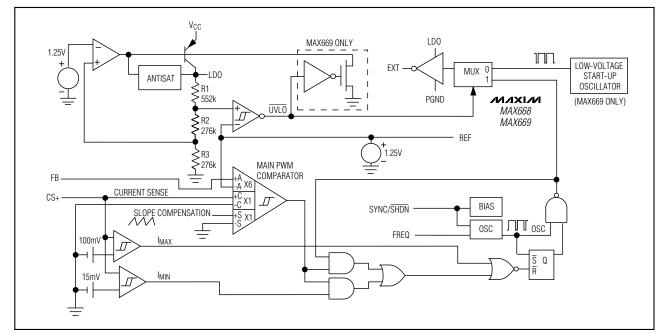

The heart of the MAX668/MAX669 current-mode PWM controller is a BiCMOS multi-input comparator that simultaneously processes the output-error signal, the current-sense signal, and a slope-compensation ramp (Figure 1). The main PWM comparator is direct summing, lacking a traditional error amplifier and its associated phase shift. The direct summing configuration approaches ideal cycle-by-cycle control over the output voltage since there is no conventional error amp in the feedback path.

In PWM mode, the controller uses fixed-frequency, current-mode operation where the duty ratio is set by the input/output voltage ratio (duty ratio =  $(V_{OUT} - V_{IN}) / V_{IN}$  in the boost configuration). The current-mode feedback loop regulates peak inductor current as a function of the output error signal.

At light loads the controller enters Idle Mode. During Idle Mode, switching pulses are provided only as needed to service the load, and operating current is minimized to provide best light-load efficiency. The minimum-current comparator threshold is 15mV, or 15% of the full-load value (I<sub>MAX</sub>) of 100mV. When the controller is synchronized to an external clock, Idle Mode occurs only at very light loads.

## Bootstrapped/Non-Bootstrapped Operation

## Low-Dropout Regulator (LDO)

Several IC biasing options, including bootstrapped and non-bootstrapped operation, are made possible by an on-chip, low-dropout 5V regulator. The regulator input is at V<sub>CC</sub>, while its output is at LDO. All MAX668/MAX669 functions, including EXT, are internally powered from LDO. The V<sub>CC</sub>-to-LDO dropout voltage is typically 200mV (300mV max at 12mA), so that when V<sub>CC</sub> is less than 5.2V, LDO is typically V<sub>CC</sub> - 200mV. When LDO is in dropout, the MAX668/MAX669 still operate with V<sub>CC</sub> as low as 3V (as long as LDO exceeds 2.7V), but with reduced amplitude FET drive at EXT. The maximum V<sub>CC</sub> input voltage is 28V.

LDO can supply up to 12mA to power the IC, supply gate charge through EXT to the external FET, and supply small external loads. When driving particularly large FETs at high switching rates, little or no LDO current may be available for external loads. For example, when switched at 500kHz, a large FET with 20nC gate charge requires 20nC x 500kHz, or 10mA.

V<sub>CC</sub> and LDO allow a variety of biasing connections to optimize efficiency, circuit quiescent current, and fullload start-up behavior for different input and output voltage ranges. Connections are shown in Figures 2, 3, 4, and 5. The characteristics of each are outlined in Table 1.

Figure 1. MAX668/MAX669 Functional Diagram

///XI//

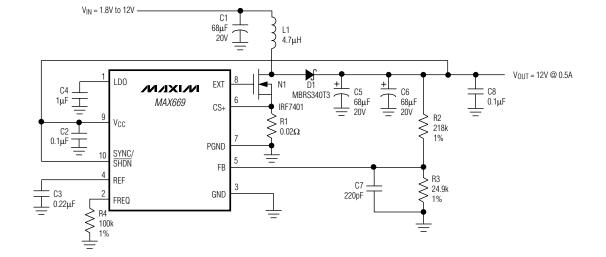

Figure 2. MAX669 High-Voltage Bootstrapped Configuration

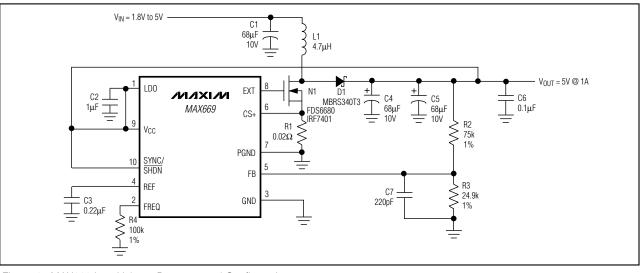

Figure 3. MAX669 Low-Voltage Bootstrapped Configuration

#### Bootstrapped Operation

With bootstrapped operation, the IC is powered from the circuit output (V<sub>OUT</sub>). This improves efficiency when the input voltage is low, since EXT drives the FET with a higher gate voltage than would be available from the low-voltage input. Higher gate voltage reduces the FET on-resistance, increasing efficiency. Other (undesirable) characteristics of bootstrapped operation are increased IC operating power (since it has a higher operating voltage) and reduced ability to start up with high load current at low input voltages. If the input voltage range extends below 2.7V, then bootstrapped operation with the MAX669 is the only option.

With V<sub>CC</sub> connected to V<sub>OUT</sub>, as in Figure 2, EXT voltage swing is 5V when V<sub>CC</sub> is 5.2V or more, and V<sub>CC</sub> - 0.2V when V<sub>CC</sub> is less than 5.2V. If the output voltage does not exceed 5.5V, the on-chip regulator can be disabled by connecting V<sub>CC</sub> to LDO (Figure 3). This eliminates the LDO forward drop and supplies maximum gate drive to the external FET.

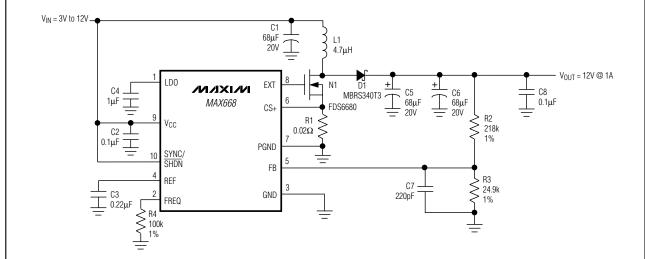

Figure 4. MAX668 High-Voltage Non-Bootstrapped Configuration

Figure 5. MAX668 Low-Voltage Non-Bootstrapped Configuration

## Non-Bootstrapped Operation

With non-bootstrapped operation, the IC is powered from the input voltage (VIN) or another source, such as a logic supply. Non-bootstrapped operation (Figure 4) is recommended (but not required) for input voltages above 5V, since the EXT amplitude (limited to 5V by LDO) at this voltage range is no higher than it would be with bootstrapped operation. Note that non-bootstrapped operation is *required* if the output voltage exceeds 28V, since this level is too high to safely con-

M/X/M

#### nect to V<sub>CC</sub>. Also note that only the MAX668 can be used with non-bootstrapped operation.

If the input voltage does not exceed 5.5V, the on-chip regulator can be disabled by connecting V<sub>CC</sub> to LDO (Figure 5). This eliminates the regulator forward drop and supplies the maximum gate drive to the external FET for lowest on-resistance. Disabling the regulator also reduces the non-bootstrapped minimum input voltage from 3V to 2.7V.

| CONFIGURATION                        | FIGURE      | USE<br>WITH: | INPUT<br>VOLTAGE<br>RANGE* (V) | OUTPUT<br>VOLTAGE<br>RANGE (V) | COMMENTS                                                                                                                                                                                                                                                                                                |

|--------------------------------------|-------------|--------------|--------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Voltage,<br>Bootstrapped        | Figure<br>2 | MAX669       | 1.8 to 28                      | 3V to 28                       | <b>Connect V<sub>CC</sub> to V<sub>OUT</sub></b> . Provides maximum external FET gate drive for low-voltage (Input <3V) to high-voltage (output >5.5V) boost circuits. V <sub>OUT</sub> cannot exceed 28V.                                                                                              |

| Low-Voltage,<br>Bootstrapped         | Figure<br>3 | MAX669       | 1.8 to 5.5                     | 2.7 to 5.5                     | <b>Connect V<sub>OUT</sub> to V<sub>CC</sub> and LDO</b> . Provides maximum possible external FET gate drive for low-voltage designs, but limits $V_{OUT}$ to 5.5V or less.                                                                                                                             |

| High-Voltage,<br>Non-Bootstrapped    | Figure<br>4 | MAX668       | 3 to 28                        | V <sub>IN</sub> to ∞           | <b>Connect V</b> <sub>IN</sub> to V <sub>CC</sub> . Provides widest input and output range, but external FET gate drive is reduced for V <sub>IN</sub> below 5V.                                                                                                                                        |

| Low-Voltage,<br>Non-Bootstrapped     | Figure<br>5 | MAX668       | 2.7 to 5.5                     | V <sub>IN</sub> to ∞           | <b>Connect VIN to V<sub>CC</sub> and LDO</b> . FET gate-drive<br>amplitude = $V_{IN}$ for logic-supply (input 3V to 5.5V) to<br>high-voltage (output >5.5V) boost circuits. IC oper-<br>ating power is less than in Figure 4, since IC current<br>does not pass through the LDO regulator.              |

| Extra IC supply,<br>Non-Bootstrapped | None        | MAX668       | Not<br>Restricted              | V <sub>IN</sub> to ∞           | Connect VCC and LDO to a separate supply (V <sub>BIAS</sub> ) that powers only the IC. FET gate-drive amplitude = V <sub>BIAS</sub> . Input power source (V <sub>IN</sub> ) and output voltage range (V <sub>OUT</sub> ) are not restricted, except that V <sub>OUT</sub> must exceed V <sub>IN</sub> . |

## Table 2. Bootstrapped and Non-Bootstrapped Configurations

\* For standard step-up DC-DC circuits (as in Figures 2, 3, 4, and 5), regulation cannot be maintained if V<sub>IN</sub> exceeds V<sub>OUT</sub>. SEPIC and transformer-based circuits do not have this limitation.

In addition to the configurations shown in Table 2, the following guidelines may help when selecting a configuration:

- If V<sub>IN</sub> is ever below 2.7V, V<sub>CC</sub> must be bootstrapped to V<sub>OUT</sub> and the MAX669 must be used. If V<sub>OUT</sub> never exceeds 5.5V, LDO may be shorted to V<sub>CC</sub> and V<sub>OUT</sub> to eliminate the dropout voltage of the LDO regulator.

- 2) If VIN is greater than 3V, VCC can be powered from VIN, rather than from VOUT (non-bootstrapped). This can save quiescent power consumption, especially when VOUT is large. If VIN never exceeds 5.5V, LDO may be shorted to VCC and VIN to eliminate the dropout voltage of the LDO regulator.

- 3) If VIN is in the 3V to 4.5V range (i.e., 1-cell Li+ or 3-cell NiMH battery range), bootstrapping V<sub>CC</sub> from V<sub>OUT</sub>, although not required, may increase overall efficiency by increasing gate drive (and reducing FET resistance) at the expense of quiescent power consumption.

- If V<sub>IN</sub> always exceeds 4.5V, V<sub>CC</sub> should be tied to V<sub>IN</sub>, since bootstrapping from V<sub>OUT</sub> does not increase gate drive from EXT but does increase quiescent power dissipation.

## **SYNC/SHDN** and FREQ Inputs

The SYNC/SHDN pin provides both external-clock synchronization (if desired) and shutdown control. When SYNC/SHDN is low, all IC functions are shut down. A logic high at SYNC/SHDN selects operation at a frequency set by ROSC, connected from FREQ to GND. The relationship between fosc and ROSC is:

$$ROSC = 5 \times 10^{10} / fOSC$$

So a 500kHz operating frequency, for example, is set with ROSC = 100k  $\Omega.$

Rising clock edges on SYNC/SHDN are interpreted as synchronization inputs. If the sync signal is lost while SYNC/SHDN is high, the internal oscillator takes over at the end of the last cycle and the frequency is returned to the rate set by ROSC. If sync is lost with SYNC/SHDN low, the IC waits for 70µs before shutting down. This maintains output regulation even with intermittent sync signals. When an external sync signal is used, Idle Mode switchover at the 15mV current-sense threshold is disabled so that Idle Mode only occurs at very light loads. Also, ROSC should be set for a frequency 15% below the SYNC clock rate:

$ROSC(SYNC) = 5 \times 10^{10} / (0.85 \times fSYNC)$

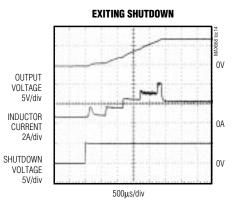

#### Soft-Start

The MAX668/MAX669 feature a "digital" soft start which is preset and requires no external capacitor. Upon start-up, the peak inductor increments from 1/5 of the value set by R<sub>CS</sub>, to the full current-limit value, in five steps over 1024 cycles of fO<sub>SC</sub> or f<sub>SYNC</sub>. For example, with an fO<sub>SC</sub> of 200kHz, the complete soft-start sequence takes 5ms. See the *Typical Operating Characteristics* for a photo of soft-start operation. Softstart is implemented: 1) when power is first applied to the IC, 2) when exiting shutdown with power already applied, and 3) when exiting undervoltage lockout. The MAX669's soft-start sequence does not start until LDO reaches 2.5V.

## **Design Procedure**

The MAX668/MAX669 can operate in a number of DC-DC converter configurations including step-up, SEPIC (single-ended primary inductance converter), and flyback. The following design discussions are limited to step-up, although SEPIC and flyback examples are shown in the *Application Circuits* section.

#### **Setting the Operating Frequency**

The MAX668/MAX669 can be set to operate from 100kHz to 500kHz. Choice of operating frequency will depend on number of factors:

Noise considerations may dictate setting (or synchronizing) fOSC above or below a certain frequency or band of frequencies, particularly in RF applications.

- 2) Higher frequencies allow the use of smaller value (hence smaller size) inductors and capacitors.

- 3) Higher frequencies consume more operating power both to operate the IC and to charge and discharge the gate of the external FET. This tends to reduce efficiency at light loads; however, the MAX668/ MAX669's Idle Mode feature substantially increases light-load efficiency.

- 4) Higher frequencies may exhibit poorer overall efficiency due to more transition losses in the FET; however, this shortcoming can often be nullified by trading some of the inductor and capacitor size benefits for lower-resistance components.

The oscillator frequency is set by a resistor, ROSC, connected from FREQ to GND. ROSC must be connected whether or not the part is externally synchronized  $R_{OSC}$  is in each case:

$$R_{OSC} = 5 \times 10^{10} / f_{OSC}$$

when *not* using an external clock.

$ROSC(SYNC) = 5 \times 10^{10} / (0.85 \times fSYNC)$ when using an external clock, fSYNC.

#### Setting the Output Voltage

The output voltage is set by two external resistors (R2 and R3, Figures 2, 3, 4, and 5). First select a value for R3 in the  $10k\Omega$  to  $1M\Omega$  range. R2 is then given by:

where V<sub>REF</sub> is 1.25V.

## **Determining Inductance Value**

For most MAX668/MAX669 boost designs, the inductor value (LIDEAL) can be derived from the following equation, which picks the optimum value for stability based on the MAX668/MAX669's internally set slope compensation:

$$LIDEAL = VOUT / (4 \times IOUT \times fOSC)$$

The MAX668/MAX669 allow significant latitude in inductor selection if  $L_{IDEAL}$  is not a convenient value. This may happen if  $L_{IDEAL}$  is a not a standard inductance (such as 10µH, 22µH, etc.), or if  $L_{IDEAL}$  is too large to be obtained with suitable resistance and saturation-current rating in the desired size. Inductance values smaller than  $L_{IDEAL}$  may be used with no adverse stability effects; however, the peak-to-peak inductor current (ILPP) will rise as L is reduced. This has the effect of raising the required ILPK for a given output power and also requiring larger output capacitance to maintain a

MAX668/MAX669

given output ripple. An inductance value larger than  $L_{IDEAL}$  may also be used, but output-filter capacitance must be increased by the same proportion that L has to  $L_{IDEAL}$ . See the *Capacitor Selection* section for more information on determining output filter values.

Due the MAX668/MAX669's high switching frequencies, inductors with a ferrite core or equivalent are recommended. Powdered iron cores are *not* recommended due to their high losses at frequencies over 50kHz.

### **Determining Peak Inductor Current**

The peak inductor current required for a particular output is:

$$I_{LPEAK} = I_{LDC} + (I_{LPP} / 2)$$

where  $I_{LDC}$  is the average DC input current and  $I_{LPP}$  is the inductor peak-to-peak ripple current. The  $I_{LDC}$  and  $I_{LPP}$  terms are determined as follows:

$$I_{LDC} = \frac{I_{OUT} (V_{OUT} + V_D)}{(V_{IN} - V_{SW})}$$

where  $V_{\rm D}$  is the forward voltage drop across the Schottky rectifier diode (D1), and V\_{SW} is the drop across the external FET, when on.

$$I_{LPP} = \frac{(V_{IN} - V_{SW})(V_{OUT} + V_D - V_{IN})}{L \times f_{OSC} (V_{OUT} + V_D)}$$

where L is the inductor value. The saturation rating of the selected inductor should meet or exceed the calculated value for ILPEAK, although most coil types can be operated up to 20% over their saturation rating without difficulty. In addition to the saturation criteria, the inductor should have as low a series resistance as possible. For continuous inductor current, the power loss in the inductor resistance,  $P_{LR}$ , is approximated by:

$$P_{LR} \cong (I_{OUT} \times V_{OUT} / V_{IN})^2 \times R_L$$

where  $R_L$  is the inductor series resistance.

Once the peak inductor current is selected, the currentsense resistor (R<sub>CS</sub>) is determined by:

For high peak inductor currents (>1A), Kelvin sensing connections should be used to connect CS+ and PGND to R<sub>CS</sub>. PGND and GND should be tied together at the ground side of R<sub>CS</sub>.

#### **Power MOSFET Selection**

The MAX668/MAX669 drive a wide variety of N-channel power MOSFETs (NFETs). Since LDO limits the EXT output gate drive to no more than 5V, a logic-level NFET is required. Best performance, especially at low input voltages (below 5V), is achieved with low-threshold NFETs that specify on-resistance with a gatesource voltage (V\_GS) of 2.7V or less. When selecting an NFET, key parameters can include:

- 1) Total gate charge (Qg)

- 2) Reverse transfer capacitance or charge (C<sub>RSS</sub>)

- 3) On-resistance (R<sub>DS(ON)</sub>)

- 4) Maximum drain-to-source voltage (V<sub>DS(MAX)</sub>)

- 5) Minimum threshold voltage (V<sub>TH(MIN)</sub>)

At high switching rates, dynamic characteristics (parameters 1 and 2 above) that predict switching losses may have more impact on efficiency than  $R_{DS(ON)}$ , which predicts DC losses.  $Q_g$  includes all capacitances associated with charging the gate. In addition, this parameter helps predict the current needed to drive the gate at the selected operating frequency. The continuous LDO current for the FET gate is:

$$GATE = Q_g \times fOSC$$

For example, the MMFT3055L has a typical Qg of 7nC (at V<sub>GS</sub> = 5V); therefore, the I<sub>GATE</sub> current at 500kHz is 3.5mA. Use the FET manufacturer's *typical* value for Qg in the above equation, since a maximum value (if supplied) is usually too conservative to be of use in estimating I<sub>GATE</sub>.

#### **Diode Selection**

The MAX668/MAX669's high switching frequency demands a high-speed rectifier. Schottky diodes are recommended for most applications because of their fast recovery time and low forward voltage. Ensure that the diode's average current rating is adequate using the diode manufacturer's data, or approximate it with the following formula:

$$DIODE = I_{OUT} + \frac{I_{LPEAK} - I_{OUT}}{3}$$

1

Also, the diode reverse breakdown voltage must exceed V<sub>OUT</sub>. For high output voltages (50V or above), Schottky diodes may not be practical because of this voltage requirement. In these cases, use a high-speed silicon rectifier with adequate reverse voltage.

## **Capacitor Selection**

#### **Output Filter Capacitor** The minimum output filter capacitance that ensures stability is:

$$C_{OUT(MIN)} = \frac{(7.5V \times L / L_{IDEAL})}{(2\pi R_{CS} \times V_{IN(MIN)} \times f_{OSC})}$$

where  $V_{IN(MIN)}$  is the minimum expected input voltage. Typically  $C_{OUT(MIN)},$  though sufficient for stability, will

not be adequate for low output voltage ripple. Since output ripple in boost DC-DC designs is dominated by capacitor equivalent series resistance (ESR), a capacitance value 2 or 3 times larger than COUT(MIN) is typically needed. Low-ESR types must be used. Output ripple due to ESR is:

VRIPPLE(ESR) = ILPEAK X ESRCOUT

#### Input Capacitor

The input capacitor (C<sub>IN</sub>) in boost designs reduces the current peaks drawn from the input supply and reduces noise injection. The value of C<sub>IN</sub> is largely determined by the source impedance of the input supply. High source impedance requires high input capacitance, particularly as the input voltage falls. Since step-up DC-DC converters act as "constant-power" loads to their input supply, input current rises as input voltage falls. Consequently, in low-input-voltage designs, increasing C<sub>IN</sub> and/or lowering its ESR can add as many as five percentage points to conversion efficiency. A good starting point is to use the same capacitance value for C<sub>IN</sub> as for C<sub>OUT</sub>.

#### Bypass Capacitors

In addition to C<sub>IN</sub> and C<sub>OUT</sub>, three ceramic bypass capacitors are also required with the MAX668/MAX669. Bypass REF to GND with 0.22µF or more. Bypass LDO to GND with 1µF or more. And bypass V<sub>CC</sub> to GND with 0.1µF or more. All bypass capacitors should be located as close to their respective pins as possible.

#### **Compensation Capacitor**

Output ripple voltage due to  $C_{OUT}$  ESR affects loop stability by introducing a left half-plane zero. A small capacitor connected from FB to GND forms a pole with the feedback resistance that cancels the ESR zero. The optimum compensation value is:

$$C_{FB} = C_{OUT} \times \frac{ESR_{COUT}}{(R2 \times R3) / (R2 + R3)}$$

where R2 and R3 are the feedback resistors (Figures 2, 3, 4, and 5). If the calculated value for CFB results in a non-standard capacitance value, values from 0.5CFB to 1.5CFB will also provide sufficient compensation.

## Applications Information

#### Starting Under Load

In non-bootstrapped configurations (Figures 4 and 5), the MAX668 can start up with any combination of output load and input voltage at which it can operate when already started. In other words, there are no special limitations to start-up in non-bootstrapped circuits.

In bootstrapped configurations with the MAX668 or MAX669, there may be circumstances where full load current can only be applied after the circuit has started and the output is near its set value. As the input voltage drops, this limitation becomes more severe. This characteristic of all bootstrapped designs occurs when the MOSFET gate is not fully driven until the output voltage rises. This is problematic because a heavily loaded output cannot rise until the MOSFET has low on-resistance. In such situations, low-threshold FETs (VTH < VIN(MIN)) are the most effective solution. The *Typical Operating Characteristics* section shows plots of startup voltage versus load current for a typical bootstrapped design.

#### Layout Considerations

Due to high current levels and fast switching waveforms that radiate noise, proper PC board layout is essential. Protect sensitive analog grounds by using a star ground configuration. Minimize ground noise by connecting GND, PGND, the input bypass-capacitor ground lead, and the output-filter ground lead to a single point (star ground configuration). Also, minimize trace lengths to reduce stray capacitance, trace resistance, and radiated noise. The trace between the external gain-setting resistors and the FB pin must be extremely short, as must the trace between GND and PGND.

### **Application Circuits**

#### Low-Voltage Boost Circuit

Figure 3 shows the MAX669 operating in a low-voltage boost application. The MAX669 is configured in the bootstrapped mode to improve low input voltage performance. The IRF7401 N-channel MOSFET was selected for Q1 in this application because of its very low 0.7V gate threshold voltage (V<sub>GS</sub>). This circuit provides a 5V output at greater than 2A of output current and operates with input voltages as low as 1.8V. Efficiency is typically in the 85% to 90% range.

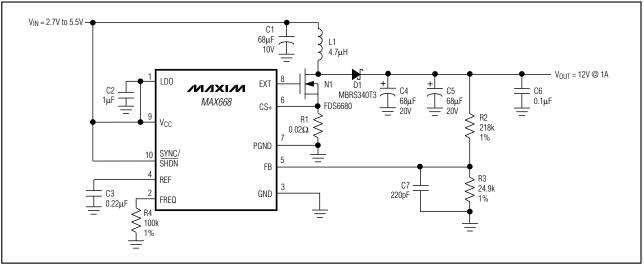

#### 12V Boost Application

Figure 5 shows the MAX668 operating in a 5V to 12V boost application. This circuit provides output currents of greater than 1A at a typical efficiency of 92%. The MAX668 is operated in non-bootstrapped mode to minimize the input supply current. This achieves maximum light-load efficiency. If input voltages below 5V are used, the IC should be operated in bootstrapped mode to achieve best low-voltage performance.

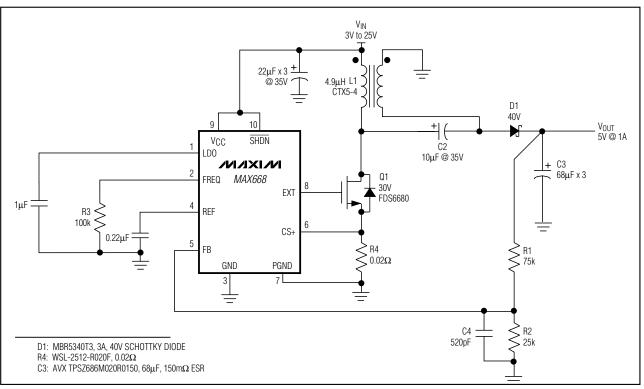

## 4-Cell to 5V SEPIC Power Supply

Figure 6 shows the MAX668 in a SEPIC (single-ended primary inductance converter) configuration. This configuration is useful when the input voltage can be either

larger or smaller than the output voltage, such as when converting four NiMH, NiCd, or Alkaline cells to a 5V output. The SEPIC configuration is often a good choice for combined step-up/step-down applications.

The N-channel MOSFET (Q1) must be selected to withstand a drain-to-source voltage (V<sub>DS</sub>) greater than the sum of the input and output voltages. The coupling capacitor (C2) must be a low-ESR type to achieve maximum efficiency. C2 must also be able to handle high ripple currents; ordinary tantalum capacitors should not be used for high-current designs.

The circuit in Figure 6 provides greater than 1A output current at 5V when operating with an input voltage from 3V to 25V. Efficiency will typically be between 70% and 85%, depending upon the input voltage and output current.

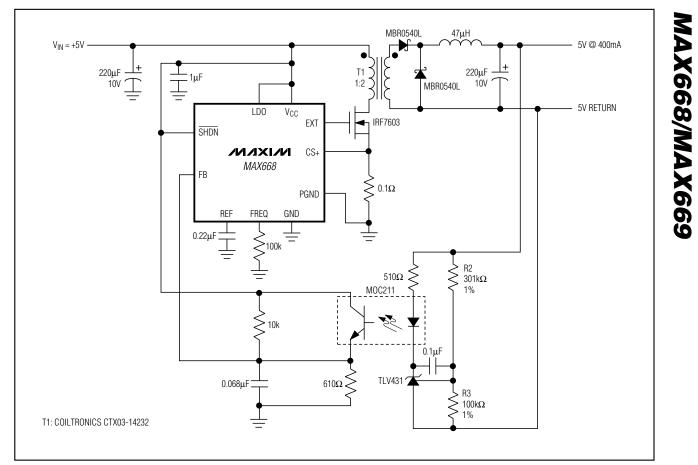

#### Isolated 5V to 5V Power Supply

The circuit of Figure 7 provides a 5V isolated output at 400mA from a 5V input power supply. Transformer T1 provides electrical isolation for the forward path of the converter, while the TLV431 shunt regulator and MOC211 opto-isolator provide an isolated feedback error voltage for the converter. The output voltage is set by resistors R2 and R3 such that the mid-point of the divider is 1.24V (threshold of TLV431). Output voltage can be adjusted from 1.24V to 6V by selecting the proper ratio for R2 and R3. For output voltages greater than 6V, substitute the TL431 for the TLV431, and use 2.5V as the voltage at the midpoint of the voltage divider.

## **Chip Information**

TRANSISTOR COUNT: 1861

Figure 6. MAX668 in SEPIC Configuration

Figure 7. Isolated 5V to 5V at 400mA Power Supply

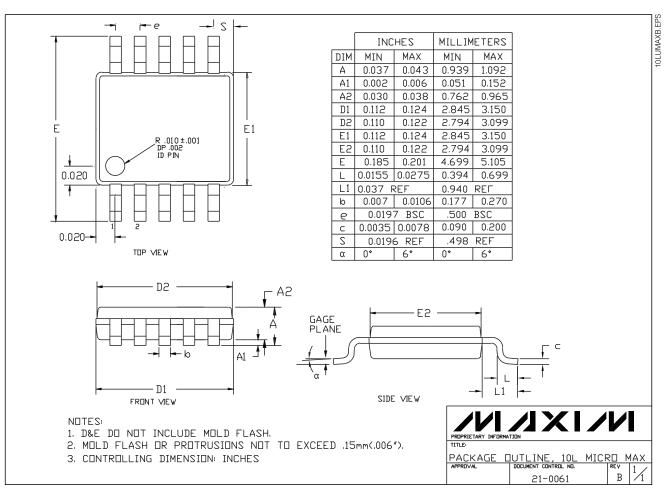

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to www.maxim-ic.com/packages.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

© 2002 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.