# L6219DSA

## Stepper motor driver for automotive range

### Features

- Able to drive both windings of bipolar stepper motor

- Output current up to 750 mA each winding

- Wide voltage range: 10 V to 46 V

- Half-step, full-step and microstepping mode

- Built-in protection diodes

- Internal PWM current control

- Low output saturation voltage

- Designed for unstabilized motor supply voltage

- Internal thermal shutdown

## Description

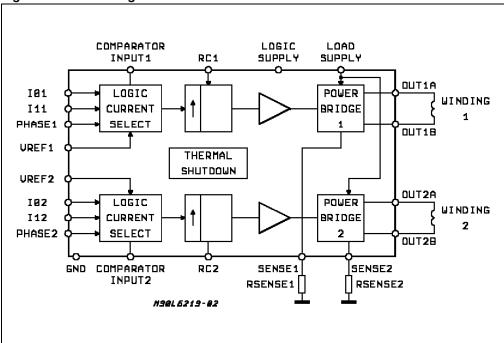

The L6219DSA is a bipolar monolithic integrated circuits intended to control and drive both winding of a bipolar stepper motor or bidirectionally control two DC motors.

The L6219DSA with a few external components form a complete control and drive circuit for LS-TTL or microprocessor controlled stepper motor system. The power stage is a dual full bridge capable of sustaining 46 V and including four diodes for current recirculation. SO24 (20+2+2)

A cross conduction protection is provided to avoid simultaneous cross conduction during switching current direction.

An internal pulse-width-modulation (PWM) controls the output current to 750 mA with peak startup current up to 1 A.

Wide range of current control from 750 mA (each bridge) is permitted by means of two logic inputs and an external voltage reference. A phase input to each bridge determines the load current direction. A thermal protection circuitry disables the outputs if the chip temperature exceeds safe operating limits.

#### Table 1. Device summary

| Order code   | Package | Packing     |

|--------------|---------|-------------|

| E-L6219DSA   | SO24    | Tube        |

| E-L6219DSATR | SO24    | Tape & reel |

# Contents

| 1 | Block diagram |                           |  |

|---|---------------|---------------------------|--|

| 2 | Func          | tional description        |  |

|   | 2.1           | Input logic (I0 and I1)   |  |

|   | 2.2           | Phase                     |  |

|   | 2.3           | Current sensor            |  |

|   | 2.4           | Single-pulse generator 10 |  |

|   | 2.5           | Output stage 10           |  |

|   | 2.6           | VS, VSS, VRef             |  |

| 3 | Appli         | cation information        |  |

| 4 | Pack          | age information           |  |

| 5 | Revis         | sion history              |  |

# List of tables

| Table 1. | Device summary            |

|----------|---------------------------|

| Table 2. | Absolute maximum rating   |

| Table 3. | Pin functions             |

|          | Thermal data              |

|          | Electrical characteristcs |

|          | Current levels            |

| Table 7. | Document revision history |

\_\_\_\_\_

# List of figures

| Figure 1. | Block diagram                                | 5 |

|-----------|----------------------------------------------|---|

| Figure 2. | SO24 pins connection (top view)              | 6 |

| Figure 3. | Timing diagram                               | 7 |

| Figure 4. | Principle operating sequence 1               | 0 |

| Figure 5. | Typical application circuit 1                | 2 |

| Figure 6. | SO24 mechanical data and package dimensions1 | 3 |

## 1 Block diagram

#### Table 2.Absolute maximum rating

| Parameter          | Description                 |             | Unit |

|--------------------|-----------------------------|-------------|------|

| V <sub>s</sub>     | Supply voltage              |             | V    |

| Ι <sub>Ο</sub>     | Output current (peak)       | ±1          | А    |

| Ι <sub>Ο</sub>     | Output current (continuous) | ±0.75       | А    |

| V <sub>ss</sub>    | Logic supply voltage        | 7           | V    |

| V <sub>in</sub>    | Logic input voltage range   | -0.3 to +7  | V    |

| V <sub>sense</sub> | Sense output voltage        | 1.5         | V    |

| Тј                 | Junction temperature        | +150        | °C   |

| T <sub>op</sub>    | Operating temperature range | -40 to +125 | °C   |

| T <sub>stg</sub>   | Storage temperature range   | -55 to +150 | °C   |

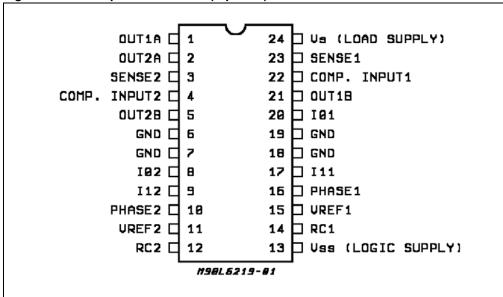

#### Figure 2. SO24 pins connection (top view)

#### Table 3. Pin functions

| Pin #                    | Name               | Description                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 21 Output of bridge 1 |                    | See pins 2, 5                                                                                                                                                                                                                                                                                                                                                                         |

| 3, 23                    | Sense resistor     | Connection to lower emitters of output stage for insertion of<br>current sense resistor                                                                                                                                                                                                                                                                                               |

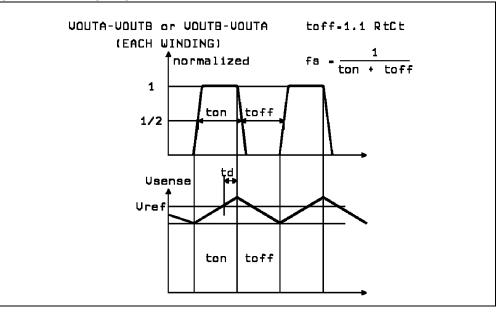

| 4, 22 Comparator input   |                    | Input connected to the comparators. The voltage across the sense resistor is feedback to this input throught the low pass filter RC CC. The higher power transistors are disabled when the sense voltage exceeds the reference voltage of the selected comparator. When this occurs the current decays for a time set by $R_T C^T$ ( $t_{off} = 1.1 R_T C_T$ ). See <i>Figure 3</i> . |

| 2, 5                     | Output of bridge 2 | Output Connection. The output stage is a H bridge formed<br>by four transistors and four diodes suitable for switching<br>applications                                                                                                                                                                                                                                                |

| 6, 7, 18, 19             | Ground             | Ground connection, they also conducts heat from die to printed circuit copper                                                                                                                                                                                                                                                                                                         |

| 8, 20                    | Input 0            | See input 1 (pins 9, 17)                                                                                                                                                                                                                                                                                                                                                              |

| 9, 17                    | Input 1            | These pins and pins 8, 20 (input 0) are logic inputs which<br>select the outputs of the comparators to set the current<br>level. Current also depends on the sensing resistor and<br>reference voltage. See functional description                                                                                                                                                    |

| Table 5. Finitunctions (continued) |                              |                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin #                              | Name                         | Description                                                                                                                                                                                                                                                                                                                |  |  |

| 10, 16                             | Phase                        | This TTL-compatible logic inputs sets the direction of<br>current flow through the load. A high level causes current to<br>flow from output A (source) to output B (sink). A schmitt<br>trigger on this input provides good noise immunity and a<br>delay circuit prevents output stage short circuits during<br>switching |  |  |

| 11, 15                             | Reference voltage            | A voltage applied to this pin sets the reference voltage of the comparators, this determining the output current (also thus depending on Rs and the two inputs input 0 and input 1)                                                                                                                                        |  |  |

| 12, 14                             | RC                           | A parallel RC network connected to this pin sets the off time of the higher power transistors. The pulse generator is a monostable triggered by the output of the comparators ( $t_{off} = 1.1 R_T C_T$ )                                                                                                                  |  |  |

| 13                                 | $V_{SS}$ - Logic supply      | Supply voltage input for logic circuitry                                                                                                                                                                                                                                                                                   |  |  |

| 24                                 | V <sub>S</sub> - Load supply | Supply voltage input for the output stages                                                                                                                                                                                                                                                                                 |  |  |

Table 3. Pin functions (continued)

Note: ESD on GND, V<sub>S</sub>, V<sub>SS</sub>, OUT 1 A and OUT 2 A is guaranteed up to 1.5 KV (human body model, 1500 W, 100 pF).

#### Figure 3. Timing diagram

#### Table 4. Thermal data

| Parameter             | Description                         |      | PDIP              | Unit |

|-----------------------|-------------------------------------|------|-------------------|------|

| R <sub>thj-case</sub> | Thermal resistance junction-case    | max. | 18                | °C/W |

| R <sub>thj-amb</sub>  | Thermal resistance junction-ambient | max. | 75 <sup>(1)</sup> | °C/W |

1. With minimized copper area.

#### Table 5.Electrical characteristcs

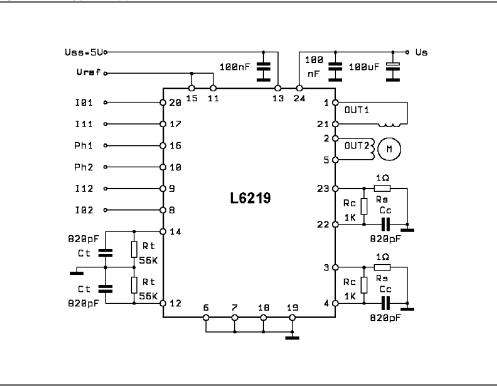

(T<sub>j</sub> = 40 °C to 125 °C, V<sub>S</sub> = 46 V, V<sub>SS</sub> = 4.75 V to 5.25 V, V<sub>REF</sub> = 5 V, unless otherwise specified) See *Figure 5*

| Parameter                                                    | Description                                | Test condition                                                                                                                                   | Min. | Тур. | Max.                       | Unit      |  |

|--------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------------|-----------|--|

| Output drivers (OUT <sub>A</sub> or OUT <sub>B</sub> )       |                                            |                                                                                                                                                  |      |      |                            |           |  |

| V <sub>S</sub> Motor supply range                            |                                            |                                                                                                                                                  | 10   | -    | 46                         | V         |  |

| ICEX                                                         | Output leakage current                     | $V_{S} = 52 V V_{OUT} = 50 V$<br>$V_{S} = 52 V V_{OUT} = 1 V$                                                                                    | -200 | -    | 200                        | μΑ<br>μΑ  |  |

|                                                              |                                            | Sink driver, $I_{OUT}$ = +500 mA<br>Sink driver, $I_{OUT}$ = +750 mA<br>Source driver, $I_{OUT}$ = -500 mA<br>Source driver, $I_{OUT}$ = -750 mA |      |      | 0.75<br>1.15<br>1.6<br>1.8 | > > > > > |  |

| V <sub>F</sub>                                               | Clamp diode forward<br>voltage             | High stage I <sub>F</sub> =750 mA<br>Low stage I <sub>F</sub> =750 mA                                                                            | -    | -    | 1.7<br>1.6                 | V<br>V    |  |

| I <sub>S(on)</sub>                                           | Driver supply current                      | Both bridges ON, no load                                                                                                                         | -    | -    | 17                         | mA        |  |

| I <sub>S(off)</sub>                                          | Driver supply current Both bridges OFF     |                                                                                                                                                  | -    | -    | 12                         | mA        |  |

| Control logi                                                 | c                                          |                                                                                                                                                  |      |      |                            |           |  |

| V <sub>IN(H)</sub>                                           | Input voltage                              | All inputs                                                                                                                                       | 2.4  | -    | -                          | V         |  |

| V <sub>IN(L)</sub>                                           | Input voltage                              | All inputs                                                                                                                                       | -    | -    | 0.8                        | V         |  |

| I <sub>IN(H)</sub>                                           | Input current                              | V <sub>IN</sub> = 2.4 V                                                                                                                          | -    | <1   | 20                         | μA        |  |

| I <sub>IN(L)</sub>                                           | Input current                              | V <sub>IN</sub> = 0.84 V                                                                                                                         | -    | -3   | -200                       | μA        |  |

| V <sub>REF</sub>                                             | Reference voltage Operating <sup>(1)</sup> |                                                                                                                                                  | 1.5  | -    | 7.5                        | V         |  |

| I <sub>SS(ON)</sub>                                          | Total logic supply current                 | $I_0 = I_1 = 0.8 \text{ V}$ , no load                                                                                                            | -    | -    | 76                         | mA        |  |

| I <sub>SS(OFF)</sub>                                         | Total logic supply current                 | $I_0 = I_1 = 2.4$ V, no load                                                                                                                     | -    | -    | 15                         | mA        |  |

| Comparator                                                   | S                                          |                                                                                                                                                  |      |      |                            |           |  |

|                                                              |                                            | $I_0 = I_1 = 0.8 V$                                                                                                                              | 9.5  | 10   | 10.5                       | -         |  |

| $V_{REF}/V_{sense}$                                          | Current limit threshold (at trip point)    | I <sub>0</sub> = 2.4 V, I <sub>1</sub> = 0.8 V                                                                                                   | 13.5 | 15   | 16.5                       | -         |  |

|                                                              |                                            | I <sub>o</sub> = 0.8 V, I <sub>1</sub> = 2.4 V                                                                                                   | 25.5 | 30   | 34.5                       | -         |  |

| $t_{off}$ Cutoff time $R_t = 56 \text{ K}\Omega \text{ C}_t$ |                                            | $R_{t} = 56 \text{ K}\Omega \text{ C}_{t} = 820 \text{ pF}$                                                                                      | -    | 50   | -                          | μs        |  |

| t <sub>d</sub> Turn off delay                                |                                            | Figure 3                                                                                                                                         | -    | 1    | -                          | μs        |  |

| Protection                                                   |                                            |                                                                                                                                                  |      |      |                            |           |  |

| Т <sub>Ј</sub>                                               | Thermal shutdown temperature               |                                                                                                                                                  | -    | 170  | -                          | °C        |  |

1. To reduce the switching losses the base bias of the bridge's low side NPN transistor is proportional to the DAC output, then the output current driving capability is also proportional to the DAC output voltage, having as reference 750 mA with  $V_{REF} = 5$  V and DAC =100%. For example using  $V_{REF} = 2$  V and DAC = 67% the output maximum current driving capability will become 750 mA\*(2V\*0.67)/(5V\*1) = 200 mA.

## 2 Functional description

The circuit is intended to drive both windings of a bipolar stepper motor.

The peak current control is generated through switch mode regulation. There is a choice of three different current levels with the two logic inputs  $I_{01} - I_{11}$  for winding 1 and  $I_{02} - I_{12}$  for winding 2.

The current can also be switched off completely.

## 2.1 Input logic ( $I_0$ and $I_1$ )

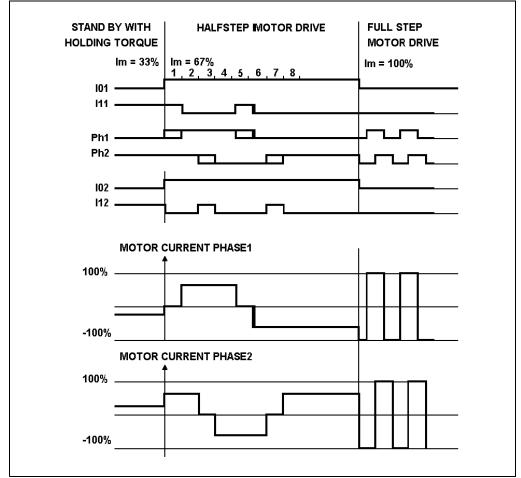

The current level in the motor winding is selected with these inputs. (See *Figure 4*). If any of the logic inputs is left open, the circuit will treat it has a high level input.

| I <sub>O</sub> | I <sub>1</sub> | Current level                         |

|----------------|----------------|---------------------------------------|

| Н              | Н              | No current                            |

| L              | Н              | Low current 1/3 I <sub>O</sub> max    |

| Н              | L              | Medium current 2/3 I <sub>O</sub> max |

| L              | L              | Maximum current I <sub>O</sub> max    |

Table 6.Current levels

### 2.2 Phase

This input determines the direction of current flow in the windings, depending on the motor connections. The signal is fed through a schmidt-trigger for noise immunity, and through a time delay in order to guarantee that no short-circuit occurs in the output stage during phase-shift. High level on the phase input causes the motor current flow from out A through the winding to out B.

### 2.3 Current sensor

This part contains a current sensing resistor ( $R_S$ ), a low pass filter ( $R_C$ ,  $C_C$ ) and three comparators. Only one comparator is active at a time. It is activated by the input logic according to the current level chosen with signals  $I_o$  and  $I_1$ . The motor current flows through the sensing resistor  $R_S$ . When the current has increased so that the voltage across  $R_S$  becomes higher than the reference voltage on the other comparator input, the comparator goes high, which triggers the pulse generator.

The max peak current I<sub>max</sub> can be defined by:

$$I_{max} = \frac{V_{ref}}{10R_s}$$

9/15

The pulse generator is a monostable triggered on the positive going edge of the comparator output. The monostable output is high during the pulse time, toff, which is determined by the time components  $R_t$  and  $C_t$ .

$$t_{off} = 1.1 \cdot R_t C_t$$

The single pulse switches off the power feed to the motor winding, causing the winding current to decrease during  $t_{off}$ . If a new trigger signal should occur during  $t_{off}$ , it is ignored.

## 2.5 Output stage

The output stage contains four darlington transistors (source drivers) four saturated transistors (sink drivers) and eight diodes, connected in two H bridge.

Figure 4. Principle operating sequence

The source transistors are used to switch the power supplied to the motor winding, thus driving a constant current through the winding. It should be noted however, that is not permitted to short circuit the outputs.

Internal circuitry is added in order to increase the accuracy of the motor current particularly with low current levels.

## 2.6 $V_S, V_{SS}, V_{Ref}$

The circuit will stand any order of turn-on or turn-off the supply voltages  $V_{\rm S}$  and  $V_{\rm SS}$ . Normal dV/dt values are then assumed.

Preferably,  $V_{Ref}$  should be tracking  $V_{SS}$  during power-on and power-off if  $V_S$  is established.

## **3** Application information

Some stepper motors are not designed for contin-uous operation at maximum current. As the circuit drives a constant current through the motor, its temperature might increase exceedingly both at low and high speed operation. Also, some stepper motors have such high core losses that they are not suited for switch mode current regulation.

Unused inputs should be connected to proper voltage levels in order to get the highest noise immunity. As the circuit operates with switch mode current regulation, interference generation problems might arise in some applications. A good measure might then be to decouple the circuit with a 100 nF capacitor, located near the package between power line and ground. The ground lead between  $R_s$ , and circuit GND should be kept as short as possible. A typical application circuit is shown in *Figure 5*. Note that  $C_t$  must be NPO type or similar else. To sense the winding current, paralleled metal film resistors are recommended ( $R_s$ ).

#### Figure 5. Typical application circuit

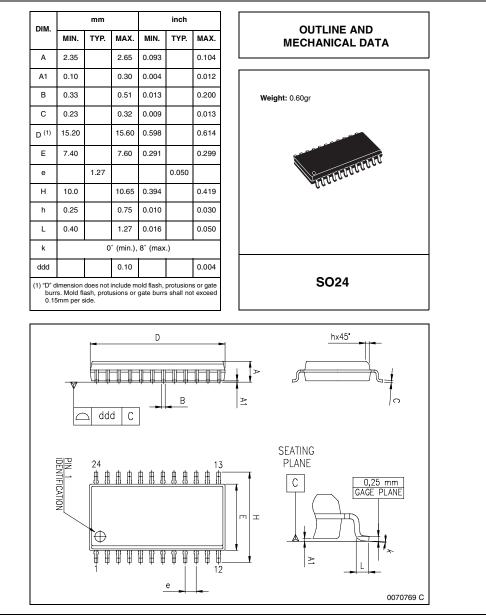

## 4 Package information

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 6. SO24 mechanical data and package dimensions

# 5 Revision history

### Table 7. Document revision history

| Date        | Revision | Changes                            |

|-------------|----------|------------------------------------|

| 12-Nov-1998 | 1        | First Issue                        |

| 29-Apr-2008 | 2        | Document reformatted.              |

| 05-Sep-2008 | 3        | Added note 1 in Table 5 on page 8. |

14/15

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

15/15