# Hex-Half-Bridge / Double Six-Driver

# TLE 6208-6 G SPT 4

#### 1 Overview

#### 1.1 Features

- Six High-Side and six Low-Side-Drivers

- Free configurable as switch, halfbridge or H-bridge

- Optimized for DC motor management applications

- 0.6 A continuous (1 A peak) current per switch

- $R_{\rm DS \,ON}$ ; typ. 0.8  $\Omega$ , @ 25 °C per switch

- Outputs fully short circuit protected with diagnosis

- Overtemperature-Protection with hysteresis and diagnosis

- · Temperature prewarning

- Standard SPI-Interface

- Very low current consumption (typ. 10  $\mu$ A, @ 25 °C) in stand-by (Inhibit) mode

- Over- and Undervoltage-Lockout

- CMOS/TTL compatible inputs with hysteresis

- Internal clamp diodes

- Enhanced power P-DSO-Package

- Green Product (RoHS compliant)

- AEC Qualified

| Туре         | Package      |

|--------------|--------------|

| TLE 6208-6 G | PG-DSO-28-24 |

#### **Functional Description**

The TLE 6208-6 G is a fully protected **Hex-Half-B**ridge-**D**river designed specifically for automotive and industrial motion control applications. The part is based on Infineons Smart Power Technology SPT® which allows bipolar and CMOS control circuitry in accordance with DMOS power devices existing on the same monolithic circuitry. The six low and high side drivers are freely configurable and can be controlled separately. Therefore all kind of loads can be combined. In motion control up to 5 actuators (DC-Motors) can be connected to the 6 halfbridge-outputs (cascade configuration). Operation modes forward (cw), reverse (ccw), brake and high impedance are controlled from a standard SPI-Interface. The possibility to control the outputs via software from a central logic, allows limiting the power dissipation. So the standard PG-DSO-28-24-package meets the application requirements and saves PCB-Board-space and cost.

Furthermore the build-in features like Over- and Undervoltage-Lockout, Over-Temperature-Protection and the very low quiescent current in stand-by mode opens a wide range of automotive- and industrial-applications.

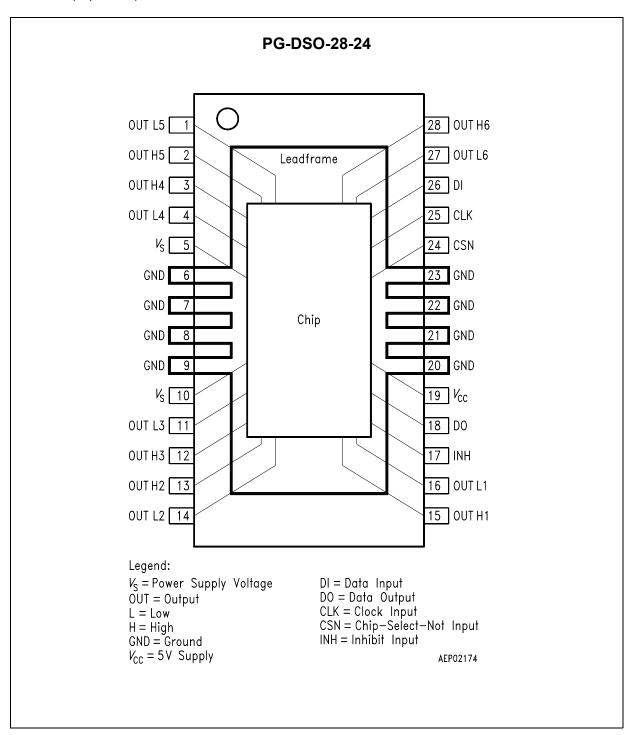

# 1.2 Pin Configuration

(top view)

Figure 1

# 1.3 Pin Definitions and Functions

| Pin No.    | Symbol       | Function                                                                                                                                                                                                                     |

|------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | OUTL5        | Low-Side-Output 5; Power-MOS open drain with internal reverse diode; no internal clamp diode or active zenering; short circuit protected and open load controlled.                                                           |

| 2          | OUTH5        | High-Side-Output 5; Power-MOS open source with internal reverse diode; no internal clamp diode or active zenering; short circuit protected and open load controlled.                                                         |

| 3          | OUTH4        | High-Side-Output 4; see pin2.                                                                                                                                                                                                |

| 4          | OUTL4        | Low-Side-Output 4; see pin1.                                                                                                                                                                                                 |

| 5          | $V_{S}$      | Power supply; external connection to pin 10 necessary; needs a blocking capacitor as close as possible to GND Value: 22 μF electrolytic in parallel to 220 nF ceramic.                                                       |

| 6, 7, 8, 9 | GND          | <b>Ground;</b> Reference potential; internal connection to pin 20, 21, 22 and 23; cooling tab; to reduce thermal resistance; place cooling areas on PCB close to this pins.                                                  |

| 10         | $V_{S}$      | Power Supply; see pin 5.                                                                                                                                                                                                     |

| 11         | OUTL3        | Low-Side-Output 3; see pin1.                                                                                                                                                                                                 |

| 12         | OUTH3        | High-Side-Output 3; see pin2.                                                                                                                                                                                                |

| 13         | OUTH2        | High-Side-Output 2; see pin2.                                                                                                                                                                                                |

| 14         | OUTL2        | Low-Side-Output 2; see pin1.                                                                                                                                                                                                 |

| 15         | OUTH1        | High-Side-Output 1; see pin2.                                                                                                                                                                                                |

| 16         | OUTL1        | Low-Side-Output 1; see pin1.                                                                                                                                                                                                 |

| 17         | INH          | Inhibit input; has an internal pull down; device is switched in standby condition by pulling the INH terminal low.                                                                                                           |

| 18         | DO           | Serial-Data-Output; this 3-state output transfers diagnosis data to the control device; the output will remain 3-stated unless the device is selected by a low on Chip-Select-Not (CSN); see Table 2 for Diagnosis protocol. |

| 19         | $V_{\sf cc}$ | <b>Logic supply voltage</b> ; needs a blocking capacitor as close as possible to GND; Value: $10  \mu F$ electrolytic in parallel to 220 nF ceramic.                                                                         |

# **1.3** Pin Definitions and Functions (cont'd)

| Pin No.           | Symbol | Function                                                                                                                                                                                                                                                                                                                                                  |

|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20, 21,<br>22, 23 | GND    | Ground                                                                                                                                                                                                                                                                                                                                                    |

| 24                | CSN    | Chip-Select-Not input; CSN is an active low input; serial communication is enabled by pulling the CSN terminal low; CSN input should only be transitioned when CLK is low; CSN has an internal active pull up and requires CMOS logic level inputs.                                                                                                       |

| 25                | CLK    | Serial clock input; clocks the shiftregister; CLK has an internal active pull down and requires CMOS logic level inputs.                                                                                                                                                                                                                                  |

| 26                | DI     | Serial data input; receives serial data from the control device; serial data transmitted to DI is an 16bit control word with the Least Significant Bit (LSB) being transferred first: the input has an active pull down and requires CMOS logic level inputs; DI will accept data on the falling edge of CLK-signal; see Table 1 for input data protocol. |

| 27                | OUTL6  | Low-Side-Output 6; see pin1.                                                                                                                                                                                                                                                                                                                              |

| 28                | OUTH6  | High-Side-Output 6; see pin2.                                                                                                                                                                                                                                                                                                                             |

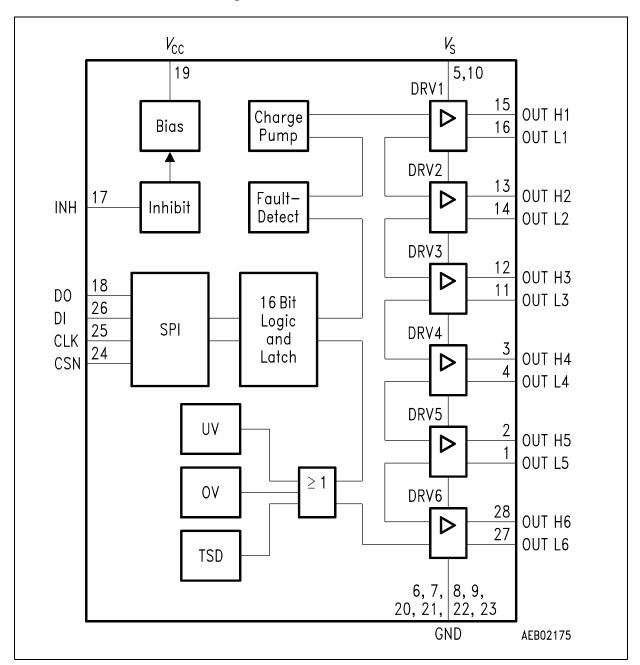

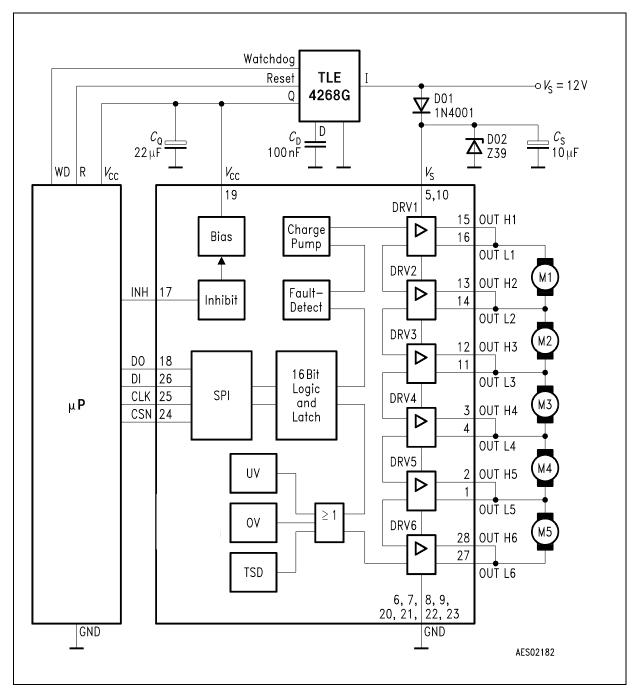

#### 1.4 Functional Block Diagram

Figure 2 Block Diagram TLE 6208-6 G

#### 1.5 Circuit Description

Figure 2 shows a block schematic diagram of the module.

There are 6 halfbridge drivers on the right-hand side. An HS driver and an LS driver are combined to form a halfbridge driver in each case.

The drivers communicate via the internal data bus with the logic and the other control and monitoring functions: undervoltage (UV), overvoltage (OV), overtemperature (TSD), charge pump and fault detect.

Two connection interfaces are provided for supply to the module: All power drivers are connected to the supply voltage  $V_{\rm S}$ . These are monitored by overvoltage and undervoltage comparators with hysteresis, so that the correct function can be checked in the application at any time.

The logic is supplied by the  $V_{\rm CC}$  voltage, typ. with 5 V. The  $V_{\rm CC}$  voltage uses an internally generated Power-On Reset (POR) to initialize the module at power-on. The advantage of this system is that information stored in the logic remains intact in the event of short-term failures in the supply voltage  $V_{\rm S}$ . The system can therefore continue to operate following  $V_{\rm S}$  undervoltage, without having to be reprogrammed. The "undervoltage" information is stored, and can be read out via the interface. The same logically applies for overvoltage. "Interference spikes" on  $V_{\rm S}$  are therefore effectively suppressed.

The situation is different in the case of undervoltage on the  $V_{\rm CC}$  connection pin. If this occurs, then the internally stored data is deleted, and the output levels are switched to high-impedance status (tristate). The module is initialized by  $V_{\rm CC}$  following restart (Power-On Reset = POR).

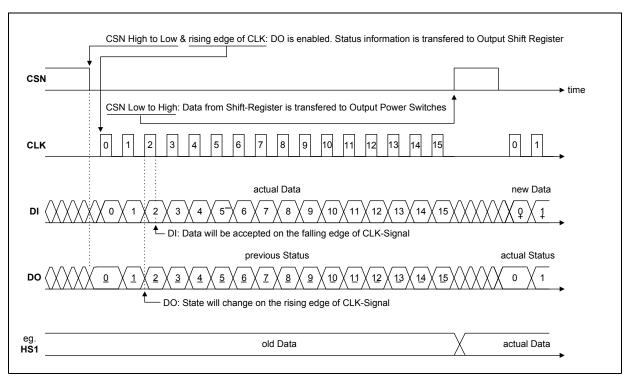

The 16-bit wide programming word or control word (see **Table 1**) is read in via the DI data input, and this is synchronized with the clock input CLK. The status word appears synchronously at the DO data output (see **Table 2**).

The transmission cycle begins when the chip is selected with the CSN input (H to L). If the CSN input changes from L to H then the word which has been read in becomes the control word. The DO output switches to tristate status at this point, thereby releasing the DO bus circuit for other uses.

The INH inhibit input can be used to cut off the complete module. This reduces the current consumption to just a few  $\mu A$ , and results in the loss of any data stored. The output levels are switched to tristate status. The module is reinitialized with the internally generated POR (Power-On Reset) at restart.

This feature allows the use of this module in battery-operated applications (vehicle body control applications).

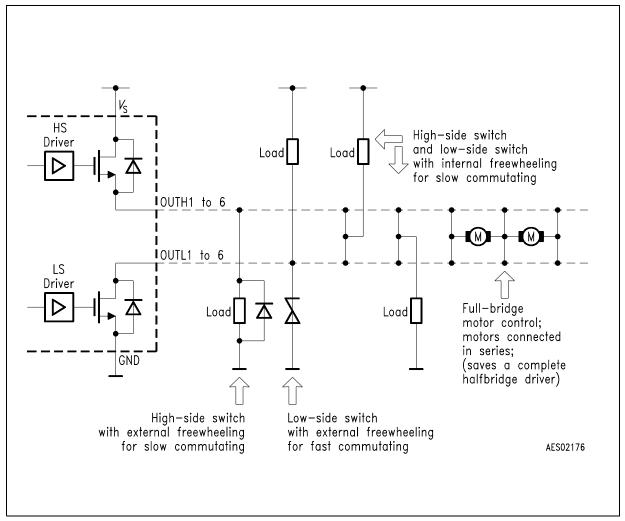

Every driver block from DRV 1 to 6 contains a low-side driver and a high-side driver. The output connections have been selected so that each HS driver and LS driver pair can be combined to form a halfbridge by short-circuiting adjacent connections. The full flexibility of the configuration can be achieved by dissecting the halfbridges into "quarter-bridges". **Table 3** shows examples of possible applications.

When commutating inductive loads, the dissipated power peak can be significantly reduced by activating the transistor located parallel to the internal freewheeling diode. A special, integrated "timer" for power ON/OFF times ensures there is no crossover current at the halfbridge.

Figure 3

Configuration Examples for "Quarter Bridges" on the TLE 6208-6 G

Table 1 Input Data Protocol

| BIT |                       |

|-----|-----------------------|

| 15  | OVLO on/off           |

| 14  | Underload SD on/off   |

| 13  | Overcurrent SD on/off |

| 12  | HS-Switch 6           |

| 11  | LS-Switch 6           |

| 10  | HS-Switch 5           |

| 9   | LS-Switch 5           |

| 8   | HS-Switch 4           |

| 7   | LS-Switch 4           |

| 6   | HS-Switch 3           |

| 5   | LS-Switch 3           |

| 4   | HS-Switch 2           |

| 3   | LS-Switch 2           |

| 2   | HS-Switch 1           |

| 1   | LS-Switch 1           |

| 0   | Status Register Reset |

|     | •                     |

H = ON L = OFF

Table 2

Diagnosis Data Protocol

| BIT |                    |

|-----|--------------------|

| 15  | Power supply fail  |

| 14  | Underload          |

| 13  | Overload           |

| 12  | Status HS-Switch 6 |

| 11  | Status LS-Switch 6 |

| 10  | Status HS-Switch 5 |

| 9   | Status LS-Switch 5 |

| 8   | Status HS-Switch 4 |

| 7   | Status LS-Switch 4 |

| 6   | Status HS-Switch 3 |

| 5   | Status LS-Switch 3 |

| 4   | Status HS-Switch 2 |

| 3   | Status LS-Switch 2 |

| 2   | Status HS-Switch 1 |

| 1   | Status LS-Switch 1 |

| 0   | Temp. Prewarning   |

|     |                    |

H = ON L = OFF

Table 3

Fault Result Table

| Fault                                          | DiagBit | Result                                                                                            |  |  |  |  |

|------------------------------------------------|---------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| Overcurrent (load)                             | 13      | Only the failed output is switched OFF. Function and protection can be deactivated by bit No. 13. |  |  |  |  |

| Short circuit to GND (high-side-switch)        | 13      | Only the failed output is switched OFF. Function and protection can be deactivated by bit No. 13. |  |  |  |  |

| Short circuit to $V_{\rm S}$ (low-side-switch) | 13      | Only the failed output is switched OFF. Function and protection can be deactivated by bit No. 13. |  |  |  |  |

| Temperature warning                            | 0       | Reaction of control device needed.                                                                |  |  |  |  |

| Temperature shut down (SD)                     | _       | All outputs OFF.                                                                                  |  |  |  |  |

| Openload                                       | 14      | Only the failed output is switched OFF. Function can be deactivated by bit No. 14.                |  |  |  |  |

| Underload                                      | 14      | Only the failed output is switched OFF. Function can be deactivated by bit No. 14.                |  |  |  |  |

| Undervoltage lockout (UVLO)                    | 15      | All outputs OFF.                                                                                  |  |  |  |  |

| Overvoltage lockout (OVLO)                     | 15      | All outputs OFF. Function can be deactivated by bit No. 15.                                       |  |  |  |  |

H = failure;

L = no failure.

#### 2 **Electrical Characteristics**

#### **Absolute Maximum Ratings** 2.1

| Parameter Symbo                          |              | Limit values |              | Unit | Remarks                                                                                      |

|------------------------------------------|--------------|--------------|--------------|------|----------------------------------------------------------------------------------------------|

|                                          |              | min.         | max.         |      |                                                                                              |

| Voltages                                 |              |              |              |      |                                                                                              |

| Supply voltage                           | $V_{S}$      | - 0.3        | 40           | V    | _                                                                                            |

| Supply voltage                           | $V_{S}$      | <b>–</b> 1   | _            | V    | $t < 0.5 \text{ s}; I_{\text{S}} > -2 \text{ A}$                                             |

| Logic supply voltage                     | $V_{\sf CC}$ | - 0.3        | 5.5          | V    | 0 V < V <sub>S</sub> < 40 V                                                                  |

| Logic input voltages (DI, CLK, CSN, INH) | $V_1$        | - 0.3        | 5.5          | V    | $0 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$0 \text{ V} < V_{\text{CC}} < 5.5 \text{ V}$ |

| Logic output voltage (DO)                | $V_{DO}$     | - 0.3        | $V_{\sf CC}$ | V    | $0 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$0 \text{ V} < V_{\text{CC}} < 5.5 \text{ V}$ |

#### Currents

| Output current (cont.), if Bit13 (OCSD) is set. | $I_{	ext{OUT1-6}}$ | _      | _    | А | internal limited       |

|-------------------------------------------------|--------------------|--------|------|---|------------------------|

| Output current (cont.),                         | $I_{	ext{OUT1-6}}$ | - 1.5  | 1.5  | Α | $V_{\rm DS}$ = 12 V    |

| if Bit13 (OCSD) is deactivated.                 |                    | - 0.7  | 0.7  | Α | $V_{\rm DS}$ = 20 V    |

|                                                 |                    | - 0.25 | 0.25 | Α | $V_{\rm DS}$ = 40 V    |

| Output current (peak), if Bit13 (OCSD) is set.  | $I_{OUT1-6}$       | _      | _    | А | internal limited       |

| Output current (peak),                          | $I_{	ext{OUT1-6}}$ | - 2    | 2    | Α | $V_{\rm DS}$ = 12 V    |

| if Bit13 (OCSD) is deactivated.                 |                    | - 0.9  | 0.9  | Α | V <sub>DS</sub> = 20 V |

| $t_{P}$ < 50 ms; $t$ = 1 s;                     |                    | - 0.3  | 0.3  | А | V <sub>DS</sub> = 40 V |

#### **Temperatures**

| Junction temperature | $T_{\rm j}$  | <b>- 40</b> | 150 | °C | _ |

|----------------------|--------------|-------------|-----|----|---|

| Storage temperature  | $T_{ m stg}$ | <b>-</b> 50 | 150 | °C | _ |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

# 2.2 Operating Range

| Parameter                               | Symbol                               | Limit Values   |              | Unit | Remarks                                       |

|-----------------------------------------|--------------------------------------|----------------|--------------|------|-----------------------------------------------|

|                                         |                                      | min.           | max.         |      |                                               |

| Supply voltage                          | $V_{S}$                              | $V_{ m UVOFF}$ | 40           | V    | After $V_{\rm S}$ rising above $V_{\rm UVON}$ |

| Supply voltage slew rate                | $\mathrm{d}V_\mathrm{S}/\mathrm{d}t$ | _              | 10           | V/μs | _                                             |

| Logic supply voltage                    | $V_{\sf CC}$                         | 4.75           | 5.50         | V    | _                                             |

| Supply voltage increasing               | $V_{S}$                              | - 0.3          | $V_{UVON}$   | V    | Outputs in tristate                           |

| Supply voltage decreasing               | $V_{S}$                              | - 0.3          | $V_{UVOFF}$  | V    | Outputs in tristate                           |

| Logic input voltage (DI, CLK, CSN, INH) | $V_1$                                | - 0.3          | $V_{\sf CC}$ | V    | _                                             |

| SPI clock frequency                     | $f_{CLK}$                            | _              | 2            | MHz  | _                                             |

| Junction temperature                    | $T_{\rm j}$                          | <b>- 40</b>    | 150          | °C   | _                                             |

# **Thermal Resistances**

| Junction pin     | $R_{	ext{thj-pin}}$ | _ | 25 | K/W | measured to pin 7 |

|------------------|---------------------|---|----|-----|-------------------|

| Junction ambient | $R_{thjA}$          | _ | 65 | K/W | _                 |

#### 2.3 Electrical Characteristics

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

# **Current Consumption**

| Quiescent current    | $I_{\mathbb{S}}$ | _ | 10  | 20  | μΑ | INH = Low;<br>$V_{\rm S}$ = 13.2 V;<br>$T_{\rm j}$ = 25 °C |

|----------------------|------------------|---|-----|-----|----|------------------------------------------------------------|

| Quiescent current    | $I_{S}$          | _ | _   | 40  | μΑ | INH = Low; $V_{\rm S}$ = 13.2 V                            |

| Supply current       | $I_{\mathbb{S}}$ | _ | 2.0 | 4.0 | mA | _                                                          |

| Logic-Supply current | $I_{CC}$         | _ | 2   | 10  | μΑ | INH = Low                                                  |

| Logic-Supply current | $I_{CC}$         | _ | 1.6 | 3.0 | mA | SPI not active                                             |

# **Over- and Under-Voltage Lockout**

| UV-Switch-ON voltage  | $V_{UVON}$  | _   | 6.5 | 7.0 | V | $V_{ m S}$ increasing        |

|-----------------------|-------------|-----|-----|-----|---|------------------------------|

| UV-Switch-OFF voltage | $V_{UVOFF}$ | 5.5 | 6.0 | 6.6 | V | $V_{\rm S}$ decreasing       |

| UV-ON/OFF-Hysteresis  | $V_{UVHY}$  | _   | 0.5 | _   | V | $V_{ m UVON} - V_{ m UVOFF}$ |

| OV-Switch-OFF voltage | $V_{OVOFF}$ | 34  | 37  | 40  | V | $V_{\rm S}$ increasing       |

| OV-Switch-ON voltage  | $V_{OVON}$  | 28  | 32  | 36  | V | $V_{\rm S}$ decreasing       |

| OV-ON/OFF-Hysteresis  | $V_{OVHY}$  | _   | 5.0 | _   | V | $V_{ m OVOFF}-V_{ m OVON}$   |

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

# **Outputs OUTH1-6 and OUTL1-6**

#### Static Drain-Source-On Resistance

| Source (High-Side) $I_{\text{OUT}} = -0.5 \text{ A}$        | $R_{DS\;ON\;H}$ | _ | 0.9 | 1.3 | Ω | $8 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$       |

|-------------------------------------------------------------|-----------------|---|-----|-----|---|-------------------------------------------------------------------------------------|

|                                                             |                 |   | _   | 2.0 | Ω | 8 V < V <sub>S</sub> < 40 V                                                         |

|                                                             |                 |   | 2.0 | _   | Ω | $V_{\text{S OFF}} < V_{\text{S}} \le 8 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$ |

|                                                             |                 |   | _   | 4.0 | Ω | $V_{\rm SOFF}$ < $V_{\rm S}$ $\leq$ 8 V                                             |

| Sink (Low-Side) $R_{\rm DS \ ON \ L}$ $I_{\rm OUT}$ = 0.5 A | $R_{DS\;ON\;L}$ |   | 8.0 | 1.2 | Ω | $8 \text{ V} < V_{\text{S}} < 40 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$       |

|                                                             |                 |   | _   | 2.0 | Ω | $8 \text{ V} < V_{\text{S}} < 40 \text{ V}$                                         |

|                                                             |                 |   | 2.0 | _   | Ω | $V_{\text{S OFF}} < V_{\text{S}} \le 8 \text{ V}$<br>$T_{\text{j}} = 25 \text{ °C}$ |

|                                                             |                 |   | _   | 4.0 | Ω | $V_{\rm SOFF}$ < $V_{\rm S}$ $\leq$ 8 V                                             |

Note: Values of  $R_{\rm DS\,ON}$  for  $V_{\rm S\,OFF}$  <  $V_{\rm S}$   $\leq$  8 V are guaranteed by design.

## **Leakage Current**

| Source-Output-Stage 1 to 6 | $I_{QLH}$ | <u> </u> | _ | _ | μΑ | $V_{\text{OUTH1-6}} = 0 \text{ V}$<br>$T_{\text{j}} = 25 ^{\circ}\text{C}$  |

|----------------------------|-----------|----------|---|---|----|-----------------------------------------------------------------------------|

| Source-Output-Stage 1 to 6 | $I_{QLH}$ | - 5      | _ | _ | μΑ | $V_{\text{OUTH1-6}}$ = 0 V                                                  |

| Sink-Output-Stage 1 to 6   | $I_{QLL}$ | _        | _ | 1 | μΑ | $V_{\text{OUTL1-6}} = V_{\text{S}}$<br>$T_{\text{j}} = 25 ^{\circ}\text{C}$ |

| Sink-Output-Stage 1 to 6   | $I_{QLL}$ | _        | _ | 5 | μΑ | $V_{\text{OUTL1-6}} = V_{\text{S}}$                                         |

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### **Overcurrent**

| Source shutdown threshold | $I_{SDU}$     | - 2.0 | - 1.5 | - 1.0 | А  | _               |

|---------------------------|---------------|-------|-------|-------|----|-----------------|

| Sink shutdown threshold   | $I_{SDL}$     | 1.0   | 1.5   | 2.0   | Α  | _               |

| Current limit             | $I_{OCL}$     | _     | 3.0   | 5.0   | Α  | sink and source |

| Shutdown delay time       | $t_{\sf dSD}$ | 10    | 25    | 50    | μs | sink and source |

## **Open Circuit**

| Detection current | $I_{OCD}$     | 15  | 30  | 50  | mA | _ |

|-------------------|---------------|-----|-----|-----|----|---|

| Delay time        | $t_{\sf dOC}$ | 200 | 350 | 600 | μs | _ |

## Delay Time from Stand-by to Data In

| Setup time | $t_{set}$ | _ | _ | 100 | μs  | _ |

|------------|-----------|---|---|-----|-----|---|

|            |           |   |   |     | l - |   |

Note: setup time is guarnteed by design

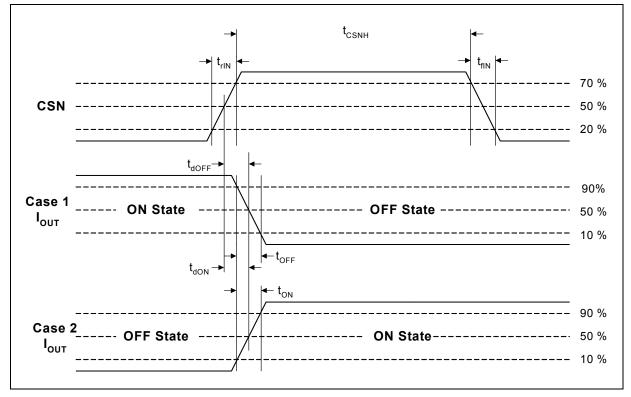

# Output Delay Times; $V_s$ = 13.2 V; $R_{Load}$ = 25 $\Omega$ (device not in stand-by for t > 1 ms)

| Source (high-side) ON  | $t_{ m d\ ON\ H}$    | _   | 7.5 | 12 | μs | _                                  |

|------------------------|----------------------|-----|-----|----|----|------------------------------------|

| Source (high-side) OFF | t <sub>d OFF H</sub> | _   | 3   | 6  | μs | _                                  |

| Sink (low-side) ON     | t <sub>d ON L</sub>  | _   | 6.5 | 12 | μs | _                                  |

| Sink (low-side) OFF    | t <sub>d OFF L</sub> | _   | 2   | 5  | μs | _                                  |

| Dead time H to L       | $t_{DHL}$            | 1.5 | _   | _  | μs | $t_{\rm d~ON~L} - t_{\rm d~OFF~H}$ |

| Dead time L to H       | $t_{ m DLH}$         | 2.5 | _   | _  | μs | $t_{\rm d~ON~H} - t_{\rm d~OFf~L}$ |

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

# Output Switching Times; $V_{\rm S}$ = 13.2 V; $R_{\rm Load}$ = 25 $\Omega$ (device not in stand-by for t > 1 ms)

| Source (high-side) rise-time | t <sub>ON H</sub>  | _ | 4 | 8 | μs | _ |

|------------------------------|--------------------|---|---|---|----|---|

| Source (high-side) fall-time | t <sub>OFF H</sub> | _ | 2 | 3 | μs | _ |

| Sink (low-side) fall-time    | t <sub>ON L</sub>  | _ | 1 | 3 | μs | _ |

| Sink (low-side) rise-time    | t <sub>OFF L</sub> | _ | 1 | 2 | μs | _ |

# **Clamp Diodes Forward Voltage**

| Upper | $V_{FU}$ | _ | 0.9 | 1.3 | V | $I_{\rm F}$ = 0.5 A |

|-------|----------|---|-----|-----|---|---------------------|

| Lower | $V_{FL}$ | _ | 0.9 | 1.3 | V | $I_{\rm F}$ = 0.5 A |

## **Inhibit Input**

| H-input voltage threshold   | $V_{IH}$  | _   | _   | 0.7 | $V_{\sf CC}$ | _                                |

|-----------------------------|-----------|-----|-----|-----|--------------|----------------------------------|

| L-input voltage threshold   | $V_{IL}$  | 0.2 | _   | _   | $V_{\sf CC}$ | _                                |

| Hysteresis of input voltage | $V_{IHY}$ | 50  | 200 | 500 | mV           | _                                |

| Pull down current           | $I_{I}$   | 10  | 25  | 50  | μΑ           | $V_{\rm I}$ = 0.2 × $V_{\rm CC}$ |

| Input capacitance           | $C_{I}$   | _   | 10  | 15  | pF           | 0 V < V <sub>CC</sub> < 5.25 V   |

Note: Capacitances are guaranteed by design

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Lin  | Limit Values |      | Unit | Test Condition |

|-----------|--------|------|--------------|------|------|----------------|

|           |        | min. | typ.         | max. |      |                |

## SPI-Interface Delay Time from Stand-by to Data In

| Setup time | $t_{set}$ | _ | _ | 100 | μs | _ |

|------------|-----------|---|---|-----|----|---|

| •          | 001       |   |   |     |    |   |

# Logic Inputs DI, CLK and CSN

| H-input voltage threshold               | $V_{IH}$   | _    | _    | 0.7         | $V_{\sf CC}$ | _                                           |

|-----------------------------------------|------------|------|------|-------------|--------------|---------------------------------------------|

| L-input voltage threshold               | $V_{IL}$   | 0.2  | _    | _           | $V_{\sf CC}$ | _                                           |

| Hysteresis of input voltage             | $V_{IHY}$  | 50   | 200  | 500         | mV           | _                                           |

| Pull up current at pin CSN              | $I_{ICSN}$ | - 50 | - 25 | <b>–</b> 10 | μΑ           | $V_{\rm CSN}$ = 0.7 × $V_{\rm CC}$          |

| Pull down current at pin DI             | $I_{IDI}$  | 10   | 25   | 50          | μΑ           | $V_{\mathrm{DI}}$ = 0.2 × $V_{\mathrm{CC}}$ |

| Pull down current at pin CLK            | $I_{ICLK}$ | 10   | 25   | 50          | μΑ           | $V_{\rm CLK}$ = 0.2 × $V_{\rm CC}$          |

| Input capacitance at pin CSN, DI or CLK | $C_{I}$    | _    | 10   | 15          | pF           | 0 V < V <sub>CC</sub> < 5.25 V              |

Note: Capacitances are guaranteed by design

# **Logic Output DO**

| H-output voltage level      | $V_{DOH}$  | V <sub>CC</sub> – 1.0 | V <sub>CC</sub> – 0.7 | _   | V  | $I_{\text{DOH}}$ = 1 mA                                                        |

|-----------------------------|------------|-----------------------|-----------------------|-----|----|--------------------------------------------------------------------------------|

| L-output voltage level      | $V_{DOL}$  | _                     | 0.2                   | 0.4 | V  | $I_{\rm DOL}$ = $-$ 1.6 mA                                                     |

| Tri-state leakage current   | $I_{DOLK}$ | <b>– 10</b>           | _                     | 10  | μΑ | $V_{\text{CSN}} = V_{\text{CC}}$ $0 \text{ V} < V_{\text{DO}} < V_{\text{CC}}$ |

| Tri-state input capacitance | $C_{DO}$   | _                     | 10                    | 15  | pF | $V_{\rm CSN} = V_{\rm CC}$<br>0 V < $V_{\rm CC}$ < 5.25 V                      |

Note: Capacitances are guaranteed by design

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Lin  | Limit Values |      |  | Test Condition |

|-----------|--------|------|--------------|------|--|----------------|

|           |        | min. | typ.         | max. |  |                |

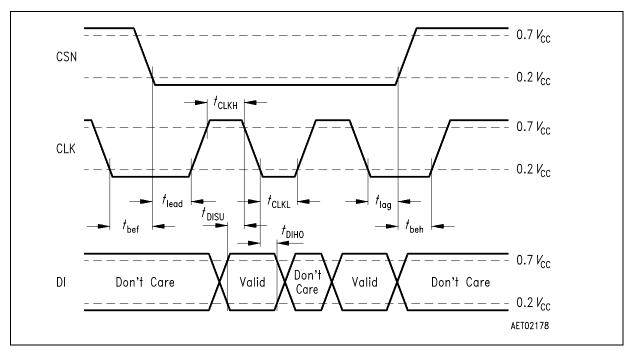

# **Data Input Timing**

| Clock period                                  | $t_{pCLK}$     | 500 | - | _   | ns | _ |

|-----------------------------------------------|----------------|-----|---|-----|----|---|

| Clock high time                               | $t_{CLKH}$     | 250 | _ | _   | ns | _ |

| Clock low time                                | $t_{CLKL}$     | 250 | - | _   | ns | _ |

| Clock low before CSN low                      | $t_{bef}$      | 250 | _ | _   | ns | _ |

| CSN setup time                                | $t_{lead}$     | 250 | _ | _   | ns | _ |

| CSN high time                                 | $t_{CSNH}$     | 12  | _ | _   | μs | _ |

| CLK setup time                                | $t_{lag}$      | 250 | _ | _   | ns | _ |

| Clock low after CSN high                      | $t_{\sf beh}$  | 250 | _ | _   | ns | _ |

| DI setup time                                 | $t_{\sf DISU}$ | 40  | _ | _   | ns | _ |

| DI hold time                                  | $t_{DIHO}$     | 40  | _ | _   | ns | _ |

| Input signal rise time at pin DI, CLK and CSN | $t_{\sf rIN}$  | _   | _ | 200 | ns | - |

| Input signal fall time at pin DI, CLK and CSN | $t_{fIN}$      |     | _ | 200 | ns | - |

|                                               |                |     |   |     |    |   |

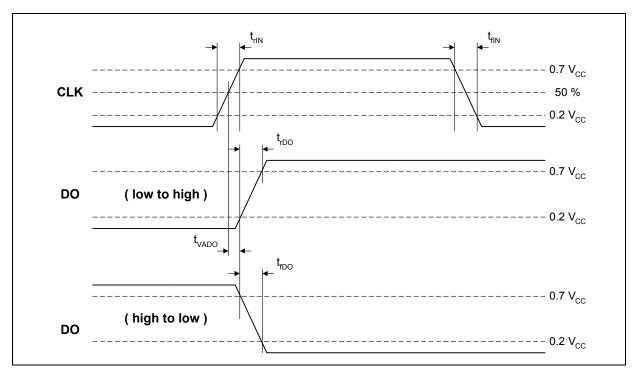

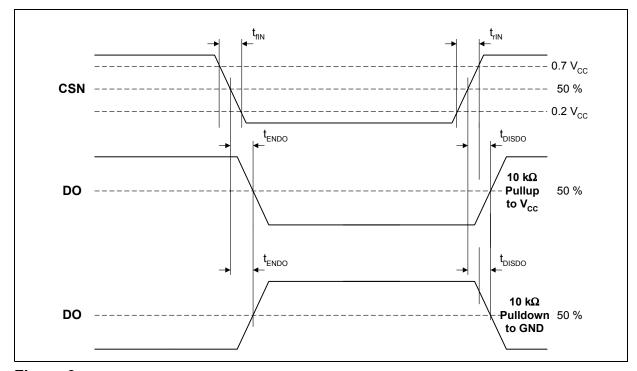

# **Data Output Timing**

| DO rise time    | $t_{rDO}$       | _ | 50  | 100 | ns | <i>C</i> <sub>L</sub> = 100 pF                                                           |

|-----------------|-----------------|---|-----|-----|----|------------------------------------------------------------------------------------------|

| DO fall time    | $t_{fDO}$       | _ | 50  | 100 | ns | $C_{\rm L}$ = 100 pF                                                                     |

| DO enable time  | $t_{ENDO}$      | - | _   | 250 | ns | low impedance                                                                            |

| DO disable time | $t_{\sf DISDO}$ | _ | _   | 250 | ns | high impedance                                                                           |

| DO valid time   | $t_{VADO}$      | _ | 100 | 250 | ns | $V_{\rm DO}$ < 0.2 $V_{\rm CC}$ ; $V_{\rm DO}$ > 0.7 $V_{\rm CC}$ ; $C_{\rm L}$ = 100 pF |

Note: SPI timing ia guaranteed by design. CSN high time: This is the minimum time the user must wait between SPI commands.

8 V <  $V_{\rm S}$  < 40 V; 4.75 V <  $V_{\rm CC}$  < 5.25 V; INH = High; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; unless otherwise specified

| Parameter | Symbol | Lin  | Limit Values |      |  | Test Condition |

|-----------|--------|------|--------------|------|--|----------------|

|           |        | min. | typ.         | max. |  |                |

# **Thermal Prewarning and Shutdown**

| Thermal prewarning junction temperature | $T_{jPW}$                    | 120  | 145  | 170 | °C | _ |

|-----------------------------------------|------------------------------|------|------|-----|----|---|

| Temperature prewarning hysteresis       | $\Delta T$                   | _    | 30   | _   | K  | _ |

| Thermal shutdown junction temperature   | $T_{jSD}$                    | 150  | 175  | 200 | °C | _ |

| Thermal switch-on junction temperature  | $T_{jSO}$                    | 120  | _    | 170 | °C | _ |

| Temperature shutdown hysteresis         | $\Delta T$                   | _    | 30   | _   | K  | _ |

| Ratio of SD to PW temperature           | $T_{\rm jSD}$ / $T_{ m jPW}$ | 1.05 | 1.20 | _   | _  | _ |

Note: Temperatures are guaranteed by design

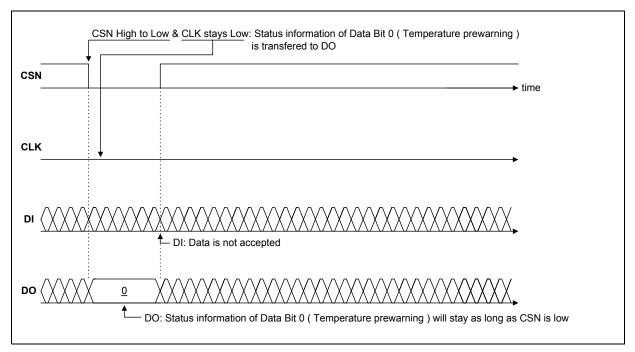

#### 3 Timing Diagrams

Figure 4

Standard Data Transfer Timing

Figure 5

Timing for Temperature Prewarning only

Figure 6 SPI-Input Timing

Figure 7

Turn OFF/ON Time

Figure 8

DO Valid Data Delay Time and Valid Time

Figure 9

DO Enable and Disable Time

## 4 Application

Figure 10

Application Circuit

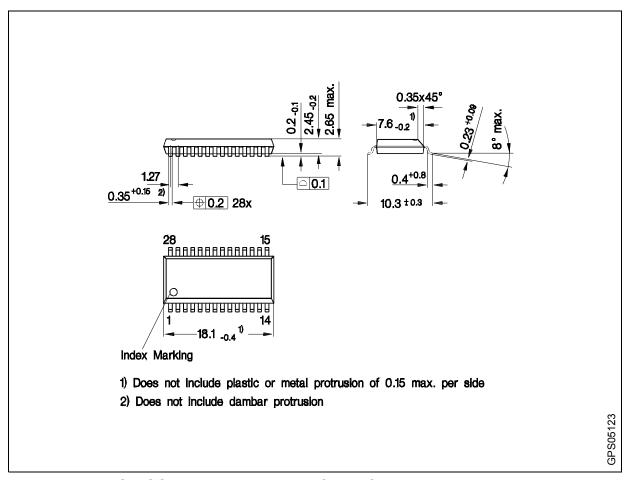

#### 5 Package Outlines

Figure 11 PG-DSO-28-24 (Plastic Dual Small Outline)

#### **Green Product** (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": <a href="http://www.infineon.com/products">http://www.infineon.com/products</a>.

SMD = Surface Mounted Device

Dimensions in mm

# **Revision History**

| Version  | Date       | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1.1 | 2007-09-12 | RoHS-compliant version of the TLE 6208-6 G                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|          |            | <ul> <li>All pages: Infineon logo updated</li> <li>Page 1:     "added AEC qualified" and "RoHS" logo, "Green Product (RoHS compliant)" and "AEC qualified" statement added to feature list, package name changed to RoHS compliant versions, package picture updated, ordering code removed</li> <li>Page 23:     Package name changed to RoHS compliant versions, "Green Product" description added</li> <li>Page 24-25:     added Revision History and Legal Disclaimer</li> </ul> |

Edition 2007-09-12

Published by Infineon Technologies AG 81726 Munich, Germany © 9/14/07 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.