# Octal configurable low/high side driver

#### **Features**

- Configurable up to 6 high side drivers

- $R_{DSON} = max.1.5 \Omega @ T_j = 25 °C$

- Current limit of each output at min. 0.8 A

- Supply voltage 4.75 V to 5.25 V

- Output voltage clamping min. 35 V (low side mode)

- Output voltage clamping -30 V (high side mode)

- SPI interface for data communication

- Additional PWM inputs for 2 outputs

- Thermal shutdown for all outputs

- Open load detection in off mode

- Reverse battery protection for outputs (amb)

- Ground disconnection for high side configured outputs

# **Description**

The L9848 IC is a highly flexible monolithic medium current output driver that incorporates 2 dedicated low side outputs (outputs 7-8) and 6 outputs that can be used as either internal low or high side drives in any combination (outputs 1-6).

In addition, 2 outputs are capable of being PWMed via an external pin (outputs 5-6). The integrated standard serial peripheral interface (SPI) controls all outputs and provides diagnostic information.

Integrated clamping circuits, waveshaping, protection against positive and negative voltage transients and thermal shutdown for all outputs open a wide range of automotive and industrial applications

Table 1. Device summary

| Order code | Package | Packing |

|------------|---------|---------|

| L9848      | SO-28   | Tube    |

Contents L9848

# **Contents**

| 1    | Block | c diagram and pin description6                       | õ |

|------|-------|------------------------------------------------------|---|

| 2    | Elect | rical specifications 8                               | 3 |

|      | 2.1   | Absolute maximum ratings                             | 3 |

|      | 2.2   | Operation conditions                                 | 3 |

|      | 2.3   | Thermal data S                                       | 9 |

|      | 2.4   | Electrical characteristcs                            | 9 |

|      |       | 2.4.1 DC characteristics                             |   |

|      |       | 2.4.2 AC characteristics                             | 1 |

| 3    | Func  | tional description                                   | 1 |

|      | 3.1   | General features                                     | 4 |

|      | 3.2   | Outputs - Common characteristics                     | 4 |

|      |       | 3.2.1 Output 1-4                                     | 4 |

|      |       | 3.2.2 Output 5-6                                     | 5 |

|      |       | 3.2.3 Output7-8                                      | 5 |

|      | 3.3   | Main power input (VDD)                               | 5 |

|      | 3.4   | Discrete inputs (IN5-6)                              | 5 |

|      | 3.5   | Serial peripheral interface (SPI)                    | 5 |

|      |       | 3.5.1 Serial data output (DO)                        | 6 |

|      |       | 3.5.2 Serial data input (DI)                         | 6 |

|      |       | 3.5.3 Chip select (CS)                               | 6 |

|      |       | 3.5.4 Serial clock (SCLK)                            | 6 |

|      | 3.6   | SPI DI input command register                        | 7 |

|      | 3.7   | Fault operation                                      | 7 |

|      |       | 3.7.1 Initial fault register SPI Cycle               | В |

|      |       | 3.7.2 Incandescent lamp outputs                      | В |

|      | 3.8   | Configuration for Output1-6                          | 3 |

|      |       | 3.8.1 Low side drivers                               | 8 |

|      |       | 3.8.2 High side drivers                              | 8 |

|      | 3.9   | DRN1-6 susceptibility to negative voltage transients | 3 |

|      | 3.10  | Thermal shutdown                                     | 9 |

|      | 3.11  | Charge pump usage                                    | 9 |

| 2/27 |       |                                                      | 7 |

| L9848 |      |          | Contents                    |

|-------|------|----------|-----------------------------|

|       | 3.12 | Waves    | haping                      |

|       | 3.13 | POR re   | egister initialization      |

|       | 3.14 | Abnorn   | nal voltage conditions 20   |

|       |      | 3.14.1   | Reverse Battery             |

|       |      | 3.14.2   | Maximum negative transients |

|       |      | 3.14.3   | Ground offsets              |

|       |      | 3.14.4   | Loss of ground operation    |

| 4     | Func | tional b | block diagram               |

| 5     | Appl | ication  | examples 22                 |

| 6     | Pack | age info | ormation                    |

List of tables L9848

# List of tables

| Table 1.  | Device summary                    | 1  |

|-----------|-----------------------------------|----|

| Table 2.  | Pin description                   | 7  |

| Table 3.  | Absolute maximum ratings          | 8  |

| Table 4.  | Operation conditions              |    |

| Table 5.  | Thermal data                      |    |

| Table 6.  | Electrical characteristcs         | 9  |

| Table 7.  | AC characteristics                | 11 |

| Table 8.  | Bit command register definition   | 17 |

| Table 9.  | Command register logic definition | 17 |

| Table 10. | Fault register definition         | 17 |

| Table 11. | Fault logic definition            |    |

| Table 12. | Document revision history         | 26 |

L9848 List of figures

# **List of figures**

| Figure 1.  | Block diagram                                                          | 6  |

|------------|------------------------------------------------------------------------|----|

| Figure 2.  | Pin connection (top view)                                              | 6  |

| Figure 3.  | DO loading for disable time measurement                                | 12 |

| Figure 4.  | Output loading for slew rate measurement                               | 12 |

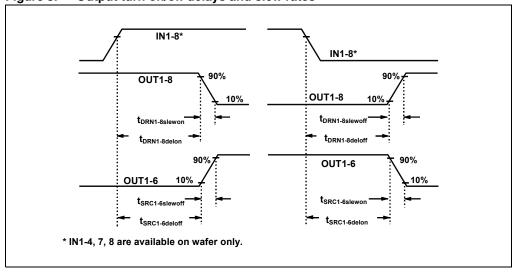

| Figure 5.  | Output turn on/off delays and slew rates                               | 12 |

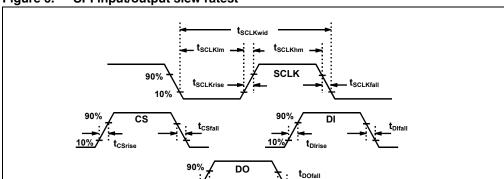

| Figure 6.  | SPI input/output slew ratest                                           | 13 |

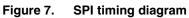

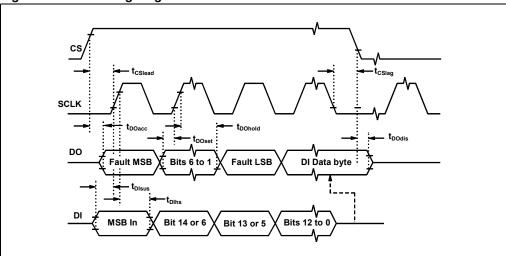

| Figure 7.  | SPI timing diagram                                                     | 13 |

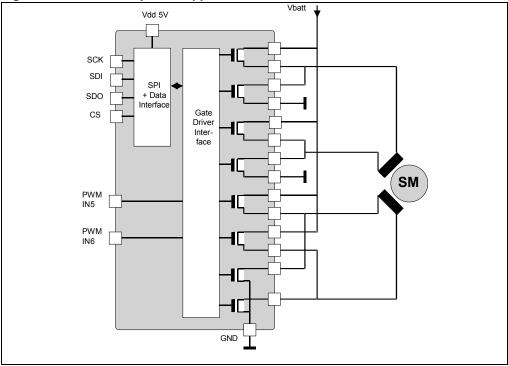

| Figure 8.  | L9848 with external components                                         | 21 |

| Figure 9.  | L9848 as mirror axis control motor drivers                             | 22 |

| Figure 10. | L9848 as mirror motor and bulb driver                                  | 22 |

| Figure 11. | L9848 as window lift relay and mirror motor driver                     | 23 |

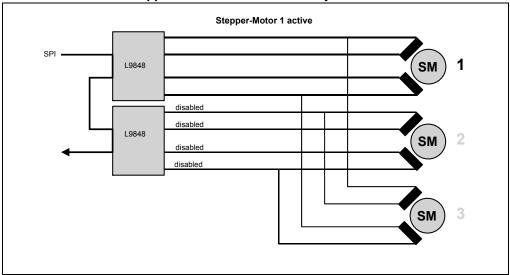

| Figure 12. | L9848 as bipolar stepper motor driver                                  | 23 |

| Figure 13. | L9848 driving approach for 3 bipolar stepper-motors in sequential mode |    |

| -          | for climate applications as window lift relay and mirror motor driver  | 24 |

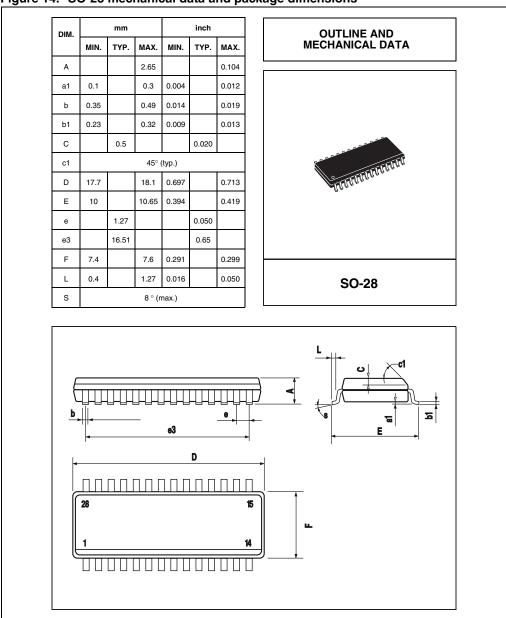

| Figure 14. | SO-28 mechanical data and package dimensions                           |    |

# 1 Block diagram and pin description

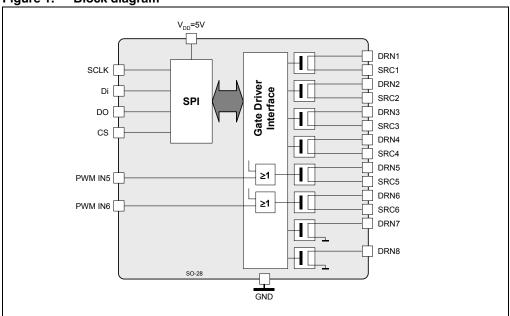

Figure 1. Block diagram

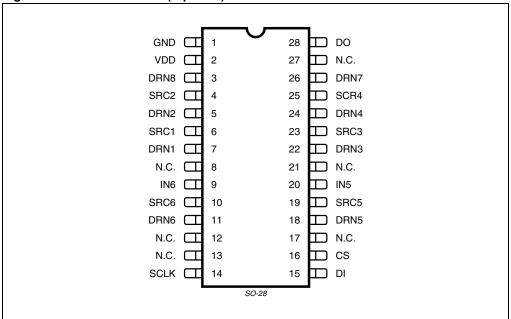

Figure 2. Pin connection (top view)

Table 2. Pin description

| N° | Pin  | Description                      |

|----|------|----------------------------------|

| 1  | GND  | Analog ground                    |

| 2  | VDD  | 5V supply input                  |

| 3  | DRN8 | Drain of low side driver #8      |

| 4  | SRC2 | Source of configurable driver #2 |

| 5  | DRN2 | Drain of configurable driver #2  |

| 6  | SRC1 | Source of configurable driver #1 |

| 7  | DRN1 | Drain of configurable driver #1  |

| 8  | NC   | Not connected                    |

| 9  | IN6  | PWM input for driver #6          |

| 10 | SRC6 | Source of configurable driver #6 |

| 11 | DRN6 | Drain of configurable driver #6  |

| 12 | NC   | Not connected                    |

| 13 | NC   | Not connected                    |

| 14 | SCLK | SPI serial clock input           |

| 15 | DI   | SPI data in                      |

| 16 | CS   | SPI chip select (active high)    |

| 17 | NC   | Not connected                    |

| 18 | DRN5 | Drain of configurable driver #5  |

| 19 | SRC5 | Source of configurable driver #5 |

| 20 | IN5  | PWM input for driver #5          |

| 21 | NC   | Not connected                    |

| 22 | DRN3 | Drain of configurable driver #3  |

| 23 | SRC3 | Source of configurable driver #3 |

| 24 | DRN4 | Drain of configurable driver #4  |

| 25 | SRC4 | Source of configurable driver #4 |

| 26 | DRN7 | Drain of low side driver #7      |

| 27 | NC   | Not connected                    |

| 28 | DO   | SPI data out                     |

# 2 Electrical specifications

# 2.1 Absolute maximum ratings

Warning: For voltages and currents applied externally to the device.

This part may be irreparably damaged if taken outside the

specified absolute maximum rating range

Table 3. Absolute maximum ratings

| Symbol                                | Parameter                         | Value                      | Unit |

|---------------------------------------|-----------------------------------|----------------------------|------|

| $V_{DD}$                              | Supply voltage                    | -0.3 to 7.0                | V    |

| Pin voltages                          |                                   |                            |      |

| $V_{CS}, V_{DI}, V_{DO}, V_{SCLK}$    | Data lines voltages               | -0.3 to 7.0                | V    |

| $V_{IN5}, V_{IN6}$                    | Input voltages                    | -0.3 to 7.0                | V    |

| V <sub>SRC1</sub> – V <sub>SRC8</sub> | Output DC voltages                | -13.5 to 40                | V    |

| V <sub>DRN1</sub> – V <sub>DRN6</sub> | Output DC voltages                | -13.5 to 60 <sup>(1)</sup> | V    |

| V <sub>SRC1</sub> – V <sub>SRC8</sub> | Output transient voltages         | -20 to 40                  | V    |

| V <sub>DRN1</sub> – V <sub>DRN6</sub> | Output transient voltages         | -20 to 60                  | V    |

| E <sub>out 1-8</sub>                  | Max. dissipation energy (@ 300mA) | 60                         | mJ   |

<sup>1.</sup> Internally limited.

# 2.2 Operation conditions

Warning: This part may not operate if taken outside the maximum

ratings. Once the condition is returned to within the specified maximum rating or the power is re-cycled, the part will

recover with no damage or degradation.

Table 4. Operation conditions

| Symbol            | Parameter                    | Value        | Unit |

|-------------------|------------------------------|--------------|------|

| $V_{DD}$          | Supply voltage               | 4.75 to 5.25 | V    |

| V <sub>Batt</sub> | Battery supply voltage       | 9 to 18      | V    |

| I <sub>out</sub>  | Output current (channel 1-8) | 350          | mA   |

| T <sub>j</sub>    | Junction temperature         | -40 to 150   | °C   |

## 2.3 Thermal data

Table 5. Thermal data

| Symbol               | Parameter                                             | Value      | Unit |

|----------------------|-------------------------------------------------------|------------|------|

| T <sub>st</sub>      | Storage temperature                                   | -65 to 150 | °C   |

| R <sub>th(j-a)</sub> | Thermal resistance junction to ambient                | max. 70    | °C/W |

| R <sub>th(j-a)</sub> | Thermal resistance junction to ambient <sup>(1)</sup> | max. 50    | °C/W |

<sup>1.</sup> With 6cm<sup>2</sup> on board heatsink area.

# 2.4 Electrical characteristcs

## 2.4.1 DC characteristics

#### Table 6. Electrical characteristcs

(T  $_j$  = -40  $^{\circ}$  C to 150  $^{\circ}$  C, V  $_{DD}$  = 4.75 V  $_{dc}$  to 5.25 V  $_{dc}$  , V  $_{Batt}$  =9 V to 18 V, unless otherwise specified)

| Symbol                                           | Parameter               | Conditions                                                                  | Min.                 | Тур. | Max.        | Unit                     |

|--------------------------------------------------|-------------------------|-----------------------------------------------------------------------------|----------------------|------|-------------|--------------------------|

| V <sub>IN5,6(ih)</sub><br>V <sub>IN5,6(il)</sub> | IN5, 6 input voltage    |                                                                             | 0.8                  |      | 2.0         | V<br>V                   |

| I <sub>IN5,6(il)</sub><br>I <sub>IN5,6(ih)</sub> | IN5, 6 input current    | $ \begin{vmatrix} V_{IN5,6} = 0V_{dc} \\ V_{IN5,6} = V_{DD} \end{vmatrix} $ | 30                   |      | 10 <br> 100 | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>CS(ih)</sub><br>V <sub>CS(il)</sub>       | CS input voltage        |                                                                             | 0.8                  |      | 2.0         | V<br>V                   |

| I <sub>CS(il)</sub>                              | CS input current        | $V_{CS} = 0V_{dc}$<br>$V_{CS} = V_{DD}$                                     | 30                   |      | 10 <br> 100 | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>SCLK(ih)</sub>                            | SCLK input voltage      |                                                                             | 0.8                  |      | 2.0         | V<br>V                   |

| I <sub>SCLK(il)</sub>                            | SCLK input current      | $V_{SCLK} = 0V_{dc}$<br>$V_{SCLK} = V_{DD}$                                 |                      |      | 10 <br> 10  | μ <b>Α</b><br>μ <b>Α</b> |

| V <sub>DI(ih)</sub><br>V <sub>DI(il)</sub>       | DI input voltage        |                                                                             | 0.8                  |      | 2.0         | V<br>V                   |

| I <sub>DI((iI)</sub>                             | DI input current        | $V_{DI} = 0V_{dc}$<br>$V_{DI} = V_{DD}$                                     |                      |      | 10 <br> 10  | μA<br>μA                 |

| I <sub>VDD</sub>                                 | V <sub>DD</sub> current | All outputs ON                                                              |                      | 4.5  | 6           | mA                       |

| I <sub>VDD</sub>                                 | V <sub>DD</sub> current | All outputs OFF                                                             | 0.5                  | 2.0  | 5.0         | mA                       |

| V <sub>DO(ol)</sub><br>V <sub>DO(oh)</sub>       | DO output voltage       | I <sub>DO</sub> = 1.6 mA<br>I <sub>DO</sub> = -200 μA                       | V <sub>DD</sub> -0.8 |      | 0.4         | V<br>V                   |

| I <sub>DO(zol)</sub><br>I <sub>DO(zoh)</sub>     | DO tri-state current    | $V_{DO} = 0V_{dc}$ $V_{DO} = V_{DD}$                                        |                      |      | 10 <br> 10  | μ <b>Α</b><br>μ <b>Α</b> |

Table 6. Electrical characteristcs (continued)  $(T_j = -40^{\circ}\text{C to } 150^{\circ}\text{C}, \ V_{DD} = 4.75 \ V_{dc} \ \text{to } 5.25 \ V_{dc}, \ V_{Batt} = 9 \ V \ \text{to } 18 \ V, \ \text{unless otherwise specified)}$

| Symbol                      | Parameter                                            | Conditions                                                                                                                                                                                                                       | Min.                | Тур.                     | Max.               | Unit                     |

|-----------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--------------------------|--------------------|--------------------------|

| I <sub>DRN1-8(lk)</sub>     | DRN1-8 leakage<br>current (low side)                 | V <sub>DD</sub> =0.5V <sub>dc</sub> , V <sub>SRC1-6</sub> =0V <sub>dc</sub> ,<br>V <sub>DRN1-8</sub> =18 V <sub>dc</sub><br>V <sub>DD</sub> =0.5V <sub>dc</sub> , V <sub>SRC1-6</sub> =0V <sub>dc</sub> , V <sub>DRN</sub> =35 V |                     | 0.1<br>1.5               | 5<br>10            | μ <b>Α</b><br>μ <b>Α</b> |

| I <sub>SRC1-6(lk)</sub>     | SRC1-6 leakage<br>current (high side)                | V <sub>DD</sub> =0.5V <sub>dc</sub> , V <sub>SRC1-6</sub> =0V <sub>dc</sub> ,<br>V <sub>DRN1-8</sub> =18 V <sub>dc</sub><br>V <sub>DD</sub> =0.5V <sub>dc</sub> , V <sub>SRC1-6</sub> =0V <sub>dc</sub> , V <sub>DRN</sub> =35 V | -5<br>-10           | -0.1<br>-1.5             |                    | μ <b>Α</b><br>μ <b>Α</b> |

| I <sub>DRN1-8</sub> (Sink)  | DRN1-8 current sink (low side)                       | $V_{SRC1-6}$ =0 $V_{dc}$ , DI=00h, $V_{DRN1-8}$ = 18 $V_{dc}$ $V_{SRC1-6}$ =0 $V_{dc}$ , DI=00h, $V_{DRN}$ =35 $V$                                                                                                               | 50<br>50            | 60                       | 80<br>100          | μ <b>Α</b><br>μ <b>Α</b> |

| I <sub>SRC1-6(Sour)</sub>   | SRC1-6 current<br>source (high side)                 | V <sub>SRC1-6</sub> =0V <sub>dc</sub> , DI=00h,<br>V <sub>DRN1-8</sub> =18 V <sub>dc</sub><br>V <sub>SRC1-6</sub> =0V <sub>dc</sub> , DI=00h, V <sub>DRN</sub> =35 V                                                             | -80<br>-100         | -50<br>-60               | -30<br>-30         | μ <b>Α</b><br>μ <b>Α</b> |

| I <sub>DRN1-8(Limit)</sub>  | DRN1-8 current limit (low side)                      | $V_{SRC1-6}$ =0 $V_{dc}$ , DI=FFh,<br>$V_{DRN1-8}$ = 4-16 $V_{dc}$                                                                                                                                                               | 0.8                 | 1.3                      | 1.8                | Α                        |

| I <sub>SRC1-6(Limit)</sub>  | SRC1-6 current limit (high side)                     | V <sub>SRC1-6</sub> =0-12 V <sub>dc</sub> , DI=FFh,<br>V <sub>DRN1-8</sub> = V <sub>Batt</sub>                                                                                                                                   | -0.8                | 1.3                      | -1.8               | Α                        |

| V <sub>DRN1-8(Cl+)</sub>    | DRN1-8 clamp<br>voltage (low side)                   | V <sub>SRC1-6</sub> =0V <sub>dc</sub> , DI=00h, I <sub>DRN1-8</sub> =10 mA                                                                                                                                                       | 35                  | 45                       | 55                 | ٧                        |

| V <sub>SRC1-6(Cl+)bat</sub> | SRC1-6 clamp<br>voltage (high side)                  | V <sub>DRN1-8</sub> =25 V DI=00h, I <sub>DRN1-8</sub> =10 mA                                                                                                                                                                     |                     | V <sub>Batt-</sub><br>45 |                    | ٧                        |

| V <sub>SRC1-6GND</sub>      | voltage (flight side)                                | V <sub>DRN</sub> = 10 V; I <sub>SRC</sub> = -10 mA                                                                                                                                                                               | -36                 | -31                      | -27                | V                        |

| V <sub>DRN1-8(Fault)</sub>  | DRN1-8 fault voltage (low side)                      | V <sub>SRC1-6</sub> =0 V <sub>dc</sub> , DI=00h                                                                                                                                                                                  | 0.9V <sub>DD</sub>  |                          | 1.1V <sub>DD</sub> | ٧                        |

| V <sub>SRC1-6(Fault)</sub>  | SRC1-6 fault voltage (high side)                     | V <sub>DRN1-8</sub> =V <sub>Batt</sub> , DI=00h                                                                                                                                                                                  | 0.55V <sub>DD</sub> |                          | 0.65V <sub>D</sub> | V                        |

| R <sub>DSONDRN1-8</sub>     | On-resistance<br>(DRN1-8)                            | T <sub>j</sub> =110 °C<br>T <sub>j</sub> =25 °C<br>T <sub>j</sub> =-40 °C                                                                                                                                                        |                     | 1.5<br>1.0               | 2.0<br>1.5<br>1.3  | W<br>W<br>W              |

| T <sub>jTS</sub>            | Thermal shutdown junction temperature <sup>(1)</sup> |                                                                                                                                                                                                                                  | 155                 |                          | 185                | °C                       |

| T <sub>jTSH</sub>           | Thermal shutdown threshold hysteresis*               |                                                                                                                                                                                                                                  | 5                   |                          | 15                 | К                        |

| POR <sub>wih</sub>          | Power on reset threshold on                          |                                                                                                                                                                                                                                  | 3.40                |                          | 4.50               | ٧                        |

| POR <sub>whyst</sub>        | Power on reset hysteresis                            |                                                                                                                                                                                                                                  | 0.4                 |                          | 0.8                | ٧                        |

<sup>1.</sup> Guaranteed by design, not tested

## 2.4.2 AC characteristics

Table 7. AC characteristics

(T  $_{j}$  = - 40 °C to 150 °C, V  $_{DD}$  = 4.75 V to 5.25 V  $_{dc},$  V  $_{Batt}$  = 9 V to 18 V, unless otherwise specified)

| rate<br>iide)<br>on<br>off | See Figure 4 and 5                                                                                                                                                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |            |           |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------|-----------|

| on<br>off                  |                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |            |           |

| off                        |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0.5                                        | 400        |           |

| -                          |                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                         | 100        | μs        |

|                            |                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 25                                         | 100        | μs        |

|                            | See Figure 4 and 5                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            |           |

| •                          |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            |           |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10                                         | -          | μs        |

| off                        |                                                                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                         |            | μs        |

|                            | <sup>t</sup> DRN1-8deloff <sup>- t</sup> DRN1-8delon                                                                                                                                  | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            | 60         | μs        |

|                            | See Figure 4 and 5                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            |           |

| •                          |                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                         | 100        | μs        |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            | μs        |

|                            | One Figure 4 and 5                                                                                                                                                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            | 100        | μο        |

|                            | See Figure 4 and 5                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            |           |

| •                          |                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                            | 20         | 110       |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            | -          | μs<br>μs  |

| JII                        | topos o L. « — topos o L.                                                                                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                         |            | μs        |

|                            | SRC1-6deloff SRC1-6delon                                                                                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |            |           |

| Capacitance*               |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            | -          | pF        |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            | 20         | pF        |

| ` '                        |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            |           |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            | ns        |

|                            | •                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            |            | ns        |

|                            |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            | 70         | ns        |

|                            |                                                                                                                                                                                       | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            |            | ns        |

|                            | •                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            | 1.10       | ns        |

| e ume                      |                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                            | 140        | ns        |

| delay time (Internal)      | Duration of open/short fault until<br>Fault Bit is "Set"                                                                                                                              | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                            | 300        | μs        |

|                            | Duration of thermal fault until Fault Bit is "Set"                                                                                                                                    | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                            | 50         | μs        |

|                            | r time side) on off  rate side) on off  rime side) on off  rime side) on off  Capacitance*  ut data (DO) time me ses time p time time delay time (Internal) mal fault delay time nal) | side) on off  tDRN1-8deloff - tDRN1-8delon  rate side) on off  time side) on off  time See Figure 4 and 5  See Figure 4 and 5  time Side) on Off  tSRC1-6deloff - tSRC1-6delon  Capacitance*  out data (DO) time So pF from DO to GND, see Fig. 6 50 pF from DO to GND, see Fig. 6 50 pF from DO to GND, see Fig. 7 50 pF from DO to GND, see Fig. 7 50 pF from DO to GND, see Fig. 7 No capacitor on DO, see Figure 3  delay time (Internal)  Duration of open/short fault until Fault Bit is "Set"  Duration of thermal fault until | off to | Side   Don | Side   On |

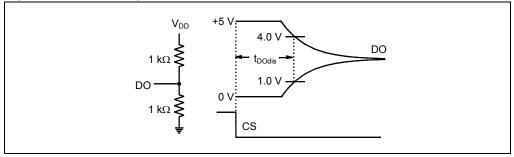

Figure 3. DO loading for disable time measurement

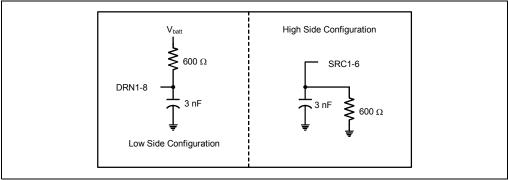

Figure 4. Output loading for slew rate measurement

Figure 5. Output turn on/off delays and slew rates

Figure 6. SPI input/output slew ratest

# 3 Functional description

### 3.1 General features

The L9848 IC is a monolithic integrated circuit, which provides high flexibility for driving medium loads. 8 outputs, whereof 6 (Output1-6) can be used as either internal low or high side drives in any combination and 2 are dedicated low side outputs (Output7-8). The use of this device reduces the I/O port requirements of the microprocessor by having serially controlled outputs via a SPI interface. In addition, Output5-6 are capable of being PWMed via an external pin (Input5-6). The 8bit SPI input is used to command the 8 output drivers either ON or OFF and additional to indicate latched fault conditions that may have occurred.

Multiple L9848s may be daisy-chained with one additional microprocessor I/O port (CSn) for each device. The implemented self-configuration allows the user to connect a high or low side load to any of these outputs and the L9848 will drive them correctly as well as provide proper fault mode operation with no other needed inputs. This device switch variable load currents within the operation temperature range. The outputs are MOSFET drivers to minimize Vdd current requirements. There's no V<sub>Batt</sub> input pin however V<sub>Batt</sub> is connected to the drains of high side outputs.

The L9848 meets all required specifications when the supply voltage applied to the drain(s) of the outputs is within the operating range. For supply voltages applied to the drain(s) down to 6.8V the part is functional however, it does not meet all parametric limits, i.e. output on-state voltages.

## 3.2 Outputs - Common characteristics

The 6 self-configuring outputs (Outputs1-6) are able to drive either incandescent lamps, inductive loads (non-PWMed), or resistive loads biased to VBatt. These outputs are enabled and disabled via the SPI bus. Each of these outputs is short circuit current limited and has an over-temperature protection as described under "Functional Description - Thermal Shutdown".

When a high side configured output is commanded OFF after having been commanded ON, the source voltage will go to the lesser negative of (VBatt-45V). This is due to the design of the circuitry and the transconductance of the MOSFET.

When a low side configured output is commanded OFF after having been commanded ON, the output voltage will rise to the internal zener clamp voltage (40 Vdc minimum) due to the flyback of the inductive load.

## 3.2.1 Output 1-4

These four outputs can be used as either high or low side drives. Integrated current source pull-ups and pull-downs are employed to correctly latch "open load" fault data. Both of these current sources are needed to detect an open load state since these outputs self configure as either high or low side drives.

#### Drain connections of output1-4 (DRN1-4)

These pins are connected to the drains of the n-channel MOSFET transistors.

#### Source connections of output1-4 (SRC1-4)

These pins are connected to the sources of the n-channel MOSFET transistors.

## 3.2.2 Output 5-6

These two self-configuring outputs can be used to drive either high or low side loads. In addition to be controlled by the SPI BUS these outputs can also be enabled and disabled via IN5 and IN6 inputs. IN5 and IN6 inputs are logically ORed with the SPI commands to allow either the IN5-6 inputs or the SPI commands to activate these outputs. The use of IN5-6 for PWM control on these outputs should only be done with non-inductive loads. Integrated current source pull-ups and pull-downs are employed to correctly latch "open load" fault data. Both of these current sources are needed to detect an open since these outputs self configure as either high or low side drives.

#### Drain connections of Output5-6 (DRN5-6)

These pins are connected to the drains of the n-channel MOSFET transistors.

#### Source connections of Output5-6 (SRC5-6)

These pins are connected to the sources of the n-channel MOSFET transistors.

## 3.2.3 Output7-8

These two outputs (DRN7-8) are dedicated low side drives. Integrated current source pull down are required to correctly latch "open load" fault data.

# 3.3 Main power input (VDD)

The VDD input is the primary power source of the L9848. This supply is used as the power source for all of its logic circuitry and other miscellaneous functions. Notice that if the L9848 is interfaced to a processor operating with a lower voltage (e.g. 3.0 VDC), the microprocessor inputs connected to the L9848 will swing from 0 to 5.0 VDC.

## 3.4 Discrete inputs (IN5-6)

These inputs allow Output5-6 to be enabled via this external pin without the use of the SPI. A logic "1" on these inputs enables the corresponding output no matter what the status of the SPI command register. A logic "0" on these inputs disables the corresponding output if the SPI command register is not commanding this output on. These pins can be left "open" if the outputs are controlled only via the SPI (internally pulled down). These inputs are ideally suited for non-inductive loads that are pulse width modulated (PWMed). This allows PWM control without the use of the SPI. The TTL level compatible input voltages allow proper operation with microprocessors that are using 5.0V or 3.0V for their Vdd supply.

# 3.5 Serial peripheral interface (SPI)

A standard serial peripheral interface, consisting of Serial Clock (SCLK), Data Out (DO), Data In (DI), and Chip Select (CS) is implemented to allow access to the internal registers of the L9848. All outputs are controlled via the SPI. The input pins CS, SCLK, and DI have TTL level compatible input voltages allowing proper operation from microprocessors that are using 5.0V or 3.0V for their VDD supply. The design of the L9848 allows a "daisy-chaining" of multiple L9848's to further reduce the need for controller pins.

## 3.5.1 Serial data output (DO)

This output pin is in a tri-state condition when CS is a logic "0" (LOW). When CS is a logic "1" (HIGH), this pin always transmits 8bits of data from the fault register to the digital controller. After the first 8bits data are transmitted the DO output then sequentially transmits the digital data that was just received (8 SCLK cycles earlier) on the DI pin. The DO output continues to transmit the 8 SCLK delayed bit data from the DI input until CS eventually transitions from a logic "1" to a logic "0". DO data changes state 10 ns or later, after the falling edge of SCLK. By definition, the MSB (Table 3) is the first bit of the byte transmitted on DO and the LSB is the last bit of the byte transmitted on DO, once CS transitions from a logic "0" to a logic "1".

## 3.5.2 Serial data input (DI)

This input takes data from the digital controller while CS is HIGH. The L9848 accepts an 8bit data stream to command the outputs ON or OFF. By definition, the MSB (Table 1) is the first bit of each byte received on DI and the LSB is the last bit of each byte received on DI, once CS transitions from a logic "0" to a logic "1".

### 3.5.3 Chip select (CS)

This is the chip select input pin. On the rising edge of CS, the DO pin switches from tri-state to active-out mode. While CS is high, register data is shifted in and shifted out by the DI and DO pin, respectively, on each subsequent SCLK. On the falling edge of CS, the DO pin switches back to tri-state mode and the fault register will be "Cleared" if a valid DI byte was received.

A valid DI byte is defined as such:

- 1st A multiple of 8 bits was received

- 2<sup>nd</sup> SCLK was low when CS went low

- 3<sup>rd</sup> Current SPI cycle started when SCLK was low

The fault data is not cleared unless all of the 3 previous conditions have been met. A SCLK transition must be seen before CS is interpreted as active. To allow sufficient time to reload the fault registers, the CS pin must remain low for a minimum of 1µs prior to going high again, before it starts shifting the fault data bits out on the DO pin. CS has an integrated glitch filter for spurious pulses of 50ns or shorter (i.e. no fault data and Outputs1-8 enable status will be altered). For open circuit condition the CS is internally pulled down to GND.

#### 3.5.4 Serial clock (SCLK)

This is the clock signal input for synchronization of serial data transfer. DI data is shifted into the DI input on the rising edge of SCLK and DO data changes on the falling edge of SCLK.

## 3.6 SPI DI input command register

An input byte (8 bits) is routed to the Command Register. The content of this Command Register is given in *Table 8* and *Table 9*. Additional DI data will continue to be wrapped around to the DO pin. If CS will go low before a complete reception of the current byte, this just transmitted byte will be ignored

Table 8. Bit command register definition

| MSB  |      |      |      |      |      |      | LSB  |

|------|------|------|------|------|------|------|------|

| OUT8 | OUT7 | OUT6 | OUT5 | OUT4 | OUT3 | OUT2 | OUT1 |

| D07  | D06  | D05  | D04  | D03  | D02  | D01  | D00  |

Table 9. Command register logic definition

| Bit     | State | Status                      |  |

|---------|-------|-----------------------------|--|

| D00-D07 | 0     | OUTPUT1-8 are commanded OFF |  |

| D00-D07 | 1     | OUTPUT1-8 are commanded ON  |  |

## 3.7 Fault operation

The fault diagnostic capability consists of one internal 8bit shift register. Open or shorted load detection is provided by comparing the source or drain voltage with the VDD voltage. When an output connected as either a low side device or a high side device is commanded OFF, an open load can be detected. When an output connected as either a low side device or a high side device is commanded ON a shorted load can be detected.

The fault bit is "set" for each channel if a short, open, or over-temperature condition occurs for Outputs1-8. The content of this Fault Register is given in *Table 10*.

The output load status of each individual channel is defined in *Table 11*. Open and shorts are subsequently re-latched provided they meet the minimum duration criterion and thermal faults will be re-latched provided they meet the duration criterion after CS goes "LOW", if these fault conditions are still present.

The fault register is capable of detecting and latching multiple fault conditions (among the 8 outputs) that have occurred between clearing of the fault flags.

All of the faults will be cleared on the falling edge of Chip Select (CS).

Table 10. Fault register definition

| MSB    |        |        |        |        |        |        | LSB    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| Fault8 | Fault7 | Fault6 | Fault5 | Fault4 | Fault3 | Fault2 | Fault1 |

| D07    | D06    | D05    | D04    | D03    | D02    | D01    | D00    |

Table 11. Fault logic definition

| BIT      | STATE | STATUS                                                   |  |  |

|----------|-------|----------------------------------------------------------|--|--|

| Fault1-8 | 0     | OUT1-8 are not open or shorted (nominal)                 |  |  |

| Fault1-8 | 1     | OUT1-8 are either open or shorted or in thermal shutdown |  |  |

## 3.7.1 Initial fault register SPI Cycle

After initial application of VDD to the L9848, the fault register is "Cleared" by the POR circuitry during the initial SPI cycle, and all subsequent cycles, valid fault data will be clocked out of DO (fault bits). The bits that are "Set" indicate which particular output(s) have a fault condition.

### 3.7.2 Incandescent lamp outputs

Software filtering may be needed to ignore fault signals due to the long turn on delay associated with lamp loads. For example, the lamp load channel gets enabled during one SPI cycle. Approximately 20ms-100ms later, a SPI cycle is required to read the correct fault latch data, which will be cleared after the falling edge of CS of that SPI cycle.

## 3.8 Configuration for Output1-6

The drain and source pins for each output must be connected in one of the two following configurations (see Figure 6a and Figure 6b).

#### 3.8.1 Low side drivers

When any combination of Output1-6 are connected in a low side drive configuration the source of the applicable output (SRC1-6) has to be connected to ground. The drain of the applicable output (DRN1-6) has to be connected to the low side of the load.

## 3.8.2 High side drivers

When any combination of Output1-6 are connected in a high side drive configuration the drain of the applicable output (DRN1-6) has to be connected to VBatt. The source of the applicable output (SRC1-6) has to be connected to the high side of the load.

# 3.9 DRN1-6 susceptibility to negative voltage transients

For any output(s) connected and used for a high side drive a fast negative transient slew rate does not inadvertently issue a POR (power on reset) or cause parasitic latching to occur. Nevertheless under some conditions it may be necessary to have a ceramic chip capacitor of 10nF to 100nF connected from drain to GND to aid in preventing the occurance of a problem due to very fast negative transient(s) on the drain(s) of the device.

### 3.10 Thermal shutdown

Each of the 8 outputs have independent thermal protection circuitry that disables each output driver once the local n-channel MOSFET device temperature reaches the overtemperature shutdown limit. Due to the hysteresis of the enable and disable temperature levels the faulted channel will periodically turn off and on until the fault condition is cleared, the ambient temperature is decreased sufficiently or the output is commanded OFF.

Once any individual channel goes into thermal shutdown, a logic "1" is latched into the Fault Register if it meets the thermal fault filter (Note: does NOT go through the open/short fault filter).

Note:

Due to the design of the L9848 each output's thermal limit "may not" be truly independent to the extent that if one output is shorted, it may impact the operation of other outputs (due to lateral heating in the die). The user may be required to monitor the fault bits periodically. If a fault bit is "Set" for the last enabled output, and subsequently, fault bits for other enabled outputs start to be "Set", the user will send two SPI write cycles within 100ms of each other. The first SPI write cycle will "Clear" the fault latches. If multiple faults are indicated after the second SPI write cycle, these faults are most likely thermal faults. The user will then disable this output that was most recently enabled. The fault register should be subsequently interrogated to verify proper operations of the other enabled output channels.

## 3.11 Charge pump usage

The L9848 uses a separate charge pump and oscillator for each of the 6 configurable output channels to provide low RDSON values when connected in a high side configuration These oscillators are operating in a non-synchronous mode of operation. The frequency range of these charge pumps is designed to be above the AM radio band and below 8.0 MHz so that harmonics do not get within the FM radio band.

# 3.12 Waveshaping

Both the turn on and the turn off slew rates on all outputs (OUTPUT1-8) are limited to reduce conducted EMC energy in the vehicle's wiring harness.

The characteristic of the turn-on and turn-off voltage is linear, with no discontinuities, during the output driver state transition.

## 3.13 POR register initialization

L9848 wakes up if the VDD supply increases from 0 to 5VDC in 0.3ms to 3ms.

The L9848 has a POR circuit, which monitors the VDD voltage. When the VDD voltage reaches roughly 4.1VDC, and remains above this trip level for minimum 20µs, the Command and Fault Registers are "cleared". Before VDD reaches this trip level, all eight outputs are guaranteed in OFF-state.

After a valid POR has occurred and the VDD voltage falls below the valid high level for a required amount of time, the L9848 is powered down in a fully controlled manner. No outputs will glitch "ON" and no erroneous fault data is allowed on the DO output.

## 3.14 Abnormal voltage conditions

The L9848 survives the following abnormal voltage conditions.

## 3.14.1 Reverse Battery

applied either directly, or through a load to the drain pins (DRN1-6) with the source pins (SRC1-6) connected to a load or to ground (cold lamp, solenoid, etc).

## 3.14.2 Maximum negative transients

that force the drains or sources of the outputs going -20V below the module ground.

#### 3.14.3 Ground offsets

with a maximum of -0.5V to 1.0V between the L9848 ground and any load directly connected to a chassis ground in the case of high side loads. If driving a low side load there will not be an offset between the L9848 ground and the load ground. In addition there may be a maximum ground difference between the L9848 ground and any other module interfacing with it of -0.5V to 1.0V or ±VAC (10-200Hz).

## 3.14.4 Loss of ground operation

Any outputs are protected to become active in case of lost ground of the L9848 module with the supply is still applied.

# 4 Functional block diagram

Figure 8. L9848 with external components DRN1 SRC1 SRC1 DRN2 DRN2 SRC2 DRN3 22  $V_{DD}$ SRC3 C2 0.01μF DRN3 22 SRC3 23 IN5 DRN4 IN6 24 SRC4 DI 25 FROM CPU CS DRN4 SCLK SRC4  $V_{BATT}$ DO (FAN OUT CAP 50nF) 26 GND DRN5 18 SRC5 DRN5 100nF DRN6 100nF SRC6 DRN6 SRC6 100nF

47/

D02AT511A

# 5 Application examples

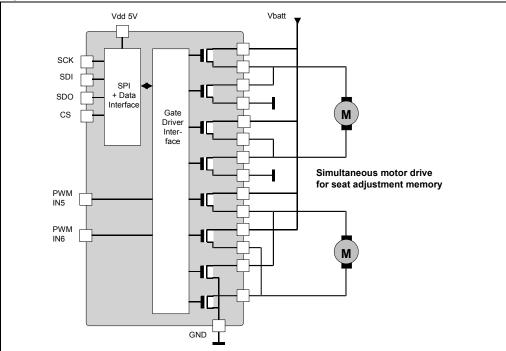

Figure 9. L9848 as mirror axis control motor drivers

Figure 10. L9848 as mirror motor and bulb driver

577

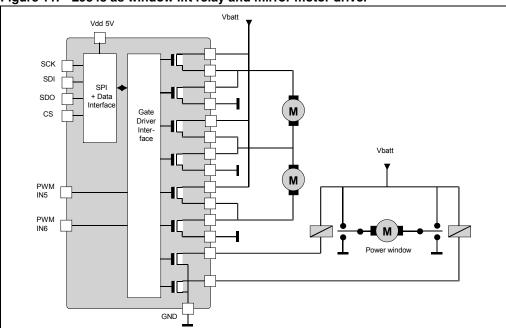

Figure 11. L9848 as window lift relay and mirror motor driver

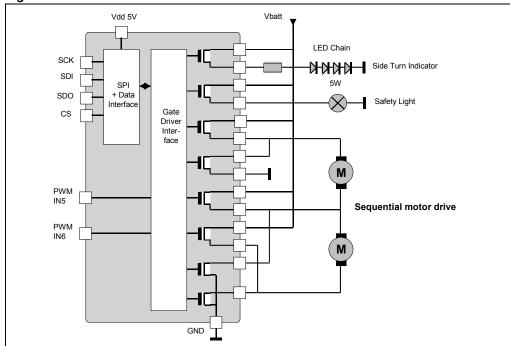

Figure 13. L9848 driving approach for 3 bipolar stepper-motors in sequential mode for climate applications as window lift relay and mirror motor driver

L9848 Package information

# 6 Package information

In order to meet environmental requirements, ST (also) offers these devices in ECOPACK<sup>®</sup> packages. ECOPACK<sup>®</sup> packages are lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 14. SO-28 mechanical data and package dimensions

Revision history L9848

# 7 Revision history

Table 12. Document revision history

| Date        | Revision | Changes                                                                                                                                                      |  |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 12-Jul-2003 | 4        | Initial release.                                                                                                                                             |  |

| 18-Nov-2008 | 5        | Document reformatted. Updated Table 2: Pin description. Updated Figure 8: L9848 with external components. Updated Section 6: Package information on page 25. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION). OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

577