# L9386

## Dual intelligent power low side switch

### Features

- Multipower BCD technology

- Dual power low side driver with 2 x 5 A

- Low R<sub>DSON</sub> typically 200 mΩ @ T<sub>J</sub> = 25 °C

- Internal output clamping diodes V<sub>FB</sub> = 50 V for inductive recirculation

- Limited output voltage slew rate for low EMI

- µP compatible enable and input

- Wide operating supply voltage range 4.5 V to 45 V

- Real time diagnostic functions:

- Output shorted to GND

- Output shorted to V<sub>SS</sub>

- Open load

- Load bypass

- Over temperature

- Device protection functions:

- Overload disable

- Reverse battery up to -16 V @ V<sub>S</sub>

- Thermal shutdown

#### Table 1.Device summary

## Description

The L9386 is a monolithic integrated dual low side driver realized in an advanced Multipower BCD mixed technology.

It is especially intended to drive valves in automotive environment. Its inputs are  $\mu P$  compatible for easy driving. Particular care has been taken to protect the device against failures, to avoid electro-magnetic interferences and to offer extensive real time diagnostic.

| Part number | Order code | Package       | Packing |  |

|-------------|------------|---------------|---------|--|

| L9386       | L9386MD    | SO20 (12+4+4) | Tube    |  |

# Contents

| 1 | Block | and pins connection diagrams | 3 |

|---|-------|------------------------------|---|

| 2 | Elect | rical specifications         | 4 |

|   | 2.1   | Absolute maximum ratings     | 4 |

|   | 2.2   | Thermal data                 | 4 |

|   | 2.3   | Electrical characteristics   | 5 |

|   | 2.4   | Circuit description          | 0 |

| 3 | Pack  | age information 1            | 2 |

| 4 | Revis | sion history                 | 3 |

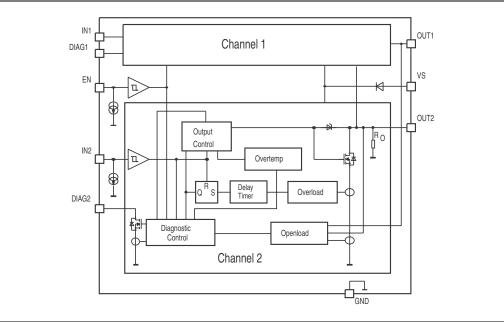

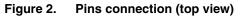

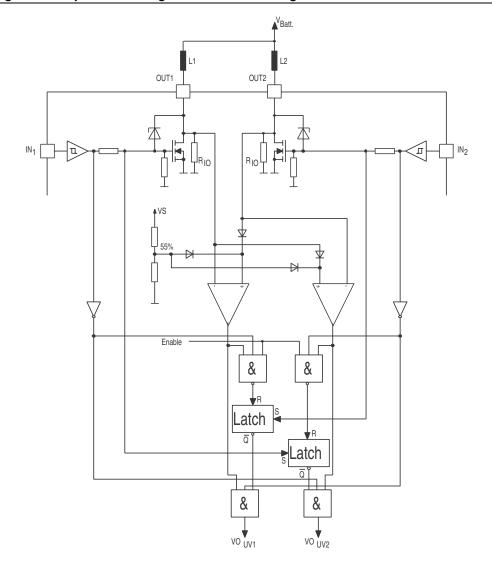

# **1** Block and pins connection diagrams

### Figure 1. Block diagram

# 2 Electrical specifications

# 2.1 Absolute maximum ratings

| Symbol                               | Parameter                                                                  | Value            | Unit |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------------------|------------------|------|--|--|--|--|

| V <sub>SDC</sub>                     | DC supply voltage                                                          | -16 to 45        | V    |  |  |  |  |

| V <sub>STR</sub>                     | Transient supply voltage (t $\leq$ 500 ms)                                 | 60               | V    |  |  |  |  |

| V <sub>IN</sub> ,EN                  | Input voltage (I $\leq$ I 10 mA I)                                         | -1.5 to 6        | V    |  |  |  |  |

| V <sub>DDC</sub>                     | Diagnostic DC output voltage ( $I \le I$ 50 mA I)                          | -0.3 to 16       | V    |  |  |  |  |

| V <sub>ODC</sub>                     | DC output voltage                                                          | 45               | V    |  |  |  |  |

| V <sub>OTR</sub>                     | Transient output voltage ( $R_L \ge 4 \Omega$ )                            | 60               | V    |  |  |  |  |

| ۱ <sub>0</sub>                       | Output load current                                                        | internal limited |      |  |  |  |  |

| I <sub>OR</sub>                      | Reverse output current limited by load                                     | -4               | А    |  |  |  |  |

| EO                                   | Switch-off energy for inductive loads $(t_{EO} = 250 \ \mu s, T = 5 \ ms)$ | 50               | mJ   |  |  |  |  |

| T <sub>jEO</sub>                     | Junction temperature during switch-off $\Sigma t = 30 \text{ min}$         | 175              | °C   |  |  |  |  |

| Тj                                   | Junction temperature                                                       | -40 to +150      | °C   |  |  |  |  |

| T <sub>stg</sub> Storage temperature |                                                                            | -55 to +150      | °C   |  |  |  |  |

Table 2. Absolute maximum ratings (no damage or latch)

# 2.2 Thermal data

| T-1-1-0  | <b>T</b> I:  |

|----------|--------------|

| Table 3. | Thermal data |

| Symbol                                                           | Symbol Parameter |            | Unit |

|------------------------------------------------------------------|------------------|------------|------|

| T <sub>jDIS</sub> Thermal disable junction temperature threshold |                  | 160 to 190 | °C   |

| R <sub>th j-pins</sub> Thermal resistance junction to pins       |                  | 14         | °C/W |

### L9386

# 2.3 Electrical characteristics

### Table 4. Electrical characteristics

(The electrical characteristics are valid within the below defined operative range, unless otherwise specified.)

| Symbol                | Parameter                                 | Test condition                                                                                  | Min.                                                   | Тур.                                                     | Max.                                                   | Unit |

|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|------|

| Vs                    | Board supply voltage                      |                                                                                                 | 4.5                                                    | 12                                                       | 32                                                     | V    |

| V <sub>D</sub>        | Stabilized diagnostic output voltage      |                                                                                                 | -0.3                                                   | 5                                                        | 16                                                     | V    |

| Тj                    | Junction temperature                      |                                                                                                 | -40                                                    |                                                          | 150                                                    | °C   |

| IS <sub>SB</sub>      | Static standby supply current             | (1)<br>(2) $V_{EN} = L$ , $VO \le VO_{uv}$                                                      |                                                        | 0.73                                                     | 1.5<br>15                                              | mA   |

| IS                    | DC supply current                         | (1)<br>(2) $V_{EN} = V_{IN} = H$                                                                |                                                        | 1.3                                                      | 5<br>15                                                | mA   |

| VDL                   | Diagnostic output low voltage             | <sup>(1)</sup> $I_D = 2 \text{ mA}$<br><sup>(2)</sup> $I_D = 1 \text{ mA}$                      |                                                        | 0.35                                                     | 0.5                                                    | V    |

| ID <sub>LE</sub>      | Diagnostic output leakage current         | $V_S = 0 \text{ V or } V_S = \text{open};$<br>$V_D = 5.5 \text{ V } T_j \le 125 ^\circ\text{C}$ |                                                        | 0.1                                                      | 2                                                      | mA   |

| ID                    | Diagnostic output current capability      | $V_D \le 16 \text{ V DIAG} = L$                                                                 | 2                                                      | 6                                                        | 30                                                     | mA   |

| VO <sub>UV</sub>      | Open load voltage threshold               | $V_{EN} = X, V_{IN} = L$                                                                        | 0.51<br>xVS                                            | 0.55<br>xVS                                              | 0.59<br>xVS                                            | V    |

| ∆VO <sub>UV1,2</sub>  | Open load difference voltage<br>threshold |                                                                                                 | VO <sub>C</sub> -<br>0.9V<br>VO <sub>C</sub> -<br>0.7V | VO <sub>C</sub> -<br>1.25V<br>VO <sub>C</sub> -<br>1.25V | VO <sub>C</sub> -<br>1.6V<br>VO <sub>C</sub> -<br>1.8V | v    |

| IO <sub>UC</sub>      | Open load current threshold               | $^{(3)}V_{EN} = V_{IN} = H$ <sup>(2)</sup>                                                      | 100<br>20                                              | 320                                                      | 480                                                    | mA   |

| IO <sub>OC</sub>      | Over load current threshold               | b)                                                                                              | 5                                                      | 7                                                        |                                                        | Α    |

| V <sub>OCL</sub>      | Output voltage during clamping            | $IO_{CL} \ge 100 mA$                                                                            | 45                                                     | 52                                                       | 60                                                     | V    |

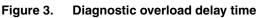

| S <sub>ON,OFF</sub>   | Output (fall, rise) slew rate             | <sup>(3)</sup> see <i>Figure 4</i>                                                              | 200                                                    | 1500                                                     | 3200                                                   | V/ms |

| R <sub>IO</sub>       | Internal output pull down resistor        | V <sub>EN</sub> = L                                                                             | 10                                                     | 20                                                       | 40                                                     | KΩ   |

| R <sub>DSON</sub>     | Output on resistance                      | $V_{S} > 9.5 V I_{O} = 2 A$<br>$T_{j} = 25 °C$<br>$T_{j} = 150 °C$                              |                                                        | 200                                                      | 300<br>500                                             | mΩ   |

| V <sub>(EN,IN)L</sub> | Logic input low voltage                   | $ I_{EN}, I_N  \le 10 \text{ mA}$<br>(1)<br>(2)                                                 | -1.5<br>-1.5                                           |                                                          | 1<br>0.5                                               | V    |

| V <sub>(EN,IN)H</sub> | Logic input high voltage                  |                                                                                                 | 2.2                                                    |                                                          | 5.5                                                    | V    |

5/14

#### Table 4. **Electrical characteristics (continued)**

(The electrical characteristics are valid within the below defined operative range, unless otherwise specified.)

| Symbol                  | Parameter                                    | Test condition                     | Min. | Тур. | Max. | Unit |

|-------------------------|----------------------------------------------|------------------------------------|------|------|------|------|

| V <sub>(EN,IN)hys</sub> | Logic input hysteresis                       |                                    | 0.2  | 0.4  | 1    | V    |

| I <sub>EN</sub>         | Enable input sink current                    | $1~V \leq V_{EN} \leq 5.5~V$       | 10   | 30   | 60   | μA   |

| I <sub>IN</sub>         | Logic input sink current                     | $1~V \leq V_{IN} \leq 5.5~V$       | 40   | 95   | 180  | μA   |

| t <sub>DON</sub>        | Output delay ON time                         | <sup>(3)</sup> see <i>Figure 4</i> |      | 4    | 25   | μs   |

| t <sub>DOFF</sub>       | Output delay OFF time                        | <sup>(3)</sup> see <i>Figure 4</i> | 5    | 15   | 30   | μs   |

| t <sub>DH-L,Diag.</sub> | Diag. delay output OFF time                  | <sup>(3)</sup> see <i>Figure 4</i> | 5    | 30   | 65   | μs   |

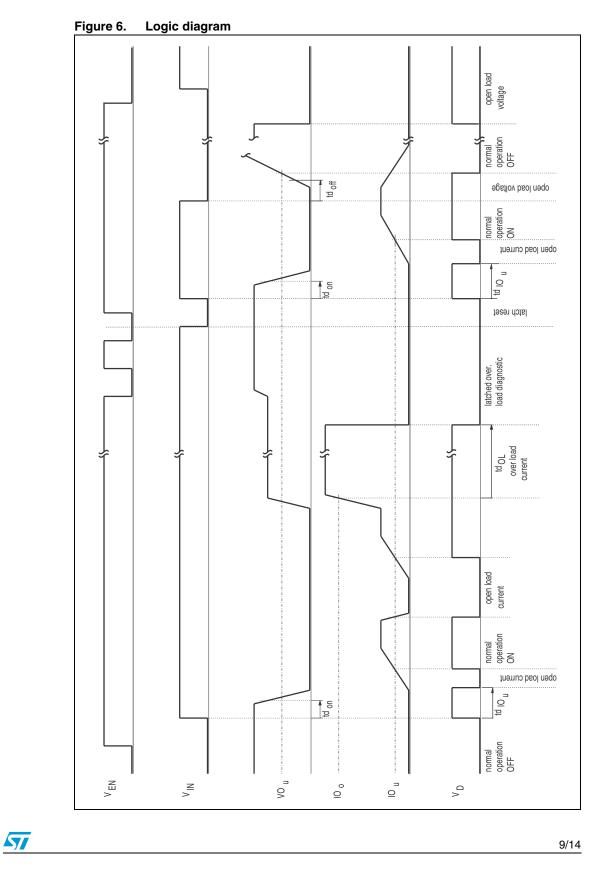

| t <sub>DIOu</sub>       | Diagnostic open load delay time              | <sup>(3)</sup> see <i>Figure 6</i> |      | 8    | 50   | μs   |

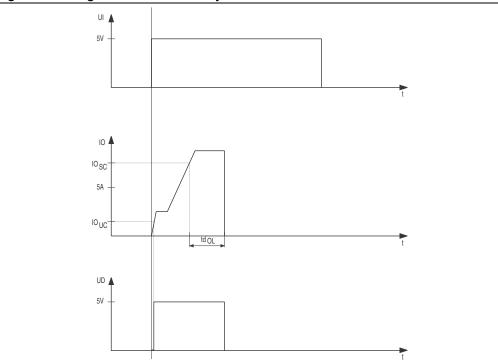

| t <sub>DOL</sub>        | Diagnostic overload delay<br>switch-off time | <sup>(3)</sup> see <i>Figure 3</i> | 50   | 160  | 300  | μs   |

1. 6.5 V  $\leq$  V<sub>S</sub>  $\leq$  16 V (Diagnostic operation range).

2. 4.5 V  $\leq$  V\_S < 6.5 V and 16 V < V\_S  $\leq$  32 V (Extended operation range).

3. 9 V  $\leq$  V  $_{S}$   $\leq$  16 V (Nominal operating range)  $R_{L}$   $\leq$  6  $\Omega,~I_{O}$   $\leq$  IO\_{OC}.

#### Table 5. Diagnostic table (operating range: 4.5 V $\leq$ V\_S $\leq$ 32 V)

| Conditions                               |                                                         | EN          | IN          | Out                             | Diag.       |

|------------------------------------------|---------------------------------------------------------|-------------|-------------|---------------------------------|-------------|

| Normal                                   | function                                                | L<br>H<br>H | X<br>L<br>H | off<br>off<br>on <sup>(1)</sup> | L<br>L<br>H |

| GND short                                | VO <sub>typ</sub> < 0.55 V                              | L           | х           | off                             | н           |

| Load bypass                              | $\Delta VO_{1,2} \ge 1.25 \text{ V}$                    | Н           | L           | off                             | н           |

| Open load                                | IO <sub>typ</sub> < 320 mA                              | Н           | Н           | on <sup>(1)</sup>               | L           |

| T <sub>j typ</sub> ≥ 175 °C o            | $T_{j typ} \ge 175 \ ^{\circ}C \ overtemperature^{(2)}$ |             | L<br>H      | off<br>off                      | H<br>L      |

| Latched overload IO <sub>min</sub> > 5 A |                                                         | х           | Н           | off                             | L           |

| Reset overload latch                     |                                                         | х           |             | D.C.                            | D.C.        |

1. for 4.5 V  $\leq$  V  $_S$  < 6.5 V, I  $_O$   $\leq$  2 A diag. table is valid.

2. If one diag. status shows the overtemperature recognition, in parallel this output will be switched OFF internally. The corresponding channel should be switched OFF additional by its Input or ENABLE signal, otherwise the overload latch will be set after t<sub>DOL</sub> is passed. This behavior will be related to the overdrop sensing which will be used as over load recognition.

57

57

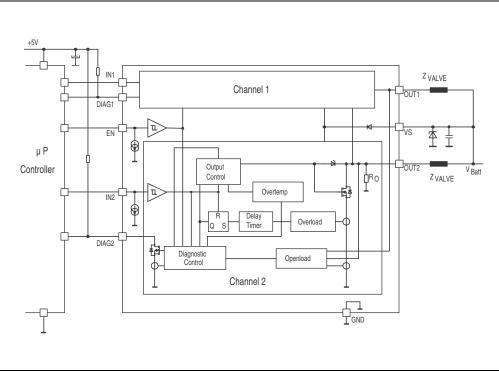

Figure 5. Open load voltage detection block diagram

### 2.4 Circuit description

The L9386 is a dual low side driver for inductive loads like valves in automotive environment.

The device is enabled by a common CMOS compatible ENABLE high signal. The internal pull down current sources at the ENABLE and INPUT pins protect the device in open input conditions against malfunctions. An output slope limitation for du/dt is implemented to reduce the EMI. An integrated active flyback voltage limitation clamps the output voltage during the flyback phase to 50V.

Each driver is protected against short circuit and thermal overload. In short circuit condition the output will be disabled after a short delay time  $t_{DOL}$  to suppress spikes. This disable is latched until a negative slope occur at the correspondent input pin. The thermal disable for  $T_J > 175$  °C of the output will be resetted if the junction temperature decreases about 20 °C below the disable threshold temperature.

For the real time error diagnosis the voltage and the current of the outputs are compared with internal fixed values V<sub>OUV</sub> for OFF and I<sub>OUC</sub> for ON conditions to recognize open load (R<sub>L</sub>  $\geq$  20 kΩ, R<sub>L</sub> > 38Ω) in ON and OFF conditions. The diagnostic operates also in the extended supply voltage range of 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  32 V.

Also the output voltages VO<sub>1,2</sub> are compared against each other in OFF condition with a fixed offset of  $\Delta$ VO<sub>UV 1,2</sub> to recognize GND bypasses. To suppress mail  $\Delta$ VO diagnoses during the flyback phases of the compared output, the  $\Delta$ VO diagnostic

includes a latch function. Reaching the flyback clamping voltage VO<sub>C</sub> the diagnostic signal is resetted by a latch. To activate again this kind of diagnostic a low signal at the correspondent INPUT or the ENABLE pin must occur (see also *Figure 5*).

The diagnostic output level in connection with different ENABLE and INPUT conditions allows to recognize different fail states, like overtemperature, short to VSS, short to GND, bypass to GND and disconnected load (see also *Table 5 on page 6*).

The diagnostic output is also protected against short to  $UD_{max}$ . Oversteping the over load current threshold IO<sub>o</sub>, the output current will be limited internally during the diagnostic overload delay switch-off time  $t_{DOI}$ .

Figure 7. Open load voltage detection block diagram

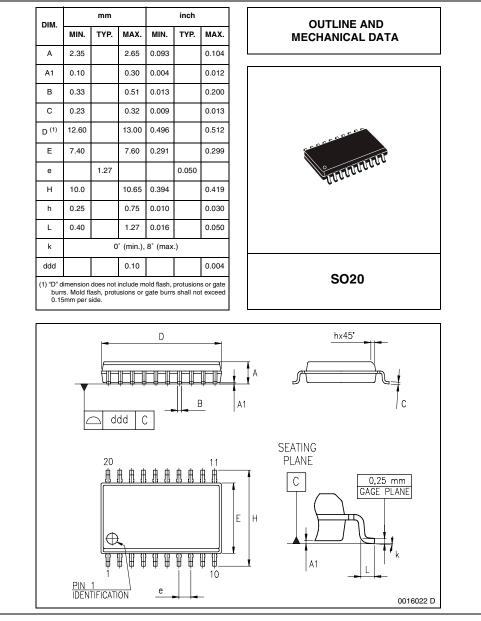

# **3** Package information

In order to meet environmental requirements, ST (also) offers these devices in ECOPACK<sup>®</sup> packages. ECOPACK<sup>®</sup> packages are lead-free. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Figure 8. SO20 mechanical data and package dimensions

57

# 4 Revision history

### Table 6. Document revision history

| Date          | Revision | Changes                                                                   |

|---------------|----------|---------------------------------------------------------------------------|

| 16-Jan-2002   | 1        | Initial release.                                                          |

| 20-Sep-2003   | 2        | Changed company name and logo.                                            |

| 16-Jul-2008 3 |          | Document reformatted.<br>Added <i>Table 1: Device summary on page 1</i> . |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

14/14