## 2Mb Ultra-Low Power Asynchronous CMOS SRAM 128K × 16bit

#### Overview

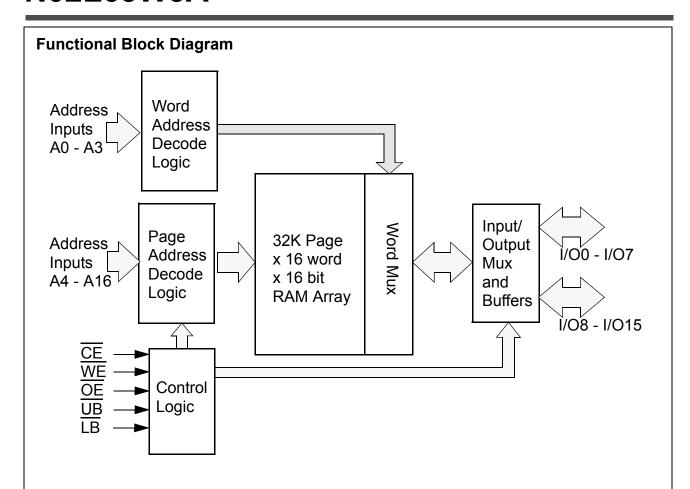

The N02L63W3A is an integrated memory device containing a 2 Mbit Static Random Access Memory organized as 131,072 words by 16 bits. The device is designed and fabricated using ON Semiconductor's advanced CMOS technology to provide both high-speed performance and ultra-low power. The device operates with a single chip enable  $(\overline{CE})$  control and output enable  $(\overline{OE})$  to allow for easy memory expansion. Byte controls  $(\overline{\mathsf{UB}} \ \mathsf{and} \ \overline{\mathsf{LB}})$  allow the upper and lower bytes to be accessed independently. The N02L63W3A is optimal for various applications where low-power is critical such as battery backup and hand-held devices. The device can operate over a very wide temperature range of -40°C to +85°C and is available in JEDEC standard packages compatible with other standard 128Kb x 16 SRAMs.

#### **Features**

- Single Wide Power Supply Range 2.3 to 3.6 Volts

- Very low standby current 2.0µA at 3.0V (Typical)

- Very low operating current

2.0mA at 3.0V and 1µs (Typical)

- Very low Page Mode operating current 0.8mA at 3.0V and 1µs (Typical)

- Simple memory control

Single Chip Enable (CE)

Byte control for independent byte operation Output Enable (OE) for memory expansion

- Low voltage data retention

Vcc = 1.8V

- Very <u>fast</u> output enable access time 30ns OE access time

- · Automatic power down to standby mode

- TTL compatible three-state output driver

- Compact space saving BGA package available

#### **Product Family**

| Part Number | Package Type       | Operating<br>Temperature | Power<br>Supply<br>(Vcc) | Speed       | Standby<br>Current (I <sub>SB</sub> ),<br>Typical | Operating<br>Current (Icc),<br>Typical |

|-------------|--------------------|--------------------------|--------------------------|-------------|---------------------------------------------------|----------------------------------------|

| N02L63W3AB  | 48 - BGA           |                          |                          |             |                                                   |                                        |

| N02L63W3AT  | 44 - TSOP II       | 10001 .0500              | 2 2 1 2 6 1              | 55ns @ 2.7V | 2 4                                               | 2 1 1 1                                |

| N02L63W3AB2 | 48 - BGA Green     | -40°C to +85°C           | 2.30 - 3.00              | 70ns @ 2.3V | 2 μΑ                                              | 2 mA @ 1MHz                            |

| N02L63W3AT2 | 44 - TSOP II Green |                          |                          |             |                                                   |                                        |

## **Pin Configurations**

|   | 1                 | 2                 | 3                     | 4               | 5                | 6                |  |

|---|-------------------|-------------------|-----------------------|-----------------|------------------|------------------|--|

| Α | LB                | OE                | A <sub>0</sub>        | A <sub>1</sub>  | A <sub>2</sub>   | NC               |  |

| В | I/O <sub>8</sub>  | UB                | <b>A</b> <sub>3</sub> | A <sub>4</sub>  | E                | I/O <sub>0</sub> |  |

| С | I/O <sub>9</sub>  | I/O <sub>10</sub> | A <sub>5</sub>        | A <sub>6</sub>  | I/O <sub>1</sub> | I/O <sub>2</sub> |  |

| D | $v_{ss}$          | I/O <sub>11</sub> | NC                    | A <sub>7</sub>  | I/O <sub>3</sub> | $v_{cc}$         |  |

| Ε | $v_{cc}$          | I/O <sub>12</sub> | NC                    | A <sub>16</sub> | I/O <sub>4</sub> | $v_{ss}$         |  |

| F | I/O <sub>14</sub> | I/O <sub>13</sub> | A <sub>14</sub>       | A <sub>15</sub> | I/O <sub>5</sub> | I/O <sub>6</sub> |  |

| G | I/O <sub>15</sub> | NC                | A <sub>12</sub>       | A <sub>13</sub> | WE               | I/O <sub>7</sub> |  |

| Н | NC                | A <sub>8</sub>    | A <sub>9</sub>        | A <sub>10</sub> | A <sub>11</sub>  | NC               |  |

|   | 10.01.004.00      |                   |                       |                 |                  |                  |  |

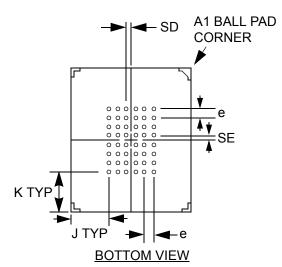

48 Pin BGA (top) 6 x 8 mm

### **Pin Descriptions**

| Pin Name                            | Pin Function            |

|-------------------------------------|-------------------------|

| A <sub>0</sub> -A <sub>16</sub>     | Address Inputs          |

| WE                                  | Write Enable Input      |

| CE                                  | Chip Enable Input       |

| ŌĒ                                  | Output Enable Input     |

| LB                                  | Lower Byte Enable Input |

| UB                                  | Upper Byte Enable Input |

| I/O <sub>0</sub> -I/O <sub>15</sub> | Data Inputs/Outputs     |

| NC                                  | Not Connected           |

| V <sub>CC</sub>                     | Power                   |

| V <sub>SS</sub>                     | Ground                  |

#### **Functional Description**

| CE | WE | OE    | UB             | LB             | I/O <sub>0</sub> - I/O <sub>15</sub> <sup>1</sup> | MODE                 | POWER   |

|----|----|-------|----------------|----------------|---------------------------------------------------|----------------------|---------|

| Н  | Х  | Χ     | Х              | Х              | High Z                                            | Standby <sup>2</sup> | Standby |

| L  | Х  | Х     | Н              | Н              | High Z                                            | Active               | Active  |

| L  | L  | $X^3$ | L <sup>1</sup> | L <sup>1</sup> | Data In                                           | Write <sup>3</sup>   | Active  |

| L  | Н  | L     | L <sup>1</sup> | L <sup>1</sup> | Data Out                                          | Read                 | Active  |

| L  | Н  | Н     | Х              | Х              | High Z                                            | Active               | Active  |

<sup>1.</sup> When  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  are in select mode (low), I/O<sub>0</sub> - I/O<sub>15</sub> are affected as shown. When  $\overline{\text{LB}}$  only is in the select mode only I/O<sub>0</sub> - I/O<sub>7</sub> are affected as shown. When  $\overline{\text{UB}}$  is in the select mode only I/O<sub>8</sub> - I/O<sub>15</sub> are affected as shown.

## Capacitance<sup>1</sup>

| Item              | Symbol           | Test Condition                                         | Min | Max | Unit |

|-------------------|------------------|--------------------------------------------------------|-----|-----|------|

| Input Capacitance | C <sub>IN</sub>  | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25°C |     | 8   | pF   |

| I/O Capacitance   | C <sub>I/O</sub> | V <sub>IN</sub> = 0V, f = 1 MHz, T <sub>A</sub> = 25°C |     | 8   | pF   |

<sup>1.</sup> These parameters are verified in device characterization and are not 100% tested

<sup>2.</sup> When the device is in standby mode, control inputs (WE, OE, UB, and LB), address inputs and data input/outputs are internally isolated from any external influence and disabled from exerting any influence externally.

<sup>3.</sup> When  $\overline{\text{WE}}$  is invoked, the  $\overline{\text{OE}}$  input is internally disabled and has no effect on the circuit.

## Absolute Maximum Ratings<sup>1</sup>

| Item                                            | Symbol              | Rating                       | Unit |

|-------------------------------------------------|---------------------|------------------------------|------|

| Voltage on any pin relative to V <sub>SS</sub>  | V <sub>IN,OUT</sub> | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Voltage on $V_{CC}$ Supply Relative to $V_{SS}$ | V <sub>CC</sub>     | -0.3 to 4.5                  | V    |

| Power Dissipation                               | $P_{D}$             | 500                          | mW   |

| Storage Temperature                             | T <sub>STG</sub>    | -40 to 125                   | °C   |

| Operating Temperature                           | T <sub>A</sub>      | -40 to +85                   | °C   |

| Soldering Temperature and Time                  | T <sub>SOLDER</sub> | 260°C, 10sec                 | °C   |

<sup>1.</sup> Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Operating Characteristics (Over Specified Temperature Range)**

| Item                                                                                                                        | Symbol           | Test Conditions                                                                           | Min.                 | Typ <sup>1</sup> | Max                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------|----------------------|------------------|----------------------|------|

| Supply Voltage                                                                                                              | V <sub>CC</sub>  |                                                                                           | 2.3                  |                  | 3.6                  | V    |

| Data Retention Voltage                                                                                                      | $V_{DR}$         | Chip Disabled <sup>2</sup>                                                                | 1.8                  |                  |                      | V    |

| Input High Voltage                                                                                                          | V <sub>IH</sub>  |                                                                                           | 1.8                  |                  | V <sub>CC</sub> +0.3 | V    |

| Input Low Voltage                                                                                                           | V <sub>IL</sub>  |                                                                                           | -0.3                 |                  | 0.6                  | V    |

| Output High Voltage                                                                                                         | V <sub>OH</sub>  | I <sub>OH</sub> = 0.2mA                                                                   | V <sub>CC</sub> -0.2 |                  |                      | V    |

| Output Low Voltage                                                                                                          | V <sub>OL</sub>  | I <sub>OL</sub> = -0.2mA                                                                  |                      |                  | 0.2                  | V    |

| Input Leakage Current                                                                                                       | I <sub>LI</sub>  | $V_{IN}$ = 0 to $V_{CC}$                                                                  |                      |                  | 0.5                  | μА   |

| Output Leakage Current                                                                                                      | I <sub>LO</sub>  | OE = V <sub>IH</sub> or Chip Disabled                                                     |                      |                  | 0.5                  | μА   |

| Read/Write Operating Supply Current @ 1 µs Cycle Time <sup>2</sup>                                                          | I <sub>CC1</sub> | $V_{CC}$ =3.6 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0           |                      | 2.0              | 4.0                  | mA   |

| Read/Write Operating Supply Current  @ 70 ns Cycle Time <sup>2</sup>                                                        | I <sub>CC2</sub> | $V_{CC}$ =3.6 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0           |                      | 12               | 16.0                 | mA   |

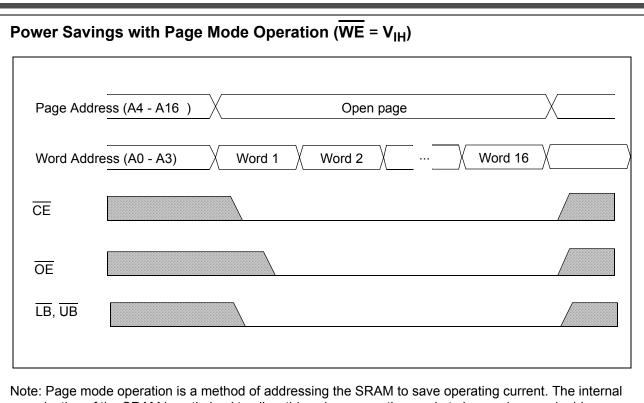

| Page Mode Operating Supply Current @ 70ns Cycle Time <sup>2</sup> (Refer to Power Savings with Page Mode Operation diagram) | I <sub>CC3</sub> | $V_{CC}$ =3.6 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0           |                      | 4                |                      | mA   |

| Read/Write Quiescent Operating Supply Current <sup>3</sup>                                                                  | I <sub>CC4</sub> | $V_{CC}$ =3.6 V, $V_{IN}$ = $V_{IH}$ or $V_{IL}$<br>Chip Enabled, $I_{OUT}$ = 0,<br>f = 0 |                      |                  | 3.0                  | mA   |

| Maximum Standby Current <sup>3</sup>                                                                                        | I <sub>SB1</sub> | $V_{IN} = V_{CC}$ or 0V<br>Chip Disabled<br>$t_A = 85^{\circ}C$ , VCC = 3.6 V             |                      | 2.0              | 20                   | μА   |

| Maximum Data Retention Current <sup>3</sup>                                                                                 | I <sub>DR</sub>  | $V_{CC}$ = 1.8V, $V_{IN}$ = $V_{CC}$ or 0<br>Chip Disabled, $t_A$ = 85°C                  |                      |                  | 10                   | μА   |

<sup>1.</sup> Typical values are measured at Vcc=Vcc Typ.,  $\rm T_A=25^{\circ}C$  and are not 100% tested.

<sup>2.</sup> This parameter is specified with the outputs disabled to avoid external loading effects. The user must add current required to drive output capacitance expected in the actual system.

<sup>3.</sup> This device assumes a standby mode if the chip is disabled ( $\overline{\text{CE}}$  high). In order to achieve low standby current all inputs must be within 0.2 volts of either VCC or VSS

Note: Page mode operation is a method of addressing the SRAM to save operating current. The internal organization of the SRAM is optimized to allow this unique operating mode to be used as a valuable power saving feature.

The only thing that needs to be done is to address the SRAM in a manner that the internal page is left open and 16-bit words of data are read from the open page. By treating addresses A0-A3 as the least significant bits and addressing the 16 words within the open page, power is reduced to the page mode value which is considerably lower than standard operating currents for low power SRAMs.

## **Timing Test Conditions**

| Item                                     |                                           |

|------------------------------------------|-------------------------------------------|

| Input Pulse Level                        | 0.1V <sub>CC</sub> to 0.9 V <sub>CC</sub> |

| Input Rise and Fall Time                 | 5ns                                       |

| Input and Output Timing Reference Levels | 0.5 V <sub>CC</sub>                       |

| Output Load                              | CL = 30pF                                 |

| Operating Temperature                    | -40 to +85 °C                             |

#### **Timing**

| lto-m                                | Cumbal                                | 2.3 - | 2.3 - 3.6 V |      | 2.7 - 3.6 V |       |

|--------------------------------------|---------------------------------------|-------|-------------|------|-------------|-------|

| Item                                 | Symbol                                | Min.  | Max.        | Min. | Max.        | Units |

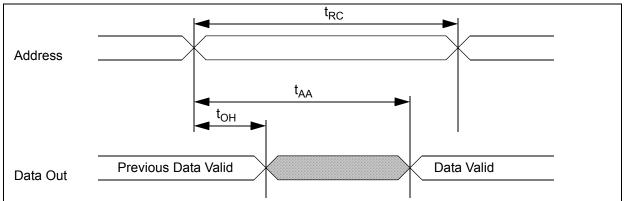

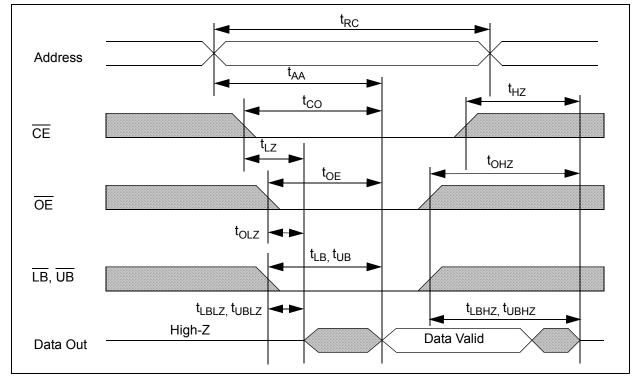

| Read Cycle Time                      | t <sub>RC</sub>                       | 70    |             | 55   |             | ns    |

| Address Access Time                  | t <sub>AA</sub>                       |       | 70          |      | 55          | ns    |

| Chip Enable to Valid Output          | t <sub>CO</sub>                       |       | 70          |      | 55          | ns    |

| Output Enable to Valid Output        | t <sub>OE</sub>                       |       | 35          |      | 30          | ns    |

| Byte Select to Valid Output          | t <sub>LB</sub> , t <sub>UB</sub>     |       | 35          |      | 30          | ns    |

| Chip Enable to Low-Z output          | t <sub>LZ</sub>                       | 10    |             | 10   |             | ns    |

| Output Enable to Low-Z Output        | t <sub>OLZ</sub>                      | 5     |             | 5    |             | ns    |

| Byte Select to Low-Z Output          | t <sub>LBZ</sub> , t <sub>UBZ</sub>   | 10    |             | 10   |             | ns    |

| Chip Disable to High-Z Output        | t <sub>HZ</sub>                       | 0     | 20          | 0    | 20          | ns    |

| Output Disable to High-Z Output      | t <sub>OHZ</sub>                      | 0     | 20          | 0    | 20          | ns    |

| Byte Select Disable to High-Z Output | t <sub>LBHZ</sub> , t <sub>UBHZ</sub> | 0     | 20          | 0    | 20          | ns    |

| Output Hold from Address Change      | t <sub>OH</sub>                       | 10    |             | 10   |             | ns    |

| Write Cycle Time                     | t <sub>WC</sub>                       | 70    |             | 55   |             | ns    |

| Chip Enable to End of Write          | t <sub>CW</sub>                       | 50    |             | 40   |             | ns    |

| Address Valid to End of Write        | t <sub>AW</sub>                       | 50    |             | 40   |             | ns    |

| Byte Select to End of Write          | t <sub>LBW</sub> , t <sub>UBW</sub>   | 50    |             | 40   |             | ns    |

| Write Pulse Width                    | t <sub>WP</sub>                       | 40    |             | 40   |             | ns    |

| Address Setup Time                   | t <sub>AS</sub>                       | 0     |             | 0    |             | ns    |

| Write Recovery Time                  | t <sub>WR</sub>                       | 0     |             | 0    |             | ns    |

| Write to High-Z Output               | t <sub>WHZ</sub>                      |       | 20          |      | 20          | ns    |

| Data to Write Time Overlap           | t <sub>DW</sub>                       | 40    |             | 35   |             | ns    |

| Data Hold from Write Time            | t <sub>DH</sub>                       | 0     |             | 0    |             | ns    |

| End Write to Low-Z Output            | t <sub>OW</sub>                       | 10    |             | 10   |             | ns    |

# Timing of Read Cycle ( $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$ )

## Timing Waveform of Read Cycle ( $\overline{WE} = V_{IH}$ )

## Timing Waveform of Write Cycle (WE control) $t_{WC}$ Address $t_{WR}$ $t_{AW}$ $t_{CW}$ CE $t_{LBW},\,t_{UBW}$ LB, UB $t_{WP}$ $t_{AS}$ $\overline{\mathsf{WE}}$ $t_{DW}$ $t_{DH}$ High-Z Data Valid Data In t<sub>WHZ</sub> ◀ t<sub>OW</sub> High-Z Data Out Timing Waveform of Write Cycle (CE Control) $t_{WC}$ Address $t_{AW}$ CE $t_{CW}$ $t_{AS}$ $t_{LBW},\,t_{UBW}$ LB, UB $t_{WP}$ WE $t_{DW}$ $t_{DH}$

Rev. 15 | Page 8 of 11 | www.onsemi.com

$t_{\text{WHZ}}$

Data Valid

High-Z

Data In

Data Out

#### Note:

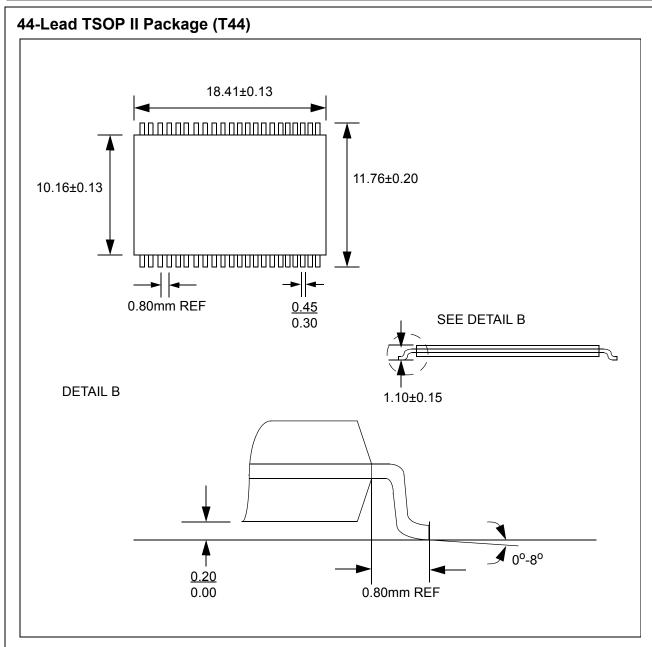

- 1. All dimensions in inches (Millimeters)

- 2. Package dimensions exclude molding flash

# Ball Grid Array Package A1 BALL PAD CORNER (3) 1.24±0.10 1.0.35±0.05 DIA. 2. SEATING PLANE - Z \$\display 0.15 \ Z \\ \$\display 0.05 \ Z \end{align\*} TOP VIEW SIDE VIEW

- 1. DIMENSION IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER. PARALLEL TO PRIMARY Z.

- 2. PRIMARY DATUM Z AND SEATING PLANE ARE DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

- 3. A1 BALL PAD CORNER I.D. TO BE MARKED BY INK.

## **Dimensions (mm)**

| D      | E        |       | BALL<br>MATRIX |       |       |      |  |

|--------|----------|-------|----------------|-------|-------|------|--|

|        | <b>-</b> | SD    | SE             | J     | K     | TYPE |  |

| 6±0.10 | 8±0.10   | 0.375 | 0.375          | 1.125 | 1.375 | FULL |  |

#### **Ordering Information**

| Part Number    | Package                           | Shipping Method |

|----------------|-----------------------------------|-----------------|

| N02L63W3AT5I   | Leaded 44-TSOP II                 | Tray            |

| N02L63W2AT25I  | Green 44-TSOP II (RoHS Compliant) | Tray            |

| N02L63W3AB5I   | Leaded 48-BGA                     | Tray            |

| N02L63W3AB25I  | Green 48-BGA (RoHS Compliant)     | Tray            |

| N02L63W3AT5IT  | Leaded 44-TSOP II                 | Tape & Reel     |

| N02L63W3AT25IT | Green 44-TSOP II (RoHS Compliant) | Tape & Reel     |

| N02L63W3AB5IT  | Leaded 48-BGA                     | Tape & Reel     |

| N02L63W3AB25IT | Green 48-BGA (RoHS Compliant)     | Tape & Reel     |

#### **Revision History**

| Revision # | Date           | Change Description                                                                                                                                                                                                           |

|------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α          | Dec. 1999      | Initial Preliminary Release                                                                                                                                                                                                  |

| В          | Sept. 2000     | Modified Voltage Range and Standby Current Limits.                                                                                                                                                                           |

| С          | Oct. 2000      | Added Missing Tas Parameter Specification.                                                                                                                                                                                   |

| D          | Oct. 2000      | Modified Standby Current Specifications.                                                                                                                                                                                     |

| Е          | Jan. 2001      | Extensive Modification to use voltage regulator design                                                                                                                                                                       |

| F          | Mar. 2001      | Modified BGA pinout, access time 70ns @ 2.7V, misc. errata                                                                                                                                                                   |

| G          | May 2001       | Changed access time to 55ns, modified 44-Lead TSOP Package diagram                                                                                                                                                           |

| Н          | June 2001      | Revised voltage range in Timing table, revised Dimensions table                                                                                                                                                              |

| I          | Sept. 2001     | Minor parametric modifications, full production release                                                                                                                                                                      |

| J          | Dec. 2001      | Part number change from EM128L16, modified Overview and Features, added Page Mode Operation diagram, revised Operating Characteristics table, Package diagram, Functional Description table and Ordering Information diagram |

| K          | Nov. 2002      | Replaced Isb and Icc on Product Family table with typical values                                                                                                                                                             |

| L          | Oct. 2004      | Added Pb-Free and Green Package Option                                                                                                                                                                                       |

| М          | Nov. 2005      | Removed Pb-Free Pkg, added Green Pkg and RoHS Compliant                                                                                                                                                                      |

| N          | September 2006 | Converted to AMI Semiconductor                                                                                                                                                                                               |

| 15         | July 2008      | Converted to ON Semiconductor and new part numbers                                                                                                                                                                           |

ON Semiconductor and unare registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, SCILLC assume any liability arising out of the application or use of any product or circuit, and specification gloscalims any and all liability, including without imitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor PO Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East & Africa Technical Support: Phone Order Literature: http://www.onsemi.com/orderlit

421-33-790-2910

Japan Customer Focus Center: Phone 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

For additional information, please contact your local Sales Representative