### **General Description**

The MAX8759 integrated cold-cathode fluorescent lamp (CCFL) inverter controller is designed to drive CCFLs using a full-bridge resonant inverter. The resonant operation ensures reliable striking and provides near-sinusoidal waveforms over the entire input range. The controller operates over a wide input-voltage range of 4.5V to 28V with high power to light efficiency. The device also includes safety features that effectively protect against single-point fault conditions such as lamp-out, secondary overvoltage, and secondary short-circuit faults.

The MAX8759 provides accurate lamp-current regulation (±2.5%) for superior CCFL inverter performance. The lamp current is adjustable with an external resistor; 10:1 dimming range can be achieved by turning the CCFL on and off using a digital pulse-width modulation (DPWM) method, while maintaining the lamp-current constant. The MAX8759 provides three mechanisms for controlling brightness: 2-wire SMBus™-compatible interface, external ambient-light sensor (ALS), or system PWM control. The MAX8759 supports Intel display power-saving technology (DPST) to maximize battery life. The device includes two lamp-current feedback input pins that support dual-lamp applications with a minimum number of external components.

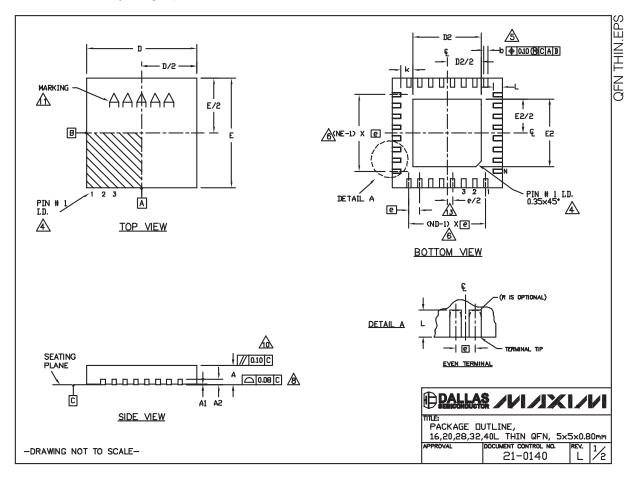

The MAX8759 controls a full-bridge inverter for maximum efficiency and directly drives four external n-channel power MOSFETs. An internal 5.35V linear regulator powers the MOSFET drivers and most of the internal circuitry. The MAX8759 is available in a space-saving, 28-pin, thin QFN package and operates over a -40°C to +85°C temperature range.

#### **Applications**

Notebooks LCD Monitors Automotive Infotainment

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-<br>PACKAGE              | PKG<br>CODE |

|-------------|----------------|------------------------------|-------------|

| MAX8759ETI+ | -40°C to +85°C | 28 Thin QFN-EP*<br>5mm × 5mm | T2855-6     |

- +Denotes a lead-free package.

- \*EP = Exposed pad.

Pin Configuration appears at end of data sheet.

SMBus is a trademark of Intel Corp.

#### **Features**

- **♦ Accurate Dimming Control Using SMBus, PWM** Interface, or Ambient Light Sensor

- ♦ 10:1 Dimming Range with 256-Step Resolution

- **♦ Resonant-Mode Operation**

Longer Lamp Life with Near Sinusoidal Lamp-**Current Waveform Guaranteed Striking Capability**

- **High-Power-to-Light Efficiency** ♦ Wide Input-Voltage Range (4.5V to 28V)

- ♦ Input Feed-Forward for Excellent Line Rejection

- **♦** ±2.5% Lamp-Current Regulation

- **♦** Adjustable 1.5% Accurate DPWM Frequency

- **♦ Dual Lamp-Current Feedback Inputs**

- **♦ Comprehensive Fault Protection** Secondary Voltage Limiting **Primary Current Limit with Lossless Sensing Lamp-Out Protection with Adjustable Timeout Secondary Short-Circuit Protection**

- ♦ Small 28-Pin, 5mm x 5mm, Thin QFN Package

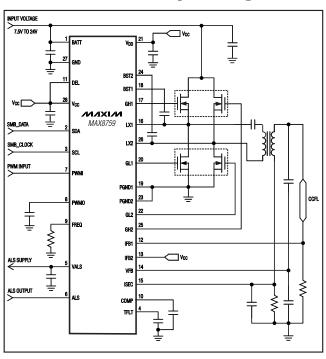

### Minimal Operating Circuit

MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| BATT to GND              | 0.3V to +30V                       | IFB1, IFB2, ISEC, VFB to GND             | 3V to +6V      |

|--------------------------|------------------------------------|------------------------------------------|----------------|

| BST1, BST2 to GND        | 0.3V to +36V                       | PGND1, PGND2 to GND                      | 0.3V to +0.3V  |

| BST1 to LX1, BST2 to LX2 | 0.3V to +6V                        | Continuous Power Dissipation (TA = +70°C | <b>(</b> )     |

| FREQ, VCC, VDD to GND    | 0.3V to +6V                        | 28-Pin Thin QFN 5mm x 5mm                |                |

| SDA, SCL to GND          | 0.3V to +6V                        | (derate 21.3mW/°C above +70°C)           | 1702mW         |

| ALS, COMP, PWMI, PWMO,   |                                    | Operating Temperature Range              | 40°C to +85°C  |

| TFLT, DEL, VALS to GND   | 0.3V to (V <sub>CC</sub> + 0.3V)   | Junction Temperature                     | +150°C         |

| GH1 to LX1               | 0.3V to (V <sub>BST1</sub> + 0.3V) | Storage Temperature Range                | 65°C to +150°C |

| GH2 to LX2               | 0.3V to (V <sub>BST2</sub> + 0.3V) | Lead Temperature (soldering, 10s)        | +300°C         |

| GL1, GL2 to GND          | 0.3V to (V <sub>DD</sub> + 0.3V)   |                                          |                |

|                          |                                    |                                          |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1, VBATT = 12V, VCC = VDD, TA = 0°C to +85°C. Typical values are at TA = +25°C, unless otherwise noted.)

| PARAMETER CONDITIONS                             |                                                     | ITIONS                                                | MIN | TYP  | MAX  | UNITS |

|--------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|-----|------|------|-------|

| DATT Innut Valtage Denge                         | VCC = VDD = VBATT                                   |                                                       | 4.5 |      | 5.5  | V     |

| BATT Input Voltage Range                         | $V_{CC} = V_{DD} = open$                            | V <sub>CC</sub> = V <sub>DD</sub> = open              |     |      | 28.0 | v     |

| BATT Quiescent Current                           | MAX8759 is enabled                                  | V <sub>BATT</sub> = 28V                               |     | 2.5  | 5    | mA    |

| DATT Quiescent Current                           | IVIAA6739 IS EHADIEU                                | V <sub>BATT</sub> = V <sub>CC</sub> = 5V              |     |      | 5    | IIIA  |

| BATT Quiescent Current, Shutdown                 | MAX8759 is disabled                                 |                                                       |     | 100  | 200  | μΑ    |

| V <sub>CC</sub> Output Voltage, Normal Operation | MAX8759 is enabled,<br>0 < I <sub>LOAD</sub> < 10mA | 6V < V <sub>BATT</sub> < 28V,                         | 5.2 | 5.35 | 5.5  | V     |

| V <sub>CC</sub> Output Voltage, Shutdown         | MAX8759 is disabled                                 | , no load                                             | 3.5 | 4.3  | 5.5  | V     |

| Varalladamialtaria Lagica it Threehold           | V <sub>CC</sub> rising (leaving lo                  | ckout)                                                |     |      | 4.3  | V     |

| V <sub>CC</sub> Undervoltage Lockout Threshold   | V <sub>CC</sub> falling (entering I                 | V <sub>CC</sub> falling (entering lockout)            |     |      |      | V     |

| V <sub>CC</sub> Undervoltage Lockout Hysteresis  |                                                     |                                                       |     | 230  |      | mV    |

| V <sub>CC</sub> POR Threshold                    | Rising edge                                         |                                                       |     | 1.75 |      | V     |

| V <sub>CC</sub> POR Hysteresis                   |                                                     |                                                       |     | 50   |      | mV    |

| GH1, GH2, GL1, GL2 On-Resistance,<br>Low State   | ITEST = 100mA, V <sub>CC</sub> =                    | ITEST = 100mA, V <sub>CC</sub> = V <sub>DD</sub> = 5V |     | 3    | 6    | Ω     |

| GH1, GH2, GL1, GL2 On-Resistance,<br>High State  | ITEST = 100mA, V <sub>CC</sub> =                    | = V <sub>DD</sub> = 5V                                |     | 10   | 18   | Ω     |

| BST1, BST2 Leakage Current                       | V <sub>BST</sub> _ = 12V, V <sub>L</sub> X_ =       | 7V                                                    |     | 4    | 10   | μΑ    |

| Resonant Frequency Range                         | Guaranteed by design                                | n                                                     | 30  |      | 80   | kHz   |

| Minimum On-Time                                  |                                                     |                                                       | 350 | 500  | 700  | ns    |

| Maximum Off-Time                                 |                                                     |                                                       | 40  | 60   | 80   | μs    |

| Current-Limit Threshold                          | LX1 - PGND1, LX2 - F                                | LX1 - PGND1, LX2 - PGND2                              |     | 430  | 445  | mV    |

| Zero-Current-Crossing Threshold                  | LX1 - PGND1, LX2 - PGND2                            |                                                       | 3   | 8    | 13   | mV    |

| Current-Limit Leading-Edge Blanking              | rent-Limit Leading-Edge Blanking                    |                                                       |     | 350  |      | ns    |

| -B1, IFB2 Input-Voltage Range                    |                                                     | -3                                                    |     | +3   | V    |       |

| IFB1 Regulation Point                            |                                                     |                                                       | 765 | 785  | 805  | mV    |

| IFB2 Regulation Point                            |                                                     |                                                       | 780 | 800  | 820  | mV    |

2 /VI/IXI/VI

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{BATT} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = 0$ °C to +85°C. Typical values are at  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                                      | CONDITIONS                                                                | MIN  | TYP  | MAX  | UNITS |

|----------------------------------------------------------------|---------------------------------------------------------------------------|------|------|------|-------|

| JEDA JEDO L. L.D.: O. L.                                       | 0 < V <sub>IFB1,2</sub> < 3V                                              | -3   |      | +3   |       |

| IFB1, IFB2 Input Bias Current                                  | -3V < V <sub>IFB1,2</sub> < 0                                             | -230 |      |      | μΑ    |

| IFB1, IFB2 Lamp-Out Threshold                                  |                                                                           | 575  | 600  | 625  | mV    |

| IFB1, IFB2 to COMP Transconductance                            | 0.5V < V <sub>COMP</sub> < 4V                                             | 60   | 100  | 160  | μS    |

| COMP Output Impedance                                          |                                                                           | 6    | 12   | 24   | МΩ    |

| COMP Discharge Current During Overvoltage or Overcurrent Fault | V <sub>VFB</sub> = 2.6V or V <sub>ISEC</sub> = 1.5V                       | 500  | 1000 | 2000 | μΑ    |

| COMP Discharge Current During DPWM Off-Time                    | $V_{COMP} = 1.5V$                                                         | 90   | 110  | 130  | μΑ    |

| DPWM Rising-to-Falling Ratio                                   | V <sub>IFB1,2</sub> = 0                                                   |      | 2.5  |      |       |

| ISEC Input Voltage Range                                       |                                                                           | -3   |      | +3   | V     |

| ISEC Overcurrent Threshold                                     |                                                                           | 1.18 | 1.21 | 1.26 | V     |

| ISEC Input Bias Current                                        | V <sub>ISEC</sub> = 1.25V                                                 | -0.3 |      | +0.3 | μΑ    |

| VFB Input Voltage Range                                        |                                                                           | -4   |      | +4   | V     |

| VFB Input Impedance                                            |                                                                           | 150  | 300  | 450  | МΩ    |

| VFB Overvoltage Threshold                                      |                                                                           | 2.2  | 2.3  | 2.4  | V     |

| VFB Undervoltage Threshold                                     |                                                                           | 210  | 240  | 280  | mV    |

| VFB Undervoltage Delay                                         | $R_{FREQ} = 169k\Omega$                                                   |      | 250  |      | μs    |

|                                                                | $R_{FREQ} = 169k\Omega$ , $T_A = +25^{\circ}C$ to $+85^{\circ}C$          | 207  | 210  | 213  |       |

| DMM Oscillator Fraguency                                       | $R_{FREQ} = 169k\Omega$                                                   | 205  | 210  | 215  | Hz    |

| DPWM Oscillator Frequency                                      | $R_{FREQ} = 340 k\Omega$                                                  |      | 106  |      |       |

|                                                                | $R_{FREQ} = 100k\Omega$                                                   |      | 343  |      |       |

| PWMO Output Impedance                                          |                                                                           | 20   | 40   | 60   | kΩ    |

| PWMI Input Low Voltage                                         |                                                                           |      |      | 0.7  | V     |

| PWMI Input High Voltage                                        |                                                                           | 2.1  |      |      | V     |

| PWMI Input Hysteresis                                          |                                                                           |      | 300  |      | mV    |

| PWMI Input Bias Current                                        |                                                                           | -0.3 |      | +0.3 | μΑ    |

| PWMI Input Frequency Range                                     |                                                                           | 5    |      | 50   | kHz   |

| PWMI Full-Range Accuracy                                       |                                                                           |      |      | 5    | LSB   |

|                                                                | PWMI duty cycle = 100%                                                    | 98   | 100  |      |       |

| PWMI Brightness Setting                                        | PWMI duty cycle = 50%                                                     | 48   | 50   | 52   | %     |

|                                                                | PWMI duty cycle = 0%                                                      | 9.7  | 10.0 | 10.3 |       |

| ALS Full-Adjustment Range                                      |                                                                           | 0    |      | 1.8  | V     |

| ALS Full-Range Accuracy                                        |                                                                           |      |      | 5    | LSB   |

| ALS Input Bias Current                                         |                                                                           | -0.1 |      | +0.1 | μΑ    |

| VALS Output Voltage                                            | MAX8759 is enabled, 6V < V <sub>BATT</sub> < 28V, I <sub>LOAD</sub> = 1mA | 5.10 | 5.30 | 5.50 | V     |

| VALS Leakage Current                                           | MAX8759 is disabled, VALS = GND                                           | -3   |      | +3   | μΑ    |

| VALS On-Resistance                                             | MAX8759 is enabled                                                        |      | 30   | 60   | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{BATT} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = 0$ °C to +85°C. Typical values are at  $T_A = +25$ °C, unless otherwise noted.)

| PARAMETER                                                          | CONDITIONS                                                                    | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------|------|-------|

| Zara Crassina Dalau                                                | $V_{BATT} = 9V, R_{THR} = 120k\Omega$                                         | 0    | 0.15 | 0.30 |       |

| Zero-Crossing Delay                                                | $V_{BATT} = 12V, R_{THR} = 120k\Omega$                                        | 1.50 | 1.80 | 2.10 | μs    |

| Maximum Zero-Crossing Delay                                        | $V_{BATT} = 18V, R_{THR} = 120k\Omega$                                        | 3.2  | 3.8  | 4.4  | μs    |

| DEL Disable Threshold                                              | DEL rising                                                                    |      |      | 4.5  | · V   |

| DEL DISABle Mireshold                                              | DEL falling                                                                   | 3.8  |      |      | V     |

|                                                                    | V <sub>ISEC</sub> < 1.25V and V <sub>IFB</sub> < 540mV; V <sub>FLT</sub> = 2V | 0.9  | 1.0  | 1.1  |       |

| TFLT Charge Current                                                | $V_{ISEC}$ < 1.25V and $V_{IFB}$ > 660mV; $V_{FLT}$ = 2V                      | -1.5 | -1.2 | -0.8 | μΑ    |

|                                                                    | $V_{ISEC} > 1.25V$ and $V_{IFB} > 660mV$ ; $V_{FLT} = 2V$                     | 115  | 135  | 155  |       |

| TFLT Trip Threshold                                                | Rising edge                                                                   | 3.7  | 4    | 4.3  | V     |

| SDA, SCL, Input Low Voltage                                        |                                                                               |      |      | 0.7  | V     |

| SDA, SCL, Input High Voltage                                       |                                                                               | 2.1  |      |      | V     |

| SDA, SCL, Input Hysteresis                                         |                                                                               |      | 100  |      | mV    |

| SDA, SCL, Input Bias Current                                       |                                                                               | -1   |      | +1   | μΑ    |

| SDA Output Low Sink Current                                        | V <sub>SDA</sub> = 0.4V                                                       | 4    |      |      | mA    |

| SMBus Frequency                                                    |                                                                               | 10   |      | 100  | kHz   |

| SMBus Free Time                                                    | tBUF                                                                          | 4.7  | 1    |      | μs    |

| SCL Serial Clock High Period                                       | thigh                                                                         | 4    |      |      | μs    |

| SCL Serial Clock Low Period                                        | t <sub>LOW</sub>                                                              | 4.7  |      |      | μs    |

| START Condition Setup Time                                         | tsu:sta                                                                       | 4.7  |      |      | μs    |

| START Condition Hold Time                                          | thD:STA                                                                       | 4    |      |      | μs    |

| STOP Condition Setup Time from SCL                                 | tsu:sto                                                                       | 4    |      |      | μs    |

| SDA Valid to SCL Rising-Edge Setup Time,<br>Slave Clocking in Data | tsu:DAT                                                                       | 250  |      |      | ns    |

| SCL Falling Edge to SDA Transition                                 | t <sub>HD:DAT</sub>                                                           | 0    |      |      | ns    |

| SCL Falling Edge to SDA Valid, Reading Out Data                    | tov                                                                           | 200  |      |      | ns    |

#### **ELECTRICAL CHARACTERISTICS**

(Circuit of Figure 1,  $V_{BATT} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = -40$ °C to +85°C.) (Note 1)

| PARAMETER                                                      | COND                                                | MIN                           | TYP  | MAX | UNITS |     |

|----------------------------------------------------------------|-----------------------------------------------------|-------------------------------|------|-----|-------|-----|

| DATT Input Veltage Denge                                       | VCC = VDD = VBATT                                   |                               | 4.5  |     | 5.5   | V   |

| BATT Input Voltage Range                                       | VCC = VDD = open                                    |                               | 5.5  |     | 28.0  | ] V |

| DATT Outless and Current                                       | MAYO7FO is enabled                                  | V <sub>BATT</sub> = 28V       |      |     | 5     | Λ   |

| BATT Quiescent Current                                         | MAX8759 is enabled                                  | VBATT = VCC = 5V              |      |     | 5     | mA  |

| V <sub>CC</sub> Output Voltage, Normal Operation               | MAX8759 is enabled,<br>0 < I <sub>LOAD</sub> < 10mA | 6V < V <sub>BATT</sub> < 28V, | 5.2  |     | 5.5   | V   |

| V <sub>CC</sub> Output Voltage, Shutdown                       | MAX8759 is disabled                                 | , no load                     | 3.5  |     | 5.5   | V   |

| V Undervoltege Leekeut Threehold                               | V <sub>CC</sub> rising (leaving lo                  | ckout)                        |      |     | 4.3   | V   |

| V <sub>CC</sub> Undervoltage Lockout Threshold                 | V <sub>CC</sub> falling (entering I                 | ockout)                       | 3.7  |     |       | V   |

| GH1, GH2, GL1, GL2 On-Resistance,<br>Low State                 | ITEST = 100mA, V <sub>CC</sub> =                    | = V <sub>DD</sub> = 5V        |      |     | 6     | Ω   |

| GH1, GH2, GL1, GL2 On-Resistance,<br>High State                | I <sub>TEST</sub> = 100mA, V <sub>CC</sub> =        | = V <sub>DD</sub> = 5V        |      |     | 18    | Ω   |

| Resonant Frequency Range                                       | Guaranteed by design                                | n                             | 30   |     | 80    | kHz |

| Minimum On-Time                                                |                                                     |                               | 350  |     | 700   | ns  |

| Maximum Off-Time                                               |                                                     |                               | 40   |     | 80    | μs  |

| Current-Limit Threshold                                        | LX1 - PGND1, LX2 - F                                | LX1 - PGND1, LX2 - PGND2      |      |     | 450   | mV  |

| Zero-Current Crossing Threshold                                | LX1 - PGND1, LX2 - F                                | LX1 - PGND1, LX2 - PGND2      |      |     | 13    | mV  |

| IFB1, IFB2 Input Voltage Range                                 |                                                     |                               | -3   |     | +3    | V   |

| IFB1 Regulation Point                                          |                                                     |                               | 760  |     | 810   | mV  |

| IFB2 Regulation Point                                          |                                                     |                               | 775  |     | 825   | mV  |

| IFB1, IFB2 Input Bias Current                                  | -3V < V <sub>IFB1,2</sub> < 0                       |                               | -230 |     |       | μΑ  |

| IFB1, IFB2 Lamp-Out Threshold                                  |                                                     |                               | 565  |     | 635   | mV  |

| IFB1, IFB2 to COMP Transconductance                            | 0.5V < V <sub>COMP</sub> < 4V                       |                               | 60   |     | 160   | μS  |

| COMP Output Impedance                                          |                                                     |                               | 6    |     | 25    | MΩ  |

| COMP Discharge Current During Overvoltage or Overcurrent Fault | V <sub>VFB</sub> = 2.6V or V <sub>ISEC</sub> = 1.5V |                               | 500  |     | 2000  | μΑ  |

| COMP Discharge Current During DPWM Off-Time                    | V <sub>COMP</sub> = 1.5V                            |                               | 90   |     | 130   | μΑ  |

| ISEC Input Voltage Range                                       |                                                     |                               | -3   |     | +3    | V   |

| ISEC Overcurrent Threshold                                     |                                                     |                               | 1.18 |     | 1.26  | V   |

| VFB Input Voltage Range                                        |                                                     |                               | -4   |     | +4    | V   |

| VFB Input Impedance                                            |                                                     |                               | 150  |     | 450   | MΩ  |

| VFB Overvoltage Threshold                                      |                                                     |                               | 2.2  |     | 2.4   | V   |

| VFB Undervoltage Threshold                                     |                                                     |                               | 210  |     | 280   | mV  |

| DPWM Oscillator Frequency                                      | $R_{FREQ} = 169 k\Omega$                            |                               | 203  |     | 217   | Hz  |

| PWMO Output Impedance                                          |                                                     |                               | 20   |     | 60    | kΩ  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(Circuit of Figure 1,  $V_{BATT}$  = 12V,  $V_{CC}$  =  $V_{DD}$ ,  $T_A$  = -40°C to +85°C.) (Note 1)

| PARAMETER                                                          | CONDITIONS                                                                   | MIN  | TYP | MAX  | UNITS    |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------|------|-----|------|----------|--|--|

| PWMI Input Low Voltage                                             |                                                                              |      |     | 0.7  | V        |  |  |

| PWMI Input High Voltage                                            |                                                                              | 2.1  |     |      | V        |  |  |

| PWMI Input Frequency Range                                         |                                                                              | 5    |     | 50   | kHz      |  |  |

|                                                                    | PWMI duty cycle = 100%                                                       | 98   |     |      |          |  |  |

| PWMI Brightness Setting                                            | PWMI duty cycle = 50%                                                        | 48   |     | 52   | %        |  |  |

|                                                                    | PWMI duty cycle = 0%                                                         |      |     | 10.3 | <u> </u> |  |  |

| ALS Full-Adjustment Range                                          |                                                                              | 0    |     | 1.8  | V        |  |  |

| VALS Output Voltage                                                | MAX8759 is enabled, 6V < V <sub>BATT</sub> < 28V,<br>I <sub>LOAD</sub> = 1mA | 5.10 |     | 5.50 | V        |  |  |

| VALS On-Resistance                                                 | MAX8759 is enabled                                                           |      |     | 60   | Ω        |  |  |

| 7 0 : 51                                                           | $V_{BATT} = 9V, R_{THR} = 100k\Omega$                                        | 0    |     | 0.3  |          |  |  |

| Zero-Crossing Delay                                                | $V_{BATT} = 12V, R_{THR} = 100k\Omega$                                       | 1.50 |     | 2.10 | μs       |  |  |

| Maximum Zero-Crossing Delay                                        | $V_{BATT} = 16V, R_{THR} = 100k\Omega$                                       | 3.2  |     | 4.4  | μs       |  |  |

| DEL Disable Threshold                                              | DEL rising                                                                   |      |     | 4.5  | 5 V      |  |  |

| DEL Disable Threshold                                              | DEL falling                                                                  | 3.9  |     |      |          |  |  |

|                                                                    | VISEC < 1.25V and VIFB < 540mV; VFLT = 2V                                    | 0.8  |     | 1.2  |          |  |  |

| FLT Charge Current                                                 | VISEC < 1.25V and VIFB > 660mV; VFLT = 2V                                    | -1.5 |     | -0.8 | μΑ       |  |  |

|                                                                    | $V_{ISEC} > 1.25V$ and $V_{IFB} > 660mV$ ; $V_{FLT} = 2V$                    | 115  |     | 155  |          |  |  |

| TFLT Trip Threshold                                                | Rising edge                                                                  | 3.7  |     | 4.3  | V        |  |  |

| SDA, SCL, Input Low Voltage                                        |                                                                              |      |     | 0.7  | V        |  |  |

| SDA, SCL, Input High Voltage                                       |                                                                              | 2.1  |     |      | V        |  |  |

| SDA Output Low-Sink Current                                        | $V_{SDA} = 0.4V$                                                             | 4    |     |      | mA       |  |  |

| SMBus Frequency                                                    |                                                                              | 10   |     | 100  | kHz      |  |  |

| SMBus Free Time                                                    | tBUF                                                                         | 4.7  |     |      | μs       |  |  |

| SCL Serial Clock High Period                                       | thigh                                                                        | 4    |     |      | μs       |  |  |

| SCL Serial Clock Low Period                                        | tLOW                                                                         | 4.7  |     |      | μs       |  |  |

| START Condition Setup Time                                         | <sup>t</sup> su:sta                                                          | 4.7  |     |      | μs       |  |  |

| START Condition Hold Time                                          | thd:sta                                                                      | 4    |     |      | μs       |  |  |

| STOP Condition Setup Time from SCL                                 | tsu:sto                                                                      | 4    |     |      | μs       |  |  |

| SDA Valid to SCL Rising-Edge Setup Time,<br>Slave Clocking in Data | tsu:dat                                                                      | 250  |     |      | ns       |  |  |

| SCL Falling Edge to SDA Transition                                 | thd:dat                                                                      | 0    |     |      | ns       |  |  |

| SCL Falling Edge to SDA Valid,<br>Reading Out Data                 | t <sub>DV</sub>                                                              | 200  |     |      | ns       |  |  |

**Note 1:** Specifications to -40°C are guaranteed by design, not production tested.

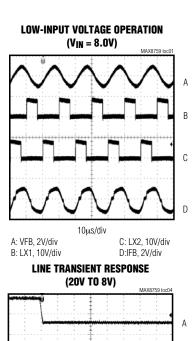

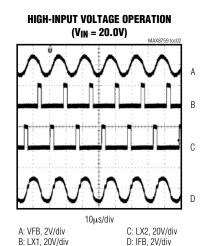

### **Typical Operating Characteristics**

(Circuit of Figure 1,  $V_{IN}$  = 12V,  $V_{CC}$  =  $V_{DD}$ ,  $T_A$  = +25°C, unless otherwise noted.)

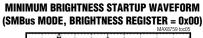

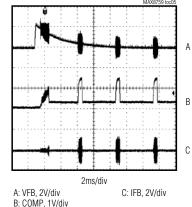

MINIMUM BRIGHTNESS DPWM OPERATION (SMBus MODE, BRIGHTNESS REGISTER = 0x00)

A: V<sub>IN</sub>, 10V/div

B: COMP, 2V/div

## **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = +25$ °C, unless otherwise noted.)

### **Typical Operating Characteristics (continued)**

(Circuit of Figure 1,  $V_{IN} = 12V$ ,  $V_{CC} = V_{DD}$ ,  $T_A = +25$ °C, unless otherwise noted.)

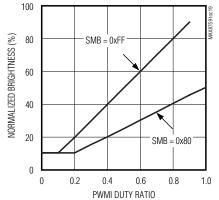

# NORMALIZED BRIGHTNESS vs. SMBus Brightness and PWMI Duty Cycle

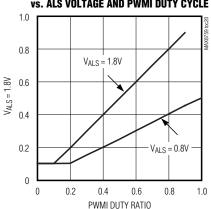

# NORMALIZED BRIGHTNESS vs. ALS VOLTAGE AND PWMI DUTY CYCLE

#### ALS TRANSIENT RESPONSE (ALSDEL1 = ALSDEL0 = 0)

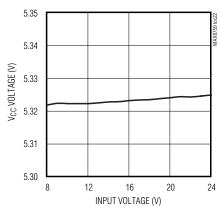

#### **V<sub>CC</sub> LINE REGULATION**

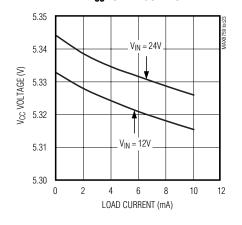

#### **V<sub>CC</sub> LOAD REGULATION**

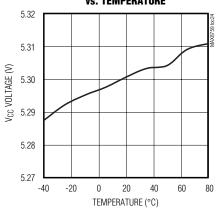

## V<sub>CC</sub> VOLTAGE vs. Temperature

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | BATT | Supply Input. BATT is the input to the internal 5.35V linear regulator that powers the device. Bypass BATT to GND with a 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | SDA  | SMBus Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3   | SCL  | SMBus Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4   | TFLT | Fault-Timer Adjustment Pin. Connect a capacitor from TFLT to GND to set the time-out periods for open-lamp and secondary overcurrent faults.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5   | VALS | Ambient-Light-Sensor Supply Pin. Bypass VALS to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | ALS  | Ambient-Light-Sensor Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7   | PWMI | DPST Control Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8   | PWMO | DPST Buffer Output. Connect a capacitor between PWMO and GND. The capacitor forms a lowpass filter with an internal $40k\Omega$ (typ) resistor for filtering the DPST signal.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9   | FREQ | Chopping-Frequency Adjustment Pin. Connect a resistor from FREQ to GND to set the DPWM frequency: $f_{DPWM} = 210 Hz \times 169 k\Omega / R_{FREQ}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10  | COMP | Transconductance Error Amplifier Output. A compensation capacitor connected between COMP and GND sets the rise and fall time of the lamp-current envelope in DPWM operation.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11  | DEL  | Adaptive Zero-Crossing-Delay Adjustment Pin. Connect a resistor between DEL and GND to adjust the range of the zero-crossing delay. Connecting DEL to V <sub>CC</sub> disables the zero-crossing delay function.                                                                                                                                                                                                                                                                                                                                                                                  |

| 12  | IFB1 | Lamp-Current-Feedback Input. The IFB1 sense signal is internally full-wave rectified. IFB1 is compared with IFB2 and the larger is used for lamp-current regulation. The average value of the rectified signal is regulated to 785mV (typ) by controlling the on-time of high-side switch. An open-lamp fault is generated if the peak voltage of IFB1 is below 600mV for a fault delay period set by TFLT.                                                                                                                                                                                       |

| 13  | IFB2 | Lamp-Current-Feedback Input. The IFB2 sense signal is internally full-wave rectified. IFB1 is compared with IFB2 and the larger is used for lamp-current regulation. The average value of the rectified signal is regulated to 800mV (typ) by controlling the on-time of high-side switch. An open-lamp fault is generated if the peak voltage of IFB2 is below 600mV for a fault-delay period set by TFLT. IFB2 input can be disabled by connecting IFB2 to VCC.                                                                                                                                 |

| 14  | VFB  | Transformer Secondary Voltage-Feedback Input. A capacitive voltage-divider between the high-voltage terminal of the CCFL tube and GND sets the maximum average lamp voltage during striking and lamp-out fault. When the peak voltage on VFB exceeds the internal overvoltage threshold, the controller turns on an internal current sink, discharging the COMP capacitor to limit the switch on-time. The VFB pin is also used to detect a secondary undervoltage condition. If the peak voltage on VFB is below 230mV continuously for 250µs during the DPWM ON period, the MAX8759 shuts down. |

| 15  | ISEC | Transformer Secondary Current-Feedback Input. A current-sense resistor connected between the low-voltage end of the transformer secondary and the ground sets the maximum secondary current during short-circuit fault. When the peak voltage on ISEC exceeds the internal overcurrent threshold, the controller turns on an internal current sink discharging the COMP capacitor.                                                                                                                                                                                                                |

| 16  | LX1  | GH1 Gate-Driver Return. LX1 is the input to the current-limit and zero-crossing comparators. The device senses the voltage across the low-side MOSFET NL1 to detect primary current zero crossing and primary overcurrent.                                                                                                                                                                                                                                                                                                                                                                        |

| 17  | GH1  | High-Side MOSFET NH1 Gate Driver Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

## \_\_Pin Description (continued)

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                   |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | BST1     | GH1 Gate-Driver Supply Input. Connect a 0.1µF capacitor from LX1 to BST1.                                                                                                                                                  |

| 19  | PGND1    | Power Ground. PGND1 is the return for the GL1 gate driver.                                                                                                                                                                 |

| 20  | GL1      | Low-Side MOSFET NL1 Gate Driver Output                                                                                                                                                                                     |

| 21  | $V_{DD}$ | Low-Side Gate-Driver Supply Input. Connect V <sub>DD</sub> to the output of the internal linear regulator (V <sub>CC</sub> ).                                                                                              |

| 22  | GL2      | Low-Side MOSFET NL2 Gate-Driver Output                                                                                                                                                                                     |

| 23  | PGND2    | Power Ground. PGND2 is the return for the GL2 gate driver.                                                                                                                                                                 |

| 24  | BST2     | GH2 Gate-Driver Supply Input. Connect a 0.1µF capacitor from LX2 to BST2.                                                                                                                                                  |

| 25  | GH2      | High-Side MOSFET NH2 Gate-Driver Output                                                                                                                                                                                    |

| 26  | LX2      | GH2 Gate-Driver Return. LX2 is the input to the current-limit and zero-crossing comparators. The device senses the voltage across the low-side MOSFET NL2 to detect primary current zero crossing and primary overcurrent. |

| 27  | GND      | Analog Ground. The ground return for $V_{CC}$ , REF, and other analog circuitry. Connect GND to PGND under the IC at the IC's backside exposed metal pad.                                                                  |

| 28  | Vcc      | 5.35V/10mA Internal Linear-Regulator Output. V <sub>CC</sub> is the supply voltage for the device. Bypass V <sub>CC</sub> with a $0.47$ µF ceramic capacitor to GND.                                                       |

| _   | EP       | Exposed Backside Pad. Connect PAD to GND.                                                                                                                                                                                  |

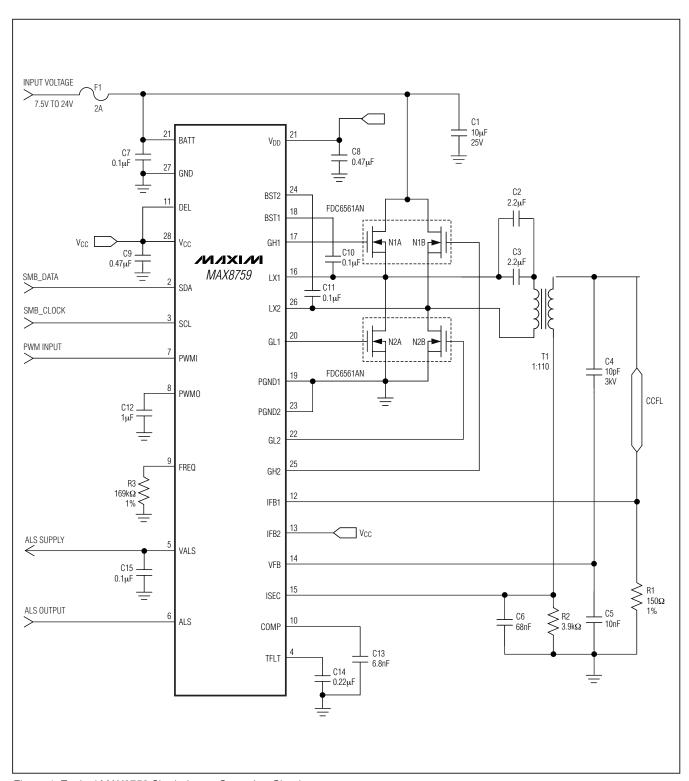

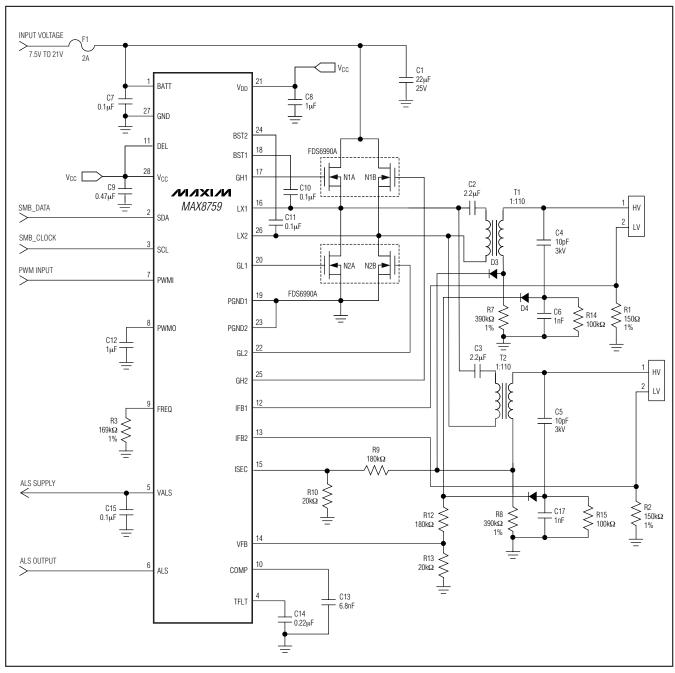

Figure 1. Typical MAX8759 Single-Lamp Operating Circuit

### Typical Operating Circuit

The MAX8759 typical operating circuit (Figure 1) is a single-lamp CCFL backlight inverter for notebook computer TFT LCD panels. The input voltage range of the circuit is from 7.5V to 24V. The maximum RMS lamp current is set to 6mA and the maximum RMS striking voltage is set to 1800V. Table 1 lists some important components and Table 2 lists the component suppliers' contact information.

### Detailed Description

The MAX8759 controls a full-bridge resonant inverter to convert an unregulated DC input into a high-frequency AC output for powering CCFLs. The resonant operation maximizes striking capability and provides near-sinu-

Table 1. List of Important Components

| DESIGNATION  | DESCRIPTION                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------|

| C1           | 10µF ±20%, 25V X5R ceramic capacitor (1210) Murata GRM32DR61E106M TDK C3225X5R1E106M            |

| C2, C3       | 2.2µF ±10%, 25V X5R ceramic capacitors<br>(0805)<br>Murata GRM21BR61E225K<br>TDK C2012X5R1E225K |

| C4           | 10pF ±10%, 3kV HV ceramic capacitor<br>(1808)<br>Kemet C1808C100KHGAC<br>TDK C4520C0G3F100F     |

| NH1/2, NL1/2 | Dual n-channel MOSFETs, 30V, 0.095Ω,<br>6-pin SOT23<br>Fairchild FDC6561AN                      |

| T1           | CCFL transformer, 1:110 turns ratio TMP UI9.8L type                                             |

### **Table 2. Component Suppliers**

| SUPPLIER                   | WEBSITE                |

|----------------------------|------------------------|

| Fairchild<br>Semiconductor | www.fairchildsemi.com  |

| Kemet                      | www.kemet.com          |

| Murata                     | www.murata.com         |

| TDK                        | www.components.tdk.com |

| TMP                        | www.tmp.com            |

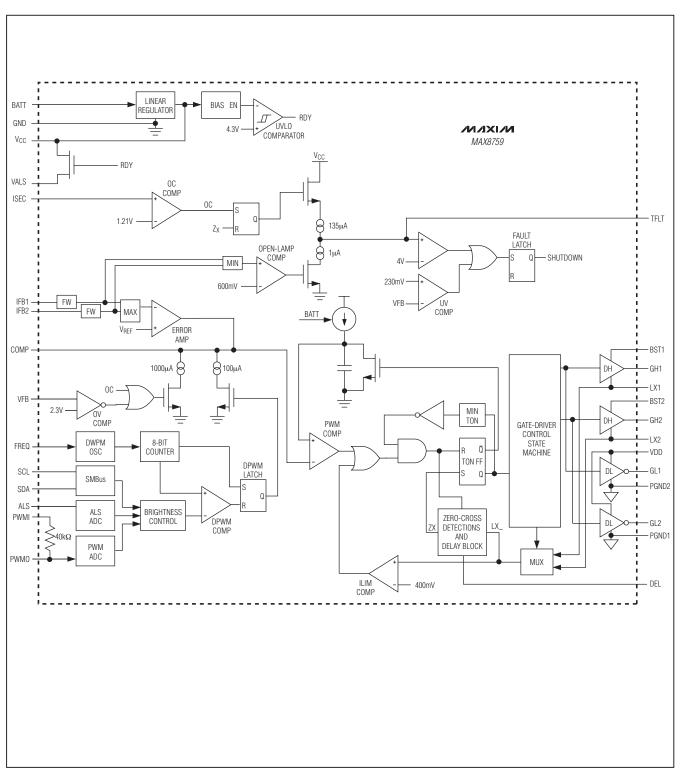

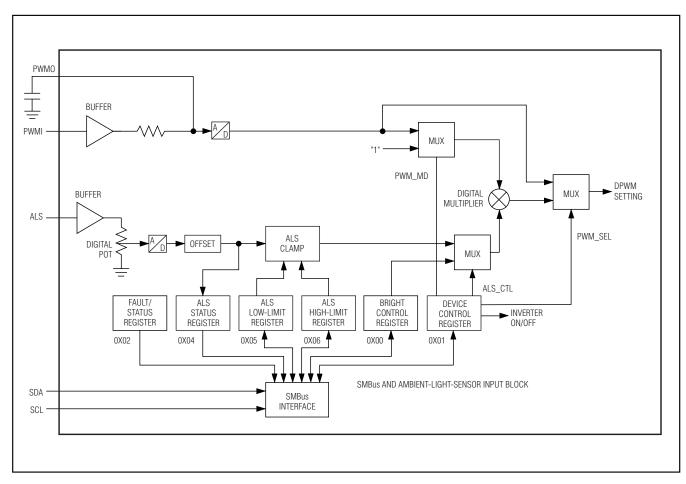

soidal waveforms over the entire input range to improve CCFL lifetime. The lamp brightness is adjusted by turning the lamp on and off with a DPWM signal. The DPWM frequency can be accurately adjusted with a resistor. The brightness of the lamp is proportional to the duty cycle of the DPWM signal, which is controlled either with a 2-wire SMBus-compatible interface, with an external ALS, or with an external PWM signal. The device also includes safety features that effectively protect against single-point fault conditions such as lampout and secondary short-circuit faults. An internal 5.35V linear regulator powers the MOSFET drivers and most of the internal circuitry. Figure 2 is the functional diagram of the MAX8759 and Figure 3 is the detailed diagram of the SMBus and ALS input block.

#### **Resonant Operation**

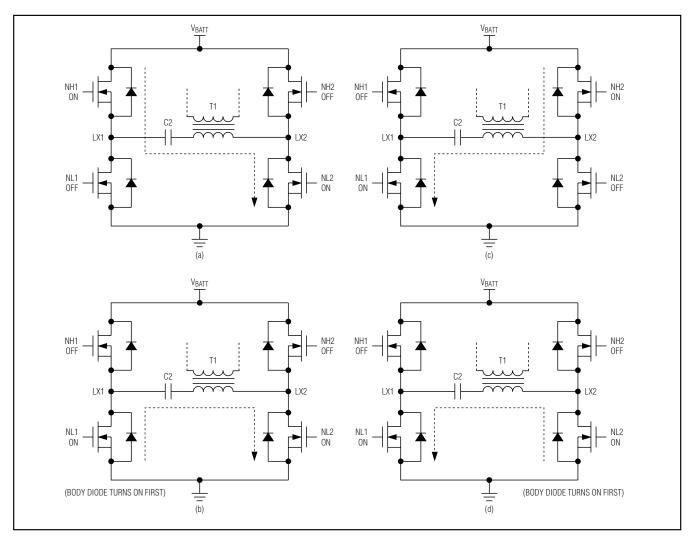

The MAX8759 drives four n-channel power MOSFETs that make up the zero-voltage-switching (ZVS) fullbridge inverter as shown in Figure 4. Assume that NH1 and NL2 are on at the beginning of a switching cycle as shown in Figure 4(a). The primary current flows through MOSFET NH1, DC blocking capacitor C2, the primary side of transformer T1, and MOSFET NL2. During this interval, the primary current ramps up until the controller turns off NH1. When NH1 is turned off, the primary current forward biases the body diode of NL1. which clamps the LX1 voltage just below ground as shown in Figure 4(b). When the controller turns on NL1, its drain-to-source voltage is near zero because its forward-biased body diode clamps the drain. Since NL2 is still on, the primary current flows through NL1, C2, the primary side of T1, and NL2. Once the primary current drops to the minimum current threshold (6mV/R<sub>DS(ON)</sub>), the controller turns off NL2. The remaining energy in T1 charges up the LX2 node until the body diode of NH2 is forward biased. When NH2 turns on, it does so with near-zero drain-to-source voltage. The primary current reverses polarity as shown in Figure 4(c), beginning a new cycle with the current flowing in the opposite direction, with NH2 and NL1 on. The primary current ramps up until the controller turns off NH2. When NH2 is turned off, the primary current forward biases the body diode of NL2, which clamps the LX2 voltage just below ground as shown in Figure 4(d). After the LX2 node goes low, the controller losslessly turns on NL2. Once the primary current drops to the minimum current threshold, the controller turns off NL1. The remaining energy charges up the LX1 node until the body diode of NH1 is forward biased. Finally, NH1 losslessly turns on, beginning a new cycle as shown in Figure 4(a). Note that switching transitions on all four power MOSFETs occur under ZVS conditions, which reduces transient power losses and EMI.

Figure 2. MAX8759 Functional Diagram

14 \_\_\_\_\_\_\_**/\/\/\**

Figure 3. MAX8759 SMBus and Ambient-Light-Sensor Input Block

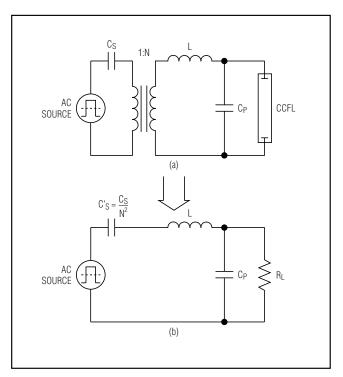

A simplified CCFL inverter circuit is shown in Figure 5 (a). The full-bridge power stage is simplified and represented as a square-wave AC source. The resonant tank circuit can be further simplified to Figure 5(b) by removing the transformer. Cs is the primary series capacitor, Cs' is the series capacitance reflected to the secondary, Cp is the secondary parallel capacitor, N is the transformer turns ratio, L is the transformer secondary leakage inductance, and  $R_L$  is an idealized resistance that models the CCFL in normal operation.

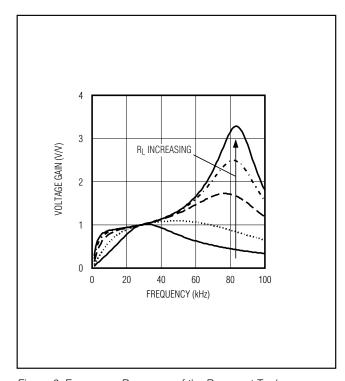

Figure 6 shows the frequency response of the resonant tank's voltage gain under different load conditions. The primary series capacitor is  $1\mu F$ , the secondary parallel capacitor is 15pF, the transformer turns ratio is 1:93, and the secondary leakage inductance is 260mH. Notice that there are two peaks, fs, and fp, in the frequency response. The first peak fs is the series resonant peak determined by the secondary leakage inductance (L) and the series capacitor reflected to the secondary (C's):

$$f_{S} = \frac{1}{2\pi\sqrt{LC_{S}'}}$$

Figure 4. Resonant Operation

The second peak fp is the parallel resonant peak determined by the secondary leakage inductance (L), the parallel capacitor (Cp), and the series capacitor reflected to the secondary (C's):

$$f_{P} = \frac{1}{2\pi \sqrt{L \frac{C'_{S}C_{P}}{C'_{S} + C_{P}}}}$$

The inverter is designed to operate between these two resonant peaks. When the lamp is off, the operating point of the resonant tank is close to the parallel resonant peak due to the lamp's infinite impedance. The circuit displays the characteristics of a parallel-loaded

resonant converter. While in parallel-loaded resonant operation, the inverter behaves like a voltage source to generate the necessary striking voltage. Theoretically, the output voltage of the resonant converter increases until the lamp is ionized or until it reaches the IC's secondary voltage limit. Once the lamp is ionized, the equivalent load resistance decreases rapidly and the operating point moves toward the series resonant peak. While in series resonant operation, the inverter behaves like a current source.

#### **Lamp-Current Regulation**

The MAX8759 uses a lamp-current control loop to regulate the current delivered to the CCFL. The heart of the control loop is a transconductance error amplifier. The

Figure 5. Equivalent Resonant Tank Circuit

AC lamp current is sensed with a resistor connected in series with the low-voltage terminal of the lamp. The MAX8759 has two lamp-current feedback inputs (IFB1 and IFB2) to support dual-lamp application. The voltages across the sense resistors are fed to the IFB1 and IFB2 inputs and are internally full-wave rectified. The transconductance error amplifier selects the higher one of the two feedback signals and compares the rectified voltage with an internal threshold to generate an error current. The error current charges and discharges a capacitor connected between COMP and ground to create an error voltage (VCOMP). VCOMP is then compared with an internal ramp signal to set the high-side MOSFET switch on-time (ton).

### **Feed-Forward Control**

The MAX8759 is designed to maintain tight control of the lamp current under all transient conditions. The feed-forward control instantaneously adjusts the ontime for changes in input voltage (VBATT). This feature provides immunity to input-voltage variations and simplifies loop compensation over wide input-voltage ranges. The feed-forward control also improves the line regulation for short DPWM on-times and makes startup transients less dependent on the input voltage.

Figure 6. Frequency Response of the Resonant Tank

Feed-forward control is implemented by increasing the internal voltage ramp rate for higher VBATT. This has the effect of varying ton as a function of the input voltage while maintaining approximately the same signal levels at VCOMP. Since the required voltage change across the compensation capacitor is minimal, the controller's response to input voltage changes is essentially instantaneous.

#### **Lamp Startup**

A CCFL is a gas-discharge lamp that is normally driven in the avalanche mode. To start ionization in a nonionized lamp, the applied voltage (striking voltage) must be increased to the level required for the start of avalanche. At low temperatures, the striking voltage can be several times the typical operating voltage.

Because of the MAX8759's resonant topology, the striking voltage is guaranteed. Before the lamp is ionized, the lamp impedance is infinite. The transformer secondary leakage inductance and the high-voltage parallel capacitor determine the unloaded resonant frequency. Since the unloaded resonant circuit has a high Q, it can generate very high voltage across the lamp.

#### **Dimming Control**

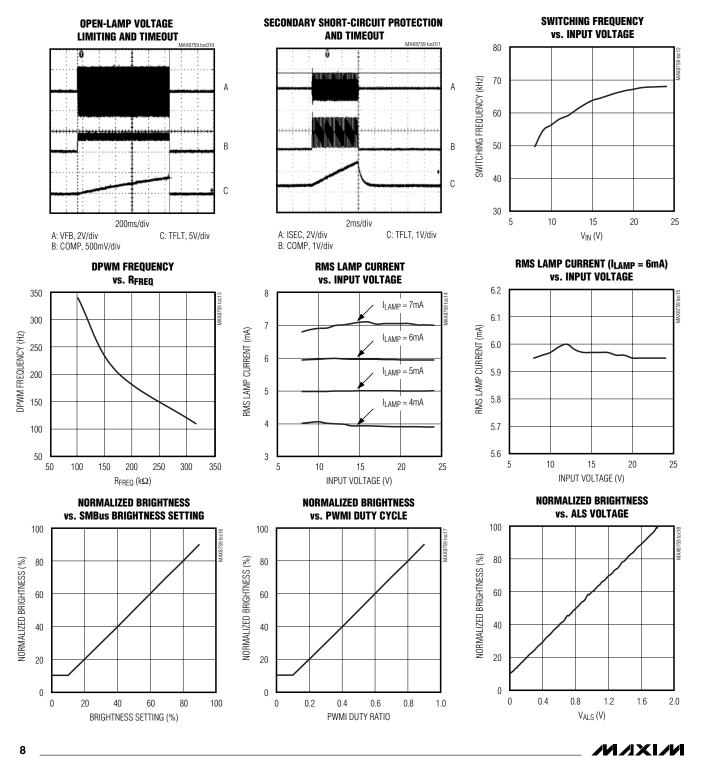

The MAX8759 controls the brightness of the CCFL by "chopping" the lamp current on and off using a low-frequency (between 100Hz and 350Hz) DPWM signal. The frequency of the internal DPWM oscillator is adjustable through a resistor connected between the FREQ pin and GND. The CCFL brightness is proportional to the DPWM duty cycle, which can be adjusted from 10.15% to 100%.

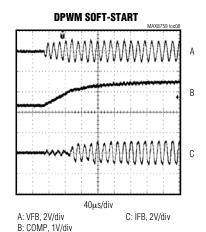

In DPWM operation, the COMP voltage controls the dynamics of the lamp-current envelope. At the beginning of the DPWM ON cycle, the average value of the lamp-current feedback signal is below the regulation point, so the transconductance error amplifier sources current into the COMP capacitor. The switch on-time (ton) gradually increases as VCOMP rises, which provides soft-start. At the end of the DPWM ON cycle, the MAX8759 turns on a 110µA internal current source. The current source linearly discharges the COMP capacitor, gradually decreasing ton, and providing soft-stop.

The DPWM frequency can be set with an external resistor. Connect a resistor between FREQ and GND. The DPWM frequency is given by the following equation:

$f_{DPWM} = 210Hz \times 169k\Omega/R_{FREQ}$

The adjustable range of the DPWM frequency is between 100Hz and 350Hz (RFREQ is between  $100k\Omega$  and  $350k\Omega$ ).

The MAX8759 has three ways for brightness control. The brightness can be controlled by a 2-wire serial interface (SMBus), by an external PWM signal, or by an external ambient-light sensor signal. There are five operating modes, which can be selected by setting bits 1 to 3 in device control register 0x01 (see the SMBus Register Definitions section for details).

#### ALS Mode

The MAX8759 can work with several types of ambient-light sensors. The ideal ambient-light sensors should have a linear response to ambient light and should have a spectral response equivalent to that of the human eye. Ambient-light sensors must provide filtering of low-frequency harmonics found in the electrical spectrum of the many light sources. The ALS's output should be a DC analog voltage that is linearly proportional to the ambient luminance.

In ALS mode, the MAX8759 sets the brightness based on the analog voltage on the ALS pin. The ALS pin is connected to the output of an external ambient-light sensor. The usable input-voltage range of the ALS pin

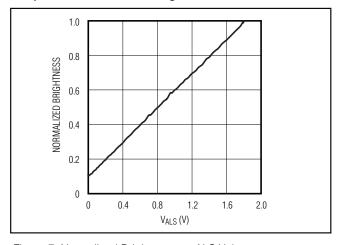

is 0 to 1.8V. The MAX8759 compares the ALS input voltage against user-programmable low and high limits. When the ALS input voltage is below the low limit, the brightness is clamped to the ALS low limit. When the ALS input voltage is above the high limit, the brightness is clamped to the ALS high limit. If the minimum ALS setting is below 10%, the brightness is clamped to 10%. Figure 7 shows the brightness change as a function of the ALS voltage.

The ALS input voltage is sampled every DPWM period and is loaded in ALS status register 0x04. The analog voltage on the ALS pin is converted into an 8-bit digital code. The total number of brightness levels is 256. One step change results in a 0.391% change in the DPWM duty cycle.

#### **PWM Mode**

In PWM mode, the MAX8759 sets the brightness based on the duty cycle of the PWMI signal. The absolute minimum brightness is 10%. If the PWMI duty cycle is less than 10%, the brightness stays at 10%. The frequency range of the PWMI signal is between 5kHz and 50kHz when the PWMO capacitor is  $1\mu F.$

#### SMBus Mode

In SMBus mode, the MAX8759 sets the brightness based on the brightness control register (0x00). The brightness control register contains 8 bits and supports 256 brightness levels. A setting of 0xFF for register 0x00 sets the inverter to the maximum brightness. A setting of 0x00 for register 0x00 sets the inverter to the minimum brightness (10%).

#### ALS with DPST Mode

In ALS with DPST mode, the MAX8759 sets the brightness based on the analog voltage on the ALS pin and duty cycle at the PWMI pin. The MAX8759 lowers the ALS brightness setting by an additional amount that is proportional to the duty cycle of the PWMI signal. For example, if the ALS brightness setting is 80% and the duty cycle of PWMI signal is 60%, the resulting brightness setting is  $80\% \times 60\% = 48\%$ .

#### SMBus with DPST Mode

In SMBus with DPST mode, the MAX8759 sets the brightness based on the brightness control register (0x00). The MAX8759 lowers the SMBus brightness setting by an additional amount that is proportional to the duty cycle of the PWMI signal. For example, if the brightness control register is set to 0x80 (corresponding to 50% brightness setting) and the duty cycle of the PWMI signal is 60%, the resulting brightness setting is  $50\% \times 60\% = 30\%$ .

# **Fault Protections** *Lamp-Out Protection*

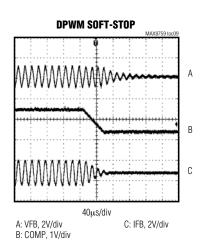

For safety, the MAX8759 monitors the lamp-current feedback inputs (IFB1 and IFB2) to detect faulty or open CCFL tubes. As described in the *Lamp-Current Regulation* section, the voltage on IFB1 and IFB2 is internally full-wave rectified. If the rectified IFB1 or IFB2 voltage is below 600mV, the MAX8759 charges the TFLT capacitor with 1µA. The MAX8759 sets the fault latch and the device is shut down when the voltage on TFLT exceeds 4V. Unlike the normal shutdown mode, the linear regulator output (V<sub>CC</sub>) remains at 5.35V. Clearing bit 0 of the device control register (0x01) or cycling the input power clears the fault latch.

During the fault-delay period, the current control loop tries to maintain the lamp-current regulation by increasing the high-side MOSFET on-time. Because the lamp impedance is very high when it is open, the transformer secondary voltage rises as a result of the high Q-factor of the resonant tank. Once the secondary voltage exceeds the overvoltage threshold, the MAX8759 turns on a 1000µA current source that discharges the COMP capacitor. The on-time of the high-side MOSFET is reduced, lowering the secondary voltage as the COMP voltage decreases. Therefore, the peak voltage of the transformer secondary winding never exceeds the limit during the lamp-out delay period.

#### **Primary Overcurrent Protection**

The MAX8759 senses primary current in each switching cycle. When the regulator turns on the low-side MOSFET, a comparator monitors the voltage drop from LX\_ to PGND\_. If the voltage exceeds the current-limit threshold (430mV, typ), the regulator immediately turns off the high-side switch to prevent the transformer primary current from increasing further.

Figure 7. Normalized Brightness vs. ALS Voltage

#### Secondary Voltage Limiting (VFB)

The MAX8759 reduces the voltage stress on the transformer's secondary winding by limiting the secondary voltage during startup and open-lamp faults. The AC voltage across the transformer secondary winding is sensed through a capacitive voltage-divider formed by C4 and C5 in Figure 1. The voltage across C5 is fed to the VFB input. An overvoltage comparator compares the VFB peak voltage with a 2.3V (typ) internal threshold. Once the VFB peak voltage exceeds the overvoltage threshold, the MAX8759 turns on an internal 1000µA current source that discharges the COMP capacitor. The high-side MOSFET's on-time shortens as the COMP voltage decreases, limiting the transformer secondary's peak voltage at the threshold determined by the capacitive voltage-divider.

#### Secondary Undervoltage Protection (VFB)

The MAX8759 senses the VFB voltage for undervoltage condition. During the DPWM ON period, if the VFB voltage is below the undervoltage threshold (230mV, typ) continuously for an internal delay period (250 $\mu$ s typ, for RFREQ = 169k $\Omega$ ), the MAX8759 shuts down.

#### Secondary Current Limit (ISEC)

The secondary current limit provides fail-safe current limiting in case of a short circuit or leakage from the lamp high-voltage terminal to ground that prevents the current control loop from functioning properly. ISEC monitors the voltage across a sense network placed between the transformer's low-voltage secondary terminal and ground. The ISEC voltage is continuously compared to the ISEC regulation threshold (1.21V, typ). Any time the ISEC voltage exceeds the threshold, the MAX8759 turns on a 1000µA current source that discharges the COMP capacitor, reducing the on-time of the high-side switches. At the same time, the MAX8759 charges the TFLT capacitor with a 135µA current. The MAX8759 sets the fault latch and shuts down when the voltage on TFLT exceeds 4V. Clearing bit 0 of the device control register (0x01) or cycling the input power clears the fault latch.

### **Linear Regulator Output (Vcc)**

The internal linear regulator steps down the DC input voltage at BATT pin to 5.35V (typ). The linear regulator supplies power to the internal control circuitry of the MAX8759 and is also used to power the MOSFET drivers by connecting VCC to VDD. The VCC voltage drops to 4.5V in shutdown.

#### **POR and UVLO**

The MAX8759 includes power-on reset (POR) and undervoltage lockout (UVLO) features. POR resets the fault latch and sets all the SMBus registers to their POR

#### WRITE-BYTE FORMAT

| S | ADDRESS | WR | ACK | COMMAND | ACK | DATA   | ACK | Р |

|---|---------|----|-----|---------|-----|--------|-----|---|

| _ | 7 BITS  | 1b | 1b  | 8 BITS  | 1b  | 8 BITS | 1b  | _ |

SLAVE ADDRESS

COMMAND BYTE: SELECTS WHICH REGISTER YOU ARE WRITING TO

DATA BYTE: DATA GOES INTO THE REGISTER SET BY THE COMMAND BYTE

#### READ-BYTE FORMAT

| s | ADDRESS | WR | ACK | COMMAND | ACK | s | ADDRESS | RD | ACK | DATA   | /// | Р |

|---|---------|----|-----|---------|-----|---|---------|----|-----|--------|-----|---|

| _ | 7 BITS  | 1b | 1b  | 8 BITS  | 1b  |   | 7 BITS  | 1b | 1b  | 8 BITS | 1b  | _ |

SLAVE ADDRESS

COMMAND BYTE: SELECTS WHICH REGISTER YOU ARE READING FROM

DUE TO CHANGE IN DATA-FLOW DIRECTION

SLAVE ADDRESS: REPEATED DATA BYTE: READS FROM THE REGISTER SET BY THE COMMAND

#### **SEND-BYTE FORMAT**

#### RECEIVE-BYTE FORMAT

| S | ADDRESS | WR | ACK | COMMAND | ACK | Р | S | ADDRESS | RD | ACK | DATA   | /// | P |

|---|---------|----|-----|---------|-----|---|---|---------|----|-----|--------|-----|---|

| _ | 7 BITS  | 1b | 1b  | 8 BITS  | 1b  | _ | _ | 7 BITS  | 1b | 1b  | 8 BITS | 1b  | _ |

COMMAND BYTE: SENDS COM-MAND WITH NO DATA: USUALLY USED FOR ONE-SHOT COMMAND SLAVE ADDRESS

DATA BYTE: READS DATA FROM THE REGISTER COMMANDED BY THE LAST READ-BYTE OR WRITE-BYTE TRANSMISSION; ALSO USED FOR SMBus ALERT RESPONSE RETURN **ADDRESS**

S = START CONDITION P = STOP CONDITION

SHADED = SLAVE TRANSMISSION ACK = ACKNOWLEDGED = 0

WR = WRITE = 0RD = READ = 1

/// = NOT ACKNOWLEDGED = 1

Figure 8. SMBus Protocols

values. POR occurs when V<sub>CC</sub> rises above 1.75V (typ). The UVLO occurs when VCC is below 4.2V (typ). The MAX8759 disables both high-side and low-side switch drivers below the UVLO threshold.

#### Low-Power Shutdown

The MAX8759 is placed into shutdown by clearing bit 0 of the device control register (0x01). When the MAX8759 is shut down, all functions of the IC are turned off except the 5.35V linear regulator. In shutdown, the linear regulator output voltage drops to 4.5V and the supply current is 6µA (typ). While in shutdown, the fault latch is reset. The device can be reenabled by setting bit 0 of the device control register to 1.

#### Ambient-Light-Sensor Supply Pin (VALS)

The MAX8759 provides the supply voltage of the ALS through the VALS pin. VALS is internally connected to the 5.35V linear regulator output through a p-channel MOSFET. The p-channel MOSFET is turned on when the MAX8759 is enabled and turned off when the part is disabled. Bypass VALS to ground with a minimum 0.1µF ceramic capacitor. Place the capacitor as close to the ALS supply input as possible.

#### SMBus Interface (SDA, SCL)

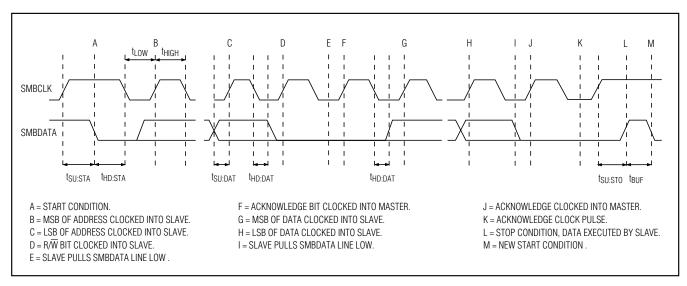

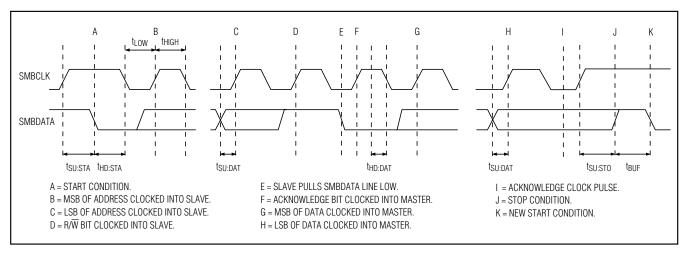

The MAX8759 supports an SMBus-compatible 2-wire digital interface. SDA is the bidirectional data line and SCL is the clock line of the 2-wire interface corresponding respectively to SMBDATA and SMBCLK lines of the SMBus. SDA and SCL have Schmidt-triggered inputs that can accommodate slow edges; however, the rising and falling edges should still be faster than 1µs and 300ns, respectively. The MAX8759 uses the write-byte and read-byte protocols (Figure 8). The SMBus protocols are documented in System Management Bus Specification V1.08 and are available at http://www.sbs-forum.org/.

The MAX8759 is a slave-only device and responds to the 7-bit address 0b0101100. The read and write commands can be distinguished by adding ONE more bit (R/W bit) to the end of the 7-bit slave address, with one indicating read and zero indicating write. The MAX8759 has seven registers: a brightness control register (0x00), a device control register (0x01), a fault/status register (0x02), an identification register (0x03), an ALS status register (0x04), an ALS low-limit register (0x05),

MIXIM

Figure 9. SMBus Write Timing

and an ALS high-limit register (0x06). The MAX8759 only acknowledges these seven registers.

Communication starts with the master signaling the beginning of a transmission with a START condition, which is a high-to-low transition on SDA while SCL is high. When the master has finished communicating with the slave, the master issues a STOP condition, which is a low-to-high transition on SDA while SCL is high. The bus is then free for another transmission. Figures 9 and 10 show the timing diagrams for signals on the 2-wire interface. The address byte, command byte, and data byte are transmitted between the START and STOP conditions. The SDA state is allowed to change only while SCL is low, except for the START and STOP conditions. Data is transmitted in 8-bit words and is sampled on the rising edge of SCL. Nine clock cycles are required to transfer each byte in or out of the MAX8759 since either the master or the slave acknowledges the receipt of the correct byte during the ninth clock. If the MAX8759 receives its correct slave

address followed by  $R/\overline{W}=0$ , it expects to receive 1 or 2 bytes of information (depending on the protocol). If the device detects a START or STOP condition prior to clocking in the bytes of data, it considers this an error condition and disregards all the data. If the transmission is completed correctly, the registers are updated immediately after a STOP (or RESTART) condition. If the MAX8759 receives its correct slave address followed by  $R/\overline{W}=1$ , it expects to clock out the register data selected by the previous command byte.

#### **SMBus Register Definitions**

All MAX8759 registers are byte wide and accessible through the read/write byte protocols mentioned in the previous section. Their bit assignments are provided in the following sections with reserved bits containing a default value of zero.

Table 3 summarizes the register assignments, as well as each register's POR state. During shutdown, the serial interface remains fully functional.

Figure 10. SMBus Read Timing

### **Table 3. Commands Description**

| OMP               |                 | 200          |                |          | DAT      | A-REGISTE | R BIT ASSIG | NMENT   |          |                |

|-------------------|-----------------|--------------|----------------|----------|----------|-----------|-------------|---------|----------|----------------|

| SMBus<br>PROTOCOL | COMMAND<br>BYTE | POR<br>STATE | BIT 7<br>(MSB) | BIT 6    | BIT 5    | BIT 4     | BIT 3       | BIT 2   | BIT 1    | BIT 0<br>(LSB) |

| Read and<br>Write | 0x00            | 0xFF         | BR7            | BRT6     | BRT5     | BR4       | BRT3        | BRT2    | BRT1     | BRT0           |

| Read and<br>Write | 0x01            | 0x00         | Reserved       | Reserved | ALSDEL1  | ALSDEL0   | ALS_CTL     | PWM_MD  | PWM_SEL  | LAMP_CTL       |

| Read Only         | 0x02            | N/A          | Reserved       | Reserved | Reserved | Reserved  | LAMP_STAT   | OV_CURR | Reserved | FAULT          |

| Read Only         | 0x03            | 0x01         | MFG4           | MFG3     | MFG2     | MFG1      | MFG0        | REV2    | REV1     | REV0           |

| Read Only         | 0x04            | 0x00         | ALS7           | ALS6     | ALS5     | ALS4      | ALS3        | ALS2    | ALS1     | ALS0           |

| Read and<br>Write | 0x05            | 0x00         | ALSLL7         | ALSLL6   | ALSLL5   | ALSLL4    | ALSLL3      | ALSLL2  | ALSLL1   | ALSLL0         |

| Read and<br>Write | 0x06            | 0xFF         | ALSHL7         | ALSHL6   | ALSHL5   | ALSHL4    | ALSHL3      | ALSHL2  | ALSHL1   | ALSHL0         |

#### Brightness Control Register [0x00] (POR = 0xFF)

The brightness control register of the MAX8759 contains 8 bits and supports 256 brightness levels. A write-byte cycle to register 0x00 sets the brightness level if the inverter is in SMBus mode. A write-byte cycle to register 0x00 has no effect if the inverter is not in

SMBus mode. A read-byte cycle to register 0x00 returns the current brightness level regardless of the operation mode. A setting of 0xFF for register 0x00 sets the inverter to the maximum brightness. A setting of 0x00 for register 0x00 sets the inverter to the minimum brightness.

| BIT 7 (R/W) | BIT 6 (R/W) | BIT 5 (R/W) | BIT 4 (R/W) | BIT 3 (R/W) | BIT 2 (R/W) | BIT 1 (R/W) | BIT 0 (R/W) |

|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| BRT7        | BRT6        | BRT5        | BRT4        | BRT3        | BRT2        | BRT1        | BRT0        |

BRT[7..0]: 256 brightness levels.

### Device Control Register [0x01] (POR = 0x00)

This register has a single bit that controls the inverter ON/OFF state, 3 bits that control the operating mode of

the inverter, and 2 bits for setting ALS delay time. The remaining bits are reserved for future use.

| BIT 7    | BIT 6    | BIT 5 (R/W) | BIT 4 (R/W) | BIT 3 (R/W) | BIT 2 (R/W) | BIT 1 (R/W) | BIT 0 (R/W) |