##

## WLED Charge Pump, RGB, OLED Boost, LDOs with ALC and CAI

## **General Description**

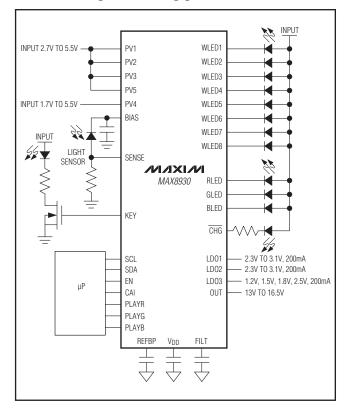

The MAX8930 integrates a charge pump for white LED display backlighting with ambient light control (ALC) feature. The high-efficiency, adaptive-mode 1x/-0.5x charge pump drives up to 11 LEDs (8 WLEDs + RGB LED) with constant current for uniform brightness. The LED current is adjustable from 0.1mA to 25.6mA in 256 linear steps through I<sup>2</sup>C. High accuracy and LED-to-LED current matching are maintained throughout the adjustment range. The MAX8930 includes soft-start, thermal shutdown, open-circuit, and short-circuit protection.

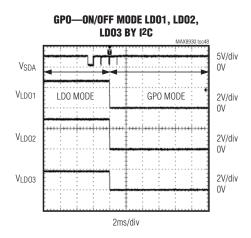

Three 200mA LDOs are provided with programmable output voltages to provide power to external circuitry. These three LDOs can also be configured for a GPO function through the I<sup>2</sup>C. A step-up converter is also available on the MAX8930 for biasing a PMOLED subpanel.

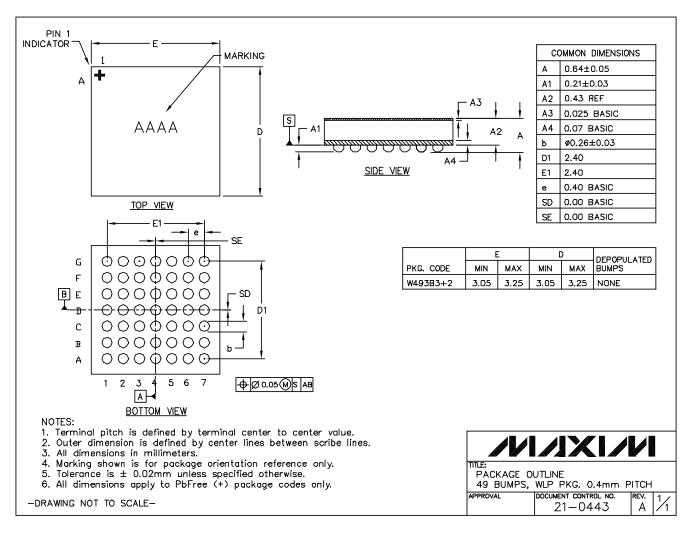

The MAX8930 is available in the 49-bump, 3.17mm x 3.17mm WLP package.

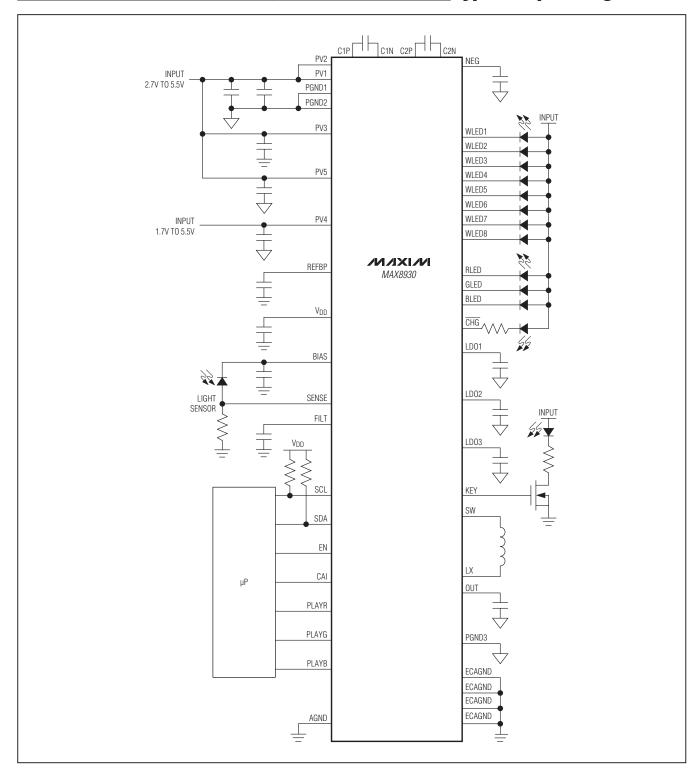

## **Simplified Application Circuit**

## Features

- White LED Charge Pump

- Adaptive 1x or -0.5x Negative Modes

- 11 Low-Dropout LED Current Sinks with 25.6mA to 0.1mA in 256 Dimming Steps

- Ramp-Up/Down Control for Main White LED

- Ramp-Up/Down Control for RGB LED

- Individual Brightness Control for Each White, RGB LED

- Low 240µA (typ) Quiescent Current

- Ambient Light Control (ALC) for Any Type of Light Sensor

- Content Adaptive Interface

- ✤ I<sup>2</sup>C-Compatible Control Interface

- Three Programmable LDOs Up to 200mA

- Step-Up DC-DC Converter with Programmable

Output for PMOLED Application

- Low 0.1µA Shutdown Current

- ♦ 2.7V to 5.5V Supply Voltage Range

- Thermal Shutdown

- Open and Short-Circuit Protection

## Applications

Cell Phones and Smartphones

PDAs, Digital Cameras, Camcorders, and Other Portable Equipment

## **\_Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE           |

|-------------|----------------|-----------------------|

| MAX8930EWJ+ | -40°C to +85°C | 49 WLP<br>0.4mm pitch |

+Denotes a lead(Pb)-free/RoHS-compliant package.

Typical Operating Circuit appears at end of data sheet.

##

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

PV\_, VDD, EN, CAI, PLAY\_, BIAS,

|                             | · ,                          |

|-----------------------------|------------------------------|

| SENSE, REFBP, ECAGND to A   | GND0.3V to +6.0V             |

| PV_, VDD, PGND_, AGND to NE | G0.3V to +6.0V               |

| ECAGND, PGND_ to AGND       | 0.3V to +0.3V                |

| WLED_, RGB_, C1N, C2N,      |                              |

| C1P, C2P to NEG0.3V to      | O(VPV1 + VPV2 + VPV3 + 0.3V) |

| FILT to AGND                | 0.3V to (VPV3 + 0.3V)        |

| SCL, SDA to AGND            | 0.3V to (VDD + 0.3V)         |

| LDO_ to AGND                | 0.3V to (VPV3 + VPV4 + 0.3V) |

| SW to PGND3                 | 0.3V to (VPv5 + 0.3V)        |

|                             |                              |

| LX, OUT to PGND3<br>KEY to AGND            |                |

|--------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70$ | ,              |

| 49-Pin WLP 3.17mm x 3.17mm                 |                |

| (derate 20mW/°C above +70°C)               | 1600mW         |

| Operating Temperature Range                | 40°C to +85°C  |

| Junction Temperature                       | +150°C         |

| Storage Temperature Range                  | 65°C to +150°C |

| Soldering Temperature (reflow)             | +260°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{PV} = V_{EN} = V_{DD} = 3.7V, V_{PGND}$  and  $V_{AGND} = 0V$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                    | COND                                                                               | DITIONS                                                                                                                   | MIN   | ТҮР   | MAX   | UNITS |

|----------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| PV1, PV2, PV3, PV5 Operating<br>Voltage      |                                                                                    |                                                                                                                           | 2.7   |       | 5.5   | V     |

| Undervoltage Lockout Threshold               | VPV1, VPV2, VPV3, VPV5 risin                                                       | VPV1, VPV2, VPV3, VPV5 rising                                                                                             |       | 2.45  | 2.65  | V     |

| UVLO Hysteresis                              |                                                                                    |                                                                                                                           |       | 100   |       | mV    |

| PV4 Operating Voltage                        |                                                                                    |                                                                                                                           | 1.7   |       | 5.5   | V     |

| V <sub>DD</sub> Operating Range              | V <sub>DD</sub> is supply voltage for I <sup>2</sup><br>logic is supplied from PV_ | C input block only; all other                                                                                             | 1.7   |       | 5.5   | V     |

| PV_ Shutdown Supply Current 1                |                                                                                    | $T_A = +25^{\circ}C$                                                                                                      |       | 0.1   | 1     |       |

| (All Outputs Off, I <sup>2</sup> C Disabled) | $EN = AGND, V_{DD} = 0V$                                                           | $T_A = +85^{\circ}C$                                                                                                      |       | 0.1   |       | μΑ    |

| PV_ Shutdown Supply Current 2                |                                                                                    | $T_A = +25^{\circ}C$                                                                                                      |       | 2     | 10    |       |

| (All Outputs Off, I <sup>2</sup> C Enabled)  | $V_{DD} = V_{PV3}$ , EN = AGND                                                     | $T_A = +85^{\circ}C$                                                                                                      |       | 2     |       | μA    |

| VDD Shutdown Threshold                       | VDD falling, hysteresis = 50                                                       | lmV                                                                                                                       | 1.15  | 1.4   | 1.65  | V     |

|                                              | 1x mode, no load, ALC off,                                                         | step-up off, ILDO_ = 0mA                                                                                                  |       | 240   | 400   | μΑ    |

| Supply Current                               |                                                                                    | -0.5x mode, 4MHz switching, each $I_{LED} = 0.1$ mA, ALC off, $I_{LDO} = 0$ mA, step-up $I_0 = 0$ mA at $V_{PV3} = 2.7$ V |       | 6.8   |       | mA    |

| Reference Bypass (REFBP)<br>Output Voltage   | $0\mu A \leq I_{REFBP} \leq 1\mu A$                                                |                                                                                                                           | 1.164 | 1.200 | 1.236 | V     |

| REFBP Supply Rejection                       | $2.5V \leq V_{PV3} \leq 5.5V$                                                      |                                                                                                                           |       | 0.2   | 5     | mV    |

| Thermal Shutdown                             |                                                                                    |                                                                                                                           |       | +160  |       | °C    |

| Thermal Shutdown Hysteresis                  |                                                                                    |                                                                                                                           |       | 20    |       | °C    |

M/IXI/M

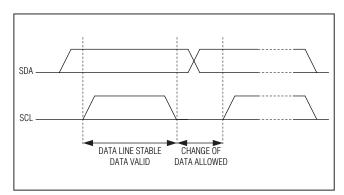

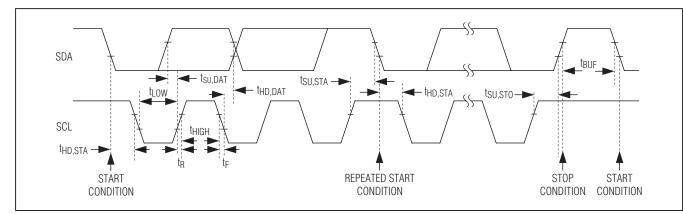

## I<sup>2</sup>C INTERFACE CHARACTERISTICS

| PARAMETER                              | CON                                      | DITIONS              | MIN                      | TYP  | MAX          | UNITS |

|----------------------------------------|------------------------------------------|----------------------|--------------------------|------|--------------|-------|

| SDA, SCL Input High Voltage            | V <sub>DD</sub> = 1.7V to 5.5V           |                      | 0.7 x<br>V <sub>DD</sub> |      |              | V     |

| SDA, SCL Input Low Voltage             | V <sub>DD</sub> = 1.7V to 5.5V           |                      |                          |      | 0.3 x<br>Vdd | V     |

| SDA, SCL Input Current                 | $V_{IL} = 0V \text{ or } V_{IH} = 5.5V,$ | $T_A = +25^{\circ}C$ |                          | 0.01 | 1            | μA    |

|                                        | VDD = 5.5V                               | $T_A = +85^{\circ}C$ |                          | 0.1  |              | μΛ    |

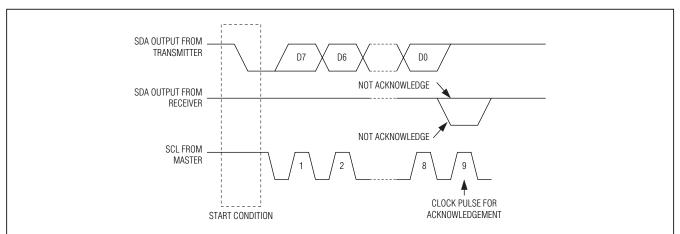

| SDA Output Low Voltage                 | ISDA = 3mA, for acknowled                | dge (Note 3)         |                          | 0.03 | 0.4          | V     |

| Clock Frequency                        | (Note 3)                                 |                      | 100                      |      | 400          | kHz   |

| Bus-Free Time Between START and STOP   | tBUF (Note 3)                            |                      | 1.3                      |      |              | μs    |

| Hold Time Repeated START<br>Condition  | t <sub>HD,STA</sub> (Note 3)             |                      | 0.6                      | 0.1  |              | μs    |

| SCL Low Period                         | tLOW (Note 3)                            |                      | 1.3                      | 0.2  |              | μs    |

| SCL High Period                        | tHIGH (Note 3)                           |                      | 0.6                      | 0.2  |              | μs    |

| Setup Time Repeated START<br>Condition | t <sub>SU,STA</sub> (Note 3)             |                      | 0.6                      | 0.1  |              | μs    |

| SDA Hold Time                          | tHD,DAT (Note 3)                         |                      | 0                        | 0.01 |              | μs    |

| SDA Setup Time                         | tsu,dat (Note 3)                         |                      |                          | 50   |              | ns    |

| Setup Time for STOP Condition          | tsu,sto (Note 3)                         |                      | 0.6                      | 0.1  |              | μs    |

## **CHARGE PUMP CHARACTERISTICS**

| PARAMETER                                   | CONDITIONS                           | MIN | TYP | MAX  | UNITS |

|---------------------------------------------|--------------------------------------|-----|-----|------|-------|

| Switching Frequency                         |                                      |     | 4   |      | MHz   |

| Pump Soft-Start Time                        |                                      |     | 0.5 |      | ms    |

| Charge-Pump Regulation<br>Voltage (and OVP) | VPV1, VPV2 - VNEG                    | 4.3 | 5   |      | V     |

| Open-Loop NEG Output<br>Resistance          | (0.5 x (VPV1 or VPV2) - VNEG)/INEG   |     | 1.3 | 2.49 | Ω     |

| Guaranteed Output Current                   | LED VFMAX = 3.9V, VPV1 = VPV2 = 3.2V | 281 |     |      | mA    |

| NEG Discharge Resistance in Shutdown        | All LEDs off                         |     | 10  |      | kΩ    |

**MAX8930**

## CURRENT SINK DRIVER CHARACTERISTICS

| PARAMETER                                                             |                          | CONDITIO                                                                    | NS                                   | MIN  | TYP            | MAX  | UNITS |

|-----------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------|--------------------------------------|------|----------------|------|-------|

| Current Setting Range                                                 | WLED1-WLED8,             | RGB program                                                                 | mable by I <sup>2</sup> C            | 0.1  |                | 25.6 | mA    |

|                                                                       |                          |                                                                             |                                      |      | 0<br>(default) |      |       |

|                                                                       |                          |                                                                             |                                      |      | 0.016          |      |       |

|                                                                       | Main WLED_ and           | d RGB ramp-up                                                               | /ramp-down in 0.1mA                  |      | 0.064          |      | ms/   |

| WLED_, RGB Ramp-Up/Ramp-<br>Down Time                                 | increments; 8 ste        | eps are prograr                                                             | nmable through I <sup>2</sup> C;     |      | 0.128          |      | 0.1mA |

| Down nine                                                             | ramp-up and ran          | np-down times                                                               | are set separately                   |      | 0.256          |      | 1     |

|                                                                       |                          |                                                                             |                                      |      | 0.512          |      |       |

|                                                                       |                          |                                                                             |                                      |      | 1.024          |      |       |

|                                                                       |                          |                                                                             |                                      |      | 2.048          |      |       |

| WLED_, RGB Current Accuracy                                           | 25.6mA setting,          | 25.6mA setting, $T_A = +25^{\circ}C$<br>0.1mA setting, $T_A = +25^{\circ}C$ |                                      | -2.5 |                | +2.5 | - %   |

| WEED_, HGD Current Accuracy                                           | 0.1mA setting, T,        |                                                                             |                                      | -50  | ±10            | +50  | /0    |

| WLED_, RGB Current Matching                                           | WLED1-WLED8,             | RGB (Note 4)                                                                |                                      |      | 5              | 10   | %     |

| WLED, RGB RDSON                                                       | 1x mode                  |                                                                             |                                      |      | 2.68           |      | Ω     |

| WEED_, HOB HDSON                                                      | -0.5x mode               |                                                                             |                                      |      | 4.12           |      | 52    |

|                                                                       | 25.6mA setting           | 1x mode                                                                     | $T_A = 0^{\circ}C$ to $+85^{\circ}C$ |      | 62             | 120  |       |

| WLED_, RGB Current Regulator<br>Dropout Voltage                       | (Note 5)                 |                                                                             | $T_A = -40^{\circ}C$                 |      | 62             | 150  | mV    |

|                                                                       |                          | -0.5x mode                                                                  |                                      |      | 95             | 200  |       |

| WLED_, RGB Current Regulator<br>Switchover Threshold<br>(1x to -0.5x) | V <sub>LED</sub> falling |                                                                             |                                      | 125  | 150            | 175  | mV    |

| WLED_, RGB Current Regulator<br>Switchover Hysteresis                 |                          |                                                                             |                                      |      | 100            |      | mV    |

| WLED_, RGB Leakage in                                                 | All LEDs off             | $T_A = +25^{\circ}C$                                                        |                                      |      | 0.01           | 5    |       |

| Shutdown                                                              | AII LEDS UII             | $T_A = +85^{\circ}C$                                                        |                                      |      | 0.1            |      | μΑ    |

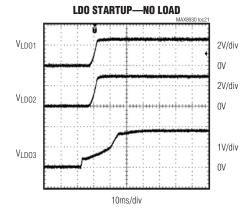

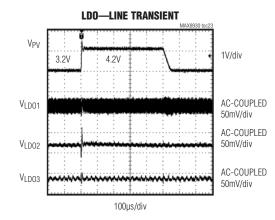

## LDO1 CHARACTERISTICS

| PARAMETER                                  | CONDITIONS                                                     | MIN   | ТҮР | MAX   | UNITS |

|--------------------------------------------|----------------------------------------------------------------|-------|-----|-------|-------|

| Output Voltage V <sub>LDO1</sub> (Default) | 200mA at V <sub>PV3</sub> = 3.6V                               | 2.522 | 2.6 | 2.678 | V     |

|                                            |                                                                | 2.231 | 2.3 | 2.369 |       |

|                                            |                                                                | 2.425 | 2.5 | 2.575 |       |

|                                            |                                                                | 2.522 | 2.6 | 2.678 |       |

| Drogrommoble Output Voltage                |                                                                | 2.619 | 2.7 | 2.781 |       |

| Programmable Output Voltage                | I <sub>LDO1</sub> = 50mA                                       | 2.716 | 2.8 | 2.884 |       |

|                                            |                                                                | 2.813 | 2.9 | 2.987 |       |

|                                            |                                                                | 2.910 | 3.0 | 3.090 |       |

|                                            |                                                                | 3.007 | 3.1 | 3.193 |       |

| Output Current                             |                                                                | 200   |     |       | mA    |

| Current Limit                              | V <sub>LDO1</sub> = 90% of nominal regulation voltage (Note 3) | 250   | 475 | 750   | mA    |

| Dropout Voltage                            | ILDO1 = 200mA, TA = +25°C                                      |       | 120 | 300   | mV    |

| Line Regulation                            | $3.4V \le V_{PV3} \le 5.5V$ , $I_{LDO1} = 150mA$               |       | 2.4 |       | mV    |

| Load Regulation                            | 1mA < ILDO1 < 200mA                                            |       | 25  |       | mV    |

## LDO1 CHARACTERISTICS (continued)

| PARAMETER                                               | CONDITIONS                                                   | MIN | ТҮР | MAX | UNITS |

|---------------------------------------------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| Power-Supply Rejection $\Delta V_{LDO1}/\Delta V_{PV3}$ | f = 10Hz to 10kHz, $I_{LDO1}$ = 10mA, $C_{LDO1}$ = 1 $\mu$ F |     | 60  |     | dB    |

| Output Noise Voltage (RMS)                              | f = 100Hz to 100kHz, ILDO1 = 10mA, CLDO1 = 1µF               |     | 45  |     | μVrms |

| Minimum Output Capacitor                                | I <sub>LDO1</sub> < 200mA                                    |     | 1   |     | μF    |

| Startup Time from Shutdown                              | ILDO1 = 150mA (Note 3)                                       |     | 40  | 100 | μs    |

| Startup Transient Overshoot                             | I <sub>LDO1</sub> = 150mA (Note 3)                           |     | 3   | 50  | mV    |

| Shutdown Output Impedance                               | LDO1 disabled through I <sup>2</sup> C (default on)          |     | 1   |     | kΩ    |

## LDO2 CHARACTERISTICS

| PARAMETER                              | CONDITIONS                                                     | MIN   | TYP | MAX   | UNITS |

|----------------------------------------|----------------------------------------------------------------|-------|-----|-------|-------|

| Output Voltage VLDO2 (Default)         | 200mA at V <sub>PV3</sub> = 3.6V                               | 2.813 | 2.9 | 2.987 | V     |

|                                        |                                                                | 2.231 | 2.3 | 2.369 |       |

|                                        |                                                                | 2.425 | 2.5 | 2.575 |       |

|                                        |                                                                | 2.522 | 2.6 | 2.678 |       |

| Programmable Output Voltage            | $I_{LDO2} = 50 \text{mA}$                                      | 2.619 | 2.7 | 2.781 | V     |

|                                        |                                                                | 2.716 | 2.8 | 2.884 | v     |

|                                        |                                                                | 2.813 | 2.9 | 2.987 |       |

|                                        |                                                                | 2.910 | 3.0 | 3.090 |       |

|                                        |                                                                | 3.007 | 3.1 | 3.193 |       |

| Output Current                         |                                                                | 200   |     |       | mA    |

| Current Limit                          | VLDO2 = 90% of nominal regulation voltage (Note 4)             | 250   | 475 | 750   | mA    |

| Dropout Voltage                        | $I_{LDO2} = 200 \text{mA}, T_A = +25 ^{\circ}\text{C}$         |       | 120 | 300   | mV    |

| Line Regulation                        | $3.4V \le V_{PV3} \le 5.5V$ , ILDO2 = 150mA                    |       | 2.4 |       | mV    |

| Load Regulation                        | 1mA < I <sub>LDO2</sub> < 200mA                                |       | 25  |       | mV    |

| Power-Supply Rejection<br>ΔVLDO2/ΔVPV3 | f = 10Hz to 10kHz, $I_{LDO2}$ = 10mA, $C_{LDO2}$ = 1 $\mu$ F   |       | 60  |       | dB    |

| Output Noise Voltage (RMS)             | f = 100Hz to 100kHz, $I_{LDO2}$ = 10mA, $C_{LDO2}$ = 1 $\mu$ F |       | 45  |       | μVrms |

| Minimum Output Capacitor               | I <sub>LDO2</sub> < 200mA                                      |       | 1   |       | μF    |

| Startup Time from Shutdown             | I <sub>LDO2</sub> = 150mA (Note 3)                             |       | 40  | 100   | μs    |

| Startup Transient Overshoot            | I <sub>LDO2</sub> = 150mA (Note 3)                             |       | 3   | 50    | mV    |

| Shutdown Output Impedance              | LDO2 disabled through I <sup>2</sup> C (default on)            |       | 1   |       | kΩ    |

**MAX8930**

## LDO3 CHARACTERISTICS

| PARAMETER                              | CONDITIONS                                                     | MIN   | ТҮР  | MAX   | UNITS |

|----------------------------------------|----------------------------------------------------------------|-------|------|-------|-------|

| Input Operating Range                  | VPV4                                                           | 1.7   |      | 5.5   | V     |

| Output Voltage VLDO3                   | 200mA at V <sub>PV4</sub> = 2.4V                               | 1.764 | 1.80 | 1.854 | V     |

|                                        |                                                                | 1.164 | 1.2  | 1.236 |       |

|                                        | $V_{PV4} = 1.8V, I_{LDO3} = 50mA$                              | 1.455 | 1.5  | 1.545 |       |

| Programmable Output Voltage            |                                                                | 1.764 | 1.80 | 1.854 | V     |

|                                        | $V_{PV4} = 3.7V, I_{LDO3} = 50mA$                              | 2.425 | 2.5  | 2.575 |       |

| Output Current                         |                                                                |       |      | 200   | mA    |

| Current Limit                          | V <sub>LDO3</sub> = 90% of nominal regulation voltage (Note 4) | 250   | 475  | 750   | mA    |

| Dropout Voltage                        | I <sub>LDO3</sub> = 200mA, T <sub>A</sub> = +25°C              |       | 120  | 300   | mV    |

| Line Regulation                        | 2.4V ≤ VPV4 ≤ 5.5V, ILDO3 = 150mA                              |       | 2.4  |       | mV    |

| Load Regulation                        | 1mA < I <sub>LDO3</sub> < 200mA                                |       | 25   |       | mV    |

| Power-Supply Rejection<br>ΔVLDO3/ΔVPV4 | f = 10Hz to 10kHz, $I_{LDO3}$ = 10mA, $C_{LDO3}$ = 2.2µF       |       | 60   |       | dB    |

| Output Noise Voltage (RMS)             | f = 100Hz to 100kHz, ILDO3 = 10mA, CLDO3 = 2.2µF               |       | 75   |       | μVRMS |

| Minimum Output Capacitor               | 0μA < I LDO3 < 200mA (Note 3)                                  | 2.2   |      |       | μF    |

| Startup Time from Shutdown             | ILDO3 = 150mA (Note 3)                                         |       | 100  | 250   | μs    |

| Startup Transient Overshoot            | I <sub>LDO3</sub> = 150mA (Note 3)                             |       | 3    | 50    | mV    |

| Shutdown Output Impedance              | LDO3 disabled through I <sup>2</sup> C (default on)            |       | 1    |       | kΩ    |

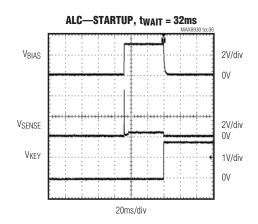

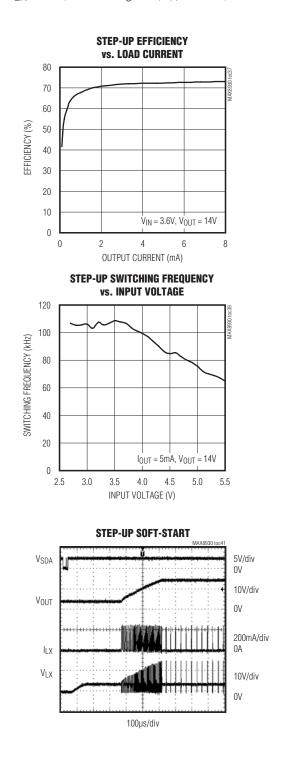

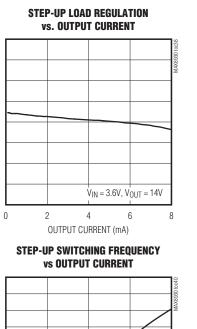

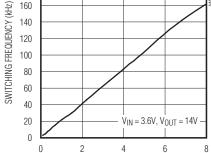

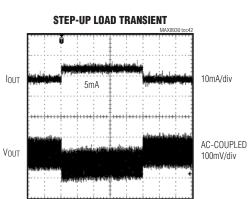

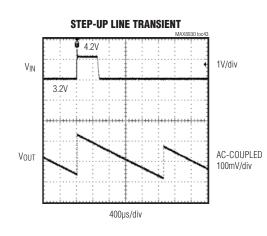

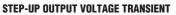

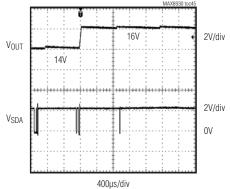

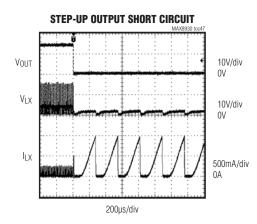

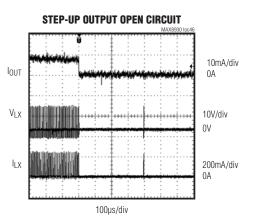

## STEP-UP CONVERTER CHARACTERISTICS

| PARAMETER                      | CON                                   | DITIONS                                        | MIN  | TYP  | MAX  | UNITS |

|--------------------------------|---------------------------------------|------------------------------------------------|------|------|------|-------|

| Input Operating Range          | VPV5                                  |                                                | 2.7  |      | 5.5  | V     |

| Line Regulation                | $V_{OUT} = 14V$ , $I_{OUT} = 5mA$ ,   | V <sub>PV5</sub> = 2.7V to 5.5V                |      | 0.1  |      | %/V   |

| Load Regulation                | Vout = 14V, lout = 0mA                | to 5mA, V <sub>PV5</sub> = 3.7V                |      | 0.1  |      | %/mA  |

| LX Voltage Range               |                                       |                                                |      |      | 20   | V     |

| LX Switch Current Limit        |                                       |                                                | 192  | 241  | 289  | mA    |

|                                | V <sub>LX</sub> = 20V, step-up        | $T_A = +25^{\circ}C$                           |      | 0.01 | 2    |       |

| LX Leakage Current             | converter disabled                    | $T_A = +85^{\circ}C$                           |      | 0.1  |      | - μΑ  |

| Isolation pMOS RDS(ON)         | VPV5 = 2.7V, ISW = 100mA              |                                                |      | 1.5  | 2.4  | Ω     |

| pMOS Rectifier RDS(ON)         | LX to OUT, V <sub>PV5</sub> = 3.7V, I | LX to OUT, $V_{PV5} = 3.7V$ , $I_{LX} = 100mA$ |      | 4.0  |      | Ω     |

| Isolation pMOS Current Limit   | VPV5 = 3.7V, VSW = 0V                 |                                                | 0.15 | 0.3  | 0.6  | A     |

| location pMOC Lockage Comment  | SW = PGND3,                           | $T_A = +25^{\circ}C$                           |      | 0.01 | 1    |       |

| Isolation pMOS Leakage Current | $V_{PV5} = 5.5V$                      | TA = +85°C                                     |      | 0.1  |      | μA    |

| SW Soft-Start Time             | VPv5 = 2.7V                           |                                                |      | 0.2  |      | ms    |

| nMOS RDS(ON)                   | VPV5 = 3.7V, ILX = 100mA              | 1                                              |      | 0.9  | 1.5  | Ω     |

| Maximum LX On-Time             |                                       |                                                | 8    | 11   | 14   | μs    |

| Minimum LX Off-Time            | V <sub>OUT</sub> > 12V                |                                                | 1.6  | 2    | 2.4  | μs    |

| OVP Threshold                  | No feedback, VOUT rising              |                                                | 17.6 | 18.5 | 19.4 | V     |

| OVP Threshold Hysteresis       |                                       |                                                |      | 1    |      | V     |

## STEP-UP CONVERTER CHARACTERISTICS (continued)

| PARAMETER                               | CONDITIONS                          |                                      | MIN  | ТҮР  | МАХ  | UNITS |  |

|-----------------------------------------|-------------------------------------|--------------------------------------|------|------|------|-------|--|

| Current Limit Propagation Delay<br>(LX) |                                     |                                      |      | 55   |      | ns    |  |

|                                         |                                     | $T_A = 0^{\circ}C$ to $+85^{\circ}C$ | -2   |      | +2   | 0/    |  |

| Output Voltage Accuracy                 | $V_{PV5} = 3.7V, I_{OUT} = 0mA$     | $T_A = -40^{\circ}C$                 | -2.5 |      | +2.5 | %     |  |

|                                         |                                     |                                      |      | 13.0 |      |       |  |

|                                         | VPv5 = 3.7V, I <sub>OUT</sub> = 0mA |                                      |      | 13.5 |      |       |  |

|                                         |                                     |                                      |      | 14.0 |      |       |  |

| Programmable Output Voltage             |                                     |                                      |      | 14.5 |      | V     |  |

|                                         |                                     |                                      |      | 15.0 |      | V     |  |

|                                         |                                     |                                      | 15.5 |      |      |       |  |

|                                         |                                     |                                      |      | 16.0 |      |       |  |

|                                         |                                     |                                      |      | 16.5 |      |       |  |

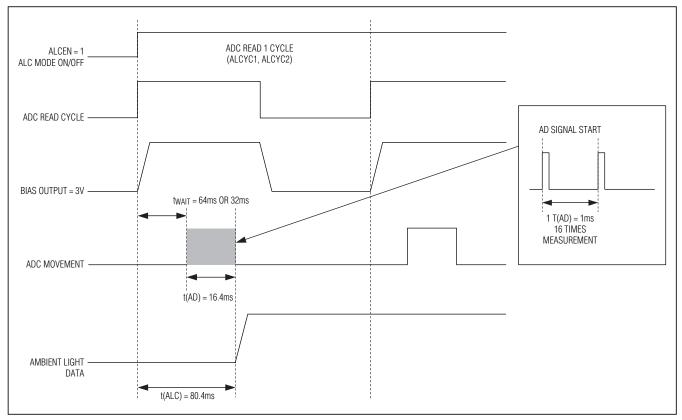

## AMBIENT LIGHT SENSOR INTERFACE

| PARAMETER                                        | CONDITIONS                    |                           |      | ТҮР             | MAX                            | UNITS |

|--------------------------------------------------|-------------------------------|---------------------------|------|-----------------|--------------------------------|-------|

| BIAS Output Voltage                              | IBAIS = 200µA, VPV3 = 3.2     | / to 5.5V                 | 2.85 | 3.0             | 3.15                           | V     |

| BIAS Output Current                              | $V_{BIAS} = 3.0V \pm 5\%$     |                           |      |                 | 30                             | mA    |

| BIAS Dropout Voltage                             | IBIAS = 10mA (Note 3)         |                           |      | 125             | 250                            | mV    |

| SENSE Input Voltage Range                        |                               |                           | 0    |                 | V <sub>BIAS</sub> x<br>255/256 | V     |

| BIAS Discharge Resistance in Shutdown            |                               |                           |      | 1.0             | 1.5                            | kΩ    |

| ADC Resolution                                   |                               |                           |      | 8               |                                | Bit   |

| ADC Integral Nonlinearity Error                  |                               |                           | -3   |                 | +3                             | LSB   |

| ADC Differential Nonlinearity<br>Error           |                               |                           | -1   |                 | +1                             | LSB   |

| SENSE Input Impedance                            | $T_A = +25^{\circ}C$ (Note 3) |                           | 1    |                 |                                | MΩ    |

|                                                  |                               | Bit 0 = 0 in 02h register |      | 32              |                                | ms    |

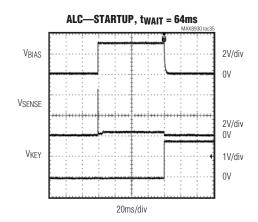

| Waiting Time for ADC Movement<br>After ALCEN = 1 | VBIAS = 3V                    | Bit = 1 in 02h register   |      | 64<br>(default) |                                | ms    |

## **KEY CHARACTERISTICS**

| PARAMETER                   | CONDITIONS               |                      | MIN | ТҮР  | MAX | UNITS |

|-----------------------------|--------------------------|----------------------|-----|------|-----|-------|

| Low-Level Output Voltage    | ISINK = 1mA              |                      |     |      | 0.4 | V     |

| High-Level Output Voltage   | ISOURCE = 1mA            |                      | 1.8 |      |     | V     |

|                             | At complementary output, | $T_A = +25^{\circ}C$ |     | 0.01 | 1   |       |

| nMOS Output Leakage Current | VPV3 = 3.7V (Note 6)     | TA = +85°C           |     | 0.1  |     | μA    |

|                             | At complementary output, | $T_A = +25^{\circ}C$ |     | 0.01 | 1   |       |

| pMOS Output Leakage Current | VPv3 = 3.7V (Note 6)     | TA = +85°C           |     | 0.1  |     | μA    |

MAX8930

## **CAI CHARACTERISTICS**

| PARAMETER                     | COND                                                                      | ITIONS               | MIN | ТҮР   | MAX  | UNITS |

|-------------------------------|---------------------------------------------------------------------------|----------------------|-----|-------|------|-------|

| PWM Low-Level Input Voltage   |                                                                           |                      |     |       | 0.4  | V     |

| PWM High-Level Input Voltage  |                                                                           |                      | 1.4 |       |      | V     |

| PWM Dimming Frequency         | $C_{FILT} = 0.1 \mu F$ (Note 3)                                           |                      |     | 0.2   | 15   | kHz   |

| Current Dimming Range         | Duty cycle = 0% to 100% (Note 3)                                          |                      |     |       | 25.6 | mA    |

| PWM Dimming Resolution        | $1\% \leq duty cycle \leq 100\%$ (Note 3)                                 |                      |     | 0.256 |      | mA/%  |

| CAI Enable Blanking Time (tB) | Time from CAI enable until dimming control switches to CAI input (Note 4) |                      |     | 10    |      | ms    |

|                               |                                                                           | $T_A = +25^{\circ}C$ |     | 0.1   | 1    |       |

| Input Leakage Current         | CAI = GND  or  VCAI = 3.7V                                                | TA = +85°C           |     | 1     |      | μA    |

## **GPO (OPEN-DRAIN OUTPUT) CHARACTERISTICS**

| PARAMETER                |                         | CONDITIONS           |  | TYP | MAX | UNITS |

|--------------------------|-------------------------|----------------------|--|-----|-----|-------|

| Low-Level Output Voltage | I <sub>SINK</sub> = 1mA | ISINK = 1mA          |  |     | 0.2 | V     |

| Output Lookage Current   |                         | $T_A = +25^{\circ}C$ |  | 0.1 |     |       |

| Output Leakage Current   | $V_{LDO} = 2.6V$        | $T_A = +85^{\circ}C$ |  | 1   |     | μΑ    |

## **EN CHARACTERISTICS**

| PARAMETER                | CONDITIONS                     |                      | MIN | TYP | MAX | UNITS |

|--------------------------|--------------------------------|----------------------|-----|-----|-----|-------|

| Low-Level Input Voltage  |                                |                      |     |     | 0.4 | V     |

| High-Level Input Voltage |                                |                      | 1.4 |     |     | V     |

|                          |                                | $T_A = +25^{\circ}C$ |     | 0.1 | 1   |       |

| Input Leakage Current    | $V_{EN} = 0V \text{ or } 3.7V$ | $T_A = +85^{\circ}C$ |     | 1   |     | - μΑ  |

## PLAYR/PLAYG/PLAYB CHARACTERISTICS

| PARAMETER                 | CONDITIONS                                                  | MIN | TYP | MAX | UNITS |

|---------------------------|-------------------------------------------------------------|-----|-----|-----|-------|

| Low-Level Input Voltage   |                                                             |     |     | 0.4 | V     |

| High-Level Input Voltage  |                                                             | 1.4 |     |     | V     |

| ON/OFF PWM Frequency      | (Note 3)                                                    | 2   |     | 200 | Hz    |

| PLAY_ Minimum High Time   | PLAY_ active high<br>(Bit 1 = low in Register 20h) (Note 3) | 80  |     |     | μs    |

| PLAY_ Minimum Low Time    | PLAY_ active low<br>(Bit 1= high in Register 20h) (Note 3)  | 80  |     |     | μs    |

| Pulldown Resistor to AGND |                                                             |     | 800 |     | kΩ    |

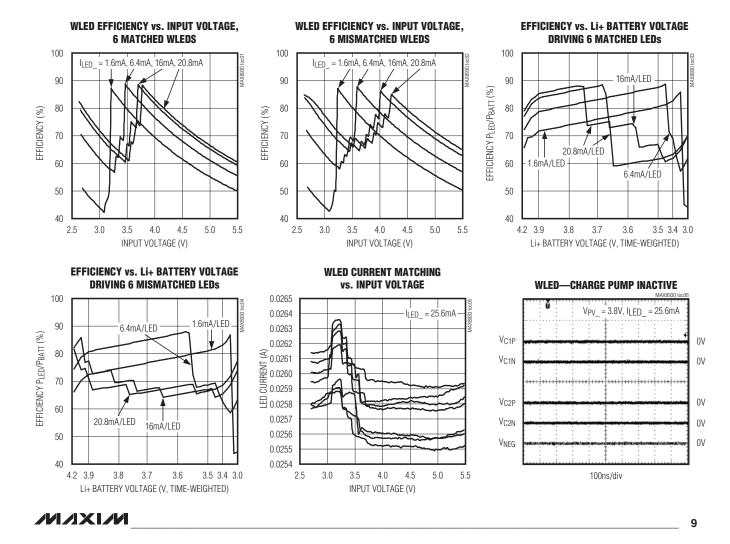

Typical Operating Characteristics

## **CHG PIN CHARACTERISTICS**

| PARAMETER         | CONDITIONS                  |                      | MIN | TYP  | MAX | UNITS |

|-------------------|-----------------------------|----------------------|-----|------|-----|-------|

| Low-Level Voltage | $I\overline{CHG} = 5mA$     |                      |     | 0.05 | 0.2 | V     |

| Leekege Current   |                             | $T_A = +25^{\circ}C$ |     | 0.1  | 1   |       |

| Leakage Current   | $V_{\overline{CHG}} = 3.7V$ | $T_A = +85^{\circ}C$ |     | 1    |     | - μΑ  |

**Note 1:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range are guaranteed by design. **Note 2:** 0.1mA LED load current is not included.

Note 3: Guaranteed by design. Not production tested.

Note 4: LED current matching is defined as: (IMAX - IMAX)/25.6mA. Matching is for LEDs within the RGB group (RLED, GLED, BLED) or the white LED group (WLED1–WLED8).

Note 5: Dropout voltage is defined as the LED\_ to AGND voltage at which current into LED\_ drops 10% from the value at V<sub>LED</sub> = 0.5V at 1x mode.

Note 6: VKEY = 0V when pulling low, leakage current from PV3. VKEY = 3.7V when pulling high, leakage current is to GND.

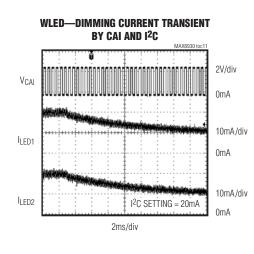

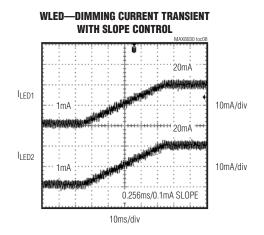

$(V_{PV} = V_{EN} = 3.7V)$ , circuit of Figure 1,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

#### Downloaded from **Elcodis.com** electronic components distributor

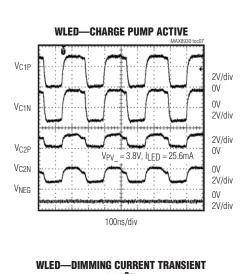

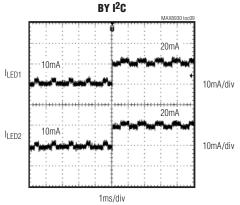

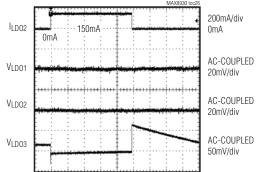

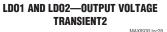

## **Typical Operating Characteristics (continued)**

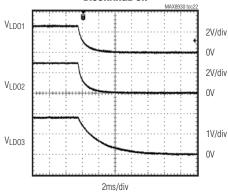

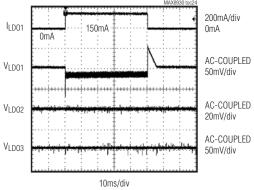

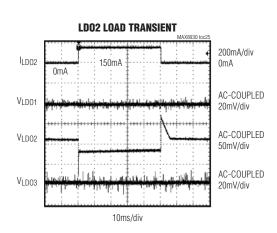

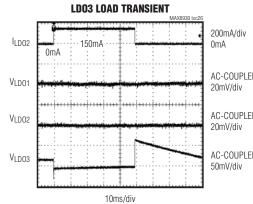

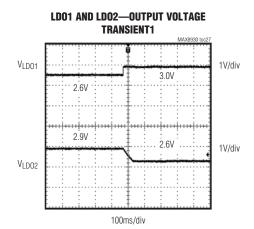

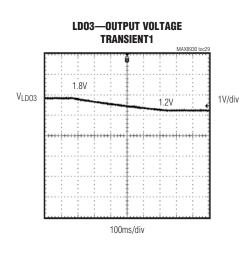

$\overline{(V_{PV} = V_{EN} = 3.7V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})}$

WLED—DIMMING CURRENT TRANSIENT BY CAI 2V/div VCAI 0mA VSDA 2V/div 0mA وفيقحة والقائرة أوطا ومرياها فرعا 10mA/div ILED1 0mA 10mA/div ILED2 I2C SETTING = 25.6mA TO 20mA 0mA 4ms/div

## **Typical Operating Characteristics (continued)**

$(V_{PV} = V_{EN} = 3.7V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

MAX8930

Downloaded from Elcodis.com electronic components distributor

**Typical Operating Characteristics (continued)**

$(V_{PV} = V_{EN} = 3.7V)$ , circuit of Figure 1,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

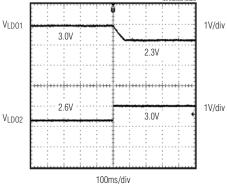

## **Typical Operating Characteristics (continued)**

$(V_{PV} = V_{EN} = 3.7V)$ , circuit of Figure 1,  $T_A = +25$ °C, unless otherwise noted.)

#### LD03—OUTPUT VOLTAGE **TRANSIENT2**

M/IXI/M

## **Typical Operating Characteristics (continued)**

$\overline{(V_{PV} = V_{EN} = 3.7V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})}$

1.04

1.03

1.02

1.01

1.00

0.99

0.98

0.97

0.96

200 180

160

NORMALIZED OUTPUT VOTLAGE

## **Typical Operating Characteristics (continued)**

$(V_{PV} = V_{EN} = 3.7V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

OUTPUT CURRENT (mA)

10ms/div

Typical Operating Characteristics (continued)

$\overline{(V_{PV} = V_{EN} = 3.7V, \text{ circuit of Figure 1, } T_A = +25^{\circ}C, \text{ unless otherwise noted.})}$

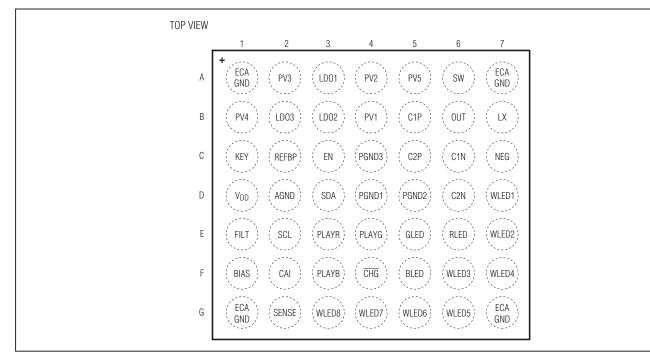

## \_Pin Configuration

## **Pin Description**

| PIN               | NAME                         | FUNCTION                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| EXTERNAL          | EXTERNALLY CONNECTED TO PGND |                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| A1, A7,<br>G1, G7 | ECAGND                       | Connect to AGND                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| POWER INP         | UT SUPPLY                    | AND POWER GROUND                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| A2                | PV3                          | Supply Voltage Input for Ref, Bias, LDO1, and LDO2. The input voltage range is 2.7V to 5.5V. Bypass PV3 to AGND with a 2.2µF ceramic capacitor as close as possible to the IC. PV3 is high impedance during shutdown. Connect PV3 to PV1, PV2, and PV5.                          |  |  |  |  |  |  |

| A4                | PV2                          | Supply Voltage Input. Connect PV2 to PV1.                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| A5                | PV5                          | Supply Voltage Input for the Step-Up Converter. The input voltage range is 2.7V to 5.5V. Bypass PV5 to PGND3 with a $1\mu$ F ceramic capacitor as close as possible to the IC. PV5 is high impedance during shutdown. Connect PV5 to PV1, PV2, and PV3.                          |  |  |  |  |  |  |

| B1                | PV4                          | Supply Voltage Input for LDO3. The input voltage range is 1.7V to 5.5V. Bypass PV4 to AGND with a 2.2µF ceramic capacitor as close as possible to the IC. PV4 is high impedance during shutdown. If PV4 is not used separately, connect PV4 to PV1.                              |  |  |  |  |  |  |

| B4                | PV1                          | Supply Voltage Input for Charge-Pump Circuitry. The input voltage range is 2.7V to 5.5V. Bypass PV1 to PGND1 and PGND2 with a $4.7\mu$ F to $10\mu$ F ceramic capacitor as close as possible to the IC. PV1 is high impedance during shutdown. Connect PV1 to PV2, PV3, and PV5. |  |  |  |  |  |  |

| C4                | PGND3                        | Power Ground for the Step-Up Converter                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| D4                | PGND1                        | Power Ground for the Charge-Pump Block                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| D5                | PGND2                        | Power Ground for the Charge-Pump Block                                                                                                                                                                                                                                           |  |  |  |  |  |  |

## Pin Description (continued)

| PIN       | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                           |

|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDO FUNCI | ΓΙΟΝ            |                                                                                                                                                                                                                                                                                                                    |

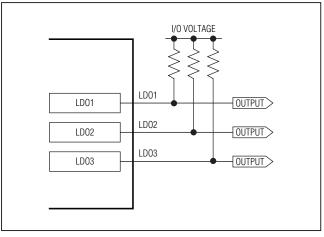

| A3        | LDO1            | Output of LDO1. The default value is 2.6V. Bypass LDO1 to AGND with a 1µF ceramic capacitor as close as possible to the IC.                                                                                                                                                                                        |

| B3        | LDO2            | Output of LDO2. The default value is 2.9V. Bypass LDO2 to AGND with a 1µF ceramic capacitor as close as possible to the IC.                                                                                                                                                                                        |

| B2        | LDO3            | Output of LDO3. The default value is 1.80V. Bypass LDO3 to AGND with a minimum 2.2 $\mu$ F ceramic capacitor as close as possible to the IC.                                                                                                                                                                       |

| LOGIC AND | ENABLE F        | UNCTION                                                                                                                                                                                                                                                                                                            |

| D1        | V <sub>DD</sub> | Logic-Supply Voltage Input. Bypass $V_{DD}$ to AGND with a 0.1µF ceramic capacitor as close as possible to the IC. The input range is 1.7V to 5.5V.                                                                                                                                                                |

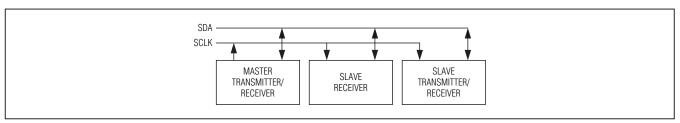

| D3        | SDA             | I <sup>2</sup> C Data Input. Data is read on the rising edge of SCL. Connect a 1.5k $\Omega$ resistor from SDA to V <sub>DD</sub> .                                                                                                                                                                                |

| E2        | SCL             | I <sup>2</sup> C Clock Input. Data is read on the rising edge of SCL. Connect a 1.5k $\Omega$ resistor from SCL to VDD.                                                                                                                                                                                            |

| D2        | AGND            | Analog Ground. Connect AGND to the system ground plane.                                                                                                                                                                                                                                                            |

| C3        | EN              | Hardware Enable Input for the IC. Drive EN high to activate the IC. Drive EN low to disable the IC.                                                                                                                                                                                                                |

| WLED AND  | RGB DIMM        | NG RELATED FUNCTION                                                                                                                                                                                                                                                                                                |

| F2        | CAI             | Brightness Control Input by Contents Adaptive Interface (DPWM signal). CAI varies the brightness of main WLEDs from 0% to 100%. The dimming frequency is typically 200Hz. When CAI is used as the main control method for main white LEDs, the ramp-up/ramp-down is automatically disabled.                        |

| E3        | PLAYR           | On/Off Input for the Red LED Current Regulator. The PLAYR signal can be either active high or active low. Program either active high or active low through the 20h register.                                                                                                                                       |

| E4        | PLAYG           | On/Off Input for the Green LED Current Regulator. The PLAYG signal can be either active high or active low. Program either active high or active low through the 20h register.                                                                                                                                     |

| F3        | PLAYB           | On/Off Input for the Blue LED Current Regulator. The PLAYB signal can be either active high or active low. Program either active high or active low through the 20h register.                                                                                                                                      |

| E1        | FILT            | PWM Filter Capacitor. Connect a $0.1\mu F$ ceramic capacitor between FILT and AGND as close as possible to FILT.                                                                                                                                                                                                   |

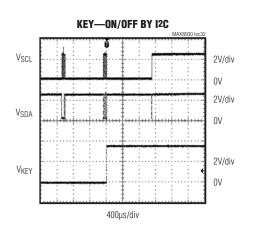

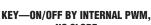

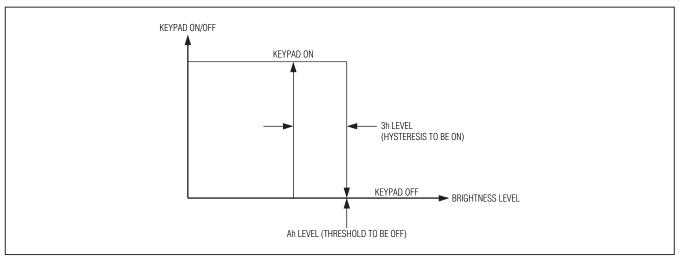

| C1        | KEY             | Key Backlight Control Output. Two threshold values for ON/OFF are available and programmable through the I <sup>2</sup> C serial interface. KEY on/off function is controlled by the I <sup>2</sup> C, ALC, or the internal 500Hz PWM signal. Program the settings for KEY through the I <sup>2</sup> C interface. |

| C2        | REFBP           | 1.20V Reference output. Bypass REFBP to AGND with 0.1 $\mu$ F ceramic capacitor as close as possible to the IC. Do not load REFBP.                                                                                                                                                                                 |

| AUTOMATIO | C LUMINAN       | CE CONTROL                                                                                                                                                                                                                                                                                                         |

| F1        | BIAS            | Bias Output for an External Light Sensor. Bypass BIAS to AGND with a $1\mu$ F ceramic capacitor as close as possible to the IC. The BIAS output is 3.0V.                                                                                                                                                           |

| G2        | SENSE           | Input from Ambient Light Sensor. Connect a 5.1k $\Omega$ resistor from SENSE to AGND.                                                                                                                                                                                                                              |

| CHARGE-P  | UMP BLOCH       |                                                                                                                                                                                                                                                                                                                    |

| B5        | C1P             | Transfer Capacitor 1 Positive Connection. Connect a 1µF ceramic capacitor from C1P to C1N.                                                                                                                                                                                                                         |

| C6        | C1N             | Transfer Capacitor 1 Negative Connection. Connect a 1µF ceramic capacitor from C1P to C1N.                                                                                                                                                                                                                         |

| C5        | C2P             | Transfer Capacitor 2 Positive Connection. Connect a 1µF ceramic capacitor from C2P to C2N.                                                                                                                                                                                                                         |

| C7        | NEG             | Charge-Pump Negative Output. Connect a 1 $\mu$ F to 2.2 $\mu$ F ceramic capacitor from NEG to PGND1. In shutdown, an internal 10k $\Omega$ resistor pulls NEG to PGND.                                                                                                                                             |

| D6        | C2N             | Transfer Capacitor 2 Negative Connection. Connect a 1µF ceramic capacitor from C2P to C2N.                                                                                                                                                                                                                         |

## \_Pin Description (continued)

| PIN       | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                       |

|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WLED AND  | RGB     |                                                                                                                                                                                                                                                                                                                |

| D7        | WLED1   | WLED Current Sink Regulator. Current into WLED1 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED1 to the cathodes of external LEDs. WLED1 is high impedance during shutdown. If unused, short WLED1 to PV3.                                                                      |

| E7        | WLED2   | WLED Current Sink Regulator. Current into WLED2 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED2 to the cathodes of external LEDs. WLED2 is high impedance during shutdown. If unused, short WLED2 to PV3.                                                                      |

| F6        | WLED3   | WLED Current Sink Regulator. Current into WLED3 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED3 to the cathode of an external WLED. WLED3 is high impedance during shutdown. If unused, short WLED3 to PV3.                                                                    |

| F7        | WLED4   | WLED Current Sink Regulator. Current into WLED4 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED4 to the cathode of an external LED. WLED4 is high impedance during shutdown. If unused, short WLED4 to P3.                                                                      |

| G6        | WLED5   | WLED Current Sink Regulator. Current into WLED5 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED5 to the cathode of an external WLED. WLED5 is high impedance during shutdown. If unused, short WLED5 to either PV3 or disable the regulator.                                    |

| G5        | WLED6   | WLED Current Sink Regulator. Current into WLED6 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED6 to the cathode of an external WLED. WLED6 is high impedance during shutdown. If unused, short WLED6 to either PV3 or disable the regulator.                                    |

| G4        | WLED7   | WLED Current Sink Regulator. Current into WLED7 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED7 to the cathode of an external WLED. WLED7 is high impedance during shutdown. If unused, short WLED7 to either PV3 or disable the regulator.                                    |

| G3        | WLED8   | WLED Current Sink Regulator. Current into WLED8 is based upon the programmed internal I <sup>2</sup> C registers. Connect WLED8 to the cathode of an external WLED. WLED8 is high impedance during shutdown. If unused, short WLED8 to either PV3 or disable the regulator.                                    |

| E6        | RLED    | Red LED Connection. The brightness is set up by I <sup>2</sup> C. ON/OFF is synchronized with the PWM signal applied to PLAYR pin. RLED maximum brightness is enabled/disabled through the serial interface.                                                                                                   |

| E5        | GLED    | Green LED Connection. The brightness is set up by I <sup>2</sup> C. ON/OFF is synchronized with the PWM signal applied to PLAYG pin. GLED maximum brightness is enabled/disabled through the serial interface.                                                                                                 |

| F5        | BLED    | Blue LED Connection. The brightness is set up by I <sup>2</sup> C. ON/OFF is synchronized with the PWM signal applied to PLAYB pin. BLED maximum brightness is enabled/disabled through the serial interface.                                                                                                  |

| BOOST CO  | NVERTER |                                                                                                                                                                                                                                                                                                                |

| B6        | OUT     | Step-Up Converter Output. Bypass OUT to GND with a 1 $\mu$ F ceramic capacitor. During shutdown, OUT is pulled to PGND3 by an internal 1M $\Omega$ resistor.                                                                                                                                                   |

| A6        | SW      | Isolation Switch Output for the Step-Up Converter. SW is internally connected to the drain of a p-channel MOSFET and used to isolate the output of the step-up from the input during shutdown. If true shutdown is not required, SW can be left open with the input supply connected directly to the inductor. |

| B7        | LX      | Inductor Switching Connection. Connect the inductor between LX and SW. For most applications, use a $22\mu H$ inductor.                                                                                                                                                                                        |

| STATUS IN | DICATOR |                                                                                                                                                                                                                                                                                                                |

| F4        | CHG     | Charging Status Output. $\overline{CHG}$ is an open-drain output that goes low when the battery is charging.<br>On/off is operated by I <sup>2</sup> C. $\overline{CHG}$ is high impedance when the IC is in shutdown mode. Enable $\overline{CHG}$ through the I <sup>2</sup> C interface.                    |

MAX8930

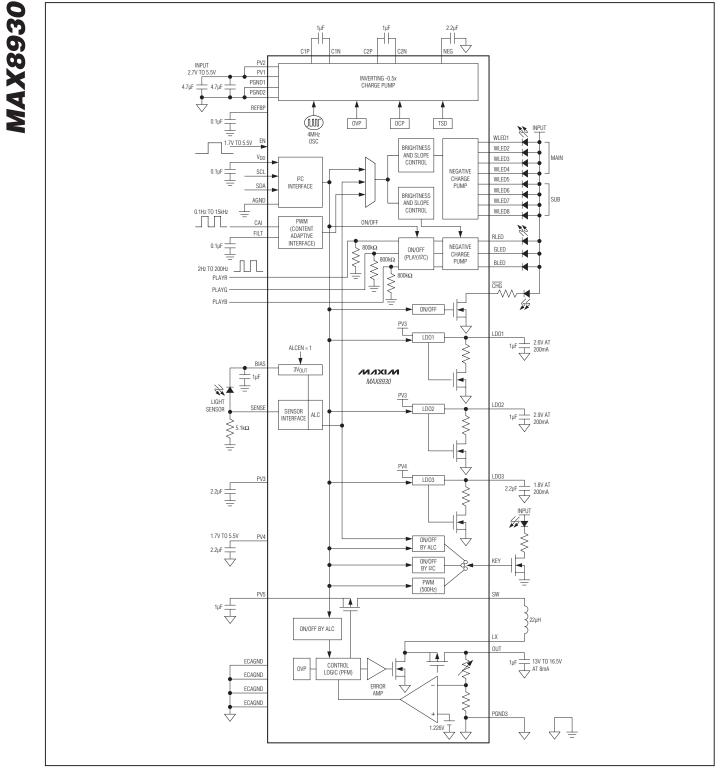

Figure 1. Typical Application and Block Diagram

## **\_External Components**

| PIN                | EXTERNAL COMPONENTS                                                          | NOTES                                |

|--------------------|------------------------------------------------------------------------------|--------------------------------------|

| PV1, PV2, PV3, PV5 | 10µF<br>Total capacitance ≥ total LDO, boost,<br>and charge-pump capacitance | System stability                     |

| PV4                | 2.2µF                                                                        | LDO stability                        |

| VDD                | 0.1µF                                                                        | Decoupling                           |

| BIAS               | 1µF                                                                          | LDO compensation                     |

| LDO1               | 1µF                                                                          | LDO compensation                     |

| LDO2               | 1µF                                                                          | LDO compensation                     |

| LDO3               | 2.2µF                                                                        | LDO compensation                     |

| FILT               | 0.1µF                                                                        | Noise filter                         |

| REFBP              | 0.1µF                                                                        | Noise filter                         |

| C1P, C1N           | 1µF                                                                          | Charge pump                          |

| C2P, C2N           | 1µF                                                                          | Charge pump                          |

| NEG                | 2.2µF                                                                        | Charge pump                          |

| WLED1-WLED8        | White LED                                                                    | _                                    |

| RLED, GLED, BLED   | Red, green, blue LED                                                         | _                                    |

| CHG                | A resister, for example $10k\Omega$                                          | Current limit                        |

| SW, LX             | 22µH                                                                         | Boost converter                      |

| OUT                | 1µF                                                                          | Boost stability                      |

| SENSE              | 5.1kΩ                                                                        | Converter ambient light to a voltage |

| ALC                | Toshiba TPS852                                                               | Any type (linear/log) of photo IC    |

Note: All output capacitors are ceramic and X7R/X5R type.

MAX8930

## **Detailed Description**

The MAX8930 integrates a negative charge pump for both white LED display backlighting with ambient light control (ALC) function, content adaptive interface (CAI) function, and R/G/B LED. There is one step-up converter for passive matrix OLED (PMOLED) oriented application and three LDOs with programmable output voltage. The three LDO outputs are able to convert to GPO (generalpurpose output) status through an I<sup>2</sup>C command. The MAX8930 includes soft-start, thermal shutdown, opencircuit, and short-circuit protection in the charge-pump circuitry.

#### **Reset Control**

The MAX8930 uses two different methods of reset: software and hardware.

**Software Reset:** All the registers are initiated by RESET = 1 at Register 00h. After that, the values in all registers come back to POR (power-on-reset) state. The bit of RESET in 00h is automatically returned to 0. Auto return to 0.

**Hardware Reset:** Hardware reset is done by toggling EN from logic-high to logic-low. All the registers under hardware reset conditions are returned to their initial values (POR) and stop receiving any commands.

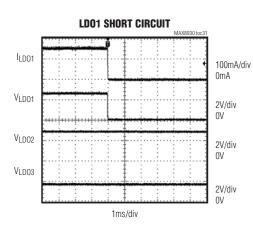

## **Open-Circuit and Short-Circuit Protection**

If any WLED/RGB fails as an open circuit, that LED pin pulls to ground, and the IC is forced into -0.5X mode. Therefore, connect any unused WLED\_/RGB pins to PV1, PV2, or PV3 to disable the corresponding current regulator. The MAX8930 contains special circuitry to detect this condition and disables the corresponding current regulator to avoid wasting battery current.

#### **Thermal Shutdown**

The MAX8930 includes a thermal-limit circuit that shuts down the IC at about +160°C. The part turns on after the IC cools by approximately  $20^{\circ}$ C.

Thermal shutdown is applied to the following blocks:

- White and RGB LED driver

- Step-up converter

- LDO1, LDO2, LDO3

- SBIAS

22

## **LED Charge Pump**

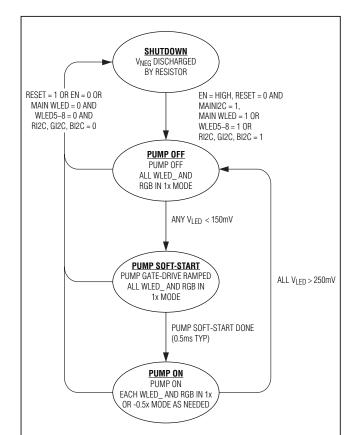

The charge pump drives up to 8 white LEDs (4 WLEDs for main and 4 WLEDs for sub) and 3 RGB LEDs with regulated constant current for both display backlight and fun light applications. By utilizing individually adaptive 1x/-0.5x negative charge-pump modes and extremely low-dropout current regulators, it is able to achieve high efficiency over the full 1-cell lithium battery input voltage range. High-frequency switching of 4MHz allows for tiny external components. The regulation scheme is optimized to ensure low EMI and low input ripple. Each channel for WLED and RGB LED has the capability of delivering 25.6mA with 256 dimming steps (0.1mA per step). The current-level adjustment is programmed by an I<sup>2</sup>C command. Figure 2 is the flow chart of the startup and mode-change algorithm.

Figure 2. Startup and Mode Change Algorithm

**UAX8930**

## WLED1-WLED8 Driver Operation

The white LED current regulators are composed of 4 main-group drivers (WLED1–WLED4) and 4 subgroup drivers (WLED5–WLED8). The current of the main-group LEDs can be selected by an I<sup>2</sup>C register. Both ambient light control (ALC) mode and ramp-up/ramp-down control are applied to only the main-group white LEDs.

The subgroup LEDs can choose either individual control or can belong to the main group based on the status of a bit in the register (01h and 02h). In this function, combinations can be adjusted as required. For example, main 4ch + sub 4ch or main 5ch + sub 3ch.

The CAI (PWM) signal from either the LCD driver module or baseband chipset controls only the main-group WLEDS. The up/down slope control can be programmed by the setting of the 0Ah register when the main LEDs are controlled by either I<sup>2</sup>C or ALC.

For main LEDs, there are three different dimming control methods, I<sup>2</sup>C, ALC, and CAI. The dimming range for main LEDs and sub LEDs is from 0.1mA to 25.6mA in 0.1mA increments.

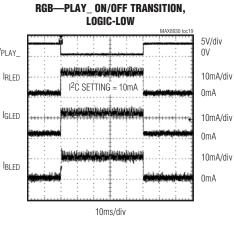

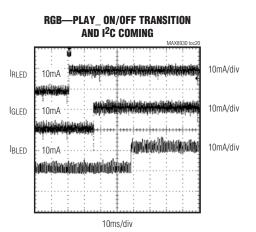

#### **RGB Driver Operation**

The brightness for each color LED has 256 different steps (0.1mA to 25.6mA). The RGB LED can be activated by either the high/low status of the PLAY\_PWM signal or by I<sup>2</sup>C ON/OFF command. The default dimming control is I<sup>2</sup>C command. An I<sup>2</sup>C command for dimming can adjust the current of each RGB individually. The operation of ON/OFF by I<sup>2</sup>C command also allows individual control. However, the operation of ON/OFF by PWM to PLAY\_RGB is group control. To operate with either an active-high or active-low signal coming from the microprocessor such as audio processor, the register related to active high or active low should be selected first (the bit 1 in 20h). When a call comes in or music plays, all RGB LEDs are allowed to be activated by either a PWM signal applied to PLAY\_ or a designated register by I<sup>2</sup>C.

The main purpose for the PLAY\_ is for ON/OFF control function and not for dimming control. If the dimming current is set to 10mA on each RGB LED, the PWM signal to PLAY\_ RGB turns all of the current regulators on or off at the same time. However, the dimming current for RGB can be set by I<sup>2</sup>C command during ON/OFF operation. When the PLAY\_ is in active-high period, the RGB current regulator is on with 10mA current. When the PLAY\_ is in the opposite state (active-low period), the RGB regulator is off with 0mA current. The default method to turn the RGB LED on is to pull the PLAY\_ input high with

a minimum on-time of 80 $\mu$ s in active-high mode. If bit 1 in 20h is set to 1, then all current regulators for RGB are activated by active-low signal with a minimum off-time of 80 $\mu$ s. The up/down slope control can be programmed by the setting of the 0Bh register when the RGB LEDs are controlled by I<sup>2</sup>C only.

If bit 7 in 20h is set to logic-low, then slope up/down is automatically deactivated.

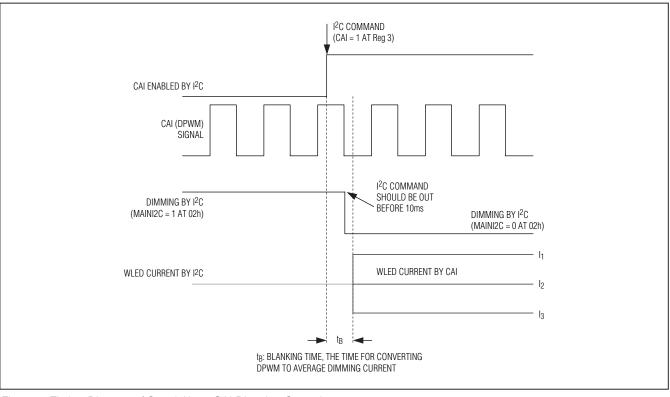

#### CAI (Contents Adaptive Interface) Operation

A 200Hz PWM signal is applied to the CAI pin. The CAI signal can be from either the LCD driver module with gamma correction information or from the baseband chipset. The main WLED can be activated by either the high/low status of the CAI PWM signal or with either an active-high or active-low signal coming from either a LCD driver module or baseband chipset. The corresponding register bit (bit 0 in 02h) should be set to either, 1 or 0 by I<sup>2</sup>C command.

Depending on the duty cycle, the brightness varies from 0mA to 25.6mA with the resolution of 0.256mA per 1% duty variation. In control of CAI (PWM) independently, the existing brightness setting from either I<sup>2</sup>C or ALC is overwritten because CAI has the priority over I<sup>2</sup>C and ALC.

See the *Dimming by Digital PWM on CAI Only* and *Dimming by Both Digital PWM on CAI and Either I<sup>2</sup>C or ALC at the Same Time* sections for details on the CAI dimming control.

#### Dimming by Digital PWM on CAI Only

When the digital PWM (DPWM) signal (100Hz ~15kHz) is provided by either the baseband or CPU for dimming the brightness, the MAX8930 DPWM function takes over the responsibility of dimming the main WLEDs. The dimming by CAI is initiated by setting CAI (bit 7 of Register 02h) to 1. After the set-up, both I<sup>2</sup>C register dimming settings and ALC no longer control the dimming current for the main WLEDs. The frequency range on the CAI pin is from 100Hz to 15kHz, where 0% duty cycle corresponds to 0mA and 100% duty cycle corresponds to full current, 25.6mA.

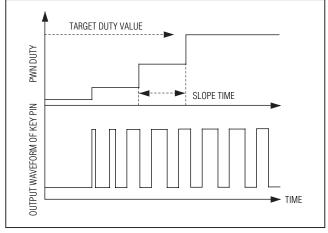

When CAI is set to 1, the ramp-up/down slope for main WLED\_ is automatically disabled by the MAX8930 control logic. Figure 3 is the timing diagram on initiating CAI. The MAX8930 maintains its previous dimming setting for tB (10ms typ) to allow the PWM filter time to settle to its average value before activating CAI dimming. This is done automatically inside the IC. The bit of MAINI2C

**MAX8930**

Figure 3. Timing Diagram of Stand-Alone CAI Dimming Operation

should be set to 0 in less than t<sub>B</sub>, 10ms (typ) for CAI dimming to be exclusively through DPWM.

If this setup fails, the previous dimming current is still effective even though bit 7 in 02h (CAI) has been set to 1.

The current of I1, I2, and I3 of Figure 3 is different depending on the duty cycle of DPWM.

tB is the settling time for the CAI input filter to calculate an average value for the dimming current.

## Dimming by Both Digital PWM on CAI and Either I<sup>2</sup>C or ALC at the Same Time

If an end-user wants to see either TV or a movie, the LCD driver module may take care of dimming control independently. In this situation, the output signal from the LCD module has some color information. For example, (16mA/LED) + gamma correction can make the user feel the same brightness of the LCD screen compared to (20mA/LED) + no gamma correction.

In this combined dimming control, any dimming current set earlier by either the  $l^2C$  register or the ALC register is the value corresponding with 100% duty cycle of the CAI signal.

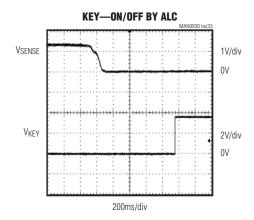

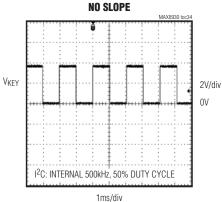

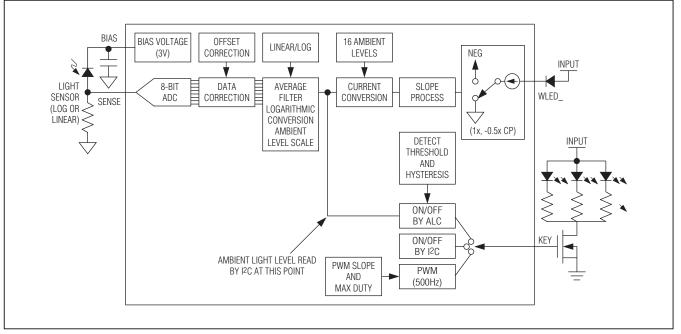

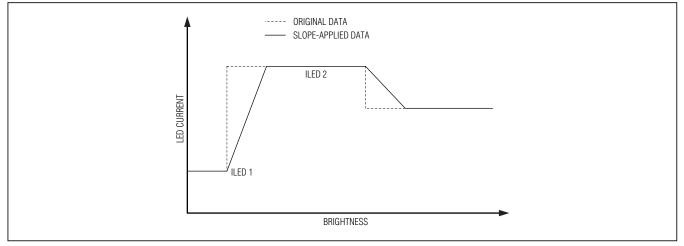

#### **Ambient Light Control Operation**

Dimming of the LCD backlight and ON/OFF control of the keypad backlight are possible on the basis of the data detected by an external ambient light sensor. The ALC consists of the following segments:

- Bias function (3V output)

- 8-bit ADC with an average filter

- A slope process function

- A LOG scale conversion function