# 3-Channel Laser Diode Driver with Oscillator

# AD9662

#### **FEATURES**

Current-controlled current source with 3 input channels Output current for Channel 3—315 mA Output current for other channels—210 mA Rise time/fall time of 0.8 ns On-chip oscillator Single 5 V power supply (±10%) Low output overshoot Low power consumption

#### **APPLICATIONS**

CD-RW drives DVD-RW, DVD+RW, MO drives Laser diode current switching

#### **GENERAL DESCRIPTION**

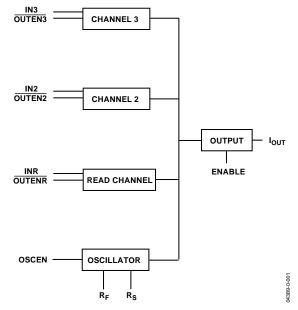

The AD9662 is a laser diode driver for high performance CD and DVD recordable drives. It includes three channels for three different optical power levels: the read channel generates a continuous output power level, whereas Channel 2 and Channel 3 are used as write channels having 0.8 ns rise/fall times. All channel currents are summed at the I<sub>OUT</sub> pin. Each channel's output current is established by multiplying the channel's gain by the channel's input current. The input current for each of the input channels—INR, IN2, and IN3—can be set either by using an external resistor that converts an input voltage to a current or by directly using a current source.

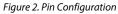

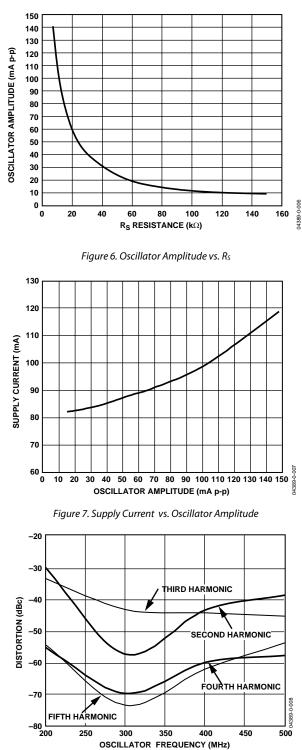

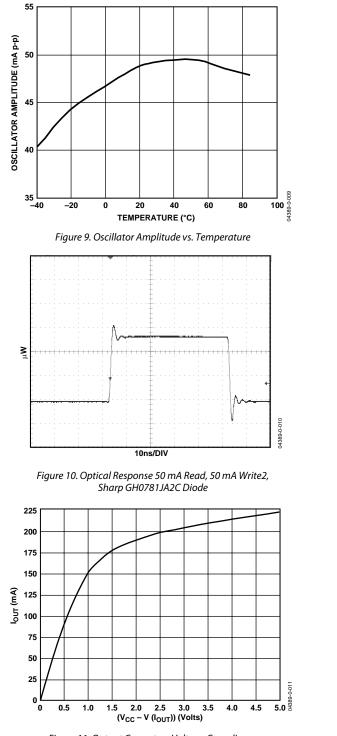

An on-chip oscillator is provided to allow output current modulation (to reduce laser mode hopping). Two external resistors control the frequency and the amplitude swing of the oscillator. The push-pull oscillator can swing up to 100 mA p-p and has a frequency range of 200 MHz to 500 MHz.

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1. AD9662 3-Channel Laser Diode Driver

Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

© 2005 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Features                 | 1 |

|--------------------------|---|

| Applications             | 1 |

| General Description      | 1 |

| Functional Block Diagram | 1 |

| Revision History         | 2 |

| Specifications           | 3 |

| Absolute Maximum Ratings | 5 |

| ESD Caution              | 5 |

| Pin Configuration and Function Descriptions | 6  |

|---------------------------------------------|----|

| Typical Performance Characteristics         | 7  |

| Applications                                | 10 |

| Temperature Considerations                  | 10 |

| Evaluation Board                            | 12 |

| Outline Dimensions                          | 13 |

| Ordering Guide                              | 13 |

### **REVISION HISTORY**

| Changes to FormatUni | versal |

|----------------------|--------|

|----------------------|--------|

### 7/04—Rev. Sp0 to Rev. SpB

| Changes to Note 2 in Specifications | 4  |

|-------------------------------------|----|

| Changes to Absolute Maximum Ratings | 5  |

| Changes to Figure 17                | 12 |

#### 12/03—Rev. SpA: Initial 2-Page Web Version

12/03—Rev. Sp0: Initial Full Version

### **SPECIFICATIONS**

At  $T_{AMB}$ ,  $V_{CC} = 5$  V, ENABLE = 1, OSCEN = 0,  $\overline{OUTENx} = 1$ , unless otherwise stated.

#### Table 1.

| Parameter                                                | Conditions                                                                                                                                                  | Min | Тур  | Max | Unit    |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|---------|

| LASER AMPLIFIER                                          |                                                                                                                                                             |     |      |     |         |

| Output Current Read Channel                              | Output is sourcing, $\overline{OUTENR} = 0$                                                                                                                 | 210 | 235  |     | mA      |

| Output Current Channel 2                                 | Output is sourcing, $\overline{OUTEN2} = 0$                                                                                                                 | 210 | 235  |     | mA      |

| Output Current Channel 3                                 | Output is sourcing, $\overline{OUTEN3} = 0$                                                                                                                 | 315 | 340  |     | mA      |

| Total Output Current                                     | Output is sourcing, $\overline{OUTEN3} = 0$ and<br>( $\overline{OUTENR} = 0$ and/or $\overline{OUTEN2} = 0$ )                                               |     | >550 |     | mA      |

| Output Current Linearity <sup>1</sup>                    | Read Channel, $\overline{OUTENR} = 0$                                                                                                                       | -4  | ±0.6 | +4  | %       |

| Output Current Linearity <sup>1</sup>                    | Write2 Channel, $\overline{OUTEN2} = 0$                                                                                                                     | -4  | ±0.6 | +4  | %       |

| Output Current Linearity <sup>1</sup>                    | Write3 Channel, $\overline{OUTEN3} = 0$                                                                                                                     | -4  | ±0.1 | +4  | %       |

| Best-Fit Current Gain <sup>1</sup>                       | Read Channel, $\overline{OUTENR} = 0$                                                                                                                       | 125 | 135  | 145 | mA/m/   |

| Best-Fit Current Gain <sup>1</sup>                       | Write2 Channel, $\overline{OUTEN2} = 0$                                                                                                                     | 120 | 130  | 140 | mA/m/   |

| Best-Fit Current Gain <sup>1</sup>                       | Write3 Channel, $\overline{OUTEN3} = 0$                                                                                                                     | 240 | 260  | 280 | mA/m/   |

| Best-Fit Current Offset <sup>1</sup>                     | Read Channel, $\overline{OUTENR} = 0$                                                                                                                       | -7  | ±0.6 | +7  | mA      |

| Best-Fit Current Offset <sup>1</sup>                     | Write2 Channel, $\overline{OUTEN2} = 0$                                                                                                                     | -7  | ±0.6 | +7  | mA      |

| Best-Fit Current Offset <sup>1</sup>                     | Write3 Channel, $\overline{OUTEN3} = 0$                                                                                                                     | -30 | -2   | +15 | mA      |

| lout Series Resistance                                   | Total Rout to Vcc rail                                                                                                                                      |     | 6.5  | 10  | Ω       |

| Input Impedance (R <sub>IN</sub> ), Channel R, Channel 2 | R <sub>IN</sub> to GND                                                                                                                                      | 160 | 200  | 240 | Ω       |

| Input Impedance ( $R_{IN}$ ), Channel 3                  | R <sub>IN</sub> to GND                                                                                                                                      | 80  | 100  | 120 | Ω       |

| I <sub>OUT</sub> Supply Sensitivity (PSRR)<br>Read Mode  | $I_{OUT} = 50 \text{ mA} \text{ (read-only)}, V_{CC} = 5 \text{ V} \pm 10\%$<br>$\overline{\text{OUTENR}} = 0$                                              |     | 10   | 15  | %/V     |

| lout Supply Sensitivity (PSRR)                           | $I_{OUT} = 100 \text{ mA} (50 \text{ mA read}, 50 \text{ mA write})$                                                                                        |     | 10   | 15  | %/V     |

| Write Mode                                               | $V_{CC} = 5 V \pm 10\%, \overline{OUTENR} = 0 \text{ and}$<br>(OUTEN2 = 0 or OUTEN3 = 0)                                                                    |     |      |     | , , , , |

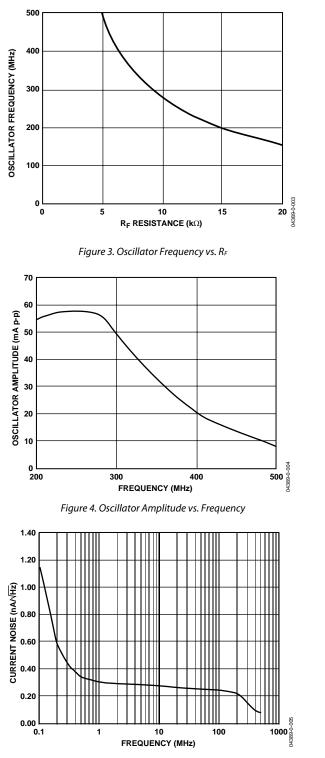

| Output Current Noise                                     | $I_{OUT} = 50 \text{ mA} (\text{Read}), \overline{\text{OUTENR}} = 0, \text{ f} = 300 \text{ MHz}$                                                          |     | 150  |     | pA/√H   |

| lout Temperature Sensitivity                             | $I_{OUT} = 50 \text{ mA} (\text{read-only})$                                                                                                                |     | 100  |     | ppm/°   |

| Read Mode                                                | OUTENR = 0                                                                                                                                                  |     |      |     |         |

| Iout Temperature Sensitivity<br>Write Mode Channel 2     | $I_{OUT} = 100 \text{ mA} (50 \text{ mA Read}, 50 \text{ mA Write2})$<br>$\overline{OUTENR} = 0, \overline{OUTEN2} = 0$                                     |     | 100  |     | ppm/°   |

| IouT Temperature Sensitivity<br>Write Mode Channel 3     | $I_{OUT} = 100 \text{ mA} (50 \text{ mA Read}, 50 \text{ mA Write3})$<br>$\overline{OUTENR} = 0, \overline{OUTEN3} = 0$                                     |     | 100  |     | ppm/°   |

| LASER AMPLIFIER AC SPECIFICATIONS                        |                                                                                                                                                             |     |      |     |         |

| Write Rise Time <sup>2</sup>                             | $I_{OUT} = 50 \text{ mA dc}$ (Read), 50 mA pulse W2 or W3<br>$\overline{OUTENR} = 0 \text{ and } (\overline{OUTEN2} = 0 \text{ or } \overline{OUTEN3} = 0)$ |     | 0.8  | 1.8 | ns      |

| Write Fall Time <sup>2</sup>                             | $I_{OUT} = 50 \text{ mA dc}$ (Read), 50 mA pulse W2 or W3<br>$\overline{OUTENR} = 0$                                                                        |     | 0.6  | 1.8 | ns      |

| Output Current Overshoot                                 | $I_{OUT} = 50 \text{ mA dc}$ (Read), 50 mA pulse W2 or W3<br>$\overline{OUTENR} = 0 \text{ and } (\overline{OUTEN2} = 0 \text{ or } \overline{OUTEN3} = 0)$ |     | 13   |     | %       |

| Iout ON Propagation Delay                                | OUTENx 50% H-L to lout at 50% of final value                                                                                                                |     | 2.7  |     | ns      |

| lout OFF Propagation Delay                               | OUTENx 50% L-H to lour at 50% of initial value                                                                                                              |     | 2.7  |     | ns      |

| Disable Time                                             | ENABLE 50% H-L to $I_{OUT}$ at 50% of initial value                                                                                                         |     | 5.4  |     | ns      |

| Enable Time                                              | ENABLE 50% L-H to IOUT at 50% of final value                                                                                                                |     | 13.5 |     | ns      |

| OSCILLATOR SPECIFICATIONS                                | $\overline{OUTENR} = 0$                                                                                                                                     | 1   |      |     | 1       |

| Oscillator Frequency                                     | $R_F = 9.53 \text{ k}\Omega$ , $R_S = 23.7 \text{ k}\Omega$                                                                                                 | 265 | 300  | 325 | MHz     |

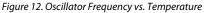

| Oscillator Frequency Temperature Coefficient             | $R_F = 9.53 \text{ k}\Omega, R_S = 23.7 \text{ k}\Omega$                                                                                                    |     | 600  |     | ppm/°   |

| Disable Time Oscillator                                  | OSCEN 50% H-L to amplitude at 50% of initial value                                                                                                          |     | 4    |     | ns      |

| Enable Time Oscillator                                   | OSCEN 50% L-H to amplitude at 50% of final value                                                                                                            |     | 6    |     | ns      |

Rev. C | Page 3 of 16

| Parameter                                      | Conditio | Conditions |        |        |        | Min | Тур | Max | Unit |

|------------------------------------------------|----------|------------|--------|--------|--------|-----|-----|-----|------|

| LOGIC SPECIFICATIONS                           |          |            |        |        |        |     |     |     |      |

| Logic HI Threshold                             |          |            |        |        |        | 2.0 |     |     | V    |

| Logic LO Threshold                             |          |            |        |        |        |     |     | 0.8 | V    |

| Input Impedance                                | OUTENx,  | ENABLE, O  | SCEN   |        |        |     | >10 |     | MΩ   |

| Input Leakage Current                          | OUTENx,  | ENABLE, C  | SCEN   |        |        |     | <1  |     | μΑ   |

| SUPPLY CURRENT                                 | ENABLE   | OSCEN      | OUTENR | OUTEN2 | OUTEN3 |     |     |     |      |

| Power-Down                                     | 0        | 0          | 1      | 1      | 1      |     | 8.5 | 10  | mA   |

| Power-Up                                       |          |            |        |        |        |     |     |     |      |

| Inputs Disabled                                | 1        | 0          | 1      | 1      | 1      |     | 18  | 22  | mA   |

| Inputs Disabled, OSC Enabled                   | 1        | 1          | 1      | 1      | 1      |     | 52  | 62  | mA   |

| Read Mode, OSC Enabled <sup>3</sup>            | 1        | 1          | 0      | 1      | 1      |     | 55  | 65  | mA   |

| l <sub>out</sub> = 50 mA                       |          |            |        |        |        |     |     |     |      |

| Write Mode <sup>3</sup>                        | 1        | 0          | 1      | 0      | 0      |     | 29  | 35  | mA   |

| l <sub>out</sub> = 100 mA (50 mA W2, 50 mA W3) |          |            |        |        |        |     |     |     |      |

| OPERATING CONDITIONS                           |          |            |        |        |        |     |     |     |      |

| Supply Voltage Range                           |          |            |        |        |        | 4.5 |     | 5.5 | V    |

| Operating Temperature Range                    |          |            |        |        | 0      |     | 85  | °C  |      |

<sup>1</sup> Output linearity, offset current, and gain are calculated using a best-fit method at 30 mA, 45 mA, 60 mA, 75 mA, and 90 mA for the Read and Write2 Channels and 90 mA, 105 mA, 120 mA, 135 mA, and 150 mA for Write Channel 3. Each channel's output current is given by  $l_{0UT} = (l_{IN} \times Gain) + l_{os}$ . <sup>2</sup> This parameter is guaranteed by design and characterization using six sigma. Rise and fall times are measured electrically from the 10% to 90% points using a Sharp GH0781JA2C diode as a load.

<sup>3</sup> The values specified do not include the output current.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                               | Range            |

|-----------------------------------------|------------------|

| Supply Voltage +Vs                      |                  |

| Pin 9, Pin 15, and Pin 16               | 5.5 V            |

| Input Pins                              |                  |

| Pin 1 and Pin 2                         | 2.2 mA           |

| Pin 5                                   | 1.6 mA           |

| Pin 6, Pin 7, Pin 8, Pin 10, and Pin 11 | –0.8 V to +5.5 V |

| Internal Power Dissipation <sup>1</sup> |                  |

| 16-Lead QSOP                            | 620 mW           |

| Operating Temperature Range             | 0°C to +85°C     |

| Storage Temperature Range               | –65°C to +150°C  |

| Lead Temperature, Soldering 60 sec      | 300°C            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup> Power dissipation is specified on SEMI standard 4-layer board.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

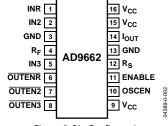

### **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 3. Pin Function Descriptions**

| Pin No.   | Mnemonic         | Description                                                                                              |

|-----------|------------------|----------------------------------------------------------------------------------------------------------|

| 1         | INR              | Input Current Pin for the Read Channel. Has a typical input impedance of 200 $\Omega$ .                  |

| 2         | IN2              | Input Current Pin for Write Channel 2. Has a typical input impedance of 200 $\Omega$ .                   |

| 3, 13     | GND              | Common External Ground Reference.                                                                        |

| 4         | R <sub>F</sub>   | Pin Used to Set Oscillator Frequency by Connecting a Resistor from This Pin to Ground.                   |

| 5         | IN3              | Input Current Pin for Write Channel 3. Has a typical input impedance of 100 $\Omega$ .                   |

| 6         | OUTENR           | TTL-Compatible Enable for the Read Channel. Logic low active.                                            |

| 7         | OUTEN2           | TTL-Compatible Enable for Write Channel 2. Logic low active.                                             |

| 8         | OUTEN3           | TTL-Compatible Enable for Write Channel 3. Logic low active.                                             |

| 9, 15, 16 | Vcc              | Power Supply Pins for the AD9662. Each pin needs to be decoupled with a 0.1 $\mu$ F capacitor to ground. |

| 10        | OSCEN            | TTL-Compatible Enable for the Oscillator. Logic high active.                                             |

| 11        | ENABLE           | TTL-Compatible Enable for the Device. Logic high active.                                                 |

| 12        | Rs               | Pin Used to Set Oscillator Amplitude by Connecting a Resistor from This Pin to Ground.                   |

| 14        | I <sub>OUT</sub> | Output Current Pin. This pin is connected to the anode of a laser diode.                                 |

### **TYPICAL PERFORMANCE CHARACTERISTICS**

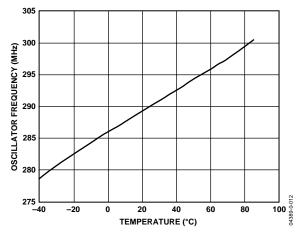

$R_{s}$  = 23.7 k $\Omega$ ,  $R_{F}$  = 9.53 k $\Omega$ , and read channel output current is 50 mA, unless otherwise noted.

Figure 5. IOUT Current Noise

Figure 8. Oscillator Harmonic Distortion vs. Frequency

Figure 11. Output Current vs. Voltage Compliance

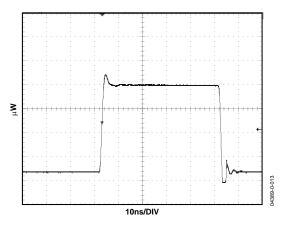

Figure 13. Optical Response 50 mA Read, 200 mA Write3, Sharp GH0781JA2C Diode

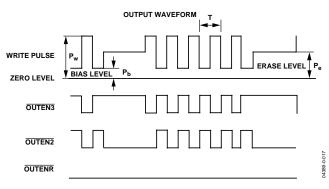

Figure 14. Typical Waveform

#### Table 4. IOUT Control

| ENABLE | OUTENR | OUTEN2 | OUTEN3 | Ιουτ                                                                                                              |

|--------|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------|

| 0      | Х      | Х      | Х      | Off                                                                                                               |

| 1      | 1      | 1      | 1      | Off                                                                                                               |

| 1      | 0      | 1      | 1      | $(I_{INR} \times Gain_R) + I_{OSR}$                                                                               |

| 1      | 1      | 0      | 1      | $(I_{INR} \times Gain_R) + I_{OSR}$<br>$(I_{IN2} \times Gain_2) + I_{OS2}$<br>$(I_{IN3} \times Gain_3) + I_{OS3}$ |

| 1      | 1      | 1      | 0      | $(I_{IN3} \times Gain_3) + I_{OS3}$                                                                               |

### Table 5. Oscillator Control

| ENABLE | OSCEN | OUTENR | OUTEN2 | OUTEN3 | OSCILLATOR |

|--------|-------|--------|--------|--------|------------|

| 0      | Х     | Х      | Х      | Х      | Off        |

| 1      | 0     | Х      | Х      | Х      | Off        |

| 1      | 1     | 1      | 1      | 1      | On         |

| 1      | 1     | 0      | Х      | Х      | On         |

| 1      | 1     | Х      | 0      | Х      | On         |

| 1      | 1     | Х      | Х      | 0      | On         |

### **APPLICATIONS**

The AD9662 uses the current at one or more of its three inputs—I<sub>INR</sub>, I<sub>IN2</sub>, and I<sub>IN3</sub>—and generates an output current proportional to the input currents. Channel R has a typical gain of 135 mA/mA, Channel 2 has a typical gain of 130 mA/mA, and Channel 3 has a typical gain of 260 mA/mA. The input impedance of Channel R and Channel 2 is typically 200  $\Omega$ , and the input impedance of Channel 3 is typically 100  $\Omega$ . In most cases, a voltage output DAC is used to set the dc current of these channels. A series resistor should be placed between each DAC's output and its respective input channel. These resistors should be chosen to properly scale the input current while not excessively loading the output of the DAC.

Channel R is used to provide bias current to the laser diode, and Channel 2 and Channel 3 are used to set the amplitudes of the current pulses that are required to write or erase the media. The output pulses are created by applying TTL level pulses to the channel enable pins while dc current is flowing into the input pins. Channel 2 and Channel 3 are turned on and off according to a predetermined write strategy (see Figure 14).

Due to the fast rise and fall time (<1 ns) required for the operation of higher speed drives, trace lengths carrying high speed signals, such as ENR, EN2, EN3, and the output current, should be kept as short as possible to minimize series inductance. A decoupling capacitor should be located near each  $V_{\rm CC}$  pin, and the ground return for the cathode of the laser diode should be kept as short as possible.

Rise time,  $t_r$ , is defined as the time a pulse requires to transition from 10% of its final value to 90% of its final value. Appropriately, fall time,  $t_f$ , is defined as the time a pulse requires to go from 90% of its initial value to 10% of its initial value.

Propagation delay is defined as the time when a transitioning logic signal reaches 50% of its amplitude to when the output current,  $I_{\rm OUT}$ , reaches 50% of its amplitude.

### **TEMPERATURE CONSIDERATIONS**

The AD9662 is in a 16-lead QSOP. JEDEC methods were used to determine the  $\theta_{JA}$  of the QSOP when mounted on a highly efficient thermally conductive test board (or 4-layer board). This board is made of FR4, is 1.60 mm thick, and consists of four copper layers. The two internal layers are solid copper (1 ounce/in<sup>2</sup> or 0.35 mm thick). The two surface layers (containing the component and back side traces) use 2 ounces/in<sup>2</sup> (0.70 mm thick) copper. This method of construction yields a  $\theta_{JA}$  for the AD9662 of approximately 105°C/W. An integrated circuit dissipating 500 mW and packaged in a QSOP, while operating in an ambient environment of 85°C, has an internal junction temperature of approximately 138°C.

$85^{\circ}C + 0.500 \text{ W} \times 105^{\circ}C/W = 138^{\circ}C$

This junction temperature is within the maximum recommended operating junction temperature of 150°C. Of course, this is not a realistic method for mounting a laser diode driver in an optical storage device. In an actual application, the laser diode driver would most likely be mounted to a flexible circuit board. The  $\theta_{JA}$  of a system is highly dependent on board layout and material. The user must consider these conditions carefully.

Some of the circuitry of the AD9662 can be used to monitor the internal junction temperature. The AD9662 uses diodes to protect it from electrostatic discharge (ESD). Every input pin has a diode between it and ground, with the anode connected to ground and the cathode connected to the particular input pin. The base-emitter junction of a PNP transistor is used for ESD protection from each pin to  $V_{CC}$ . The collector is electrically connected to the substrate of the die (see Figure 15). The base-emitter junction of this transistor can be used to monitor the internal die temperature of the IC.

Using a 10 V source at the enable pin to forward-bias the base-emitter junction and a 1 M $\Omega$  resistor to limit the current, a 2-point measurement can be used to calculate the junction temperature of the IC. Because the enable pin (ENABLE) needs to be a logic high for normal operation, the AD9662 can be operated with the 10 V applied through the 1 M $\Omega$  resistor.

The first point is obtained by measuring the voltage, V1, with  $I_{OUT} = 0$  immediately after the AD9662 is turned on. The case temperature, T1, can be measured using a thermocouple. The temperature of the case is measured immediately after the IC is turned on, and that temperature is the temperature of the transistor junction and of the die itself. Through characterization of the AD9662, it was determined that the forward-bias voltage of the base-emitter junction of the transistor decreases by 1.9 mV for every 1°C rise in junction temperature.

The second point of the 2-point measurement is obtained when the AD9662 is operated under load. IOUT is adjusted until the increase in supply current is 200 mA. The AD9662 is allowed to reach thermal equilibrium, and then the voltage, V2, is measured.

The voltage measurements taken with the IC running are lower than the actual base-emitter drop across the transistor due to the voltage drops across the internal resistance that is in series with the supply current (see Figure 15). This finite resistance was calculated to be approximately 120 m $\Omega$ . Therefore, for a supply current change of 200 mA, the  $\Delta V_{BE}$  calculation is 24 mV too low. Therefore, 24 mV must be added to the difference in measured voltages. The change in the base-emitter voltage is then calculated.

$$\Delta V_{BE} = (V2 + 24 \text{ mV} - V1)$$

The change in junction temperature can then be determined.

$$T_{J} = T1 + \Delta V_{BE}/(1.9 \text{ mV/°C})$$

$$I_{CC}$$

This 2-point measurement allows the rise in die temperature to be calculated for any given power dissipation. The  $\theta_{IA}$  of the

system can be calculated using the power dissipation of the LDD.

$$P_D = V_{CC} \times I_{CC} - V_{DIODE} \times I_{DIODE}$$

$$\theta_{\rm JA} = (T_J - T1)/P_D$$

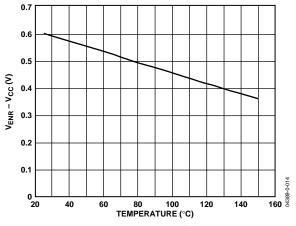

Figure 16 shows a graph of the measured voltage between ENR and  $V_{CC}$  ( $V_{ENR} - V_{CC}$ ) vs. the die temperature. This graph was constructed using a 2-layer evaluation board for the AD9662 (see Figure 17).

Using the preceding method, actual data was taken to determine the  $\theta_{JA}$  of the AD9662 in the evaluation board. Immediately after power-up, V1 was measured to be 593 mV. The supply current was 27 mA. The AD9662 was adjusted to deliver 200 mA into a 10  $\Omega$  load. This resulted in a total supply current of 244 mA. After allowing the part to reach thermal equilibrium, V2 measured 412 mV. The voltage drop across the 120 m $\Omega$  internal resistor due to the change in supply current was then calculated.

$(244 \text{ mA} - 27 \text{ mA}) \times 120 \text{ m}\Omega = 26 \text{ mV}$

This 26 mV internal voltage drop was then added to the measured voltage reduction to determine the actual  $\Delta V_{BE}$ .

$\Delta V_{BE} = (593 \text{ mV} - 412 \text{ mV} + 26 \text{ mV}) = 207 \text{ mV}$

The die temperature change measured 82.4°C. The output of the AD9662 was at a voltage of 2 V. The part dissipated an additional 600 mW of power (3 V × 200 mA). The  $\theta_{JA}$  for the AD9962 mounted on its 2-layer board was calculated to be: 600 mW/82.4°C = 137°C/W.

Figure 16. V<sub>ENR</sub> – V<sub>CC</sub> vs. Internal Temperature

### **EVALUATION BOARD**

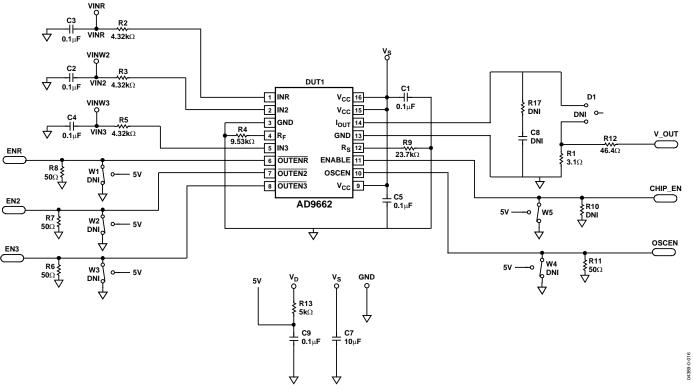

Figure 17. AD9662 QSOP-16 Evaluation Board Schematic

Note: If dc logic levels are desired on the enable pins, then Jumper W1 through Jumper W5 should be used, and Resistor R6 through Resistor R11 should not be installed. If the enable pins are driven from external signal sources, then these resistors should be installed, and the jumpers are not necessary.

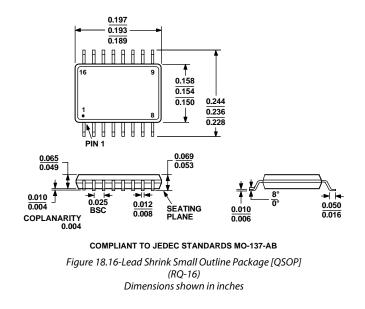

# **OUTLINE DIMENSIONS**

### **ORDERING GUIDE**

| Model                        | Temperature Range | Package Description | Package Option |

|------------------------------|-------------------|---------------------|----------------|

| AD9662ARQZ <sup>1</sup>      | 0°C to 85°C       | 16-Lead QSOP        | RQ-16          |

| AD9662ARQZ-REEL <sup>1</sup> | 0°C to 85°C       | 16-Lead QSOP        | RQ-16          |

| AD9662ARQZ-REEL71            | 0°C to 85°C       | 16-Lead QSOP        | RQ-16          |

$^{1}$  Z = Pb-free part.

# NOTES

# NOTES

### NOTES

$^{\odot}$  2005 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. C04389-0-11/05(C)

www.analog.com

Downloaded from Elcodis.com electronic components distributor