### **General Description**

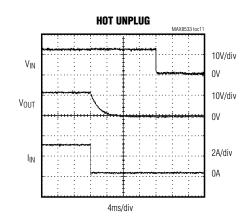

The MAX8533 is a single-port, 12V, Infiniband<sup>TM</sup>-compliant (IB) versatile hot-swap controller. The device can be implemented in both IB Class I (nonisolated) and Class II (isolated) power-topology applications. Additionally, the MAX8533 can be used as a reliable power controller on hot-swappable blade servers, RAID cards, and network switches or routers that are powered from a 12V bus.

The MAX8533 integrates several features that allow reliable insertion and removal of the circuit card, as well as real-time monitoring of abnormal occurrences. The MAX8533 allows for an adjustable soft-start ramp during turn-on of the input voltage, while providing overcurrent protection. It also provides accurate and consistent current-regulated outputs for a programmable period of time to latch off and soft-start in the presence of overcurrent conditions (OC). Additionally, it provides a second level of severe overcurrent (SOC) protection by responding to a dead short in 100ns. The MAX8533 also includes adjustable overvoltage protection.

The MAX8533 incorporates undervoltage lockout (UVLO) and a power-good (POK) signal to the DC-to-DC converters to confirm the status of output voltage rails during operation. Two enable inputs EN (logic enable) and LPEN (local power enable) provide flexible sequencing. The MAX8533 is specified across the extended temperature range and has an absolute maximum rating of 16V to withstand inductive kickback during board removal.

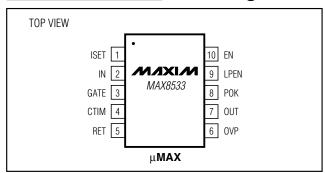

The MAX8533 is available in the space-saving 10-pin µMAX package.

## **Applications**

12V Hot-Swap

Infiniband Bulk Power

Hot-Swap/Plug/Dock Power Management

Blade Servers

**RAID**

Network Routers and Switches

#### Pin Configuration appears at end of data sheet.

Infiniband is a trademark of Infiniband<sup>SM</sup> Trade Association.

#### Features

- ♦ 12V Hot-Swap Controller for 25W or 50W **Infiniband Ports**

- **♦ Programmable Overcurrent Protection Regulation** Level

- ◆ EN and LPEN Inputs for Flexible Sequencing

- ♦ Power-Good Signal

- ♦ 16V Absolute Maximum Rating Withstands **Inductive Kickbacks**

- ♦ Soft-Start Overcurrent Protection During Turn-On

- ◆ Timed Current Regulation Period (Adjustable)

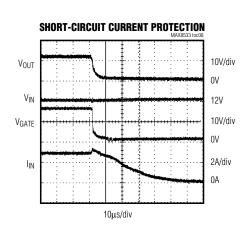

- ♦ 100ns IC Response Time to Output Dead Short

- **♦ Adjustable Overvoltage Protection**

- ♦ Undervoltage Lockout

- ♦ Adjustable Turn-On Ramp

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX8533EUB | -40°C to +85°C | 10 μMAX     |

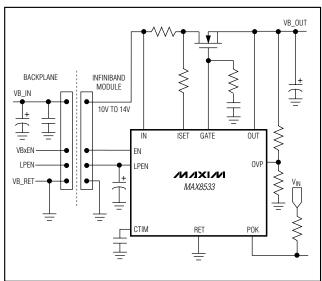

## Typical Operating Circuit

MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, POK to RET                           | 0.3V to (V <sub>IN</sub> + 7V)<br>-0.3V to (V <sub>IN</sub> + 0.3V)<br> | Operating Temperature Range | +150°C<br>+150°C to +150°C |

|------------------------------------------|-------------------------------------------------------------------------|-----------------------------|----------------------------|

| 10-Pin µiviax (derate 5.6 miv/ C above + | 70°C)444.4 IIIW                                                         |                             |                            |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +12V, V_{EN} = 0, T_A = 0$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                                   | CONDITIONS                                                                                                              | MIN                 | TYP                 | MAX  | UNITS |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|------|-------|

| VB BULK SUPPLY CONTROL                      |                                                                                                                         |                     |                     |      | •     |

| IN Supply Voltage Range                     |                                                                                                                         | 10                  | 12                  | 14   | V     |

| ISET Current Source                         |                                                                                                                         | 18.5                | 20                  | 21.5 | μΑ    |

| Current-Limit Offset Voltage                | VISET - VIN                                                                                                             | -4                  | 0                   | +4   | mV    |

| OUT Input Current                           | V <sub>OUT</sub> = 12V                                                                                                  |                     | 6                   | 12   | μΑ    |

| Severe Overcurrent Threshold                | With respect to current regulation threshold                                                                            |                     | 150                 |      | mV    |

| 25W OUT Current Regulation                  | RISET = $3.09$ k $\Omega$ $\pm 1$ %, RSENSE = $20$ m $\Omega$ $\pm 1$ %                                                 | 2.6                 | 3.1                 | 3.6  | Α     |

| 50W OUT Current Regulation                  | RISET = $3.09$ k $\Omega$ $\pm 1$ %, RSENSE = $10$ m $\Omega$ $\pm 1$ %                                                 | 5.2                 | 6.2                 | 7.2  | Α     |

| GATE PARAMETERS                             |                                                                                                                         |                     |                     |      |       |

| Gate Response Time to Severe<br>Overcurrent | V <sub>RSENSE</sub> ≥ (150mV + current regulation threshold + 50mV) until V <sub>GATE</sub> begins to slew low (Note 1) |                     | 100                 |      | ns    |

| Gate Response Time to<br>Overcurrent        | V <sub>RSENSE</sub> ≥ current regulation threshold + 50mV until V <sub>GATE</sub> begins to slew low (Note 1)           |                     | 600                 |      | ns    |

| Gate Turn-On Current                        |                                                                                                                         | 8.4                 | 10                  | 11.6 | μΑ    |

| Gate Pulldown Current                       | Overcurrent, V <sub>RSENSE</sub> ≥ (current regulation threshold + 100mV) (Note 1)                                      |                     | 2.7                 |      | mA    |

|                                             | Severe overcurrent                                                                                                      |                     | 350                 |      | 1     |

| Gate High Voltage                           |                                                                                                                         | V <sub>IN</sub> + 4 | V <sub>IN</sub> + 5 |      | V     |

| IN PARAMETERS                               |                                                                                                                         |                     |                     |      |       |

| Quiescent Supply Current                    |                                                                                                                         |                     | 1.5                 | 3    | mA    |

| IN UVLO Threshold                           | Hysteresis = 300mV                                                                                                      | 7.5                 | 8.4                 | 9.0  | V     |

| POK Undervoltage Threshold                  | Measured at OUT, rising edge, hysteresis = 300mV                                                                        | 9.2                 | 9.6                 | 10.0 | V     |

| POK Delay                                   | V <sub>POK</sub> rising                                                                                                 | 100                 | 220                 | 350  | μs    |

| POK Output Voltage                          | V <sub>OUT</sub> < 9.2V, I <sub>POK</sub> = 1.6mA                                                                       |                     | 0.1                 | 0.25 | V     |

| POK Leakage Current                         | V <sub>OUT</sub> > 10V, V <sub>POK</sub> = 14V                                                                          |                     | 0.1                 | 1    | μΑ    |

| EN Rising Threshold                         | Hysteresis = 120mV                                                                                                      | 1.3                 | 1.65                | 2.0  | V     |

| EN Pullup Voltage                           | EN unconnected                                                                                                          | 4.5                 | 5.5                 |      | V     |

| EN Pullup Current                           |                                                                                                                         | 12                  | 20                  | 28   | μΑ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +12V, V_{EN} = 0, T_A = 0$ °C to +85°C, unless otherwise noted. Typical values are at  $T_A = +25$ °C.)

| PARAMETER                               | CONDITIONS                                 | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|--------------------------------------------|------|------|------|-------|

| LPEN Rising Threshold                   | Hysteresis = 120mV                         | 1.3  | 1.65 | 2.0  | V     |

| LPEN Pullup Voltage                     | LPEN unconnected                           | 4.5  | 5.5  |      | V     |

| LPEN Pullup Current                     |                                            | 12   | 20   | 28   | μΑ    |

| OVP Threshold Voltage                   | Hysteresis = 10mV, V <sub>OVP</sub> rising | 1.96 | 2.00 | 2.04 | V     |

| OVP Fault Timeout                       |                                            |      | 1.5  |      | ms    |

| CTIM PARAMETERS                         | CTIM PARAMETERS                            |      |      |      |       |

| CTIM Charging Current                   | V <sub>CTIM</sub> < 1.5V                   | 16   | 20   | 24   | μΑ    |

| CTIM Fault Pullup Current               | V <sub>CTIM</sub> = 6V                     | 6    | 8    | 12   | mA    |

| Current-Limit Timeout Threshold Voltage |                                            | 1.5  | 1.8  | 2.1  | V     |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = +12V, V_{EN} = 0, T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                    | CONDITIONS                                                         | MIN                 | TYP | MAX  | UNITS |

|------------------------------|--------------------------------------------------------------------|---------------------|-----|------|-------|

| VB BULK SUPPLY CONTROL       |                                                                    |                     |     |      |       |

| IN Supply Voltage Range      |                                                                    | 10                  |     | 14   | V     |

| ISET Current Source          | Current regulation threshold = ISET x RISET                        | 18                  |     | 22   | μΑ    |

| Current-Limit Offset Voltage | VISET - VIN                                                        | -4                  |     | +4   | mV    |

| OUT Input Current            | $V_{OUT} = 12V$                                                    |                     |     | 12   | μA    |

| 25W OUT Current Regulation   | $R_{ISET} = 3.09k\Omega \pm 1\%$ , $R_{SENSE} = 20m\Omega \pm 1\%$ | 2.5                 |     | 3.7  | А     |

| 50W OUT Current Regulation   | $R_{ISET} = 3.09k\Omega \pm 1\%$ , $R_{SENSE} = 10m\Omega \pm 1\%$ | 5.0                 |     | 7.4  | А     |

| GATE PARAMETERS              |                                                                    |                     |     |      |       |

| Gate Turn-On Current         |                                                                    | 8                   |     | 12   | μΑ    |

| Gate High Voltage            |                                                                    | V <sub>IN</sub> + 4 |     |      | V     |

| IN PARAMETERS                |                                                                    |                     |     |      |       |

| Quiescent Supply Current     |                                                                    |                     |     | 3    | mA    |

| IN UVLO Threshold            | Hysteresis = 300mV                                                 | 7.5                 |     | 9.0  | V     |

| POK Undervoltage Threshold   | Measured at OUT, rising edge, hysteresis = 300mV                   | 9.0                 |     | 10.2 | V     |

| POK Delay                    | V <sub>POK</sub> rising                                            | 100                 |     | 350  | μs    |

| POK Output Voltage           | $V_{OUT} < 9.2V$ , $I_{POK} = 1.6mA$                               |                     |     | 0.25 | V     |

| POK Leakage Current          | $V_{OUT} > 10V$ , $V_{POK} = 14V$                                  |                     |     | 1    | μΑ    |

| EN Rising Threshold          | Hysteresis = 120mV                                                 | 1.3                 |     | 2.0  | V     |

| EN Pullup Voltage            | EN unconnected                                                     | 4.5                 |     |      | V     |

| EN Pullup Current            |                                                                    | 12                  |     | 28   | μΑ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = +12V, V_{EN} = 0, T_A = -40$ °C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                               | CONDITIONS                                 | MIN  | TYP | MAX  | UNITS |  |

|-----------------------------------------|--------------------------------------------|------|-----|------|-------|--|

| LPEN Rising Threshold                   | Hysteresis = 120mV                         | 1.3  |     | 2.0  | V     |  |

| LPEN Pullup Voltage                     | LPEN unconnected                           | 4.5  |     |      | V     |  |

| LPEN Pullup Current                     |                                            | 12   |     | 28   | μΑ    |  |

| OVP Threshold Voltage                   | Hysteresis = 10mV, V <sub>OVP</sub> rising | 1.96 |     | 2.04 | V     |  |

| CTIM PARAMETERS                         | CTIM PARAMETERS                            |      |     |      |       |  |

| CTIM Charging Current                   | V <sub>CTIM</sub> < 1.5V                   | 15   |     | 25   | μΑ    |  |

| CTIM Fault Pullup Current               | V <sub>CTIM</sub> = 6V                     | 6    |     | 12   | mA    |  |

| Current-Limit Timeout Threshold Voltage |                                            | 1.4  |     | 2.2  | V     |  |

Note 1: The current regulation threshold is set by R3 (Figure 2). It is equal to 20µA x R3.

Note 2: Specifications to -40°C are guaranteed by design and not production tested.

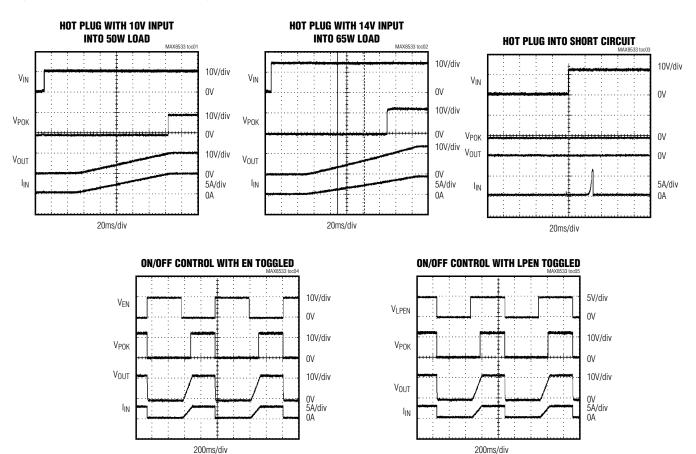

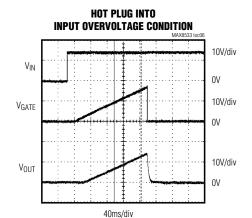

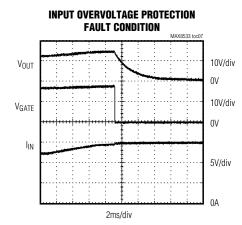

## Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ISET | Current-Limit Threshold Programming Input. Connect to the low side of the current-limit threshold programming resistor.                                                                                                                                                                                                                                                                      |

| 2   | IN   | Bulk Power Supply. Connect to the input power supply and positive terminal of the current-sense resistor.                                                                                                                                                                                                                                                                                    |

| 3   | GATE | External MOSFET-Gate-Drive Output. Connect to the gate of the external N-channel MOSFET. A series resistor and capacitor connected from GATE to RET sets the turn-on ramp rate. At turn-on, this capacitor is charged to V <sub>IN</sub> + 5V (typ) by an internal current source. GATE is pulled to RET when EN is high and/or LPEN is low. GATE is pulled to RET during a fault condition. |

| 4   | CTIM | Current Regulation Time Programming Input. Connect a capacitor from CTIM to RET. The capacitance at CTIM determines the time delay between an overcurrent event and chip output shutdown (current-limit timeout). CTIM is pulled low, resetting the fault latch when either EN is high or LPEN is low.                                                                                       |

| 5   | RET  | Bulk Power Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 6   | OVP  | Overvoltage Protection Input. Connect to common point of a resistor-divider from OUT to RET. GATE pulls low when V <sub>OVP</sub> exceeds the 2V threshold for at least 1.5ms and the IC is latched off.                                                                                                                                                                                     |

| 7   | OUT  | Output Voltage. Connect to the output of the circuit.                                                                                                                                                                                                                                                                                                                                        |

| 8   | POK  | Power-Good Output. POK is an open-drain output that becomes high impedance when V <sub>OUT</sub> reaches 9.6V. Pull POK up to the supply rail using an external pullup resistor. POK is pulled to RET until the MAX8533 is enabled.                                                                                                                                                          |

| 9   | LPEN | Local Power-Enable Input. LPEN is a positive-assertion enable input to turn on the IC. Pull LPEN low to disable the output. LPEN has an internal pullup to 5V.                                                                                                                                                                                                                               |

| 10  | EN   | Chip-Enable Input. EN is an active-low input that enables the IC.                                                                                                                                                                                                                                                                                                                            |

## **Detailed Description**

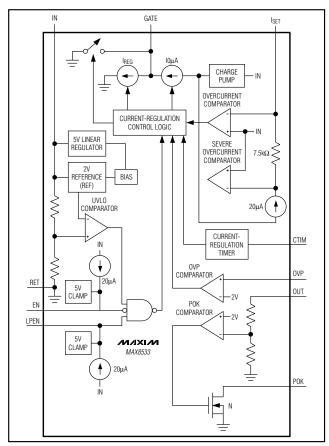

The MAX8533 is a single-port, 12V, IB-compliant versatile hot-swap controller IC designed for applications where a line card is inserted into a live backplane. The MAX8533 can be implemented in both IB Class I (nonisolated) and Class II (isolated) power-topology applications. Normally, when a line card is plugged into a live backplane, the low impedance of the card's discharged filter capacitors can momentarily collapse the input supply voltage. The MAX8533 is designed to reside on the line card and to provide inrush current-limiting and short-circuit protection. This is achieved using an external N-channel MOSFET, current-sense resistor, and current-limit set resistor, along with two on-chip comparators (Figure 1).

#### **UVLO** and Startup

The MAX8533 has an undervoltage lockout protection circuit. The circuit is disabled when  $V_{\text{IN}}$  is below 8.4V (typ). The gate of the MOSFET, CTIM, LPEN, and POK is pulled to RET until  $V_{\text{IN}}$  exceeds the UVLO threshold.

Once  $V_{\text{IN}}$  exceeds the UVLO threshold and LPEN and EN are enabled, the capacitor on the gate of the external MOSFET is charged and the MOSFET turns on. The charging of this capacitor provides soft-start to prevent high inrush currents.

#### **On/Off Control**

The MAX8533 is enabled/disabled using LPEN and EN. Drive EN low and LPEN high to enable the device. LPEN can also be left unconnected as it is internally connected to 5V. Drive LPEN low or EN high to disable the output. Table 1 is the truth table for these inputs.

Table 1. Truth Table

| EN | LPEN | OUTPUT |

|----|------|--------|

| 0  | 0    | OFF    |

| 0  | 1    | ON     |

| 1  | 0    | OFF    |

| 1  | 1    | OFF    |

Zero is a logic-low input, 1 is a logic-high input or unconnected input

#### Startup Into Load

The MAX8533 is intended to be used in a circuit where no load is applied until the POK signal is enabled. In an application where the load is applied during the output-voltage ramp up, the RDS(ON) of the MOSFET is higher and the power dissipated by the MOSFET is larger. Repeated, rapid hot-swaps into a load can create sufficient heat to exceed the power-dissipation limits of the package causing failure of the MOSFET.

## \_Applications Information

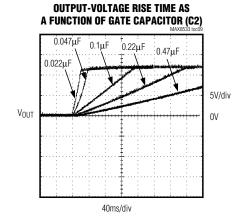

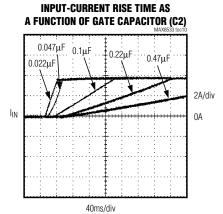

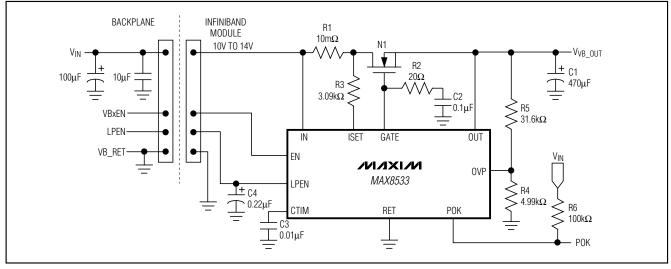

#### **Setting the Turn-On Ramp Rate**

The MOSFET turn-on ramp rate is determined by the capacitor (C2) at GATE (Figure 2). An internal  $10\mu A$  current source charges C2 to bring GATE high. The soft-start rate is determined as follows:

$$tss = C2 \times (V_{IN} + 5)/(10 \times 10^{-6})$$

tss may be longer than expected in the application depending on the gate capacitance of the external MOSFET. The necessary gate voltage is provided by an on-board charge pump that boosts the voltage at GATE to  $(V_{IN} + 5V)$ .

#### **External Power MOSFET Selection**

Select the N-channel MOSFET according to the application's current requirements. Table 2 lists some recommended components. The MOSFET's on-resistance (RDS(ON)) should be chosen low enough to have a minimal voltage drop at full load to limit the MOSFET power dissipation. High RDS(ON) can cause high output ripple if the board has pulsing loads, or trigger an external

Figure 1. MAX8533 Functional Diagram

Figure 2. Typical 50W Applications Circuit

Table 2. External Component List for 50W Output

| REF<br>DESIGNATOR | DESCRIPTION                                   | MANUFACTURER PART NO.        |

|-------------------|-----------------------------------------------|------------------------------|

| C1                | 470μF, 25V aluminum electrolytic capacitor    | Sanyo<br>25MV470HC           |

| C2                | 0.1µF ±10%, 25V X5R ceramic capacitor         | Taiyo Yuden<br>TMK107BJ104KA |

| C3                | 0.01µF ±20% X7R ceramic capacitor             | Kemet<br>C0606C103M4RAC      |

| C4                | 0.22µF ±10%, 25V X5R ceramic capacitor        | TDK<br>C1608X5R1A224K        |

| R1*               | 10m $\Omega$ ±1%, 0.5W current-sense resistor | Dale<br>LRF1206-01-R010-F    |

| R2                | 20Ω ±5% resistor                              | Panasonic                    |

| R3                | $3.09$ k $\Omega$ ±1% resistor                | Panasonic                    |

| R4                | $4.99$ k $\Omega$ $\pm 1\%$ resistor          | Panasonic                    |

| R5                | 31.6k $\Omega$ ±1% resistor                   | Panasonic                    |

| N1                | N-channel MOSFET, 30V, 6m $\Omega$            | Siliconix<br>Si4842DY        |

<sup>\*</sup>Use a  $20m\Omega$  ±1%, 0.25W current-sense resistor for 25W applications.

undervoltage reset monitor at full load. The maximum gate voltage ( $V_{GS}$ ) rating must be at least  $\pm 20V$ . Low MOSFET gate capacitance is not necessary for the inrush current limiting because it is achieved by limiting the GATE dV/dt. However, higher gate capacitance increases the turn-off time of the MOSFET under fault conditions.

#### **Current-Limit and Overload Protection**

The MAX8533 features a dual overcurrent protection circuit that turns off the MOSFET in overcurrent situations. When an overload event is sensed, the IC limits the current to a level set by ISET. Continuous overload for a period set by the user (tctim) latches off the MOSFET. The severe overcurrent protection immediately shuts down the external MOSFET and latches it off.

R3 sets the current-limit threshold voltage. This voltage is generated from an internal  $20\mu A$  source driven through R3. Therefore:

$$V_{ILIM} = R3 \times 20 \mu A$$

The current-sense signal is sensed across resistor R1. With no load, the voltage at ISET is the input voltage

plus VILIM. As the load current increases, the voltage drop across R1 increases and reduces the voltage at ISET. Once VISET is lower than VIN, the overcurrent comparator (Figure 1) is tripped and the MAX8533 enters current regulation mode. During current regulation mode, the gate voltage of the MOSFET is decreased to limit the current to the output. The maximum time period for the current regulation mode is set by the external capacitor at CTIM (C3). This feature allows transient currents that exceed the current limit to pass without shutting down the circuit. The current regulation time period is determined as:

$$t_{IREG} = C3 \times (1.8V/20\mu A)$$

If tIREG expires and the overcurrent condition still exists, the MOSFET is latched off.

The severe overcurrent comparator (Figure 1) trips if the drop across the current-sense resistor (R1) is 150mV higher than the current-limit threshold (V<sub>IN</sub> exceeds V<sub>ISET</sub> by 150mV). During a severe overcurrent event, the gate of the external MOSFET is pulled down with a 350mA current source and latched immediately.

Toggle EN, LPEN, or input power to clear the latched fault condition.

#### **Overvoltage Protection**

The MAX8533 has an adjustable overvoltage protection feature that latches the IC off in case of an overvoltage event. An external resistor-divider (R4 and R5, Figure 2) from OUT to RET with OVP connected to the center, sets the overvoltage threshold. Use  $4.99k\Omega$  for R4. R5 is determined using the following equation:

$$R5 = 4.99 \times 10^3 \times ((V_{OVT} / V_{OVP}) - 1)$$

VOVT is the desired overvoltage threshold and VOVP is 2V (typ). OVP latches off the MAX8533 if an overvoltage condition exists for 1.5ms. Toggle EN, LPEN, or input power to clear the latched fault condition.

#### **Fault Reset**

Overcurrent, severe overcurrent, and overvoltage conditions result in the MAX8533 entering a latched fault condition. Toggle LPEN, EN, or input power to reset the latched fault condition and return to normal operation.

#### **Power-Good Output (POK)**

POK is an open-drain output used to enable the onboard DC-to-DC converter. The POK output turns high impedance when the output rail reaches 9.6V. POK must be pulled up to the user's logic level using a pullup resistor.

## **PC Board Layout Guidelines**

To take advantage of the switch response time to an output fault condition, keep all traces as short as possible and maximize the high-current trace width to reduce the effect of undesirable parasitic inductance. The MOSFET dissipates a fair amount of heat due to the high currents involved, especially during an overcurrent condition. In order to dissipate the heat generated by the MOSFET, make the power traces very wide with a large amount of copper area. A more efficient way to achieve good power dissipation on a surface-mount package is to lay out two copper pads directly under the MOSFET package on both sides of the board. Connect the two pads to the ground plane through vias, and use enlarged copper mounting pads on the top side of the board.

Minimize the current-sense resistor trace length (<10mm), and ensure accurate current sensing with Kelvin connections. Place capacitor CTIM as close as possible to the IC. The traces from the current-sense resistor to IN and ISET should be as short as possible for accurate current sensing. Place the MAX8533 circuit as close as possible to the backplane connector. A sample PC board layout is available in the MAX8533 Evaluation Kit.

## **Pin Configuration**

## **Chip Information**

TRANSISTOR COUNT: 2541

PROCESS: BICMOS

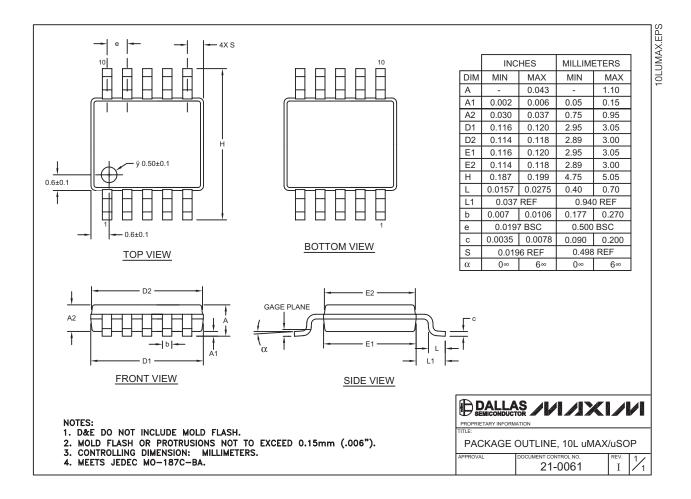

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

10 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.