# **MM5486 LED Display Driver**

# **General Description**

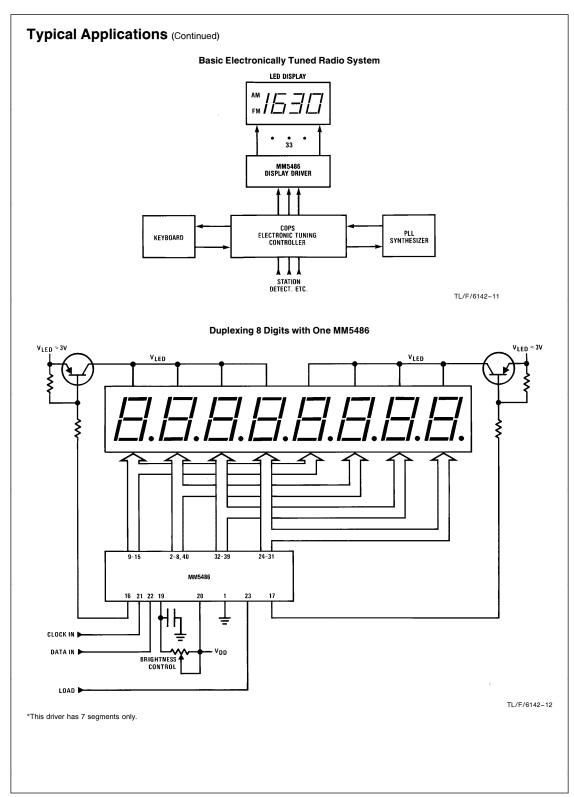

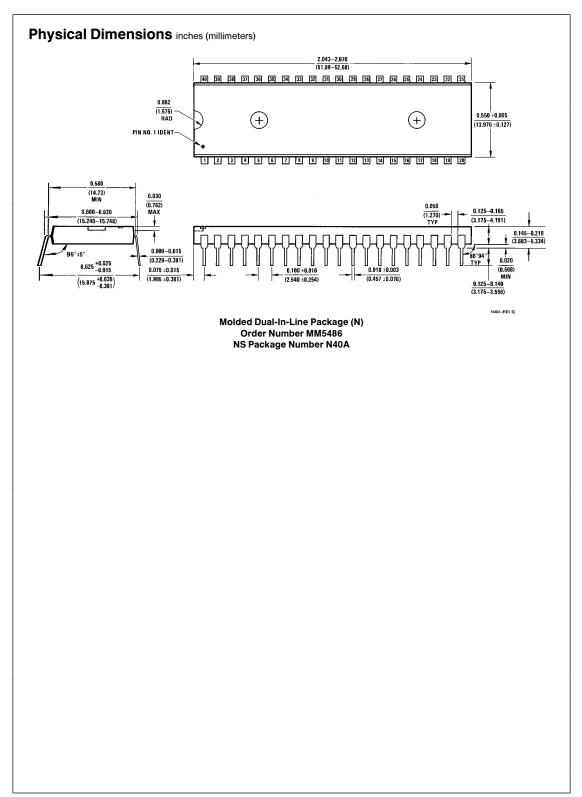

The MM5486 is a monolithic MOS integrated circuit utilizing N-channel metal-gate low-threshold, enhancement mode and ion-implanted depletion mode devices. It is available in a 40-pin molded dual-in-line package. The MM5486 is designed to drive common anode-separate cathode LED displays. A single pin controls the LED display brightness by setting a reference current through a variable resistor connected to  $\mbox{V}_{\mbox{DD}}$ .

#### **Features**

- Continuous brightness control

- Serial data input/outut

- External load input

- Cascaded operation capability

- Wide power supply operation

- TTL compatibility

- 33 outputs, 15 mA sink capability

- Alphanumeric capability

# **Applications**

- COPS™ or microprocessor displays

- Industrial control indicator

- Relay driver

- Digital clock, thermometer, counter, voltmeter

- Instrumentation readouts

#### **Block and Connection Diagrams Dual-In-Line Package** OUTPUT 33 OUTPUT 1 OUTPUT BIT 17 OUTPUT RIT 16 - OUTPUT RIT 18 OUTPUT BIT 15 OUTPUT BIT 19 33 OUTPUT BUFFERS OUTPUT BIT 14 OUTPUT BIT 20 DUTPUT RIT 13 - OUTPUT BIT 21 LOAD 33 LATCHES OUTPUT BIT 22 OUTPUT BIT 11 OUTPUT BIT 23 33-BIT SHIFT REGISTER OUTPUT BIT 10 - OUTPUT BIT 24 OUTPUT BIT 8 -- OUTPUT BIT 26 OUTPUT BIT 7 -- OUTPUT BIT 27 Ţ OUTPUT RIT 5 OUTPUT RIT 29 TI /F/6142-1 OUTPUT BIT 4 -- OUTPUT BIT 30 FIGURE 1 OUTPUT BIT 3 OUTPUT BIT 31 OUTPUT BIT 2 -OUTPUT BIT 32 T BIT 17 F BIT 18 BIT 20 BIT 21 OUTPUT BIT 1 OUTPUT BIT 33 DATA OUT -- LOAD OUTPUT BIT OUTPUT BIT BRIGHTNESS CONTROL - DATA IN OUTPUT OUTPUT OUTPUT DUTPUT CLOCK IN VDD ss Vss TL/F/6142-2 **Top View** OUTPUT BIT 12 OUTPUT BIT 22 Order Number MM5486N OUTPUT BIT 11 OUTPUT BIT 23 See NS Package Number N40A OUTPUT BIT 10 OUTPUT BIT 24 OUTPUT BIT 9 OUTPUT BIT 25 FIGURE 2 OUTPUT BIT 8 - OUTPUT BIT 26 N/C MM5486V **-** N/C OUTPUT BIT 7 OUTPUT BIT 27 OUTPUT BIT 6 OUTPUT BIT 28 OUTPUT BIT 5 OUTPUT BIT 4 OUTPUT BIT 30 OUTPUT BIT 3 OUTPUT BIT 31 DATA OUT — BRIGHTNESS CONTROL — Vbb — N/C — BIT 33 -LOAD OUTPUT TL/F/6142-13 **Order Number MM5486V** See NS Package Number V44A COPS™ is a trademark of National Semiconductor Corporation

©1995 National Semiconductor Corporation TL/F/6142

RRD-B30M105/Printed in U. S. A.

# **Absolute Maximum Ratings**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Voltage at Any Pin  $V_{SS}$  to  $V_{SS}+12V$ Operating Temperature  $-25^{\circ}$ C to  $+85^{\circ}$ C Storage Temperature  $-65^{\circ}$ C to  $+150^{\circ}$ C Power Dissipation at 25°C

Molded DIP Package, Board Mount

Molded DIP Package, Socket Mount

2.5W\*

2.3W\*\*

Junction Temperature

+ 150°C

Lead Temperature (Soldering, 10 seconds) 300°C  $^*$ Molded DIP Package, Board Mount,  $\theta_{\rm JA}=49^{\circ}$ C/W, Derate 20.4 mW/°C above 25°C.

\*\*Molded DIP Package, Socket Mount,  $\theta_{\rm JA}=54^{\circ}{\rm C/W}$ , Derate 18.5 mW/°C above 25°C.

# **Electrical Characteristics**

$T_A$  within operating range,  $V_{DD}=4.75V$  to 11.0V,  $V_{SS}=0V$ , unless otherwise specified

| Symbol                                             | Parameter                                             | Conditions                                                                                       | Min                               | Тур | Max                    | Units           |

|----------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|-----|------------------------|-----------------|

| $V_{DD}$                                           | Power Supply                                          |                                                                                                  | 4.75                              |     | 11                     | ٧               |

| I <sub>DD</sub>                                    | Power Supply Current                                  | Excluding Output Loads                                                                           |                                   |     | 7                      | mA              |

| V <sub>IL</sub><br>V <sub>IH</sub>                 | Input Voltages<br>Logic "0" Level<br>Logic "1" Level  | $\pm$ 10 $\mu A$ Input Bias $4.75 \leq V_{DD} \leq 5.25$ $V_{DD} > 5.25$                         | -0.3<br>2.2<br>V <sub>DD</sub> -2 |     | 0.8<br>V <sub>DD</sub> | V<br>V          |

| I <sub>BR</sub>                                    | Brightness Input (Note 2)                             |                                                                                                  | 0                                 |     | 0.75                   | mA              |

| I <sub>OH</sub><br>I <sub>OL</sub>                 | Output Sink Current (Note 3) Segment OFF Segment ON   | V <sub>OUT</sub> = 3.0V<br>V <sub>OUT</sub> = 1V (Note 4)                                        |                                   |     | 10                     | μΑ              |

|                                                    |                                                       | Brightness Input = $0 \mu A$<br>Brightness Input = $100 \mu A$<br>Brightness Input = $750 \mu A$ | 0<br>2.0<br>15                    | 2.7 | 10<br>4<br>25          | μA<br>mA<br>mA  |

| Io                                                 | Maximum Segment Current                               |                                                                                                  |                                   |     | 40                     | mA              |

| V <sub>IBR</sub>                                   | Brightness Input Voltage (Pin 19)                     | Input Current = 750 μA                                                                           | 3.0                               |     | 4.3                    | ٧               |

| ОМ                                                 | Output Matching (Note 1)                              |                                                                                                  |                                   |     | ±20                    | %               |

| V <sub>OL</sub><br>V <sub>OH</sub>                 | Data Output<br>Logical "0" Level<br>Logical "1" Level | $I_{OUT}=0.5 \text{ mA}$ $I_{OUT}=100 \mu \text{A}$                                              | V <sub>SS</sub> 2.4               |     | 0.4<br>V <sub>DD</sub> | V<br>V          |

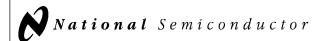

| f <sub>C</sub><br>t <sub>h</sub><br>t <sub>l</sub> | Clock Input<br>Frequency<br>High Time<br>Low Time     | (Notes 5 and 6)                                                                                  | 950<br>950                        |     | 500                    | kHz<br>ns<br>ns |

| t <sub>DS</sub>                                    | Data Input<br>Set-Up Time<br>Hold Time                |                                                                                                  | 300<br>300                        |     |                        | ns<br>ns        |

Note 1: Output matching is calculated as the percent variation  $(I_{MAX} + I_{MIN})/2$ .

Note 2: With a fixed resistor on the brightness input pin, some variation in brightness will occur from one device to another. Maximum brightness input current can be 2 mA as long as Note 3 and junction temperature equation are complied with.

Note 3: Absolute maximum for each output should be limited to 40 mA.

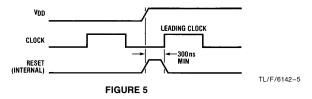

$\textbf{Note 4:} \ \text{The V}_{\text{OUT}} \ \text{voltage should be regulated by the user. See} \ \textit{Figures 6} \ \text{and 7 for allowable V}_{\text{OUT}} \ \text{vs I}_{\text{OUT}} \ \text{operation.}$

Note 5: AC input waveform specification for test purpose:  $t_f \le$  20 ns,  $t_f \le$  20 ns,  $t_f =$  500 kHz, 50%  $\pm$ 10% duty cycle.

Note 6: Clock input rise and fall times must not exceed 300 ns.

#### **Functional Description**

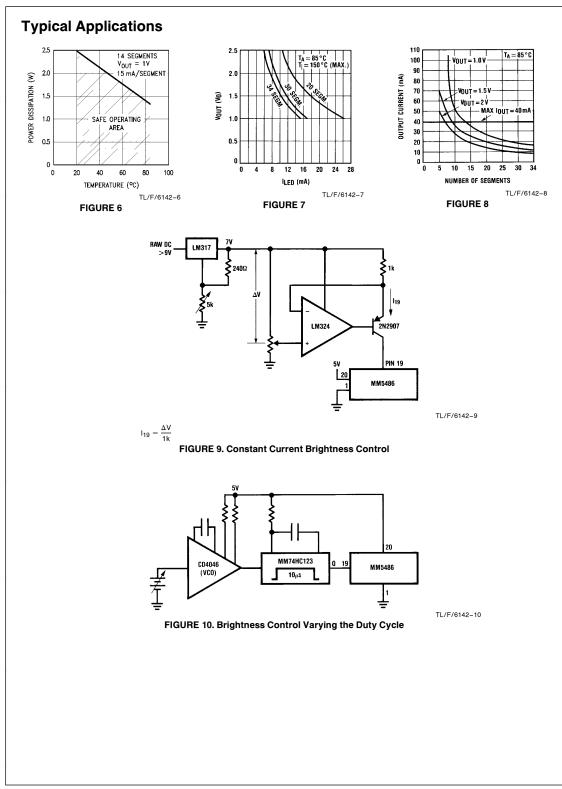

The MM5486 is specifically designed to operate four-digit alphanumeric displays with minimal interface with the display and the data source. Serial data transfer from the data source to the display driver is accomplished with 3 signals, serial data, clock, and load. The data bits are latched by a positive-level load signal, thus providing non-multiplexed, direct drive to the display. When load is high, the data in the shift registers is displayed on the output drivers. Outputs change only if the serial data bits differ from the previous time. Display brightness is determined by control of the output current for LED displays. A 0.001  $\mu\text{F}$  capacitor should be connected to brightness control, pin 19, to prevent possible oscillations. The output current is typically 20 times greater than the current into pin 19, which is set by an external variable resistor. There is an internal limiting resistor of 400 $\Omega$  nominal value.

A block diagram is shown in Figure 1.

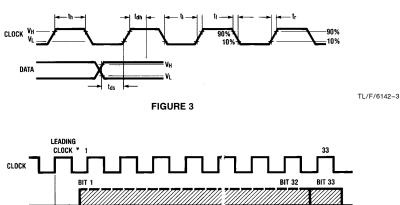

Figure 4 shows the input data format. Bit "1" is the first bit into the data input pin and it will appear on pin 17. A logical "1" at the input will turn on the appropriate LED. The load signal latches the 33 bits of the shift register into the latches. The data out pin allows for cascading the shift registers for more than 33 output drivers.

When the chip first powers ON, an internal power ON reset signal is generated which resets all registers and latches. The leading clock returns the chip to its normal operation.

Figure 3 shows the timing relationship between data, clock and data enable. A maximum clock frequency of 0.5 MHz is assumed.

For applications where a lesser number of outputs are used, it is possible to either increase the current per output, or operate the part at higher than 1V V<sub>OUT</sub>. The following equation can be used for calculations:

$T_{J} = (V_{OUT}) (I_{LED})$  (No. of segments)  $(\theta_{JA}) + T_{A}$  where:

$T_J$  = junction temperature, 150°C max.

$V_{OUT}$  = the voltage at the LED driver outputs

I<sub>LED</sub> = the LED current

$\theta_{JA}$  = thermal coefficient of the package

T<sub>A</sub> = ambient temperature

$\theta_{JA}$  (Socket Mount) = 54°C/W

$\theta_{JA}$  (Board Mount) = 49°C/W

The above equation was used to plot Figure 6, Figure 7, and Figure 8

TL/F/6142-4

LOAD BIT 1 BIT 33

LOAD RESET (INTERNAL)

\*This leading clock is necessary only after power ON.

FIGURE 4. Input Data Format

#### Physical Dimensions inches (millimeters) (Continued) +0.006 0.650 -0.000 +0.15 16.51 0 0.017±0.004 [0.43±0.10] TYP 45°X 0.045 PIN 1 IDENT 45°X 0.045 [1.14] 1 44 0.029±0.003 11 TYP [0.74±0.08] 0.610±0.020 [15.49±0.51] SEATING PLANE 18 28 0.020 [0.51] MIN TYP [1.27] TYP 0.690-0.005 [17.53-0.13] 0.105±0.015 [2.67±0.38] TYP 0.500 [12.70] TYP 0.165-0.180 [4.19-4.57] TYP

44-Lead Plastic Chip Carrier (V) Order Number MM5486V NS Package Number V44A

0.004[0.10]

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwgs@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (652) 2737-1600 Fax: (652) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408

V44A (REV K)

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications