# Converting from CY14E256L/STK14C88 to CY14E256LA

# AN55663

Author: Ravi Prakash

Associated Part Family: CY14E256L/STK14C88

CY14E256LA

Associated Application Notes: None

# **Application Note Abstract**

This application note provides information for converting from CY14E256L/STK14C88 parts to the CY14E256LA. It lists the parameter differences between the parts and the design considerations when converting existing applications from CY14E256L/STK14C88 to CY14E256LA.

#### Introduction

Cypress CY14E256LA is a 5V, 32Kb x 8, 256 Kbit nvSRAM in 0.13u technology. This part is functionally equivalent to CY14E256L/STK14C88 (0.8u) and is intended as a drop in replacement. (STK14C88 is the Simtek part number for CY14E256L.) This application note highlights the differences between the CY14E256L/STK14C88 and the CY14E256LA and the parameters of significance that must be considered while migrating.

#### **Overview**

The following tables compare the features and parameters of the two parts. As shown in Table 1, the 256 Kbit nvSRAM is available in x8 configuration.

Table 1. Part Number Description

| Description | Original<br>Part Number | Replacement<br>Part Number |

|-------------|-------------------------|----------------------------|

| 32Kb x 8    | CY14E256L/STK14C88      | CY14E256LA                 |

#### **Feature Set**

Both parts share the same overall feature set and are available in the operation speed bins as follows.

Table 2. Feature Set Comparison

| Feature Set                 | CY14E256L/<br>STK14C88 | CY14E256LA    |

|-----------------------------|------------------------|---------------|

| AutoStore                   | Available              | Available     |

| Software STORE              | Available              | Available     |

| Hardware STORE              | Available              | Available     |

| Software RECALL             | Available              | Available     |

| AutoStore Inhibit           | Available              | Not Available |

| AutoStore<br>Enable/Disable | Not Available          | Available     |

| Feature Set                   | Feature Set CY14E256L/<br>STK14C88 |                  |

|-------------------------------|------------------------------------|------------------|

|                               | 25 ns                              | 25 ns            |

| Speed                         | 35 ns<br>45 ns                     | -<br>45 ns       |

| STORE Cycles                  | 1,000,000                          | 200,000          |

| Data Retention 100 years at 5 |                                    | 20 years at 85°C |

#### **Operating Temperature Range**

While CY14E256L/STK14C88 is available in both Commercial and Industrial temperature ranges, CY14E256LA is offered only in the Industrial temperature range.

Table 3. Operating Temperature Range Comparison

| Operating<br>Temperature<br>Range | CY14E256L/<br>STK14C88 | CY14E256LA    |

|-----------------------------------|------------------------|---------------|

| Commercial<br>(0 to 70°C)         | Available              | Not Available |

| Industrial<br>(-40 to 85°C)       | Available              | Available     |

## **Packages**

CY14E256LA is pin compatible with CY14E256L/STK14C88 and is available in the same packages and pin configurations, as well as in additional packages

Table 4. Packages Comparison

| Package   | CY14E256L/<br>STK14C88 | CY14E256LA    |

|-----------|------------------------|---------------|

| 32 SOIC   | Available              | Available     |

| 32 CDIP   | Available              | Not Available |

| 44 TSOPII | Not Available          | Available     |

#### **Parameters**

The CY14E256LA is a drop in replacement for CY14E256L/STK14C88 and will require minimum changes in the application board. However, the differences in parameters should be considered before replacing one part with the other. Table 5 lists the differences in parameters between CY14E256L/STK14C88 and CY14E256LA.

Table 5. Parameter Comparison

| Parameter            | Description Speed CY14E256L/<br>STK14C88                              |        |               | CY14                              | E256LA | Unit                              |      |

|----------------------|-----------------------------------------------------------------------|--------|---------------|-----------------------------------|--------|-----------------------------------|------|

|                      | 2 2 2 2 3 4 1 2 3 1                                                   | op.com | Min           | Max                               | Min    | Max                               |      |

| DC Parame            | ters                                                                  |        |               | 1                                 |        | -                                 |      |

|                      |                                                                       | 25 ns  |               | 100                               |        | 70                                |      |

| I <sub>CC1</sub>     | Average V <sub>CC</sub> Current                                       | 35 ns  |               | 85                                |        | -                                 | mA   |

|                      |                                                                       | 45 ns  |               | 70                                |        | 52                                |      |

| I <sub>CC2</sub>     | Average V <sub>CC</sub> Current during STORE                          |        |               | 3                                 |        | 10                                | A    |

| Іссз                 | Average V <sub>CC</sub> Current at t <sub>RC</sub> = 200 ns, 5V, 25°C |        | 1             | 0 (typ)                           | 3      | ō (typ)                           | – mA |

| I <sub>CC4</sub>     | Average V <sub>CAP</sub> Current during AutoStore Cycle               |        |               | 2                                 |        | 5                                 | mA   |

|                      |                                                                       | 25 ns  |               | 31                                |        |                                   |      |

| I <sub>SB1</sub>     | Average V <sub>CC</sub> Standby Current (Standby, Cycling Input)      | 35 ns  |               | 26                                | Not    | specified                         | mA   |

|                      | oyamig mp my                                                          | 45 ns  |               | 23                                |        |                                   |      |

| I <sub>SB</sub>      | V <sub>CC</sub> Standby Current                                       |        |               | 1.5                               |        | 5                                 | mA   |

| I <sub>IX</sub>      | Input Leakage Current                                                 |        | -5            | +5                                | -1     | +1                                | uA   |

| $V_{IH}$             | Input High Voltage                                                    |        | 2.2           |                                   | 2      |                                   | V    |

| $V_{OH}$             | Output HIGH Voltage                                                   |        |               | 2.4<br>(I <sub>OUT</sub> = -4 mA) |        | 2.4<br>(I <sub>OUT</sub> = -2 mA) | V    |

| V <sub>OL</sub>      | Output LOW Voltage                                                    |        |               | 0.4<br>(I <sub>OUT</sub> = 8 mA)  |        | 0.4<br>(I <sub>OUT</sub> = 4 mA)  | V    |

| V <sub>CAP</sub>     | Storage Capacitor                                                     |        | 54            | to 260                            | 61     | to 180                            | uF   |

| AC Switchi           | ng Parameters                                                         |        |               |                                   |        |                                   | •    |

|                      |                                                                       | 25 ns  |               | 10                                |        | 12                                |      |

| $t_{DOE}$            | Output Enable to Data Valid                                           | 35 ns  |               | 15                                |        | -                                 | mA   |

|                      |                                                                       | 45 ns  |               | 20                                |        | 20                                |      |

| t <sub>OHA</sub>     | Output Hold After Address Change                                      |        | 5             |                                   | 3      |                                   | ns   |

| t <sub>LZCE</sub>    | Chip Enable to Output Active                                          |        | 5             |                                   | 3      |                                   | ns   |

| t <sub>LZWE</sub>    | Output Active After End of Write                                      |        | 5             |                                   | 3      |                                   | ns   |

| AutoStore /          | Power Up RECALL Parameters                                            |        |               |                                   |        |                                   |      |

| t <sub>HRECALL</sub> | Power Up RECALL Duration                                              |        |               | 0.55                              |        | 20                                | ms   |

| t <sub>STORE</sub>   | STORE Cycle Duration                                                  |        |               | 10                                |        | 8                                 | ms   |

| $t_{VSBL}$           | Low Voltage Trigger ( $V_{SWITCH}$ ) to $\overline{HSB}$ low          |        |               | 300                               |        | 25                                | ns   |

| $V_{RESET}$          | Low Voltage Reset Level                                               |        |               | 3.6                               | Not A  | pplicable                         | V    |

| V <sub>SWITCH</sub>  | Low Voltage Trigger Level                                             |        | 4.0           | 4.5                               |        | 4.4                               | V    |

| t <sub>DELAY</sub>   | Time Allowed to Complete SRAM Write Cycle                             |        | 1,000         |                                   |        | 25                                | ns   |

| $V_{HDIS}$           | HSB Output Disable Voltage                                            |        | Not           | specified                         |        | 1.9                               | V    |

| t <sub>LZHSB</sub>   | HSB To Output Active Time                                             |        | Not           | specified                         |        | 5                                 | us   |

| t <sub>HHHD</sub>    | HSB High Active Time                                                  |        | Not specified |                                   | _      | 500                               | ns   |

[+] Feedback

| Parameter           | Description                                        | Speed CY14E2  |     | CY14E256LA |     | Unit                     |    |

|---------------------|----------------------------------------------------|---------------|-----|------------|-----|--------------------------|----|

|                     | ·                                                  |               | Min | Max        | Min | Max                      |    |

| Software Co         | Software Controlled STORE/RECALL cycle Parameters  |               |     |            |     |                          |    |

| t <sub>HA</sub>     | Address Hold Time                                  |               | 20  |            | 0   |                          | ns |

| t <sub>RECALL</sub> | STORE Cycle Duration                               |               |     | 20         |     | 200                      | us |

| Hardware S          | Hardware STORE cycle Parameters                    |               |     |            |     |                          |    |

| t <sub>HLBL</sub>   | HSB LOW to STORE Busy                              |               |     | 300        |     | 25 (t <sub>DELAY</sub> ) | ns |

| t <sub>DHSB</sub>   | HSB To Output Active Time when write latch not set | Not specified |     | 25         | ns  |                          |    |

## **Critical Considerations**

The impact of the differences in CY14E256LA with respect to the CY14E256/STK14C88 in existing applications are discussed below. Board designers are recommended to review the detailed datasheets when converting to the new part.

#### **DC Parameters**

$I_{\text{CC1}}$  (Average current at full speed) is lower in CY14E256LA and hence power supply design in applications with CY14E256L/STK14C88 would require no changes when replacing the nvSRAM with the CY14E256LA in spite of the higher values in the lower speed / higher standby current. The critical parameter to consider is the  $V_{\text{CAP}}$ .

#### $V_{CAP}$

While most of the differences do not impact the application, the difference in  $V_{\text{CAP}}$  is a critical consideration while converting from the older rev parts.  $V_{\text{CAP}}$  is the capacitor which provides the required charge for AutoStore to complete NV store of the SRAM data during power down. The required capacitor range is different in the two parts.

Table 6. V<sub>CAP</sub> Comparison

| Description | CY14E256L/<br>STK14C88 | CY14E256LA     |

|-------------|------------------------|----------------|

| $V_{CAP}$   | 54uF to 260 uF         | 61uF to 180 uF |

Therefore, any existing application using a capacitor value outside the overlapping range for the capacitor values needs to consider the impact of capacitor dimensions while changing to the new capacitor. Note: The capacitor range is the absolute value of the capacitor, net of tolerence.

#### **AC Switching Parameters**

There are a few minor differences in switching parameters between the CY14E256LA and the CY14B256L/STK14C88 as listed in the Table 5. However, these differences do not impact most applications. For replacing 35ns speed parts, choose the 25ns speed parts as replacement (since 35ns speed grade is not available in the CY14E256LA).

#### **AutoStore / Power Up RECALL Parameters**

#### **t**HRECALL

The power up RECALL is much different in the CY14E256LA compared to the STK14C88 because of architecture differences.

Table 7. threcall Comparison

| Description          | CY14E256L/<br>STK14C88 | CY14E256LA |

|----------------------|------------------------|------------|

| t <sub>HRECALL</sub> | 550 us                 | 20 ms      |

This difference is not likely to affect applications since the initialization of the controller on the board happens at the same time. However, this should be taken into consideration when replacing the STK14C88 with CY14E256LA.

#### Software Controlled STORE/RECALL Cycle Parameters

The Software cycle parameter  $t_{\text{RECALL}}$  is different in CY14E256LA as described below. The software address sequences are identical to that in the old rev part.

#### $t_{RECALL}$

Software RECALL time (t<sub>RECALL</sub>) is higher in CY14E256LA.

Table 8. t<sub>RECALL</sub> Comparison

| Description         | CY14E256L/<br>STK14C88 | CY14E256LA |

|---------------------|------------------------|------------|

| t <sub>RECALL</sub> | 20 us                  | 200 us     |

This difference could require firmware change in the application to increase the wait state when software RECALL is initiated.

#### **Software Sequence**

The CY14E256LA has been designed to be compatible with the CY14E256L/STK14C88 in the software sequence modes. Hence, the same Software STORE and RECALL address sequences in CY14E256L/STK14C88 works in CY14E256LA, requiring no firmware change.

#### **Hardware STORE cycle Parameters**

The Hardware STORE parameters are much improved in the CY14E256LA. The improvements are listed under the following section on Details of Improvement. No changes will be required in applications.

#### **AutoStore Inhibit**

The CY14E256L/STK14C88 has the AutoStore Inhibit feature and the CY14E256LA has AutoStore Disable mode. These two provide the same result of AutoStore disable but are done by different means — hardware in CY14E256L/STK14C88 and software in CY14E256LA.

To disable AutoStore in CY14E256L/STK14C88, the power is to be connected to the  $V_{\text{CAP}}$  pin and the  $V_{\text{CC}}$  pin is grounded (or left open). This cannot be done in CY14E256LA. For proper operation of the device, in CY14E256LA, power is to be connected to the  $V_{\text{CC}}$  pin only. However, AutoStore disable is more easily done through simple software sequence. Therefore, if the CY14E256L/STK14C88 is to be replaced in an application where AutoStore has been disabled, then the layout has to be modified to connect the power to the  $V_{\text{CC}}$  pin and a software sequence has to be used to disable AutoStore function followed by a Software STORE, the first time the board is powerd up.

#### **STORE Cycles**

The NV STORE cycles endurance in CY14E256LA is lower than the endurance in the older 0.8u technology. However, this would not affect in most applications since all nvSRAMs have infinite read/write endurance and the NV STORE would happen only during power down or during Software STORE. For example, if a system is powered down 10 times a day, then the NV STORE endurance is reached in 54 years in CY14E256LA.

#### **Data Retention**

The Data Retention in 0.13u part is vastly improved from the older technology part. The CY14E256LA has a data retention of 20 years at 85°C against the CY14E256L/STK14C88 data retention of 100 years at 55°C. This would translate to over 4 times improvement in data retention at the same temperatures.

# **Details of Improvement**

#### **Hardware STORE Related Improvements**

HSB pin (Hardware STORE Busy Indication/Hardware STORE Initiation)

The  $\overline{\text{HSB}}$  pin of the nvSRAM is an open drain I/O pin used to indicate or initiate a STORE operation. When a STORE operation is in progress, nvSRAM pulls the  $\overline{\text{HSB}}$  pin low to indicate that the device is busy and cannot be accessed for read/write operation. During normal operation, the  $\overline{\text{HSB}}$  pin can be pulled low to initiate a Hardware STORE operation.

As shown in Table 5, several timing parameters related to the HSB pin input and output have changed from CY14E256L/STK14C88 to CY14E256LA. All of these changes are improvements from the original part specification and should be considered as added benefits in your system while converting to the new part number.

Write Latch: When a write operation is done, a 'write latch' is set internally. When  $\overline{\text{HSB}}$  is pulled low, nvSRAM checks this write latch before initiating a STORE. This is done to prevent any unnecessary loss of endurance cycles.

#### $t_{DELAY}$

If a write latch is set and the HSB pin is pulled low, CY14E256L/STK14C88 enables 1 us time for write operations to complete before STORE operation begins and

reads and writes are inhibited. This potentially enables inadvertent data to be written to the nvSRAM during the  $t_{\text{DELAY}}$  duration.

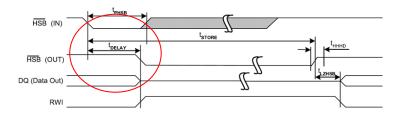

In CY14E256LA, the  $t_{DELAY}$  parameter enables only one write cycle time for any ongoing write to complete after  $\overline{\text{HSB}}$  pin is pulled low. This improvement provides better security from inadvertent write operations.

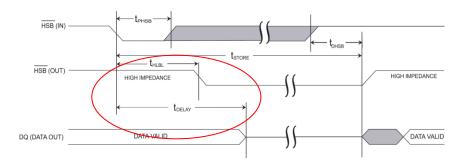

Also, if HSB pin is pulled low externally for a minimum of  $t_{PHSB}$  time on CY14E256LA, the output driver of  $\overline{HSB}$  pin pulls the pin low only indicating a STORE operation within 25 ns ( $t_{DELAY}$ ). This parameter for  $\overline{HSB}$  low to STORE busy is not specified in the CY14E256L/STK14C88. (See Figure 1 and Figure 2)

HSB LOW when write latch not set:

If no writes are performed since the last STORE/RECALL operation, STORE operation does not start when  $\overline{\text{HSB}}$  is pulled low. However, the  $\overline{\text{HSB}}$  pin is still internally pulled low for 1 us (t<sub>DELAY</sub>) time in the CY14E256L/ STK14C88 device.

CY14E256LA device does not pull the HSB pin low internally if write latch is not set.

Figure 1. CY14E256L/STK14C88: AC Parameters Related to HSB

Figure 2. CY14E256LA: AC Parameters Related to HSB

Write Latch not Set

October 5, 2009 Document No. 001-55663 Rev. \*\* 5

Write Latch Set

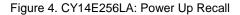

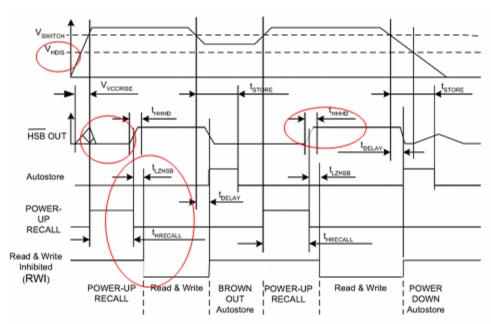

## **Power up Recall Related Improvements**

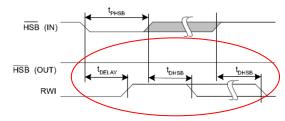

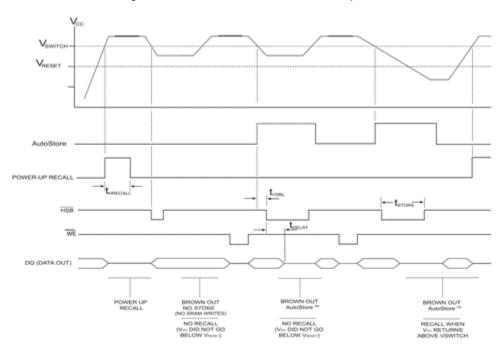

Additional parameters are specified in CY14E256LA such as  $\overline{\text{HSB}}$  Output Disable Voltage (V<sub>HDIS</sub>),  $\overline{\text{HSB}}$  To Output Active Time (t<sub>LZHSB</sub>), and  $\overline{\text{HSB}}$  High Active Time (t<sub>HHHD</sub>) which helps in system design. Refer to Figure 3 and Figure 4 for the definition of the additional specs in power up. Also, note that  $\overline{\text{HSB}}$  remains low until the end of the power up in the new part. This would guard against the system inadvertently thinking the part has completed the boot up prior to real completion.

Figure 3. CY14E256L/STK14C88: Power Up Recall

[+] Feedback

# **Summary**

The application note discusses the differences between CY14E256LA in the latest 0.13u technology and CY14E256L/STK14C88 in the 0.8u technology. Several parameters related to  $\overline{\text{HSB}}$  and power up have improved / specified in the new device enabling faster device response, greater data security and ease of design.

CY14E256LA is pin compatible and can replace the CY14E256L/STK14C88 device with no changes or minimum changes to the firmware. The value of  $V_{CAP}$  in the existing design needs to be considered while replacing the part.

# **Document History**

Document Title: Converting from CY14E256L/STK14C88 to CY14E256LA

Document Number: 001-55663

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change |

|----------|---------|--------------------|--------------------|-----------------------|

| **       | 2773126 | PSR                | 10/01/09           | New Spec.             |

All trademarks and registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone: 408-943-2600 Fax: 408-943-4730

http://www.cypress.com/

© Cypress Semiconductor Corporation, 2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document No. 001-55663 Rev. \*\*

[+] Feedback