# DALLAS SEMICONDUCTOR

# DS2016 2k x 8 3V/5V Operation Static RAM

#### www.maxim-ic.com

#### **FEATURES**

- Low-power CMOS design

- Standby current

- 50nA max at  $t_A = +25^{\circ}C V_{CC} = 3.0V$

- 100nA max at  $t_A = +25^{\circ}C V_{CC} = 5.5V$

- $1\mu A \text{ max at } t_A = +60^{\circ} C V_{CC} = 5.5 V$

- Full operation for  $V_{CC} = 5.5V$  to 2.7V

- Data retention voltage = 5.5V to 2.0V

- Fast 5V access time

- DS2016-100 100ns

- Reduced-speed 3V access time

DS2016-100 250ns

- Operating temperature range of -40°C to +85°C

- Full static operation

- TTL compatible inputs and outputs over voltage range of 5.5V to 2.7V

- Available in 24-pin DIP and 24-pin SO packages

- Suitable for both battery operated and battery backup applications

### **PIN ASSIGNMENT**

| A7   <br>A6   <br>A5   <br>A3   <br>A2   <br>A1   <br>DQ0   <br>DQ1   <br>DQ2   <br>GND | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12 | 24   V <sub>CC</sub> 23   A8     22   A9     21   WE     20   OE     19   A10     18   CE     17   DQ7     16   DQ6     15   DQ5     14   DQ4     13   DQ3 |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         | 12                                                          |                                                                                                                                                            |

DS2016 24-Pin DIP (600mil) DS2016R 24-Pin SO (300mil)

#### **PIN DESCRIPTION**

| A0 to A10              | - Address Inputs                 |

|------------------------|----------------------------------|

| DQ0 to DQ7             | - Data Input/Output              |

| $\overline{\text{CE}}$ | - Chip Enable Input              |

| WE                     | - Write Enable Input             |

| $\overline{OE}$        | - Output Enable Input            |

| V <sub>CC</sub>        | - Power Supply Input 2.7V - 5.5V |

| GND                    | - Ground                         |

# DESCRIPTION

The DS2016 2k x 8 3V/5V Operation Static RAM is a 16,384-bit, low-power, fully static random access memory organized as 2048 words by 8 bits using CMOS technology. The device operates from a single power supply with a voltage input between 2.7V and 5.5V. The chip enable input ( $\overline{CE}$ ) is used for device selection and can be used in order to achieve the minimum standby current mode, which facilitates both battery operated and battery backup applications. The device provides access times as fast as 100ns when operated from a 5V power supply input and also provides relatively good performance of 250ns access while operating from a 3V input. The device maintains TTL-level inputs and outputs over the input voltage range of 2.7V to 5.5V. The DS2016 is most suitable for low-power applications where battery operation or battery backup for nonvolatility is required. The DS2016 is a JEDEC-standard 2k x 8 SRAM and is pin-compatible with ROM and EPROM of similar density.

# **OPERATION MODE**

| MODE     | CE | ŌĒ | WE | A0-A10 | DQ-DQ7   | POWER            |

|----------|----|----|----|--------|----------|------------------|

| READ     | L  | L  | Н  | STABLE | DATA OUT | I <sub>CCO</sub> |

| WRITE    | L  | Х  | L  | STABLE | DATA IN  | I <sub>CCO</sub> |

| DESELECT | L  | Н  | Н  | Х      | HIGH-Z   | I <sub>CCO</sub> |

| STANDBY  | Н  | Х  | Х  | Х      | HIGH-Z   | I <sub>CCS</sub> |

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                             | PARAMETER                   | RATING                        |

|------------------------------------|-----------------------------|-------------------------------|

| V <sub>CC</sub>                    | Power Supply Voltage        | -0.3V to +7.0V                |

| V <sub>IN</sub> , V <sub>I/O</sub> | Input, Input/Output Voltage | -0.3 to V <sub>CC</sub> +0.3V |

| T <sub>STG</sub>                   | Storage Temperature         | -55°C to +125°C               |

| T <sub>OPR</sub>                   | Operating Temperature       | -40°C to +85°C                |

| T <sub>SOLDER</sub>                | Soldering Temperature/Time  | IPC/JEDEC J-STD-020           |

#### CAPACITANCE +25°C)

$(T_A =$

| 120 0)    |    |

|-----------|----|

| PARAMETER | SY |

| T I G I   |    |

| PARAMETER                | SYMBOL           | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|------------------|-----|-----|-----|-------|-------|

| Input Capacitance        | C <sub>IN</sub>  |     | 5   | 10  | pF    |       |

| Input/Output Capacitance | C <sub>I/O</sub> |     | 5   | 12  | pF    |       |

# +5-VOLT OPERATION

| RECOMMENDED DC OP      | (T <sub>A</sub> = -40°C to +85°C) |      |     |                |       |       |

|------------------------|-----------------------------------|------|-----|----------------|-------|-------|

| PARAMETER              | SYMBOL                            | MIN  | ТҮР | MAX            | UNITS | NOTES |

| Power Supply Voltage   | V <sub>CC</sub>                   | 4.5  | 5.0 | 5.5            | V     |       |

| Input High Voltage     | V <sub>IH</sub>                   | 2.0  |     | $V_{CC} + 0.3$ | V     |       |

| Input Low Voltage      | V <sub>IL</sub>                   | -0.3 |     | 0.8            | V     |       |

| Data Retention Voltage | V <sub>DR</sub>                   | 2.0  |     | 5.5            | V     |       |

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C; V_{CC} = 5V \pm 10\%)$

| PARAMETER             | SYMBOL            | CONDITIONS                                                                     | MIN  | TYP | MAX       | UNITS |  |

|-----------------------|-------------------|--------------------------------------------------------------------------------|------|-----|-----------|-------|--|

| Input Leakage Current | I <sub>IL</sub>   | $0V \leq V_{IN} \leq V_{CC}$                                                   |      |     | $\pm 0.1$ | μA    |  |

| I/O Leakage Current   | ILO               | $\overline{\text{CE}} = V_{\text{IH}}, 0V \le V_{\text{IO}} \le V_{\text{CC}}$ |      |     | $\pm 0.5$ | μA    |  |

| Output High Current   | I <sub>OH</sub>   | $V_{OH} = 2.4 V$                                                               | -1.0 |     |           | mA    |  |

| Output Low Current    | I <sub>OL</sub>   | $V_{OL} = 0.4 V$                                                               | 4.0  |     |           | mA    |  |

| Standby Current       | I <sub>CCS1</sub> | $\overline{\text{CE}} = 2.0 \text{V}$                                          |      |     | 0.3       | mA    |  |

| Standby Current       | I <sub>CCS2</sub> | $\overline{CE} \ge V_{CC} - 0.5V, t_A = +60^{\circ}C$                          |      |     | 1         | μΑ    |  |

| Standby Current       | I <sub>CCS2</sub> | $\overline{CE} \ge V_{CC} - 0.5V, t_A = +25^{\circ}C$                          |      |     | 100       | nA    |  |

| Operating Current     | I <sub>CCO</sub>  | $\overline{\text{CE}} = 0.8 \text{V}, 200 \text{ns cycle}$                     |      |     | 55        | mA    |  |

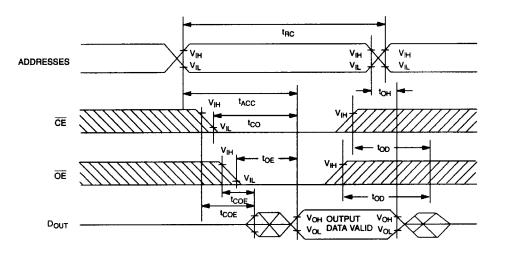

| AC CHARACTERISTICS READ CYCLE $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C; V_{CC} = 5V \pm 10\%)$ |                  |            |     |     |  |  |  |       |       |

|-----------------------------------------------------------------------------------------------------|------------------|------------|-----|-----|--|--|--|-------|-------|

| PARAMETER                                                                                           | SYMBOL           | DS2016-100 |     |     |  |  |  | UNITS | NOTES |

| FANAMEIEN                                                                                           | SINDUL           | MIN        | TYP | MAX |  |  |  | UNITS | NULES |

| Read Cycle Time                                                                                     | t <sub>RC</sub>  | 100        |     |     |  |  |  | ns    |       |

| Access Time                                                                                         | t <sub>ACC</sub> |            |     | 100 |  |  |  | ns    |       |

| OE to Output Valid                                                                                  | t <sub>OE</sub>  |            |     | 50  |  |  |  | ns    |       |

| CE to Output Valid                                                                                  | t <sub>CO</sub>  |            |     | 100 |  |  |  | ns    |       |

| $\overline{CE}$ or $\overline{OE}$ to Output<br>Active                                              | t <sub>COE</sub> | 5          |     |     |  |  |  | ns    |       |

| Output High-Z from Deselection                                                                      | t <sub>OD</sub>  | 5          |     | 35  |  |  |  | ns    |       |

| Output Hold from<br>Address Change                                                                  | t <sub>OH</sub>  | 5          |     |     |  |  |  | ns    |       |

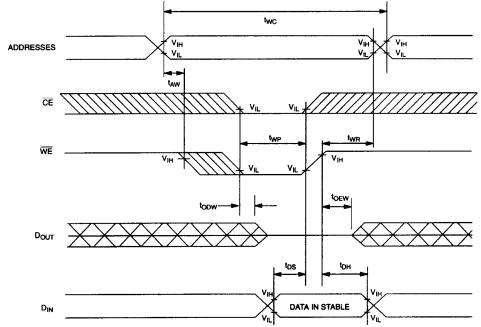

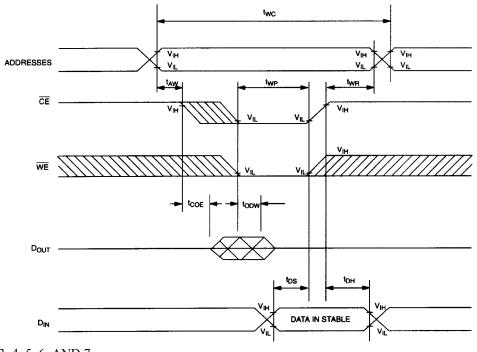

# **AC CHARACTERISTICS WRITE CYCLE** ( $T_A$ = -40°C to +85°C; $V_{CC}$ = 5V ±10%)

| PARAMETER                                                | SYMBOL           | DS2016-100 |     |     |  | UNITS | NOTES |

|----------------------------------------------------------|------------------|------------|-----|-----|--|-------|-------|

| FANAMEIEN                                                | SIMBUL           | MIN        | ТҮР | MAX |  | UNITS | NULES |

| Write Cycle Time                                         | t <sub>WC</sub>  | 100        |     |     |  | ns    |       |

| Write Pulse Width                                        | t <sub>WP</sub>  | 75         |     |     |  | ns    |       |

| Address Setup Time                                       | $t_{AW}$         | 0          |     |     |  | ns    |       |

| Write Recovery<br>Time                                   | t <sub>WR</sub>  | 10         |     |     |  | ns    |       |

| $\frac{\text{Output High-Z from}}{\overline{\text{WE}}}$ | t <sub>ODW</sub> |            |     | 35  |  | ns    |       |

| $\frac{\text{Output Active from}}{\overline{\text{WE}}}$ | t <sub>OEW</sub> | 5          |     |     |  | ns    |       |

| Data Setup Time                                          | t <sub>DS</sub>  | 40         |     |     |  | ns    |       |

| Data Hold Time                                           | t <sub>DH</sub>  | 0          |     |     |  | ns    |       |

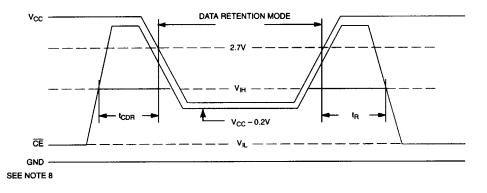

| DATA RETENTION                     | $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$ |                                                                |     |      |     |       |

|------------------------------------|-------------------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| PARAMETER                          | SYMBOL                                          | CONDITIONS                                                     | MIN | TYP  | MAX | UNITS |

| Data Retention Supply<br>Voltage   | V <sub>DR</sub>                                 | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.5 \text{V}$ | 2.0 |      | 5.5 | V     |

| Data Retention<br>Current at 5.5V  | I <sub>CCR1</sub>                               | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.5 \text{V}$ |     | 0.1* | 1   | μΑ    |

| Data Retention<br>Current at 2.0V  | I <sub>CCR2</sub>                               | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.5 \text{V}$ |     | 50*  | 750 | nA    |

| Chip Deselect to Data<br>Retention | t <sub>CDR</sub>                                |                                                                | 0   |      |     | μs    |

| Recovery Time                      | t <sub>R</sub>                                  |                                                                | 2   |      |     | ms    |

\* Typical values are at +25°C

# +3-VOLT OPERATION

| RECOMMENDED DC OP      | (T <sub>A</sub> = -40°C to +85°C) |      |     |                |       |       |

|------------------------|-----------------------------------|------|-----|----------------|-------|-------|

| PARAMETER              | SYMBOL                            | MIN  | TYP | MAX            | UNITS | NOTES |

| Power Supply Voltage   | V <sub>CC</sub>                   | 2.7  | 3.0 | 3.5            | V     |       |

| Input High Voltage     | V <sub>IH</sub>                   | 2.0  |     | $V_{CC} + 0.3$ | V     |       |

| Input Low Voltage      | V <sub>IL</sub>                   | -0.3 |     | 0.6            | V     |       |

| Data Retention Voltage | V <sub>DR</sub>                   | 2.0  |     | 3.5            | V     |       |

| DC CHARACTERIS        | STICS             | $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C; V_{CC} = 2.7V \text{ to } 3.5V)$                            |      |     |      |       |  |

|-----------------------|-------------------|------------------------------------------------------------------------------------------------------------|------|-----|------|-------|--|

| PARAMETER             | SYMBOL            | CONDITIONS                                                                                                 | MIN  | TYP | MAX  | UNITS |  |

| Input Leakage Current | $I_{IL}$          | $0V \leq V_{IN} \leq V_{CC}$                                                                               |      |     | ±0.1 | μA    |  |

| I/O Leakage Current   | ILO               | $\overline{\text{CE}} = \text{V}_{\text{IH}}, 0\text{V} \le \text{V}_{\text{IO}} \le \text{V}_{\text{CC}}$ |      |     | ±0.5 | μA    |  |

| Output High Current   | I <sub>OH</sub>   | $V_{OH} = 2.2V$                                                                                            | -0.5 |     |      | mA    |  |

| Output Low Current    | I <sub>OL</sub>   | $V_{OL} = 0.4 V$                                                                                           | 4.0  |     |      | mA    |  |

| Standby Current       | I <sub>CCS1</sub> | $\overline{\text{CE}} = 2.0 \text{V}$                                                                      |      |     | 0.1  | mA    |  |

| Standby Current       | I <sub>CCS2</sub> | $\overline{CE} \ge V_{CC} - 0.3V, T_A = +60^{\circ}C$                                                      |      |     | 500  | nA    |  |

| Standby Current       | I <sub>CCS2</sub> | $\overline{\text{CE}} \ge V_{\text{CC}} - 0.3 \text{V}, \text{T}_{\text{A}} = +25^{\circ}\text{C}$         |      |     | 50   | nA    |  |

| Operating Current     | I <sub>CCO</sub>  | $\overline{\text{CE}} = 0.6 \text{V} \text{ min cycle}$                                                    |      |     | 25   | mA    |  |

# AC CHARACTERISTICS READ CYCLE

|                                                     |                  | $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C; V_{CC} = 2.7V \text{ to } 3.5V)$ |     |     |       |       |  |

|-----------------------------------------------------|------------------|---------------------------------------------------------------------------------|-----|-----|-------|-------|--|

| PARAMETER                                           | SYMBOL           | MIN                                                                             | TYP | MAX | UNITS | NOTES |  |

| Read Cycle Time                                     | t <sub>RC</sub>  | 250                                                                             |     |     | ns    |       |  |

| Access Time                                         | t <sub>ACC</sub> |                                                                                 |     | 250 | ns    |       |  |

| OE to Output Valid                                  | t <sub>OE</sub>  |                                                                                 |     | 120 | ns    |       |  |

| $\overline{CE}$ to Output Valid                     | t <sub>CO</sub>  |                                                                                 |     | 250 | ns    |       |  |

| $\overline{CE}$ or $\overline{OE}$ to Output Active | t <sub>COE</sub> | 15                                                                              |     |     | ns    |       |  |

| Output High-Z<br>from Deselection                   | t <sub>OD</sub>  | 5                                                                               |     | 100 | ns    |       |  |

| Output Hold from<br>Address Change                  | t <sub>OH</sub>  | 15                                                                              |     |     | ns    |       |  |

# AC CHARACTERISTICS WRITE CYCLE

|                                    |                  | $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C; V_{CC} = 2.7V \text{ to } 3.5V)$ |     |     |       |       |  |

|------------------------------------|------------------|---------------------------------------------------------------------------------|-----|-----|-------|-------|--|

| PARAMETER                          | SYMBOL           | MIN                                                                             | TYP | MAX | UNITS | NOTES |  |

| Write Cycle Time                   | t <sub>WC</sub>  | 250                                                                             |     |     | ns    |       |  |

| Write Pulse Width                  | t <sub>WP</sub>  | 190                                                                             |     |     | ns    |       |  |

| Address Setup Time                 | t <sub>AW</sub>  | 0                                                                               |     |     | ns    |       |  |

| Write Recovery Time                | t <sub>WR</sub>  | 25                                                                              |     |     | ns    |       |  |

| Output High-Z from $\overline{WE}$ | t <sub>ODW</sub> |                                                                                 |     | 90  | ns    |       |  |

| Output Active from $\overline{WE}$ | t <sub>OEW</sub> | 5                                                                               |     |     | ns    |       |  |

| Data Setup Time                    | t <sub>DS</sub>  | 100                                                                             |     |     | ns    |       |  |

| Data Hold Time                     | t <sub>DH</sub>  | 0                                                                               |     |     | ns    |       |  |

#### DATA RETENTION CHARACTERISTICS

$(T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C)$

|                  |                   |                                                                |     | ( 'A |      | 0.000 |

|------------------|-------------------|----------------------------------------------------------------|-----|------|------|-------|

| PARAMETER        | SYMBOL            | CONDITIONS                                                     | MIN | TYP  | MAX  | UNITS |

| Data Retention   | V <sub>DR</sub>   | $\overline{CE} > V = 0.2V$                                     | 2.0 |      | 3.5  | V     |

| Supply Voltage   | V DR              | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.3 \text{V}$ | 2.0 |      | 5.5  | v     |

| Data Retention   | T                 | $\overline{CE} > V = 0.2V$                                     |     | 50*  | 1000 | ۳Å    |

| Current at 3.5V  | I <sub>CCR1</sub> | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.3\text{V}$  |     | 30.  | 1000 | nA    |

| Data Retention   | T                 | $\overline{CE} > V = 0.2V$                                     |     | 50*  | 750  | A     |

| Current at 2.0V  | I <sub>CCR2</sub> | $\overline{\text{CE}} \ge \text{V}_{\text{CC}} - 0.3 \text{V}$ |     | 50*  | 750  | nA    |

| Chip Deselect to | 4                 |                                                                | 0   |      |      |       |

| Data Retention   | t <sub>CDR</sub>  |                                                                | 0   |      |      | μs    |

| Recovery Time    | t <sub>R</sub>    |                                                                | 2   |      |      | ms    |

|                  |                   |                                                                |     |      |      |       |

\* Typical values are at +25°C

# TIMING DIAGRAM: READ CYCLE

SEE NOTE 1

# **TIMING DIAGRAM: WRITE CYCLE 1**

SEE NOTES 2, 3, 4, 5, 6, AND 7

# TIMING DIAGRAM: WRITE CYCLE 2

SEE NOTES 2, 3, 4, 5, 6, AND 7

#### TIMING DIAGRAM: DATA RETENTION - POWER-UP, POWER-DOWN Figure 1

#### NOTES:

- 1)  $\overline{\text{WE}}$  is high for read cycles.

- 2)  $\overline{OE} = V_{IH}$  or  $V_{IL}$ . If  $\overline{OE} = V_{IH}$  during write cycle, the output buffers remain in a high impedance state.

- 3)  $t_{WP}$  is specified as the logical AND of  $\overline{CE}$  and  $\overline{WE}$ .  $t_{WP}$  is measured from the latter of  $\overline{CE}$  or  $\overline{WE}$  going low to the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 4)  $t_{DH}$  and  $t_{DS}$  are measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 5) If the  $\overline{CE}$  low transition occurs simultaneously with or later than the  $\overline{WE}$  low transition, the output buffers remain in a high impedance state.

- 6) If the  $\overline{CE}$  high transition occurs prior to or simultaneously with the  $\overline{WE}$  high transition, the output buffers remain in a high impedance state.

- 7) If  $\overline{WE}$  is low or the  $\overline{WE}$  low transition occurs prior to or simultaneously with the  $\overline{CE}$  low transition, the output buffers remain in a high impedance state.

- 8) If the  $V_{IH}$  level of CE is 2.0V during the period that  $V_{CC}$  voltage is going down from 4.5V to 2.7V,  $I_{CCS1}$  current flows.

- 9) The DS2016 maintains full operation from 5.5V to 2.7V. The electrical characteristics tables show two tested and guaranteed points of operation. For operation between 4.5V and 3.5V, use the composite worst case characteristics from both 5V and 3V operation for design purposes.

# **DC TEST CONDITIONS**

Outputs Open All voltages are referenced to ground.

# AC TEST CONDITIONS

Output Load: 100pF + 1TTL Gate Input Pulse Levels: 0V - 3.0V Timing Measurement Reference Levels Input: 1.5V Output: 1.5V Input Pulse Rise and Fall Times: 5ns

# PACKAGE INFORMATION

For the latest package outline information, go to <u>www.maxim-ic.com/DallasPackInfo</u>.