# **SSRP105B1**

# Application Specific Discretes ASD™

# DUAL ASYMMETRICAL OVERVOLTAGE PROTECTION FOR TELECOM LINE

### **MAIN APPLICATIONS**

Where asymmetrical protection against lightning strikes and other transient overvoltages is required:

- Solid-State relays

- SLIC with integrated ring generator

### **DESCRIPTION**

The SSRP105B1 is a dual asymmetrical transient voltage suppressor designed to protect a solid-state ring relay or SLICs with integrated ring generator from overvoltages.

The asymmetrical protection configuration is necessary to allow the use of all different types of ringing schemes.

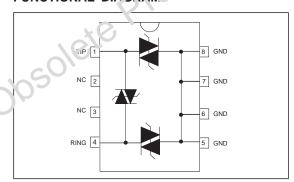

# FUNCTIONAL DIACRAM

**SO-8**

### **FEATURES**

- Dual bi-directional asymmetrical protection Stand-off voltages:

- Between Line and Ground

- +105V for positive voltages

- -180V for negative voltages

- Between Line and Line

- +180V for positive voltages

- -180V for negative voltages

- Peak pulse current: IPP = 50A (5/3.0, vs)

- Holding current:

- I<sub>H+</sub> = 100mA

- I<sub>H-</sub> = 150mA

# COMPLY WITH THE ! O'LLOWING STANDARDS

| coleite            | Peak Surge<br>Voltage<br>(V) | Voltage<br>Waveform<br>(μs) | Current<br>Waveform<br>(µs) | Required<br>Peak<br>current<br>(A) | Min. serial resistor to meet standards $(\Omega)$ |

|--------------------|------------------------------|-----------------------------|-----------------------------|------------------------------------|---------------------------------------------------|

| Tru T K20 / K21    | 1500                         | 10/700                      | 5/310                       | 38                                 | -                                                 |

| VDE0433            | 2000                         | 10/700                      | 5/310                       | 50                                 | -                                                 |

| IEC61000-4-5       | Level 3                      | 10/700                      | 5/310                       | 50                                 | -                                                 |

|                    | Level 4                      | 1.2/50                      | 8/20                        | 100                                | -                                                 |

| FCC Part 68        | 1500                         | 10/160                      | 10/160                      | 200                                | 18                                                |

|                    | 800                          | 10/560                      | 10/560                      | 100                                | 10                                                |

| BELLCORE           | 2500                         | 2/10                        | 2/10                        | 500                                | 10                                                |

| GR1089 First level | 1000                         | 10/1000                     | 10/1000                     | 100                                | 19                                                |

TM: ASD is trademarks of STMicroelectronics.

October 2002 - Ed: 1A 1/6

# Downloaded from Elcodis.com electronic components distributor

### APPLICATION INFORMATION

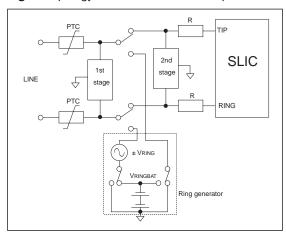

Fig. 1: Topology of the classical line card protection.

The classical line card requires protection before the ring relay and a second one for the SLIC (*figure 1*).

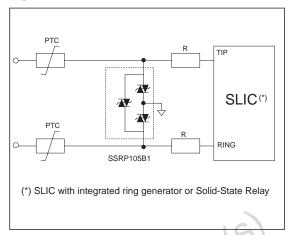

The use of new SLICs with integrated ring generator or board based on solid-state ring relay suppresses this second protection (figure 2). Then, the only remaining stage, located between the line and the ring relay, has to optimize the protection.

The classical symmetrical first stage protector becomes not sufficient to avoid any circuit destruction during surges.

Fig. 2: Classical use of the SSRP105B1.

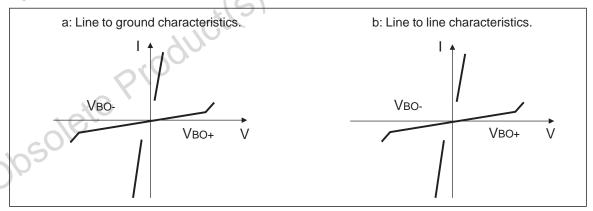

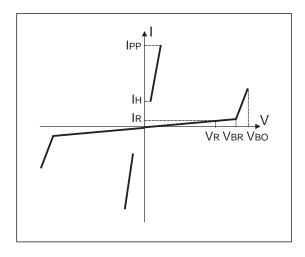

The SSRP105B1 device takes into account this fact and is based on asymmetrical voltage characteristics (*figure 3a*). The ring signal being shifted back by the battery voltage, the SSRP105B1 negative breakover value V<sub>BO-</sub> is greater than the positive one V<sub>BO+</sub>. This point guarantees a protection operation very close to the peak of the normal operating voltage without any disturbance of the ring signal.

Fig. 3: SSRP105B1 electrical characteristics.

In addition with the 2 crowbar functions which perform the protection of both TIP and RING lines versus ground, a third cell assumes the differential mode protection of the SLIC. The breakover voltage values of this third cell are the same for

both positive and negative parts of the characteristics and are equivalent to the negative breakover voltage value of the TIP and RING lines versus GND cells (*figure 3b*).

# **ABSOLUTE MAXIMUM RATINGS** (T<sub>amb</sub> = 25°C)

| Symbol                             | Parameter                                                           |                                                                               | Value                              | Unit |

|------------------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------|------|

| Ірр                                | Peak pulse current (see note 1)                                     | 10 / 1000 µs<br>10 / 560µs<br>5 / 310µs<br>10 / 160µs<br>8 / 20µs<br>2 / 10µs | 35<br>45<br>50<br>60<br>120<br>175 | A    |

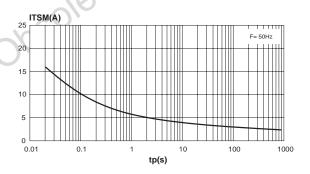

| I <sub>TSM</sub>                   | Non repetitive surge peak on-state current (F=50Hz)                 | tp = 0.2 s<br>tp = 5 s<br>tp = 15 min.                                        | 8.5<br>4.5<br>2.5                  | А    |

| T <sub>op</sub>                    | Operating temperature range                                         |                                                                               | 0 to + 70                          | °C   |

| T <sub>stg</sub><br>T <sub>j</sub> | Storage temperature range<br>Maximum operating junction temperature | - 55 to + 150<br>+ 150                                                        | °C<br>°C                           |      |

| TL                                 | Maximum lead temperature for soldering during 1                     | 10s                                                                           | 260                                | C°C  |

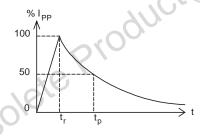

### Note 1 : Pulse waveform :

| 10/1000µs | t <sub>r</sub> =10µs | t <sub>p</sub> =1000µs |

|-----------|----------------------|------------------------|

| 10/560µs  | $t_r=10\mu s$        | t <sub>p</sub> =560µs  |

| 5/310µs   | $t_r=5\mu s$         | t <sub>p</sub> =310µs  |

| 10/160µs  | $t_r=10\mu s$        | t <sub>p</sub> =160µs  |

| 8/20µs    | t <sub>r</sub> =8µs  | t <sub>p</sub> =20µs   |

| 2/10µs    | t <sub>r</sub> =2µs  | t <sub>p</sub> =10µs   |

# THERMAL RESISTANCE

| Symbol                | Parameter           | Value | Unit |

|-----------------------|---------------------|-------|------|

| R <sub>th (j-a)</sub> | Junction to ambient | 170   | °C/W |

# **ELECTRICAL CHARACTERISTICS** (T<sub>amb</sub> = 25°C)

| Symbol          | Parameter                            |

|-----------------|--------------------------------------|

| V <sub>R</sub>  | Stand-off voltage                    |

| I <sub>R</sub>  | Leakage current at stand-off voltage |

| V <sub>BR</sub> | Breakdown voltage                    |

| V <sub>BO</sub> | Breakover voltage                    |

| IH              | Holding current                      |

| I <sub>BO</sub> | Breakover current                    |

| I <sub>PP</sub> | Peak pulse current                   |

| С               | Capacitance                          |

57

# ELECTRICAL CHARACTERISTICS between TIP and GND, RING and GND (Tamb=25°C)

| Symbol          | Parameter                  | Test conditions (note 1)                                                                              | Min.       | Тур.     | Max.       | Unit |

|-----------------|----------------------------|-------------------------------------------------------------------------------------------------------|------------|----------|------------|------|

| V <sub>BO</sub> | Breakover voltage (note 2) | Positive voltage . 50Hz . 10/700µs                                                                    |            |          | 165<br>165 | V    |

|                 |                            | Negative voltage . 50Hz<br>. 10/700µs                                                                 |            |          | 225<br>225 |      |

| l <sub>H</sub>  | Holding current            | Positive polarity<br>Negative polarity                                                                | 100<br>150 |          |            | mA   |

| I <sub>R</sub>  | Leakage current (note 3)   | V <sub>R</sub> = +105 V<br>V <sub>R</sub> = -180 V                                                    |            |          | 10<br>10   | μΑ   |

| С               | Capacitance                | $F = 1MHz$ , $V_{RMS} = 1V$ , $V_{R(T/G)} = -5V$<br>$F = 1MHz$ , $V_{RMS} = 1V$ , $V_{R(T/G)} = -50V$ |            | 30<br>16 |            | pF   |

# ELECTRICAL CHARACTERISTICS between TIP and RING (Tamb=25°C)

| Symbol         | Parameter                | Test conditions                                    | Min | Max      | Unit |

|----------------|--------------------------|----------------------------------------------------|-----|----------|------|

| I <sub>R</sub> | Leakage current (note 3) | V <sub>R</sub> = +180 V<br>V <sub>R</sub> = -180 V |     | 10<br>10 | μΑ   |

Note 1: Positive voltage means between T and G, or between R and G.

Negative voltage means between G and T, or between G and R.

Note 2:

See test circuit for V<sub>BO</sub> parameters I<sub>R</sub> measured at V<sub>R</sub> guarantees V<sub>BR</sub> > V<sub>R</sub> Note 3:

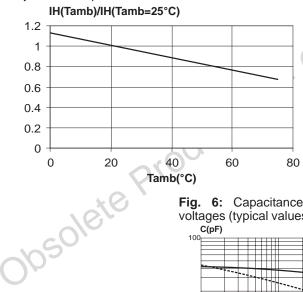

Fig. 4: Relative variation of holding current versus junction temperature.

Fig. 5: Non-repetitive peak on-state current versus overload duration (Tj initial = +25°C)..

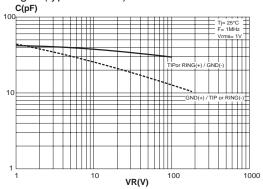

Fig. 6: Capacitance versus applied reverse voltages (typical values).

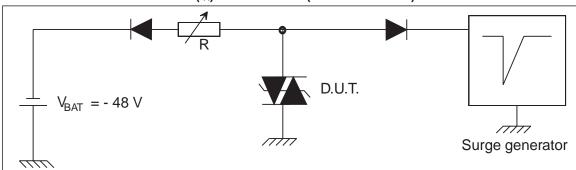

# FUNCTION HOLDING CURRENT (IH) TEST CIRCUIT (GO-NO GO TEST)

This is a GO-NOGO test which allows to confirm the holding current (I<sub>H</sub>) level in a functional test circuit.

### **TEST PROCEDURE:**

- 1) Adjust the current level at the I<sub>H</sub> value by short circuiting the D.U.T.

- 2) Fire the D.U.T with a surge Current : Ipp = 10A , 10/1000µs.

- 3) The D.U.T will come back off-state within 50 ms max.

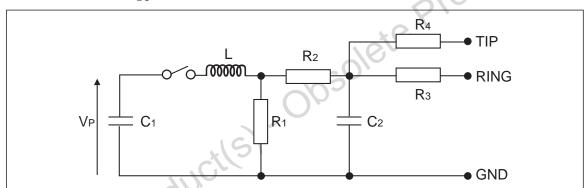

### TEST CIRCUIT FOR VBO PARAMETERS:

| Pulse          | e (µs)     | <b>V</b> <sub>p</sub> | <b>C</b> <sub>1</sub> | <b>C</b> <sub>2</sub> | L    | R <sub>1</sub>      | R <sub>2</sub>      | R <sub>3</sub>      | R <sub>4</sub>      | <b>I</b> PP | Rp                  |

|----------------|------------|-----------------------|-----------------------|-----------------------|------|---------------------|---------------------|---------------------|---------------------|-------------|---------------------|

| t <sub>r</sub> | <b>t</b> p | (V)                   | (µF)                  | (nF)                  | (µH) | <b>(</b> Ω <b>)</b> | <b>(</b> Ω <b>)</b> | <b>(</b> Ω <b>)</b> | <b>(</b> Ω <b>)</b> | (A)         | <b>(</b> Ω <b>)</b> |

| 10             | 700        | 1000                  | 20                    | 200                   | 0    | 50                  | 15                  | 25                  | 25                  | 38          | 0                   |

| 1.2            | 50         | 1500                  | 1                     | 33                    | 0    | 76                  | 13                  | 25                  | 25                  | 30          | 10                  |

| 2              | 10         | 2500                  | 10                    | 0                     | 1.1  | 1.3                 | 0                   | 3                   | 3                   | 38          | 62                  |

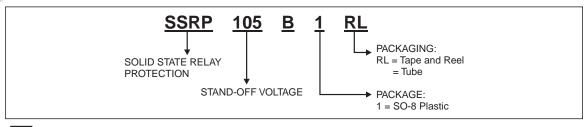

### ORDER CODE

# **SSRP105B1**

### OTHER INFORMATION

| Orderin | g type | Marking | Package | Weight  | Base Qty (pcs) | Delivery mode       |

|---------|--------|---------|---------|---------|----------------|---------------------|

| SSRP10  |        | SSR105  | SO-8    | 0.08 g. | 100<br>2500    | Tube<br>Tape & Reel |

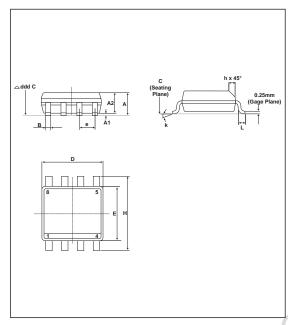

### **PACKAGE MECHANICAL DATA**

SO-8 (Plastic)

|      | DIMENSIONS  |        |        |       |  |  |  |

|------|-------------|--------|--------|-------|--|--|--|

| REF. | Millim      | netres | Inches |       |  |  |  |

|      | Min. Max.   |        | Min.   | Max.  |  |  |  |

| Α    | 1.35        | 1.75   | 0.053  | 0.069 |  |  |  |

| A1   | 0.1         | 0.25   | 0.004  | 0.010 |  |  |  |

| A2   | 1.10        | 1.65   | 0.043  | 0.065 |  |  |  |

| В    | 0.33        | 0.51   | 0.013  | 0.020 |  |  |  |

| С    | 0.19        | 0.25   | 0.007  | 0.010 |  |  |  |

| D    | 4.80        | 5.00   | 0.189  | 0.197 |  |  |  |

| Е    | 3.80        | 4.00   | 0.150  | 0.157 |  |  |  |

| е    | 1.27        | Тур.   | 0.05   | Тур.  |  |  |  |

| Н    | 5.80        | 6.20   | 0.228  | 0.244 |  |  |  |

| h    | 0.25        | 0.50   | 0.010  | 0.019 |  |  |  |

| L    | 0.40        | 1.27   | 0.016  | 0.050 |  |  |  |

| k.   | 8° (max)    |        |        |       |  |  |  |

| ddd  | 0.100 0.004 |        |        |       |  |  |  |

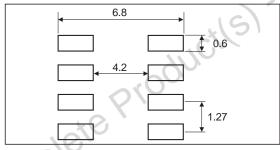

### **FOOT-PRINT DIMENSIONS** (in millimeters)

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

$\hbox{@ 2002 STM}{\sc icroelectronics}$  - Printed in Italy - All rights reserved.

STMicroelectronics GROUP OF COMPANIES Australia - Brazil - Canada - China - Finland - France - Germany

Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore

Spain - Sweden - Switzerland - United Kingdom - United States.

http://www.st.com