#### Dual current limited over-voltage protected digital termination

#### **Applications**

- Type 1, 2 and 3 logic input termination for industrial automation

- AS-Interface bus input termination

- I/O termination in programmable logic controller

- Proximity detector interface

- Decentralized Input / Output modules

#### **Features**

- 2 channel topology

- Low side input with common ground

- Wide range input DC Voltage:

- V  $_{I}$  = 0.3 to 30 V with R  $_{I}$  = 0  $\Omega$

- $V_1 = -30 \text{ to } 35 \text{ V with } R_1 = 750 \Omega$

- Current limiter:

- 3 to 7.5 mA programmable reference

- $\,$  I  $_{I\,IM}$  = 6.1 mA to 8.8 mA with  $R_{REF}$  = 10  $k\Omega$

- I<sub>LIM</sub> = 2.8 mA to 4.3 mA with R<sub>REF</sub> = 22 k $\Omega$

- Narrow limiter spread: < 17 %</li>

- Temperature compensated operation

- Output drive:

- No output activation below 2 mA input current

- 1.5 mA minimum output activating current in opto-coupler mode

- Programmable CMOS output mode option (V<sub>MOD</sub> > 2.9 V)

- LED drive for sensor status: 4.4 mA typical with  $R_{BEF} = 10 \text{ k}\Omega$

- Input protection ( $R_I = 750 \Omega C_{IN} = 22 nF$ )

- IEC61000-4-2 electrostatic discharge ESD, Level 4

- In contact, ± 8 kV; in air, ± 15 kV

- Criteria B: temporary disruption

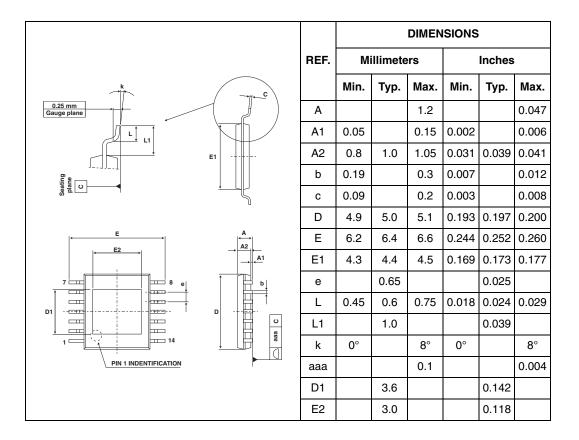

# TSSOP14 Exposed pad

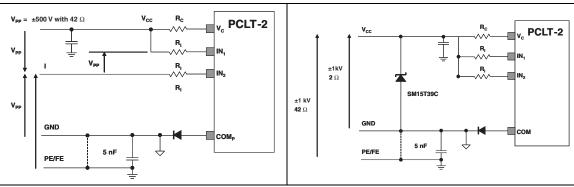

- IEC61000-4-5 voltage surge, Level 3

- $\pm$  500 V with 42  $\Omega$  series resistor in differential mode

- Criteria B: temporary disruption

- IEC61000-4-4 transient burst immunity

- ± 4 kV peak voltage; 5 kHz repetitive rate

- Criteria A: fully functional

- IEC61000-4-6 conducted Radio Frequency Interference immunity

- 10 V<sub>RMS</sub> voltage

- Criteria A: fully functional

- Input protection against -30 V reverse polarity

- Ambient temperature: -25 to 85 °C

#### **Benefits**

- Enable input to meet type1, 2 and 3 characteristics of IEC61131-2 standard

- Compatible operation with 2 & 3 wires proximity sensor according EN60947-5-2 standard

- Flexible configuration driving either opto coupler, or CMOS bus controller input, or 12 V AS-interface network

- Reduced overall dissipation

- Enhanced functional reliability

- Compact with high integration

- Surface Mount Package for highly automated assembly

- Insensitive to the on state sensor impedance

Rev 1 1/18

www.st.com

November 2005

## 1 Characteristics

#### 1.1 IEC61000-4 standard compliance application diagrams

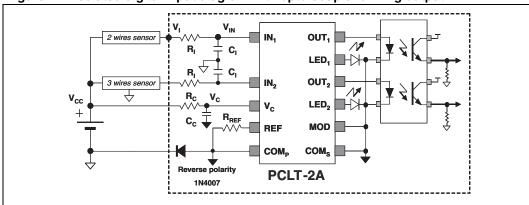

Figure 1. Isolated digital input diagram with opto-coupler driving output

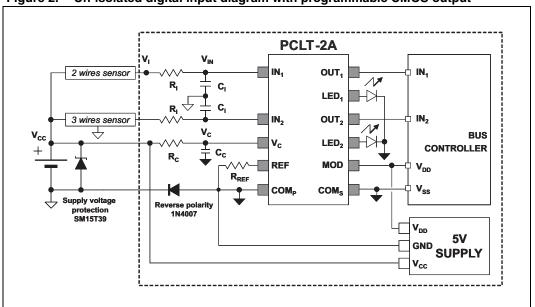

Figure 2. Un-isolated digital input diagram with programmable CMOS output

577

**PCLT-2A** 1 Characteristics

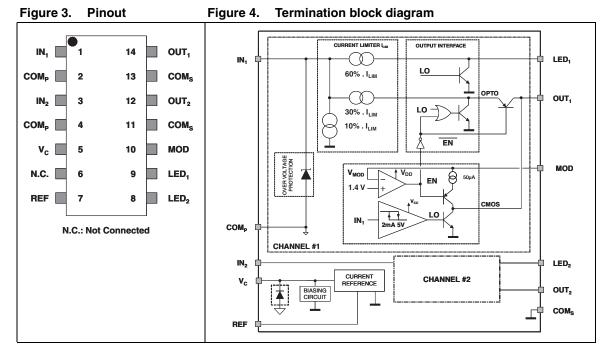

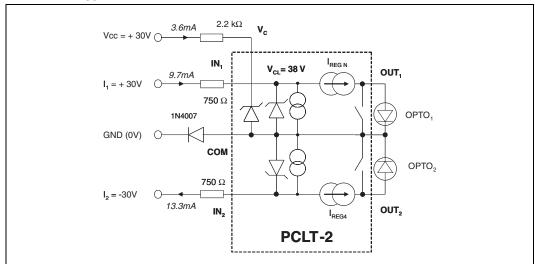

#### PCLT-2A Pinout and current limited termination block diagram 1.2

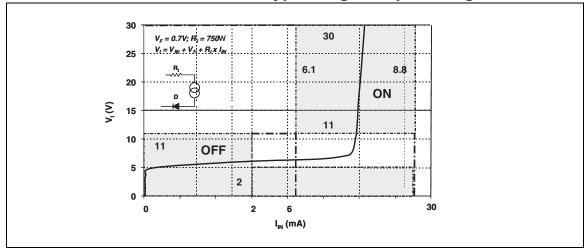

1.3 Static characteristic of a type-2 digital input using PCLT-2A

### 1.4 Absolute ratings

| Symbol                            | Pin            | Parameter name & conditions                                                                        | Value       | Unit |

|-----------------------------------|----------------|----------------------------------------------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>                   | V <sub>C</sub> | Power supply steady state voltage, $R_C = 2.2 \text{ k}\Omega$                                     | - 0.3 to 35 | V    |

| V <sub>C</sub>                    | V <sub>C</sub> | Supply steady state voltage, $R_C = 0 \text{ k}\Omega$                                             | - 0.3 to 30 | V    |

| V <sub>IN</sub>                   | IN             | Input steady state voltage, $R_I = 0 \text{ k}\Omega$                                              | - 0.3 to 30 | V    |

| V (Note: 1)                       | INI            | Input steady state voltage, $R_I = 750 \Omega$                                                     | -30 to 32   | V    |

| V <sub>I</sub> ( <i>Note: 1</i> ) | IN             | Input repetitive pulse voltage, $R_I = 750 \Omega$                                                 | -30 to 35   | V    |

| 1                                 |                | Input maximum forward current $R_I = 750~\Omega~R_C = 2.2~k\Omega$                                 | 10          | mA   |

| I <sub>IN</sub>                   | IN             | Input maximum reverse current $R_I = 750 \Omega \text{ RC} = 2.2 \text{ k}\Omega \text{ (Note 2)}$ | 20          | mA   |

| V <sub>MOD</sub>                  | MOD            | Maximum applied CMOS supply voltage                                                                | 14          | V    |

| V <sub>OM</sub>                   | OUT LED        | Maximum applied output voltage, V <sub>MOD</sub> < 0.75 V                                          | 2.5         | V    |

|                                   | OUT, LED       | Maximum applied output voltage, V <sub>MOD</sub> > 2.9 V                                           | 14          | V    |

| Гом                               | OUT, LED       | Output driver current                                                                              | - 4 to 7    | mA   |

| T <sub>J</sub>                    | ALL            | Junction temperature range                                                                         | - 25 to 150 | °C   |

## 1.5 Recommended operating conditions

| Symbol                  | Pin            | Parameter name & conditions                                            | Value       | Unit |

|-------------------------|----------------|------------------------------------------------------------------------|-------------|------|

| V <sub>CC</sub>         | V <sub>C</sub> | Power supply steady state voltage, $R_C = 2.2 \text{ k}\Omega$         | 19 to 35    | V    |

| V <sub>C</sub>          | V <sub>C</sub> | Power supply voltage range                                             | 14 to 27    | V    |

| V <sub>I</sub> (Note 1) | IN             | Input repetitive pulse voltage<br>$R_I = 750~\Omega~R_C = 2.2~k\Omega$ | - 30 to 30  | V    |

| V <sub>MOD</sub>        | MOD            | Operating CMOS mode voltage range                                      | 2.9 to 5.5  | V    |

| ▼ MOD                   | IVIOD          | Maximum operating 12V Analog voltage                                   | 13.5        | V    |

| T <sub>AMB</sub>        | ALL            | Operating Ambient temperature range                                    | - 25 to 85  | °C   |

| T <sub>J</sub>          | ALL            | Operating Junction temperature range                                   | - 25 to 150 | °C   |

Note: 1  $V_I = V_{IN} + V_F + R_I \times I_{IN}$  with  $V_{IN} = voltage$  at the PCLT-2A input pin;  $V_{CC} = V_C + R_C \times I_{CC}$  with  $V_C = voltage$  at the PCLT-2A power supply pin.

<sup>2</sup> Respect to the reverse polarity test of one input as shown on Figure 12.

PCLT-2A 1 Characteristics

#### 1.6 Electromagnetic compatibility ratings

$\rm T_J = 25~^{\circ}C,~R_I = 750~\Omega~R_C = 2.2~k\Omega$  , & reverse diode connected (unless otherwise specified)

| Symbol           | Node            | Parameter name & conditions                                                                                         | Value  | Unit |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------|--------|------|

|                  |                 | ESD protection, IEC 61000-4-2, per input, in air                                                                    | ± 15   | kV   |

| V                | , IN            | ESD protection, IEC 61000-4-2, per input, in contact                                                                | ± 8    | kV   |

| V <sub>ESD</sub> | V <sub>CC</sub> | ESD protection, IEC 61000-4-2, per input, in air, $R_{I} = 0 \Omega$                                                | ± 3    | kV   |

|                  |                 | ESD protection, IEC 61000-4-2, per input, in contact, $R_{I} = 0 \Omega$                                            | ± 3    | kV   |

| V <sub>PPB</sub> | VI              | Total Peak Pulse Voltage Burst, IEC61000-4-4 $C_C = 33 \text{ nF}, C_I = 22 \text{ nF}, F = 5 \text{ kHz (Note 1)}$ | ± 4    | kV   |

| $V_{PP}$         | VI              | Peak Pulse Voltage Surge, IEC61000-4-5, R = 42 $\Omega$ (Note 2)                                                    | ± 500  | V    |

| V <sub>PP</sub>  | VI              | Peak Pulse Voltage Surge, IEC61000-4-5, R = 42 $\Omega$ R <sub>I</sub> = 1200 $\Omega$ (Note 2)                     | ± 1000 | V    |

| V <sub>PP</sub>  | V <sub>CC</sub> | Peak Pulse Voltage Surge, IEC61000-4-5, R = 2 $\Omega$ (Note 2)                                                     | ± 1000 | V    |

Note: 1 Test diagram described on Figure 1 using the application PCB with a normalized capacitive coupling clamp

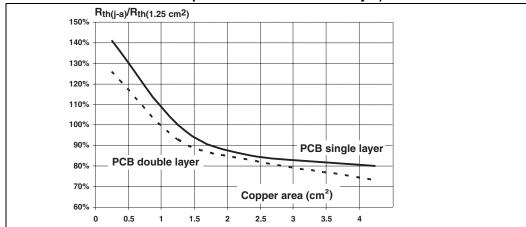

#### 1.7 Thermal resistance

| Symbol             | Parameter name & conditions                                                                                      | Value | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------------|-------|------|

| R <sub>TH JA</sub> | Thermal resistance Junction to ambient<br>Board copper surface = 1.25 cm², copper thickness = 35 µm, single face | 100   | °C/W |

<sup>2</sup> Test diagram described on Figure 1

#### 1.8 DC electrical characteristics

(T<sub>J</sub> = 25 °C, V<sub>CC</sub> = 24 V, R<sub>REF</sub> = 10 k $\Omega$  R<sub>C</sub> = 2.2 k $\Omega$  and referred to COM pin voltage, unless otherwise specified)

| Symbol              | Pin                | Name                                                                                                               | Conditions                                                                                                                                                                                                 | Min                      | Тур  | Max                      | Unit |

|---------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|------|

| Current li          | mitation           |                                                                                                                    |                                                                                                                                                                                                            |                          |      |                          |      |

| I <sub>LIM</sub>    | IN                 | Input limiting current                                                                                             | $V_{IN} = 4.5 \text{ to } 26 \text{ V}$ $V_{OUT} = 0.9 \text{ to } 1.5 \text{ V}$ $V_{LED} = 1.5 \text{ to } 2.5 \text{ V}$ $T_{AMB} = -25 \text{ to } 85 ^{\circ}\text{C}$ $R_{REF} = 10 \text{ k}\Omega$ | 6.1                      | 7.6  | 8.8                      | mA   |

| I <sub>LIM</sub>    | IN                 | Input limiting current                                                                                             | $V_{IN}$ = 5.5 to 26 V<br>$V_{OUT}$ = 0.9 to 1.5 V<br>$V_{LED}$ = 1.5 to 2.5 V<br>$T_{AMB}$ =-25 to 85 °C<br>$R_{REF}$ = 22 k $\Omega$                                                                     | 2.8                      | 3.6  | 4.3                      | mA   |

|                     |                    | Low current input voltage                                                                                          | I <sub>IN</sub> = 100 μA                                                                                                                                                                                   |                          | 1.5  | 3                        | ٧    |

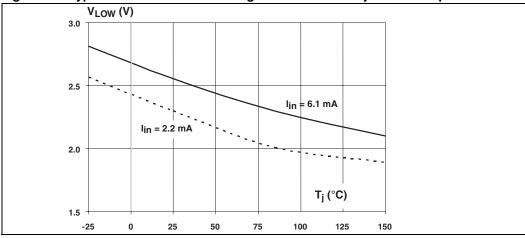

| $V_{LOW}$           | IN                 | Current limiter activation                                                                                         | I <sub>IN</sub> =6 mA                                                                                                                                                                                      | -                        | 2.6  | -                        | V    |

|                     |                    | voltage                                                                                                            | $I_{IN}$ =2 mA, $R_{REF}$ =22 k $\Omega$                                                                                                                                                                   | -                        | 2.3  | -                        | ٧    |

| Input & S           | upply Prote        | ection                                                                                                             | •                                                                                                                                                                                                          |                          |      |                          |      |

| V <sub>CL</sub>     | IN, V <sub>C</sub> | Clamping voltage                                                                                                   | $I_{IN} = 7 \text{ mA}, t_P = 1 \text{ ms}, R_{REF} \text{ open}$                                                                                                                                          | 31                       | 38   | -                        | ٧    |

| Output in           | terface ope        | eration                                                                                                            |                                                                                                                                                                                                            |                          |      |                          |      |

|                     | OUT                | 0"                                                                                                                 | V <sub>MOD</sub> = 0 V, V <sub>I</sub> = 5 V, (Note 1)                                                                                                                                                     | -                        | 10   | 40                       | μA   |

| l <sub>OFF</sub>    | LED                | Off state output current                                                                                           | V <sub>MOD</sub> = 0 V, I <sub>IN</sub> =2 mA, (Note <i>2</i> )                                                                                                                                            | -                        | 10   | 40                       | μΑ   |

| V <sub>OFF</sub>    | LED                | Off state LED voltage                                                                                              | I <sub>IN</sub> = 2 mA                                                                                                                                                                                     |                          | 0.1  | 0.2                      | ٧    |

|                     |                    |                                                                                                                    | V <sub>MOD</sub> = 0 V, I <sub>IN</sub> = 2 mA                                                                                                                                                             |                          | 0.02 | 0.1                      | V    |

| V <sub>OFF</sub>    | OUT                | Off state output voltage                                                                                           | V <sub>MOD</sub> > 2.9 V, I <sub>IN</sub> = 2 mA                                                                                                                                                           |                          |      | 20 %<br>V <sub>MOD</sub> | ٧    |

| 1                   | OUT                | On state opto-coupler                                                                                              | V <sub>MOD</sub> = 0 V, V <sub>OUT</sub> = 1.5 V<br>V <sub>IN</sub> =4.5 V                                                                                                                                 | 1.5                      | 2    |                          | mA   |

| I <sub>ON</sub> OUT | current            | $V_{MOD} = 0 \text{ V}, V_{IN} = 5.5 \text{ V},$ $R_{REF} = 22 \text{ k}\Omega \text{ , } V_{OUT} = 1.5 \text{ V}$ | 0.5                                                                                                                                                                                                        | 0.9                      |      | mA                       |      |

| V <sub>ON</sub>     | OUT                | On state output voltage                                                                                            | $V_{MOD} > 2.9 \text{ V}$ $R_{REF} = 10 \text{ k}\Omega$ , $V_{IN} > 4.5 \text{ V}$ $R_{REF} = 22 \text{ k}\Omega$ $V_{IN} > 5.5 \text{ V}$                                                                | 80%.<br>V <sub>MOD</sub> |      |                          |      |

|                     |                    |                                                                                                                    | V <sub>IN</sub> = 4.5 V, V <sub>LED</sub> = 2.5 V (Note <i>3</i> )                                                                                                                                         | 3.5                      | 4.4  |                          | mA   |

| I <sub>ON</sub>     | LED                | On state LED current                                                                                               | $V_{IN} = 5.5 \text{ V}, R_{REF} = 22 \text{ k}\Omega$<br>$V_{LED} = 2.5 \text{ V}$                                                                                                                        | 1.4                      | 2.1  |                          | mA   |

577

PCLT-2A 1 Characteristics

| Symbol              | Pin                                | Name Conditions       |                                              | Min  | Тур  | Max  | Unit |

|---------------------|------------------------------------|-----------------------|----------------------------------------------|------|------|------|------|

| Output ope          | Output operation selection circuit |                       |                                              |      |      |      |      |

| V <sub>TH MOD</sub> | MOD                                | Opto-CMOS threshold   |                                              | 0.75 |      | 2.9  | V    |

| I <sub>OUT</sub>    | OUT                                | CMOS output current   | V <sub>MOD</sub> = 12V                       | 35   | 50   | 65   | μΑ   |

| Power supp          | Power supply circuit               |                       |                                              |      |      |      |      |

| I <sub>C</sub>      | V <sub>C</sub>                     | Supply current        | V <sub>CC</sub> = 30V                        |      | 1.5  | 2    | mA   |

| l                   | MOD CMOS supp                      |                       | V <sub>MOD</sub> = 5V, V <sub>IN</sub> open  |      | 0.25 | 0.35 | mA   |

| IDD                 |                                    | CiviOS supply current | V <sub>MOD</sub> = 12V, V <sub>IN</sub> open |      | 0.4  | 0.8  | mA   |

Note: 1 According to application diagram (Figure 1) with the use of a  $R_I$  = 750  $\Omega$  resistor a reverse diode from COM to GND ( $V_F$  = 0.7 V) and an opto-coupler ( $R_{LED}$  (0V) = 15 k $\Omega$  ,  $V_F$ =1.2 V).

- 2 Same as note 1 above, but  $R_{l}=0$ .

- 3 When no LED diode is used, connect LED pin to the COMP ground.

#### 1.9 Switching electrical characteristics

$(T_J = 25^{\circ}C,\,V_{CC} = 24$  V,  $R_C = 2.2k\Omega,\,C_I = 0$  and COM pin voltage referred unless otherwise specified)

| Symbol           | Pin    | Name                                | Conditions                                       | Min | Тур | Max | Unit |

|------------------|--------|-------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| F <sub>MAX</sub> | IN-OUT | Input to output operating frequency | Duty cycle = 50%                                 |     | 5   |     | kHz  |

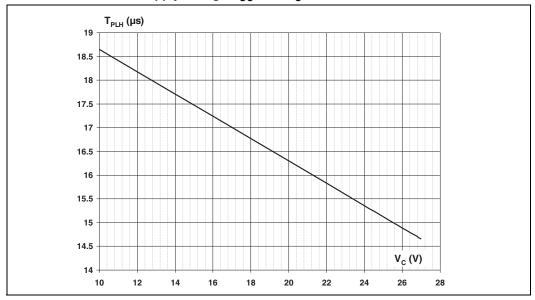

| T <sub>PLH</sub> | IN-OUT | Input Lo to Hi propagation time     | C <sub>I</sub> = 0                               |     | 16  |     | μs   |

|                  |        |                                     | $C_I = 0$ , $V_{MOD} = 0$ V                      |     | 0.1 |     |      |

| T <sub>PHL</sub> | IN-OUT | Input Hi to Lo propagation time     | $C_I = 0$ , $V_{MOD} = 5 V$<br>$C_{OUT} = 50 pF$ |     | 7.6 |     | μs   |

#### 1.10 Functional characteristics

Figure 5. Variation of the input-output propagation delay time  $T_{PLH}$  at rising edge versus the supply voltage  $V_{CC}$  with  $R_C$  = 2.2  $k\Omega$

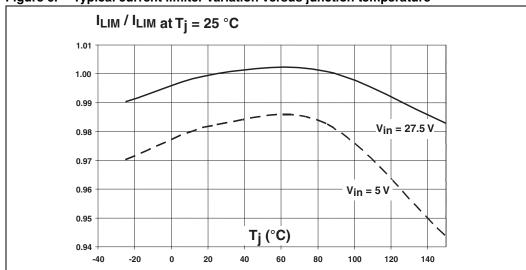

Figure 6. Typical current limiter variation versus junction temperature

PCLT-2A 1 Characteristics

ILIM (mA)

9

8

V<sub>C</sub> = 27 V, V<sub>in</sub> = 25 v,

V<sub>out</sub> = 0.9 V, V<sub>led</sub> = 1.5 V

Figure 7. Typical current limiter variation versus reference resistance R<sub>REF</sub>

20

25

$R_{REF}(k\Omega)$

15

10

0

Figure 9. Thermal resistance variation versus copper area (35  $\mu$ m layer thickness; 50vias/cm<sup>2</sup> and 300  $\mu$ m via diameter in double layer)

2 Functional description PCLT-2A

## 2 Functional description

The PCLT-2A is a dual input termination device designed for 24 V DC automation applications. It achieves the front-end circuitry of a digital input module (I/O) in industrial automation.

Available in a two channels configuration, it offers a high-density termination by minimizing the conducting dissipation and the external components count. It is housed in a surface mount package to reduce the printed board size.

Made of an input voltage protection, a serial current limiting circuit and an output interface, each channel circuit terminates the connection between the logic input and its associated high side sensor or switch.

The PCLT-2A is a current limited dual channel circuit compatible with the type 2 (7.5 mA) or type 3 (3 mA) characteristic of the IEC61131-2 standard. An external resistance R<sub>REF</sub> allows the limiting current value to be adjusted from 3 to 7.5 mA.

The unique structure of the PCLT limiter allows its activation threshold to be low and insensitive to the output voltage up to 2.5 V.

Each input voltage clamping block protects the module input against electromagnetic interferences such as those described in the IEC61131-2 standard and IEC61000-4-2 (ESD), 4-4 (transient burst), 4-5 (voltage surge) and 4-6 (conducted radio frequency interferences) standards. The supply input is also designed with such a protection structure.

The current limiting circuit connected between the input and the output pins is compensated all over the temperature range. Thanks to its low tolerance, the current limitation allows reducing drastically the dissipation of the input compared to a resistive input. Furthermore, the PCLT2 is housed into a very low R<sub>TH</sub> exposed pad TSSOP14 package that allows the PCB cooling pad to be reduced: the overall module becomes smaller and the hot spot effect is reduced.

The output block of each termination channel transfers the input logic state to a logic output and a Light Emitting Diode (LED) that allows this state to be checked visually.

### 2.1 The V<sub>MOD</sub> pin

The voltage  $V_{MOD}$  applied to the selector pin MOD allows the output OUT to be configured either in an opto-coupler driver for  $V_{MOD}$  less than 0.75 V or in a CMOS output able to interface directly a bus controller circuit for  $V_{MOD}$  higher than 2.9 V.

In CMOS mode, the  $V_{MOD}$  pin activates a CMOS compatible buffer output, able to source up to a 50  $\mu$ A current powered by the MOD pin.

#### 2.2 OFF state

In accordance with IEC61131-2 standard, for both opto-coupler and CMOS configuration modes when the input current is less than 2 mA (type 2) or 1.5 mA (type 3) the output circuits divert all the input current and maintain both LED and output in OFF state.

#### 2.3 ON state

When the module input voltage  $V_I$ , including the 750  $\Omega$  input resistor and the reverse diode, is higher than 11V corresponding to a PCLT input voltage  $V_{IN}$  of 5V, both LED and output circuits are in ON state. The input current is then shared between the internal circuitry, the LED (about 60 %), and the driver output (about 30 %) in case of opto-coupler mode.

In CMOS mode, the CMOS level is defined by the  $V_{MOD}$  voltage that is equal the supply voltage  $V_{DD}$  of the bus controller: it can be 3.3 V or 5 V. The output voltage is delivering 80 % of  $V_{DD}$  for high state and 20 %  $V_{DD}$  for low state.

When no LED diode is used, the LED outputs pin must be connected to the ground COM<sub>P</sub> of the circuit to allow the current to flow back to the power supply.

### 3 Surge voltage test circuit

The input and supply pins are designed to withstand electromagnetic interferences. They are protected by a clamping diode that is connected to the common pin COM. Combined with the serial input resistance RI, this clamping diode is effective against the fast transient bursts (±4 kV, IEC61000-4-4) and the voltage surges (±1 kV, IEC61000-4-5).

This topology allows the surge voltage to be applied from each input to other inputs, the ground and the supply contacts in differential or common modes (see figure 10).

Thanks to its high resistance  $R_C = 2.2~k\Omega$  and the conventional power supply protection that uses a clamping diode such as the SM15T39C Transil<sup>TM</sup>, the supply pin  $V_C$  withstands  $\pm 1000~V$  surge voltage according to IEC61000-4-5 (see figure 11).

Figure 10. Input pin IN voltage surge test circuit

Figure 11. Supply pin V<sub>C</sub> voltage surge test circuit

TM: Transil is a trademark of STMicroelectronics

577

## 4 Input reverse polarity robustness

Each input of the PCLT circuit may be biased to a reverse polarity equal to - V<sub>CC</sub>. This case corresponds to a connection mistake or a reverse biasing that is generated by the demagnetization of a monitored inductive solenoid.

The involved input withstands the high reverse current up to 20 mA; its opto-coupler is OFF and is protected by the conducting input diode. The input remains operational, and some extra dissipation should be take place in their clamping protections.

Figure 12. Current sharing in the PCLT device when  $\rm IN_2$  is biased at -30 V and  $\rm IN_1$  at +30 V.

Considering the supply operation, a reverse blocking diode can be connected between the module ground and the common pin COM to protect the PCLT device against any spurious reverse supply connection. Then, the whole module supply voltage rating is extended to  $\pm$  30 V.

# 5 Programming of the PCLT-2A according to the input type requirement

The operation of the PCLT-2 can be set to the various logic input types defined in the IEC61131-2 standard. The current reference of the input-limiting block of each channel is programmable thanks to an external resistor R<sub>REF</sub> Moreover, because the operating current is different for each type, the external input resistor R<sub>I</sub> can be changed to improve the overvoltage robustness of the whole circuit. *Table 1* describes the input characteristics requirements according to the IEC standard, and *Table 2* the resistance values for the 1, 2, and 3 types and the corresponding performances of the PCLT input.

Table 1. IEC61131-2 requirements for logic input

|       |                      | Туре | 1                          | 3                          | 2                          |

|-------|----------------------|------|----------------------------|----------------------------|----------------------------|

| State | Parameter            | Unit |                            |                            |                            |

| OFF   | I <sub>OFF MAX</sub> | mA   | 0.5                        | 1.5                        | 2                          |

|       | V <sub>OFF MAX</sub> | V    | 5<br>15 @ l <sub>OFF</sub> | 5<br>11 @ l <sub>OFF</sub> | 5<br>11 @ l <sub>OFF</sub> |

| ON    | I <sub>ON MIN</sub>  | mA   | 2                          | 2                          | 6                          |

|       | V <sub>ON MIN</sub>  | V    | 15                         | 11                         | 11                         |

Table 2. PCLT-2A setting for each type of logic input

| Туре                    |      | 1                                 | 3   | 2    |  |

|-------------------------|------|-----------------------------------|-----|------|--|

| Setting                 | Unit | ı                                 | 3   | 2    |  |

| R <sub>REF</sub>        | kΩ   | 22                                | 22  | 10   |  |

| R <sub>I</sub>          | kΩ   | 2.2                               | 1.2 | 0.75 |  |

| R <sub>C</sub>          | kΩ   |                                   | 2.2 |      |  |

| PERFORMANCES            |      |                                   |     |      |  |

| I <sub>IN MIN</sub>     | mA   | 2.8                               | 2.8 | 6.1  |  |

| I <sub>IN TYP</sub>     | mA   | 3.6                               | 3.6 | 7.6  |  |

| I <sub>IN MAX</sub>     | mA   | 4.3                               | 4.3 | 8.8  |  |

| I <sub>LED TYP</sub>    | mA   | 2.1                               | 2.1 | 4.4  |  |

| SURGE w/R <sub>I</sub>  | kV   | > 1                               | 1   | 0.5  |  |

| ESD with R <sub>I</sub> | kV   | 8 in contact, 15 in air (class 4) |     |      |  |

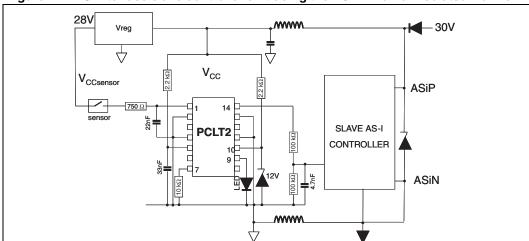

### 6 Unisolated ASI-interface bus application diagram

#### 6.1 AS-Interface Bus application overview

The AS-Interface bus is a low-end field bus for actuators and sensors in manufacturing & industrial automation. Its electrical architecture uses an unshielded 2-wire yellow cable that transports both the 24 V power supply of the field nodes and the serial bi-directional data communication.

AS-i MASTER

Power Supply

30.5V<sub>DC</sub>

/ 8 A

Vo slave

Vo slave

AS-i Slaves

AS-i Slaves

Figure 13. Simplified architecture of AS-Interface bus.

The data communication is achieved with a current carrier modulation superimposed over the power wires. Therefore, the power bus terminals are filtered in order to maintain identical and calibrated differential and common mode impedances measured by both master and slave units.

# 6.2 Isolation of the sensor section and the supply from data/supply bus

The PCLT can be designed as an interface between a proximity sensor and its associated slave controller unit.

The sensor power supply is generated from the bus power supply with a filter and a regulator that are inserted in the slave unit. In the same manner, the sensor logic signal is isolated from the AS- Interface power supply bus to avoid any degradation of the data transmission.

A conventional way to achieve the interface with the PCLT and the AS- Interface controller is to insert an opto-coupler between the AS-Interface controller and the PCLT that runs in opto-coupler mode as shown on figure 1 (MOD=0).

57

# 6.3 Un-isolated connection of the PCLT with AS-Interface controller

To remove the opto-coupler the operation of the PCLT has been extended to fit the AS-Interface application. A precaution is required on its interface with the bus controller: the impedance between the two circuits must be high in order to maintain the impedance isolation.

To achieve this impedance isolation, the PCLT runs in CMOS mode (MOD= $V_{CC}$ ) and the buffer operation is extended up to  $V_{CC}$  = 12 V. In the application, the  $V_{CC}$  voltage is generated with a Zener diode reference fed from the sensor bus.

Because of the buffer voltage increase, it becomes possible to insert high impedance between the PCLT output and the AS-Interface bus controller input. Typically a  $100 \text{k}\Omega$  resistor is designed while keeping a 5 V CMOS operation on the input of the bus controller.

Figure 14 shows the application diagram where the PCLT is connected to the slave bus controller through a 100 kΩ resistor. The logic signal is transmitted with a low level of less than 20% of the  $V_{DD}$  supply voltage and a high level of at least 3.5 V defined by the PCLT output buffer limiting its current to 35 μA minimum and the 100 kΩ pull down resistor (0.035 mA times 100 kΩ).

Figure 14. AS-Interface slave controller unit using the PCLT in an un-isolated manner.

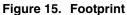

# 7 Package mechanical data

**577**

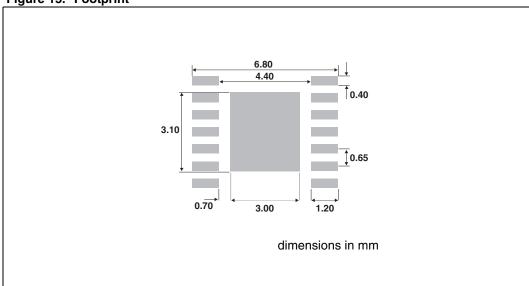

## 8 Ordering information scheme

## 9 Ordering information

| Ordering Code | Marking   | Package                | Weight | Base Qty | Delivery Mode |

|---------------|-----------|------------------------|--------|----------|---------------|

| PCLT-2AT4     | PCLT-2AT4 | TSSOP14 <sup>(1)</sup> | 0.057g | 96       | Tube          |

| PCLT-2AT4-TR  | PCLT-2AT4 | TSSOP14 <sup>(1)</sup> | 0.057g | 2500     | Tape & reel   |

<sup>1.</sup> Exposed pad version

## 10 Revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 16-Nov-2005 | 1        | Initial release. |

10 Revision history PCLT-2A

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2005 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

**57**